用于每列具有两个位线的电阻式随机存取存储器阵列的电路和布局

文献发布时间:2023-06-19 09:41:38

背景技术

本发明涉及集成电路技术和电阻式随机存取存储器(ReRAM)技术。更具体地讲,本发明涉及采用小几何晶体管器件诸如FinFET晶体管器件的ReRAM存储器单元的可寻址阵列的集成电路布局。通过驱动配置可编程电路的开关晶体管,ReRAM存储器单元已被用作用户可编程集成电路的配置存储器。ReRAM存储器单元也已被用作集成电路中的随机存取存储器(RAM)。本发明涉及在集成电路中用作随机存取存储器(RAM)单元的ReRAM存储器单元,这些存储器单元必须被寻址并耦接到感测放大器以读取这些存储器单元包含的数据。

由于小几何晶体管器件诸如FinFET晶体管不能单独支持编程和擦除ReRAM器件所需的电压,因此两个FinFET晶体管已被串联放置在可寻址ReRAM存储器单元中。

首先参见图1、图2A和图2B,分别示出了现有技术ReRAM存储器阵列的部分10的示意图、图1所示的存储器阵列的部分10的布局的顶视图以及通过线2B-2B截取的图2A所示的存储器阵列的部分的布局的剖视图。在图1中,现有技术ReRAM存储器阵列的部分10包括六个ReRAM存储器单元(分别在附图标号12a至12f处以虚线指示)。ReRAM存储器单元12a、12b和12c位于阵列的第一列中,并且ReRAM存储器单元12d、12e和12f位于阵列的第二列中。本领域的普通技术人员将观察到,存储器单元12a至12f的布局为镜像配置。因此,在阵列的第一列中,存储器单元12a和12b彼此镜像,存储器单元12b和12c彼此镜像。类似的镜像存在于阵列的第二列中。

每个存储器单元12a至12f包括ReRAM器件和两个串联晶体管器件。将使用对应于这些电路元件设置在其中的存储器单元的字母后缀来指定这些电路元件。作为示例,ReRAM存储器单元12a包括ReRAM器件14a以及两个n沟道FinFET晶体管器件16a和18a,所述两个n沟道FinFET晶体管器件全部串联在第一公共偏置节点20-1和附图标号22-1处的与阵列的部分10的第一列相关联的第一位线BL0之间。在本文ReRAM器件的附图符号中使用的约定是:ReRAM器件的较宽端为器件的离子源侧,并且较窄端是通过固体电解质层与离子源分开的相对电极。为了编程ReRAM器件,即,为了将其设置为较低的电阻,以最大的正电势向ReRAM器件的较宽端施加编程电压。为了擦除ReRAM器件,即,为了将其设置为高的电阻,以最大的正电势向ReRAM器件的较窄端施加编程电压。

ReRAM存储器单元12b包括ReRAM器件14b以及两个n沟道FinFET晶体管器件16b和18b,所述两个n沟道FinFET晶体管器件全部串联连接在第二公共偏置节点20-2和第一位线22-1之间。ReRAM存储器单元12c包括ReRAM器件14c以及两个n沟道FinFET晶体管器件16c和18c,所述两个n沟道FinFET晶体管器件全部串联连接在第二公共偏置节点20-2和第一位线22-1之间。ReRAM单元12d、12e和12f类似地连接,不同的是它们分别连接在公共偏置节点20-1和20-2以及与阵列的部分10的第二列相关联的第二位线22-2之间。

阵列的每行中的两个FinFET晶体管的栅极共同连接到字线。因此,FinFET晶体管16a和18a以及16d和18d一起连接到附图标号24处的字线WL0。字线24以两个区段示出,所述两个区段中的每个区段表示由例如金属或金属硅化物形成的栅极线,该栅极线延伸包含ReRAM存储器单元12a和12d的阵列中的行的长度。如连接26所示,这些栅极线被接合在一起。类似地,FinFET晶体管16b和18b以及16e和18e的栅极一起连接到附图标号28处的字线WL1。如连接30所示,这些栅极线被接合在一起。FinFET晶体管16c和18c以及16f和18f的栅极一起连接到附图标号32处的字线WL2。如连接34所示,这些栅极线被接合在一起。

现在参见图2A和图2B两者,示意图示出了用于ReRAM存储器单元(如图1A的那些)的集成电路中的具体实施的典型布局40。图2A和图2B中描绘的ReRAM阵列的部分在图1的虚线36内示出。因此,本领域的普通技术人员将会注意到,图2A和图2B中描绘的布局不包括图1中描绘的ReRAM单元12c和12f。其中图2A和图2B中描绘了图1中的元件,将使用与图1中的这些元件所用相同的附图标号来指定这些元件。

为简单起见,在图2A中表示为扩散部的第一组翅片42形成阵列的第一列的FinFET晶体管16a、18a、16b和18b的源极、漏极和沟道,并且第二组翅片44形成阵列的第二列中的FinFET晶体管16d、18d、16e和18e的源极、漏极和沟道。在图2A中的附图标号12a、12b、12d和12e处指示的虚线示出图1的ReRAM存储器单元12a、12b、12d和12e的位置。

栅极电极线46形成FinFET晶体管16a和16d的栅极并用作字线WL0。栅极线48形成FinFET晶体管18a和18d的栅极并且也用作字线WL0(如图1和图2A中的连接26所示)。栅极电极线50形成FinFET晶体管16b和16e的栅极并用作字线WL1。栅极电极线52形成FinFET晶体管18b和18e的栅极,并且也用作字线WL1(如图1和图2A中的连接30所示)。栅极电极线46、48、50和52由金属形成,如FinFET制造领域中已知的。

FinFET技术需要虚拟栅极电极来终止扩散区的端部以将其与邻接的扩散区域隔离。虚拟栅极电极与栅极电极线46、48、50和52同时且以相同方式形成,并被称为虚拟栅极电极,因为在这些栅极电极下方不形成晶体管。虚拟栅极电极线54提供设置在虚拟栅极电极线54上方的ReRAM器件14a、14d和ReRAM器件(未示出)之间的隔离。类似地,虚拟栅极电极线56提供设置在栅极电极线56下方的ReRAM器件14b、14e和ReRAM器件(未示出)之间的隔离。

图2B中的附图标号58指示栅极电极线46、48、50、54和56下方的栅介质层。接触件60和62将栅极电极线46和48连接到将FinFET 16a和18a的栅极连接在一起的金属级0(M0)区段64(在图1中标识为接线连接26)。接触件66和68将栅极线50和52连接到将FinFET 16b和18b的栅极连接在一起的M0区段70(在图1中标识为接线连接30)。

金属级0(M0)区段72-1通过图2B所示的接触件74连接到翅片组42。接触件76将M0区段72-1连接到金属级1(M1)区段78。接触件80将M1区段78连接到金属级2(M2)区段82。图2A和图2B两者中所示的接触件84将M2区段82连接到用作图1中的位线22-1的金属级3(M3)区段86。为避免使附图过度复杂化,金属区段78和82以及接触件76和80未在图2A中示出。

金属层2区段88用作图1中的第一公共偏置节点20-1。接触件90-1将M2区段88连接到图1的ReRAM 14a,如图2A所示,并且在图2B中也示出为包括离子源层92和固体电解质层94。本领域技术人员将理解,ReRAM器件是已知的并且比图2B所示更复杂。如图2B所示,ReRAM器件14a通过接触件96连接到M1层区段98、通过接触件100连接到M0区段102-1以及通过接触件104而连接到FinFET晶体管16a。

金属层2区段106用作图1中的第二公共偏置节点20-2,接触件90-2将M2区段106连接到图1的ReRAM 14b,如图2A所示,并且在图2B中也示出为包括离子源层108和固体电解质层110。本领域技术人员将理解,ReRAM器件是已知的并且比图2B所示更复杂。如图2B所示,ReRAM器件14b通过接触件112连接到M1层区段114、通过接触件116连接到M0区段102-2以及通过接触件118而连接到FinFET晶体管16b。

为了编程图1中的存储器单元12a中的ReRAM器件14a,将正电压施加到字线WL0 24以接通晶体管16a和18a,并且在偏置线20-1和位线022-1之间施加电压,其中将更大的正电势施加到偏置线20-1。为了擦除图1中的存储器单元12a中的ReRAM器件14a,将正电压施加到字线WL0 24以接通晶体管16a和18a,并且在偏置线20-1和位线0 22-1之间施加电压,其中将更大的正电势施加到位线0 22-1。为了禁止存储器单元12b和12c中的ReRAM器件14b和14c的编程/擦除,断开字线WL1 28和WL232。为了禁止存储器单元12d、12e和12f中的ReRAM器件14d、14e和14f的编程/擦除,将位线1 22-2处的电压设置为与偏置线0 20-1相同的电压。

在用于编程ReRAM存储器单元(使用存储器单元12a作为示例)的偏置条件下,晶体管16a和18a处于提供电流限制的公共源极配置中。此外,由于晶体管16a和18a两者都被接通,因此在它们两端的电压接近零,从而导致这些晶体管上很小的应力或没有应力。在用于擦除ReRAM器件的相反方向上(使用存储器单元12a作为示例)不存在电流限制,因为所选择的ReRAM单元的FinFET晶体管都不接地(即,处于公共源极配置中),并且ReRAM器件14a的变化的电阻将源极偏压置于晶体管16a和18a上,从而降低了晶体管的电流处理能力。此外,晶体管16a和18a两端存在比编程期间更高的电压,从而需要更多数量的FinFET晶体管来支持该电压。该要求限制了ReRAM存储器单元的最小化。

此外,ReRAM存储器单元需要约100μA或更大的编程电流和擦除电流。为了提供此类电流,编程和擦除路径必须具有足够低的阻抗以允许该量值的编程和擦除电流流动。随着器件尺寸减小,所使用的晶体管变得更小、更弱,并且需要更宽的金属线以提供必要的编程电势。此外,如上文相对于图2A所述,采用使用深亚微米线制造的ReRAM存储器单元的现有技术ReRAM存储器阵列(即,FinFET晶体管器件)需要采用附加虚拟栅极线(例如,图2A中的虚拟栅极线54和56)来终止单元之间的扩散区域的量化布局规则。

发明内容

根据本发明的一个方面,公开了一种用于包括ReRAM单元的行和列的ReRAM存储器单元阵列的布局,每个ReRAM单元位于ReRAM单元的行和列中。每个ReRAM单元包括ReRAM器件。第一晶体管耦接在所述ReRAM器件和与包含所述ReRAM单元的所述列相关联的第一位线之间。所述第一晶体管具有耦接到与包含所述ReRAM单元的所述行相关联的第一字线的栅极。第二晶体管耦接在所述ReRAM器件和与包含所述ReRAM单元的所述列相关联的第二位线之间。所述第二晶体管具有耦接到与包含所述ReRAM单元的所述行相关联的第二字线的栅极。

附图说明

下面将参考实施方案和附图更详细地解释本发明,附图中示出:

图1是现有技术ReRAM存储器阵列部分的示意图;

图2A是图1所示的存储器阵列部分的布局的顶视图;

图2B是沿线2B-2B截取的图2A所示的存储器阵列的部分的布局剖视图;

图3是根据本发明的一个方面的ReRAM存储器阵列的部分的示意图;

图4A是图3所示的存储器阵列的部分的布局顶视图;

图4B是沿线4B-4B截取的图4A所示的存储器阵列的部分的布局剖视图;

图4C为沿线4C-4C截取的图4A所示的存储器阵列的部分的布局剖视图;并且

图5是示出根据本发明的一个方面的典型ReRAM存储器阵列以及相关联的读取、写入和擦除控制电路的框图。

具体实施方式

本领域普通技术人员将认识到,本发明的以下描述仅是示例性的而非以任何方式进行限制。本发明的其他实施方案将易于向本领域技术人员提出。

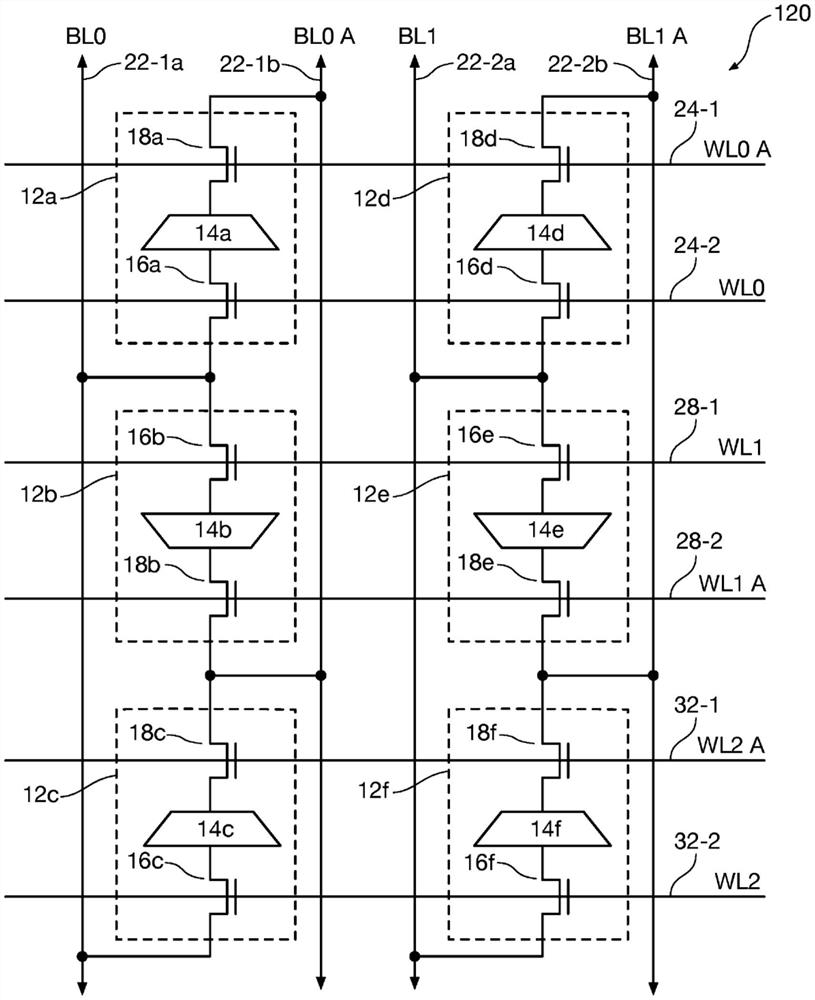

现在参见图3,示意图示出了根据本发明的一个方面的可寻址ReRAM存储器阵列的部分120。图3的实施方案中的各种电路元件对应于图1的现有技术阵列中的电路元件,并且将使用与用于标识图1中的那些电路元件相同的附图标号来指代。

在图3中,根据本发明的该例示性实施方案的可寻址ReRAM存储器阵列的部分120包括六个ReRAM存储器单元(分别以虚线在附图标号12a至12f处指示)。ReRAM存储器单元12a、12b和12c位于阵列的第一列中,并且ReRAM存储器单元12d、12e和12f位于阵列的第二列中。

每个存储器单元12a至12f包括ReRAM器件和与相应ReRAM器件串联连接但在该相应ReRAM器件的相对端上的两个晶体管器件。将使用对应于这些电路元件设置在其中的存储器单元的字母后缀来指定这些电路元件。作为示例,ReRAM存储器单元12a包括ReRAM器件14a和两个n沟道FinFET晶体管器件16a和18a。与图1中的晶体管16a和18a不同,FinFET晶体管16a连接在ReRAM器件14a的离子源和与阵列的部分120的第一列相关联的第一位线(BL0)附图标号22-1a之间,并且FinFET晶体管18a连接在ReRAM器件14a的相对电极和与阵列的部分120的第一列相关联的第二互补位线(BL0 A)附图标号22-1b之间。

ReRAM存储器单元12b包括ReRAM器件14b以及两个n沟道FinFET晶体管器件16b和18b。FinFET晶体管16b连接在ReRAM器件14b的离子源和阵列的第一位线(BL0)22-1a之间,并且FinFET晶体管18b连接在ReRAM器件14b的相对电极和与阵列的部分120的第一列相关联的第二互补位线(BL0 A)22-1b之间。

ReRAM存储器单元12c包括ReRAM器件14c以及两个n沟道FinFET晶体管器件16c和18b。FinFET晶体管16c连接在ReRAM器件14c的离子源和阵列的第一位线(BL0)22-1a之间,并且FinFET晶体管18c连接在ReRAM器件14c的相对电极和与阵列的部分120的第一列相关联的第二互补位线(BL0 A)22-1b之间。

ReRAM单元12d、12e和12f类似地连接,不同的是它们连接在互补位线(BL1)22-2a和(BL1 A)22-2b之间。

本领域的普通技术人员将注意到,ReRAM器件的取向在交替的行中改变。这是因为图4A至图4C所示的布局在交替的行中镜像。如所指示的那样,通过将最大正电势置于ReRAM器件的被示出为比另一端宽的端部来对ReRAM器件进行编程。

阵列的第一行中的两个FinFET晶体管16a和16d的栅极共同连接到字线(WL0)24-2。阵列的第一行中的两个FinFET晶体管18a和18d的栅极共同连接到字线(WL0 A)24-1。阵列的第二行中的两个FinFET晶体管16b和16e的栅极共同连接到字线(WL1)28-1。阵列的第二行中的两个FinFET晶体管18b和18e的栅极共同连接到字线(WL1 A)28-2。阵列的第三行中的两个FinFET晶体管18c和18f的栅极共同连接到字线(WL2)32-1。阵列的第三行中的两个FinFET晶体管16c和16f的栅极共同连接到字线(WL2 A)32-1。

现在参见图4A、图4B和图4C,顶视图和剖视图示出了包括两列ReRAM存储器单元的图3所示的存储器阵列的部分120的例示性布局。图4B为沿线4B-4B截取的图4A所示的存储器阵列的部分的布局剖视图。图4C为沿线4C-4C截取的图4A所示的存储器阵列的部分的布局剖视图。图4A、图4B和图4C的实施方案中的电路元件中的一些对应于图2A和图2B的现有技术阵列中的电路元件,并且将使用与用于标识图2A和图2B中的那些电路元件相同的附图标号来指代。

图4A、图4B和图4C以虚线示出了阵列的第二行中的完整ReRAM存储器单元12b和12e以及阵列的第三行中的完整ReRAM存储器单元12c和12f。ReRAM存储器单元12b和12e上方的图4A的布局部分是ReRAM存储器单元12a和12d的不完整部分。

如图4A所示,阵列的第一列中的ReRAM器件14a、14b和14c连接到第一组翅片(被划分成区域122a至122f)。被划分成区域122a至122f的第一组翅片也形成阵列的第一列的FinFET晶体管16a、16b和16c的源极、漏极和沟道,并且第二组翅片124(被划分成区域124a至124f)形成阵列的第一列的FinFET晶体管18a、18b和18c的源极、漏极和沟道。

阵列的第二列中的ReRAM器件14d、14e和14f连接到第三翅片组126。第三翅片组126也形成阵列的第二列的FinFET晶体管16d、16e和16f的源极、漏极和沟道,并且第四翅片组128形成阵列的第二列的FinFET晶体管18d、18e和18f的源极、漏极和沟道。在图4B中示出了被划分成区域122a至122f的第一组翅片,并且在图4C中示出了被划分成区域124a至124f的第二组翅片。

栅极电极线130是字线WL0(图3中的附图标号24-2)并且形成ReRAM存储器单元12a和12d中的FinFET晶体管16a和16d的栅极(其仅一部分在图4A和图4B中示出)。栅极电极线132是字线WL1(图3中的附图标号28-1)并且形成ReRAM存储器单元12b和12e中的FinFET晶体管16b和16e的栅极。栅极电极线134是字线WL1 A(图3中的附图标号28-2)并且形成ReRAM存储器单元12b和12e中的FinFET晶体管18b和18e的栅极。栅极电极线136是字线WL2A(图3中的32-1)并且形成ReRAM存储器单元12c和12f中的FinFET晶体管18c和18f的栅极。栅极电极线138是字线WL2(图3中的附图标号32-2)并且形成ReRAM存储器单元12c和12f中的FinFET晶体管16c和16f的栅极。图4B所示的附图标号58指示将翅片组122与栅极电极线130、132、134、136和138分开的栅介质层。

如图4A和图4B所见,在阵列的第一列中,金属级3(M3)线140形成位线BL0(图3中的附图标号22-1a),并且如图4A和图4C所示,金属级3(M3)线142形成位线BL0 A(图3中的22-1b)。在阵列的第二列(仅在图4A中可见)中,金属级3(M3)线144形成位线BL1(图3中的22-2a),并且金属级3(M3)线146形成位线BL1 A(图3中的22-2b)。

图4A、图4B和图4C所示的实施方案包括与图2A和图2B描绘的现有技术布局中的结构类似的一些结构。这些结构包括将晶体管扩散部连接到位线的接触结构和金属区段结构,以及形成ReRAM器件的层和将ReRAM器件连接到布局中电路的其余部分的接触结构和金属区段结构。这些结构在图3、图4A和图4B所示的实施方案中的位置不同于它们在图2A和图2B的现有技术布局中的位置。

如图4A和图4B所见,在ReRAM存储器单元12a的局部视图中,金属级0(M0)区段148通过图4B所示的接触件150连接到翅片组122a的部分,该部分形成FinFET晶体管16a的漏极。接触件152将M0区段148连接到金属级1(M1)区段154。接触件156将M1区段154连接到ReRAM器件14a的固体电解质层158。ReRAM器件14a的离子源层160通过接触件164连接到金属级2(M2)区段162。如参考图4C将更容易看到的,金属级2(M2)段162将ReRAM器件14a的离子源层160连接到第二组翅片中的翅片区域124a,如图4C所示。翅片区域124a形成晶体管18a的源极。如本领域的普通技术人员将理解的,晶体管18a的其余部分位于图4C的左边缘之外。

如图4B所示,金属级0(M0)段166通过接触件168连接到翅片组122b的部分,该部分形成FinFET晶体管16a和16b两者的源极。图4A和图4B两者中所示的接触件170将M0区段166连接到金属级1(M1)金属区段172。接触件174将金属级1(M1)金属区段172连接到金属级3(M2)区段176。接触件178将金属级2(M2)金属区段176连接到用作图3中的位线BL0 22-1a的金属级3(M3)区段140。

如图4A和图4B所见,在ReRAM存储器单元12b中,金属级0(M0)区段180通过图4B所示的接触件182连接到翅片组122c的部分,该部分形成FinFET晶体管16b的漏极。接触件184将M0区段180连接到金属级1(M1)区段186。接触件188将M1区段186连接到ReRAM器件14a的固体电解质层190。ReRAM器件14a的离子源层192通过接触件192连接到金属级2(M2)区段194。如参考图4C将更容易看到的,金属级2(M2)段194在第二组翅片中的翅片区域124c处将ReRAM器件14b的离子源层192连接到晶体管18b的源极。

如图4C所见,金属级2(M2)区段162通过接触件200连接到金属级1(M1)区段198。金属级1(M1)区段198通过接触件204连接到金属级0(M0)区段202。金属级0(M0)区段202通过接触件206连接到翅片组124a的部分,该部分形成FinFET晶体管18a的漏极。金属级2(M2)区段194通过接触件210连接到金属级1(M1)区段208。金属级1(M1)区段208通过接触件214连接到金属级0(M0)区段212。金属级0(M0)区段212通过接触件216连接到翅片组124c的部分,该部分形成FinFET晶体管18b的漏极。

还如图4C所见,金属级0(M0)区段218通过接触件220连接到翅片组124d的部分,该部分形成FinFET晶体管18b和18c两者的源极。图4A和图4C两者中所示的接触件222将M0区段218连接到金属级1(M1)金属区段224。接触件226将金属级1(M1)金属区段224连接到金属级3(M2)区段228。接触件230将金属级2(M2)金属区段228连接到用作图3中的位线BL0 22-1b的金属级3(M3)区段142。

再次参见图4A和图4B,在ReRAM存储器单元12c中,金属级0(M0)区段232通过图4B所示的接触件234连接到翅片组122e的部分,该部分形成FinFET晶体管16c的漏极。接触件236将M0区段234连接到金属级1(M1)区段238。接触件240将M1区段238连接到ReRAM器件14c的固体电解质层242。ReRAM器件14c的离子源层244通过接触件248连接到金属级2(M2)区段246。如参考图4C将更容易看到的,金属级2(M2)区段246在翅片区域124e处将ReRAM器件14c的离子源层244连接到晶体管18c的源极。

如图4A和图4C所见,金属级2(M2)区段246的另一端通过接触件252连接到金属级1(M1)区段250。金属级1(M1)区段250通过接触件256连接到金属级0(M0)区段254。金属级0(M0)区段254通过接触件258连接到翅片组124e的部分,该部分形成FinFET晶体管18c的漏极。

再次参见图4A和图4B,在ReRAM存储器单元12c中,金属级0(M0)区段260通过图4B所示的接触件262连接到翅片组122f的部分,该部分形成FinFET晶体管16c的漏极。接触件264将M0区段260连接到金属级1(M1)区段266。接触件268将M1区段266连接到金属级2(M2)区段270。接触件272将金属级2(M2)金属区段270连接到用作图3中的位线BL0 22-1a的金属级3(M3)区段140。

形成在翅片组126和128上并连接到位线144和146的ReRAM存储器单元14d、14e和14f以与恰好针对ReRAM存储器单元14a、14b和14c所述完全相同的方式连接。

表1示出了施加到从ReRAM单元到图3的ReRAM存储器单元12b中的编程、擦除和读取ReRAM器件14b的各种连接的操作电压。图3中的其他ReRAM存储器单元在表1中被示出为未被选择。在读取模式中,根据一个读取步骤,将位线BL0A预充电至电压诸如0.2V,并且检测在位线BL0A中流动的电流I

本领域的普通技术人员将观察到,可同时编程、擦除或读取图3阵列的行中的多于一个ReRAM存储器单元。例如,如果位线BL1 22-2a和位线BL1A 22-2b分别与位线BL1 22-1a和位线BL1A 22-1b偏置相同,则ReRAM存储器单元12h中的ReRAM器件14h可以与ReRAM存储器单元12b中的ReRAM器件14b同时编程。

本发明的ReRAM单元和阵列的优点在于它消除了对如在采用FinFET晶体管器件的现有技术ReRAM存储器单元中的虚拟栅极电极的需要。从图3和表1可以观察到的另一个优点是无论ReRAM单元是正被编程还是正被擦除,n沟道FinFET晶体管器件16或18中的一者都作为公共源极设备连接。这提供了以下优点:公共源极晶体管可以通过位线的电容或通过位线从电源来限制通过ReRAM器件提供的电流,并且编程和擦除电路路径是对称的。因此,编程和擦除均得到很好的控制。该优点是以阵列的每个列需要两个翅片组为代价的,但是提供两个翅片组减小了总体位线电阻,从而允许针对给定位线宽度传送更多电流。

现在参见图5,框图示出了根据本发明的一个方面的典型ReRAM存储器阵列系统以及相关联的读取、写入和擦除控制电路。ReRAM存储器阵列系统280包括经由位线286驱动感测放大器电路284的ReRAM存储器阵列282。感测放大器电路可为任何类型的感测放大器电路,这取决于ReRAM存储器阵列282的读取模式操作期间位线286上存在的输出电压/电流。特定感测放大器电路的设计完全在本领域普通技术人员的范围内。感测放大器的输出呈现在输出线288上。

由编程/擦除/读取偏置生成电路290控制读取、编程(写入)和擦除ReRAM存储器阵列282中的存储器单元。编程/擦除/读取偏置生成电路290生成表1所示的电势,以操作ReRAM存储器阵列282的编程、擦除和读取模式。特定电路的设计将取决于所需的特定电势,并且完全在本领域的普通技术人员水平之内。操作ReRAM存储器阵列282的编程、擦除和读取模式所需的电势被驱动到ReRAM存储器阵列282中,以通过字线驱动器292、偏置线驱动器294和位线驱动器296操作ReRAM存储器阵列282的编程、擦除和读取模式。字线驱动器、偏置线驱动器和位线驱动器电路在本领域中是已知的,并且这些电路的特定实例容易被设计用于具有特定电压和电流要求的特定ReRAM存储器阵列。

编程/擦除控制器298通过以本领域已知的方式提供定时和其他控制来通过控制线300引导编程/擦除/读取偏置生成电路290的操作。本领域技术人员将理解,通过在禁用线302上断言来自编程/擦除控制器298的信号来在编程和擦除操作期间禁用感测放大器284。

虽然已经示出和描述了本发明的实施方案和应用,但是对于本领域技术人员来说显而易见的是,在不脱离本文的发明构思的情况下,可以进行比上述更多的修改。因此,除了所附权利要求的实质之外,本发明不受限制。

- 用于每列具有两个位线的电阻式随机存取存储器阵列的电路和布局

- 用于电阻式随机存取存储器阵列的电路和布局