串行存储器数据读取频率设置方法

文献发布时间:2023-06-19 10:00:31

技术领域

本发明涉及存储器技术,特别涉及一种串行存储器数据读取频率设置方法。

背景技术

在串行存储器的应用中,由于设计读取速度越来越高,频率越来越快,存储器操作系统读取数据的频率和存储器PIN(引脚)的寄生电容电阻以及电感都有相关性。而且,在不同电压和温度条件下,数据输出频率也是不相同的。为了能提高存储器操作系统的存储器读频率,用户一般不会在一个固定时间内抓取数据,而是根据存储器封装的实际环境,先预测试读取数据0和1的速度,然后据此速度来读取数据,从而提高了读取数据的灵活性,增加了系统的传输频率。

在传统的串行存储器设计中,读取存储器的数据的顺序一般是:下读取数据命令,下读取数据地址,等待n个dummy(等待)时钟,然后在时钟下降沿或上升沿输出数据。

为了预测试读取数据0和1的速度,一般在等待n个dummy时钟的时候,预测试读取数据0和1的频率,这样用户可以拿预定模式数据和读取的数据进行比对,并能够动态调节读出数据所需的时间,并在实际读出数据时以此能够准确读出数据所需的最短时间为依据,再增加一点读出数据的冗余时间,就可以在最快频率下读取数据。

现有的串行存储器数据读取频率设置方法,是在存储器内的只读存储区预存模式数据,由于模式数据是存储在只读存储区,存储器操作系统不能更改,这样存储器操作系统预测试时读到的模式数据(数据类型)是固定的,并不能覆盖全部的可能用到的所有模式数据,由于数据的前后关系也会影响到数据输出的频率,所以根据预测试确定的存储器数据读取频率进行实际存储器数据读取,会存在一定的错误读取风险。

发明内容

本发明要解决的技术问题是提供一种串行存储器数据读取频率设置方法,用户可以自己通过存储器操作系统自由配置模式数据,大大降低了实际存储器数据读取时的错误读取风险。

为解决上述技术问题,本发明提供串行存储器数据读取频率设置方法,存储器中设置有测试存储区及主存储区;

所述测试存储区为可读可写,用于预存模式数据;

所述主存储区为可读可写;

存储器操作系统设置有测试存储区写指令及主存储区写指令,测试存储区写指令、主存储区写指令为两种不同的指令;

存储器操作系统向存储器发出测试存储区写指令及模式数据时,将模式数据更新写入到测试存储区;

存储器操作系统向主存储区发出主存储区读指令及存储地址时,在等待时钟期间内,在时钟下降沿或上升沿从测试存储区读出模式数据,在等待时钟期间后,在时钟下降沿或上升沿从主存储区的相应存储地址的存储单元读出主存数据;

包括以下步骤:

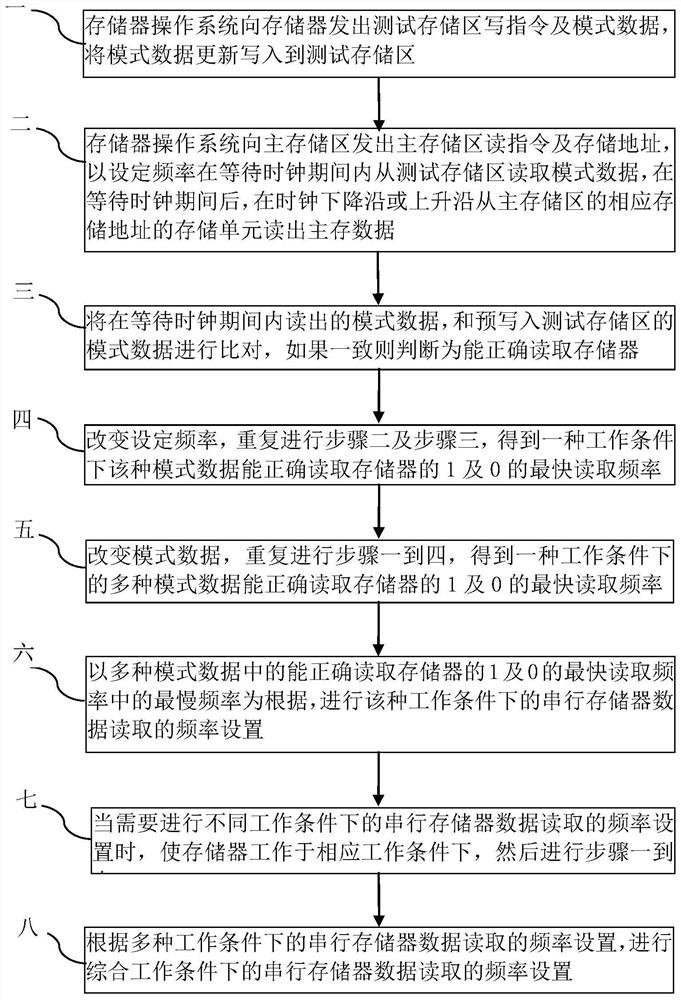

一.存储器操作系统向存储器发出测试存储区写指令及模式数据,将模式数据更新写入到测试存储区;

二.存储器操作系统向主存储区发出主存储区读指令及存储地址,以设定频率在等待时钟期间内从测试存储区读取模式数据,在等待时钟期间后,在时钟下降沿或上升沿从主存储区的相应存储地址的存储单元读出主存数据;

三.将在等待时钟期间内读出的模式数据,和预写入测试存储区的模式数据进行比对,如果一致则判断为能正确读取存储器;

四.改变设定频率,重复进行步骤二及步骤三,得到一种工作条件下该种模式数据能正确读取存储器的1及0的最快读取频率;

五.改变模式数据,重复进行步骤一到四,得到一种工作条件下的多种模式数据能正确读取存储器的1及0的最快读取频率;

六.以多种模式数据中的能正确读取存储器的1及0的最快读取频率中的最慢频率为根据,进行该种工作条件下的串行存储器数据读取的频率设置。

较佳的,当需要进行不同工作条件下的串行存储器数据读取的频率设置时,使存储器工作于相应工作条件下,然后进行步骤一到六。

较佳的,根据多种工作条件下的串行存储器数据读取的频率设置,进行综合工作条件下的串行存储器数据读取的频率设置。

较佳的,所述工作条件包括工作电压、环境温度、负载中的至少一种。

较佳的,存储器操作系统还设置有测试存储区读指令;

存储器操作系统对测试存储区进行读写时,为保护1线读写,通过存储器芯片的一串行输入引脚输入测试存储区读指令或测试存储区写指令,通过存储器芯片的一串行输出引脚输出读取数据。

较佳的,存储器操作系统还设置有测试存储区读指令;

存储器操作系统对测试存储区进行读写时,为保护2线读写,通过存储器芯片的一串行输入引脚及一串行输出引脚输入测试存储区读指令或测试存储区写指令,通过存储器芯片的一串行输入引脚及一串行输出引脚输出读取数据。

较佳的,存储器操作系统还设置有测试存储区读指令;

存储器操作系统对测试存储区进行读写时,为保护4线读写,通过存储器芯片的一串行输入引脚及一串行输出引脚输入测试存储区读指令或测试存储区写指令,通过存储器芯片的四个串行输出引脚输出读取数据。

较佳的,存储器操作系统还设置有测试存储区读指令;

存储器操作系统对测试存储区进行读写时,为保护8线读写,通过存储器芯片的一串行输入引脚及一串行输处引脚输入测试存储区读指令或测试存储区写指令,通过存储器芯片的八个串行输出引脚输出读取数据。

较佳的,所述测试存储区,为挥发存储单元区或非挥发存储单元区。

本发明的串行存储器数据读取频率设置方法,用户能够通过存储器操作系统更新模式数据,能够得到一种工作条件下的多种模式数据下的能正确读取存储器的1及0的最快读取频率,从而能以多种模式数据中的能正确读取存储器的1及0的最快读取频率中的最慢频率为根据,进行该种工作条件下的串行存储器数据读取的频率设置,得到该种工作条件下各种模式数据均能保证存储器数据正确读取的最快串行存储器数据读取频率,用户可以自己通过存储器操作系统自由配置模式数据,大大降低了实际存储器数据读取时的错误读取风险。

附图说明

为了更清楚地说明本发明的技术方案,下面对本发明所需要使用的附图作简单的介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1是本发明的串行存储器数据读取频率设置方法一实施例流程示意图。

具体实施方式

下面将结合附图,对本发明中的技术方案进行清楚、完整的描述,显然,所描述的实施例是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动的前提下所获得的所有其它实施例,都属于本发明保护的范围。

实施例一

串行存储器数据读取频率设置方法,存储器中设置有测试存储区及主存储区;

所述测试存储区为可读可写,用于预存模式数据;

所述主存储区为可读可写;

存储器操作系统设置有测试存储区写指令及主存储区写指令,测试存储区写指令、主存储区写指令为两种不同的指令;

存储器操作系统向存储器发出测试存储区写指令及模式数据时,将模式数据更新写入到测试存储区;

存储器操作系统向主存储区发出主存储区读指令及存储地址时,在dummy(等待)时钟期间内,在时钟下降沿或上升沿从测试存储区读出模式数据,在dummy(等待)时钟期间后,在时钟下降沿或上升沿从主存储区的相应存储地址的存储单元读出主存数据;

包括以下步骤:

一.存储器操作系统向存储器发出测试存储区写指令及模式数据,将模式数据更新写入到测试存储区;

二.存储器操作系统向主存储区发出主存储区读指令及存储地址,以设定频率在dummy(等待)时钟期间内从测试存储区读取模式数据,在dummy(等待)时钟期间后,在时钟下降沿或上升沿从主存储区的相应存储地址的存储单元读出主存数据;

三.将在dummy(等待)时钟期间内读出的模式数据,和预写入测试存储区的模式数据进行比对,如果一致则判断为能正确读取存储器;

四.改变设定频率,重复进行步骤二及步骤三,得到一种工作条件下该种模式数据能正确读取存储器的1及0的最快读取频率;

五.改变模式数据,重复进行步骤一到四,得到一种工作条件下的多种模式数据能正确读取存储器的1及0的最快读取频率;

六.以多种模式数据中的能正确读取存储器的1及0的最快读取频率中的最慢频率为根据,进行该种工作条件下的串行存储器数据读取的频率设置。

较佳的,当需要进行不同工作条件下的串行存储器数据读取的频率设置时,使存储器工作于相应工作条件下,然后进行步骤一到六。

较佳的,根据多种工作条件下的串行存储器数据读取的频率设置,进行综合工作条件下的串行存储器数据读取的频率设置。

较佳的,所述工作条件包括工作电压、环境温度、负载中的至少一种。

实施例一的串行存储器数据读取频率设置方法,用户能够通过存储器操作系统更新模式数据,能够得到一种工作条件下的多种模式数据下的能正确读取存储器的1及0的最快读取频率,从而能以多种模式数据中的能正确读取存储器的1及0的最快读取频率中的最慢频率为根据,进行该种工作条件下的串行存储器数据读取的频率设置,得到该种工作条件下各种模式数据均能保证存储器数据正确读取的最快串行存储器数据读取频率,用户可以自己通过存储器操作系统自由配置模式数据,大大降低了实际存储器数据读取时的错误读取风险。

实施例二

基于实施一的串行存储器数据读取频率设置方法,存储器操作系统还设置有测试存储区读指令;

存储器操作系统对测试存储区进行读写时,为保护1线读写,通过存储器芯片的一串行输入引脚(SI PIN)输入测试存储区读指令或测试存储区写指令,通过存储器芯片的一串行输出引脚(SO PIN)输出读取数据。

实施例三

基于实施一的串行存储器数据读取频率设置方法,存储器操作系统还设置有测试存储区读指令;

存储器操作系统对测试存储区进行读写时,为保护2线读写,通过存储器芯片的一串行输入引脚(SI PIN)及一串行输出引脚(SO PIN)输入测试存储区读指令或测试存储区写指令,通过存储器芯片的一串行输入引脚(SI PIN)及一串行输出引脚(SO PIN)输出读取数据。

实施例四

基于实施一的串行存储器数据读取频率设置方法,存储器操作系统还设置有测试存储区读指令;

存储器操作系统对测试存储区进行读写时,为保护4线读写,通过存储器芯片的一串行输入引脚(SI PIN)及一串行输出引脚(SO PIN)输入测试存储区读指令或测试存储区写指令,通过存储器芯片的四个串行输出引脚(SO PIN)输出读取数据。

实施例五

基于实施一的串行存储器数据读取频率设置方法,存储器操作系统还设置有测试存储区读指令;

存储器操作系统对测试存储区进行读写时,为保护8线读写,通过存储器芯片的一串行输入引脚(SI PIN)及一串行输出引脚(SO PIN)输入测试存储区读指令或测试存储区写指令,通过存储器芯片的八个串行输出引脚(SO PIN)输出读取数据。

实施例六

基于实施一的串行存储器数据读取频率设置方法,所述测试存储区,为挥发存储单元区(掉电数据消失)或非挥发存储单元区。

以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明保护的范围之内。

- 串行存储器数据读取频率设置方法

- 数据读取方法、存储器控制电路单元及存储器储存装置