图像传感器的图像数据读取系统及读取与组织的方法

文献发布时间:2023-06-19 11:21:00

技术领域

本发明涉及一种图像传感器的图像数据读取系统,本发明还涉及一种图像传感器的图像数据读取与组织的方法,属于图像传感器技术领域。

背景技术

图像传感器是一种被广泛应用于机器视觉、目标侦察、安防监控和医疗检测的光电成像器件,由于具有成本低,集成度高的优势,图像传感器芯片能够集成更多相机系统功能,从而减少相机的外围电路,实现了相机体积微型化和功能多样化。

目标侦察中,为了实现快速成像和重点目标的监视跟踪,相机先进行次采样模式,待发现目标后进入开窗扫描跟踪模式,只对像素阵列中设定的区域内的行、列像素进行扫描,捕获目标物的精确图像。

而随着技术的发展,图像传感器所含像素数量目前已可达千万像素及X亿像素,如此大像素的图像传感器应用于目标侦察时,根据目标位置变化,需要快速动态调整窗口位置,捕获目标,而有时需要捕获多个目标,这时就需要在每一帧图像中,动态获取多个选定范围内的列像素,而目前没有针对高帧率X亿级像素图像传感器的动态开窗解决方案,且现有的方法应用于高帧率X亿级像素传感器时若并行截取列像素数据,则会增加电路规模,后端布线资源紧张,若串行截取列像素数据则会降低帧率,无法高帧率动态追踪目标。

发明内容

本发明的首要目的在于,克服现有技术中存在的问题,提供一种图像传感器的图像数据读取系统,可实现降低电路规模,减轻后端工程师的压力并且能够兼容全像素、次采样与动态开窗读取。

为了解决上述问题,本发明提供一种图像传感器的图像数据读取系统,包括像素阵列、像素阵列控制单元、系统控制模块、掩码产生模块和数据重组模块,所述像素阵列控制单元包括列地址控制模块、行地址控制模块和像素数据读取模块;所述系统控制模块通过SPI端口接收指令,所述系统控制模块的输出端与像素阵列控制单元的输入端相连,所述列地址控制模块的输出端与像素阵列中的列选择电路相连,所述行地址控制模块的输出端与像素阵列中的行选择电路相连,所述像素阵列中的像素数据通过所述像素数据读取模块与数据重组模块的输入端相连;所述系统控制模块的输出端通过掩码产生模块与数据重组模块的输入端相连,所述数据重组模块通过接口输出重组后的数据。

本发明的有益效果是:1、可以在图像的帧与帧之间高频率的切换需要读取的列像素范围;

2、将图像分割成n个部分并行处理,降低了电路规模,缩小了后端布线的空间,减轻了后端布线的压力;

3、兼容全像素、多次采样与动态开窗读取。

本发明的另一个目的在于,克服现有技术中存在的问题,提供一种图像传感器的图像数据读取与组织的方法,可实现降低电路规模,减轻后端工程师的压力并且能够兼容全像素、次采样与动态开窗读取。

为了解决上述问题,本发明还提供一种图像传感器的图像数据读取与组织的方法,依次包括以下步骤:

步骤1:在每一帧起始更新得到像素掩码M,像素掩码每个bit对应一行中一个像素数据,根据需求将像素掩码平均分为n个部分,每个部分有M/n个bit像素掩码,n为大于1的整数;

步骤2:等待一行曝光结束,得到一行像素数据D,将像素数据D映射分割为n个部分,与步骤1的像素掩码相对应,像素数据D中的n个部分相互间以同样的流程并行处理;

步骤3:针对分割后的每一部分像素数据,选取一个可容纳多个像素的缓存寄存器R作为缓存;

步骤4:判断像素掩码值是否为1,若像素掩码值为0,则将该像素掩码值对应的像素数据丢弃;若像素掩码值为1,进入步骤5;

步骤5:将步骤4中所述的像素掩码值对应的像素数据放入缓存寄存器R中,拼接有效像素数据;

步骤6:判断缓存寄存器R是否放满,如果缓存寄存器R没有放满,则继续处理下一个像素数据;如果缓存寄存器R放满,即像素数据已拼接为固定位宽时,将拼接有效像素数据写入数据队列中;

当所有像素数据处理完时,无论缓存寄存器是否放满,将所拼接的有效像素数据写入数据队列中;

步骤7:当所有像素数据处理完时,将n个部分的像素数据同时写入至数据队列中的数据依次读取出;

步骤8:重复步骤2-7直至处理完一帧;

步骤9:重复步骤1-8,直到图像停止曝光。

进一步的,所述数据队列为fifo数据队列。

本发明的有益效果是:1、可以在图像的帧与帧之间高频率的切换需要读取的列像素范围;

2、将图像分割成n个部分并行处理,降低了电路规模,缩小了后端布线的空间,减轻了后端布线的压力;

3、兼容全像素、多次采样与动态开窗读取。

附图说明

图1为本发明图像传感器的图像数据读取系统的示意图;

图2为图1中像素数据读取、掩码产生和缓存寄存器的示意图;

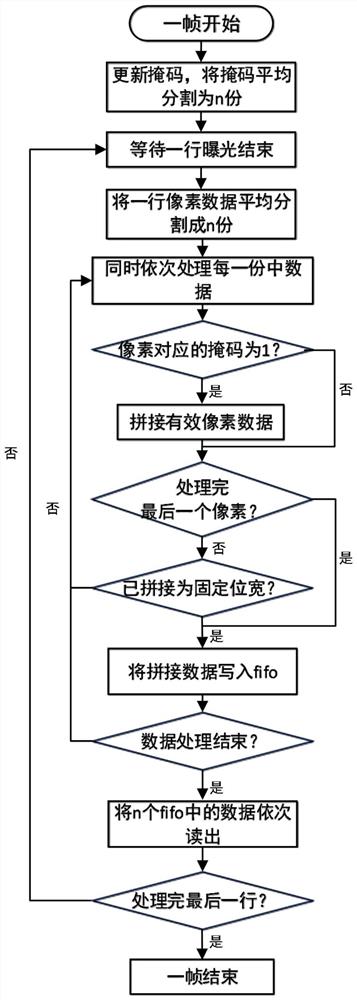

图3为图像传感器的图像数据读取与组织的方法的流程图;

图4为本发明中数据处理结束依次输出的示意图。

具体实施方式

现在结合附图对本发明作进一步详细的说明。这些附图均为简化的示意图,仅以示意方式说明本发明的基本结构,因此其仅显示与本发明有关的构成。

如图1所示,本发明的图像传感器的图像数据读取系统包括像素阵列、像素阵列控制单元、系统控制模块、掩码产生模块和数据重组模块,像素阵列控制单元包括列地址控制模块、行地址控制模块和像素数据读取模块;系统控制模块通过SPI端口接收指令,系统控制模块的输出端与像素阵列控制单元的输入端相连,列地址控制模块的输出端与像素阵列中的列选择电路相连,行地址控制模块的输出端与像素阵列中的行选择电路相连,像素阵列中的像素数据通过像素数据读取模块与数据重组模块的输入端相连;系统控制模块的输出端通过掩码产生模块与数据重组模块的输入端相连,数据重组模块通过接口输出重组后的数据。

工程师通过SPI端口向系统控制模块发送图像处理指令,系统控制模块控制掩码产生模块生成像素掩码,同时系统控制模块通过像素阵列控制单元中的列地址控制模块控制像素阵列的列选择电路,通过像素阵列单元中的行地址控制模块控制像素阵列的行选择电路,列选择电路接收列地址控制模块发布的指令,选择对应列地址的像素数据并输出;行选择电路接收行地址控制模块发布的指令,选择对应行地址的像素数据并输出,像素阵列输出的像素数据通过像素数据读取模块读出后与像素掩码进行重组,经过重组后的像素数据通过接口输出传送给工程师进行下一步处理。

如图2至图4所示,本发明的图像传感器的图像数据读取与组织的方法,依次包括以下步骤:

步骤1:在每一帧起始更新得到像素掩码M,像素掩码每个bit对应一行中一个像素数据,根据需求将像素掩码平均分为n个部分,每个部分有M/n个bit像素掩码,n为大于1的整数;

步骤2:等待一行曝光结束,得到一行像素数据D,将像素数据D映射分割为n个部分,与步骤1的像素掩码相对应,像素数据D中的n个部分相互间以同样的流程并行处理;

步骤3:针对分割后的每一部分像素数据,选取一个可容纳多个像素的缓存寄存器R作为缓存;如图2所示,当处理一行18个像素的图像时,将像素掩码平均分为2个部分,即每个部分有9bit像素掩码,将一行像素数据D分割为2个部分,每个部分选取一个缓存寄存器R,每个缓存寄存器R可以容纳3个像素数据,像素掩码值为9’h193的二进制数值;

步骤4:判断像素掩码值是否为1,若像素掩码值为0,则将该像素掩码值对应的像素数据丢弃;若像素掩码值为1,进入步骤5;

步骤5:将步骤4中所述的像素掩码值对应的像素数据放入缓存寄存器R中,拼接有效像素数据;

步骤6:判断缓存寄存器R是否放满,如果缓存寄存器R没有放满,则继续处理下一个像素数据;如果缓存寄存器R放满,即像素数据已拼接为固定位宽时,将拼接有效像素数据写入数据队列中;

当所有像素数据处理完时,无论缓存寄存器是否放满,将所拼接的有效像素数据写入数据队列中;

步骤7:当所有像素数据处理完时,将n个部分的像素数据同时写入至数据队列中的数据依次读取出;如图4所示,如像素数据P0对应的掩码值为1,则放入缓存寄存器,像素数据P3对应的掩码值为0,则丢弃,当像素数据P0、P1、P4放满缓存寄存器时,将缓存寄存器写入fifo队列中,清空缓存寄存器,当像素数据P7与P8放入缓存寄存器时,虽然缓存寄存器没满,但像素数据已全部被处理,则将此时的缓存寄存器写入fifo队列中,在第一部分工作的同时,第二部分按照相同的流程在并行工作;

步骤8:重复步骤2-7直至处理完一帧;

步骤9:重复步骤1-8,直到图像停止曝光。

以上述依据本发明的理想实施例为启示,通过上述的说明内容,相关工作人员完全可以在不偏离本项发明技术思想的范围内,进行多样的变更以及修改。本项发明的技术性范围并不局限于说明书上的内容,必须要根据权利要求范围来确定其技术性范围。

- 图像传感器的图像数据读取系统及读取与组织的方法

- 图像传感器的图像数据读取方法