一种存储器的纠错方法及装置

文献发布时间:2023-06-19 11:57:35

技术领域

本发明涉及半导体器件及其制造领域,特别涉及一种存储器的纠错方法及装置。

背景技术

半导体存储器件的特点可为易失性的或非易失性的,尽管易失性半导体存储器件可以高速执行读取操作和写入操作,但是在断电状态下存储在易失性半导体存储器件中的内容会丢失。相反,非易失性半导体存储器件的特点是无论是否加电均保留存储的内容。闪存器件(Flash memory)是典型的非易失性半导体存储器件的示例,闪存器件可以被广泛地用作数据存储介质。

在NAND Flash存储器件中,可以在浮栅或电荷俘获层中注入不同数量的电子可以得到不同的阈值电压,从而表示不同的逻辑态,以双层单元(Multi-Level Cell,MLC)NANDFlash为例,在读取数据时,通过在栅极施加3个不同的读取电压,来区分四个逻辑态。

然而存储单元的阈值电压通常随着存储器件的特性、时间的流逝和/或外围温度而变化,举例来说,参考图1所示,浮栅或电荷俘获层中的电子会随着时间的增加逐渐流失,使存储单元的阈值电压减小,当存储单元的阈值电压从高于相对应的读取电压减小到低于相对应的读取电压的电压,将会导致存储单元产生读取错误,称为数据保持错误(dataretention error),数据保持错误会随着存储时间的增加逐渐增多。差错控制编码(ErrorCorrecting Code,ECC)可以纠正读出数据的错误,是保证写入数据和读出数据的一致性,提高存储系统可靠性的重要手段。但ECC也有一定的纠错范围,如果读出数据的原始误码率较高,将会超出差错控制编码的纠错能力,无法正确的恢复出写入的数据。

参考图2所示,为目前一种数据存储示意图,横坐标为阈值电压(threholdvoltage),纵坐标为存储单元的数量,图中以E、P1、P2、P3态为例进行说明,实线表示数据写入到闪存中的零时刻存储单元的阈值电压所形成的初始阈值电压分布态,虚线表示经过一段存储时间后闪存的阈值电压分布态,从图中可以看出,经过一段存储时间后,由于存储单元所保持的电荷泄漏,导致闪存的阈值电压分布态向阈值电压较小的一侧偏移,即分布态左移,如果这时候使用数据写入零时刻所使用的读电压Vread1、Vread2、Vread3对闪存进行读操作,将会导致读出数据的误码率较高。很有可能无法通过ECC校验,无法得到正确的存储数据。

数据保持错误是NAND Flash数据错误中最主要的成分,对NAND Flash可靠性影响最大,数据存储后最终能够被正确读出时所对应的最长存储时间成为数据保持(dataretention)时间,如何延长data retention时间,降低数据保持错误是本领域重要的研究方向。

此外,在读取NAND Flash中某个存储单元的数据时,会向这个单元(cell)的所在串(string)上的其他单元栅极施加一个大于单元所有阈值电压的导通电压,使单元处于导通态。由于导通电压较高,将会导致存储单元阈值电压增大,造成数据读取错误,称为readdisturb(读干扰)。

参见图3所示,图中阴影部分为受到读干扰的存储单元,参见图4所示,较高的导通电压会向这些单元内注入电子,单次读干扰所造成的干扰效应很小,对NAND Flash可靠性造成的影响较小,但每次读干扰都会积累下来,当经历几万次读操作后,读干扰效应将变的显著,参见图5所示,为目前一种数据存储示意图,横坐标为阈值电压(threhold voltage),纵坐标为存储单元的数量,图中以E、P1、P2、P3态为例进行说明,实线表示数据写入到闪存中的零时刻存储单元的阈值电压所形成的初始阈值电压分布态,虚线表示经过几万次读干扰后闪存的阈值电压分布态,从图中可以看出,由于每次读取存储单元中的数据时,较高的导通电压会向这些存储单元中注入电子,导致闪存的阈值电压分布态向阈值电压较大的一侧偏移,即分布态右移,如果这时候使用数据写入零时刻所使用的读电压Vread1、Vread2、Vread3对闪存进行读操作,会造成数据读取错误。

因此,如何减少存储器中的数据读干扰错误和数据保持错误,且不降低NANDFlash的性能和可靠性,是本领域亟待解决的技术问题。

发明内容

有鉴于此,本申请的目的在于提供一种存储器的纠错方法及装置,可以同时减少存储器中的数据读干扰和数据保持错误,且不降低存储器的可靠性和性能。

为实现上述目的,本申请有如下技术方案:

第一方面,本申请提供了一种存储器的纠错方法,包括:

当检测到存储块的存储时长大于或等于第一预设时长时,或,所述存储块中的数据的误码率大于或等于第一预设阈值时,将所述存储块作为目标存储块;

将热数据对应的热数据存储页标为无效,以使所述热数据存储页不再被访问;所述热数据为读取频率大于或等于第一预设频率的数据;所述热数据存储页为存储所述热数据的存储页;

复制所述热数据向所述目标存储块中的空白存储页写入所述热数据。

可选的,所述向所述目标存储块中的空白存储页写入所述热数据,包括:

根据所述误码率从所述热数据中选择对应的目标热数据;

将所述目标热数据写入所述目标存储块中的空白存储页。

可选的,所述方法还包括:

将所述目标存储块的原导通电压增大为第一预设电压;

在读取所述目标存储块中的数据时,向所述目标存储块施加所述第一预设电压,以使所述目标存储块处于导通态。

可选的,所述目标热数据包括:

一个或多个目标热数据页;

所述目标热数据页为所述目标热数据对应的数据页;不同读取频率的目标热数据对应不同的目标热数据页。

可选的,所述将所述目标热数据写入所述目标存储块中的空白存储页,包括:

所述空白存储页包括多页;

在不同的数据存储时刻,向所述空白存储页写入一个或多个目标热数据页;或;在同一数据存储时刻,写入一个或多个目标热数据页。

第二方面,本申请提供了一种存储器的纠错装置,包括:

目标存储块确定单元,用于当检测到存储块的存储时长大于或等于第一预设时长时,或,所述存储块中的数据的误码率大于或等于第一预设阈值时,将所述存储块作为目标存储块;

热数据存储页无效单元,用于将热数据对应的热数据存储页标为无效,以使所述热数据存储页不再被访问;所述热数据为读取频率大于或等于第一预设频率的数据;所述热数据存储页为存储所述热数据的存储页;

热数据写入单元,用于复制所述热数据向所述目标存储块中的空白存储页写入所述热数据。

可选的,所述热数据写入单元,包括:

目标热数据选择单元,用于根据所述误码率从所述热数据中选择对应的目标热数据;

目标热数据写入单元,用于将所述目标热数据写入所述目标存储块中的空白存储页。

可选的,所述装置还包括:

电压增大单元,用于将所述目标存储块的原导通电压增大为第一预设电压;

电压施加单元,用于在读取所述目标存储块中的数据时,向所述目标存储块施加所述第一预设电压,以使所述目标存储块处于导通态。

可选的,所述目标热数据包括:

一个或多个目标热数据页;

所述目标热数据页为所述目标热数据对应的数据页;不同读取频率的目标热数据对应不同的目标热数据页。

可选的,所述目标热数据写入单元,包括:

目标热数据页写入单元,用于在不同的数据存储时刻,向所述空白存储页写入一个或多个目标热数据页;或;在同一数据存储时刻,写入一个或多个目标热数据页;所述空白存储页包括多页。

本申请实施例提供了一种存储器的纠错方法及装置,当检测到存储块的存储时长大于或等于第一预设时长时,或,存储块中的数据的误码率大于或等于第一预设阈值时,将存储块作为目标存储块,将热数据对应的热数据存储页标为无效,以使热数据存储页不再被访问,热数据为读取频率大于或等于第一预设频率的数据,热数据存储页为存储热数据的存储页。由于读取频率高的热数据产生的读干扰使目标存储块的阈值电压变大,可减轻由于数据保持错误导致的目标存储块的阈值电压变小,即减轻数据保持错误;同时由于热数据存储页被标为无效不被访问,可减轻热数据读取频率高而使热数据存储页的阈值电压变大带来的读干扰,即可同时减轻存储器的数据保持错误和数据读干扰错误。

附图说明

为了更清楚地说明本申请实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

图1为目前一种受到数据保持错误的存储器中的电子移动方向的示意图;

图2为目前一种受到数据保持错误的存储器的阈值电压的分布态的示意图;

图3为目前一种受到数据读干扰错误的存储单元的示意图;

图4为目前一种受到数据读干扰错误的存储器中的电子移动方向的示意图;

图5为目前一种受到数据读干扰错误的存储器的分布态的示意图;

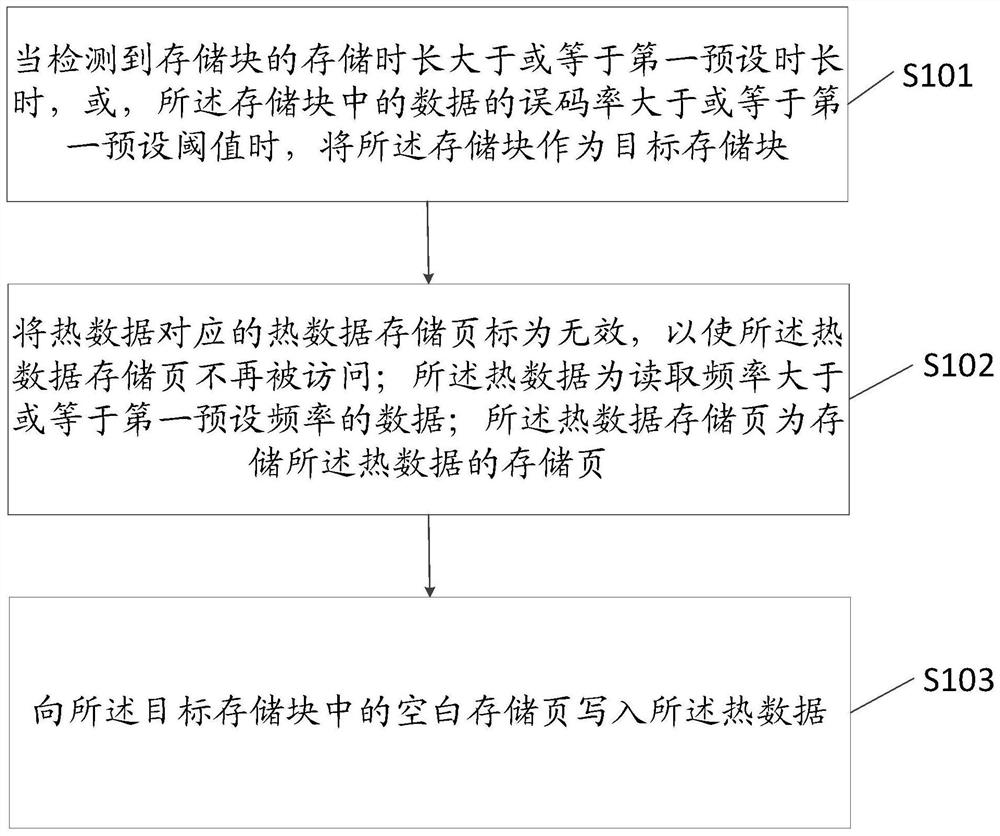

图6为本申请实施例提供的一种存储器纠错方法的流程图;

图7为本申请实施例提供的一种上层操作系统的逻辑页和底层NAND Flash的物理页的映射关系的示意图;

图8为本申请实施例提供的一种存储单元经历数据保持错误和数据读干扰错误后的阈值电压分布态的示意图;

图9为本申请实施例提供的一种存储器的纠错方法的逻辑表和物理表的映射关系的示意图;

图10为本申请实施例提供的一种经历多次数据保持错误恢复的数据存储时间和误码率对应的示意图;

图11为本申请实施例提供的一种存储器纠错装置的示意图。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

为了便于理解本申请实施例提供的读取方法,首先介绍本申请实施例的具体应用场景。非易失存储器包括多个以阵列排列的用于存储数据的存储单元。其中,存储单元分为若干个块(block),每个块又分为若干个页(page),对非易失性存储器的读写、验证、清除等操作均可以以页为单位进行。

非易失性存储器包括存储单元阵列、控制逻辑、页缓存器(Page Buffer,PB)、字线电压产生器和字线译码器,存储单元阵列中的每列存储单元通过一条位线(Bit Line,BL)连接页缓存器,每行存储单元的栅极通过一条字线(Word Line,WL)连接字线译码器。控制逻辑通过控制字线电压产生器和页缓存器。在进行读取操作时,控制逻辑通过控制字线电压产生器在选中的字线上施加读取电压,在未选中的字线上施加读通过电压后,控制页缓存器根据不同的读取操作方法对相应位线上存储单元存储的数据进行感测,从而读取出非易失性存储器存储的数据。

非易失性存储器主要分为SLC(Single-Level Cell)、MLC(Milti-Level Cell)、TLC(Trinary-Level Cell)、QLC(Quad-Level Cell)等多种类型,SLC即1bit/cell,每个存储单元存储1比特数据,存储单元只存在两种存储状态:“0”和“1”。MLC,即2bit/cell,每个存储单元存储2比特数据,存储单元存在四种存储状态:“00”、“01”、“10”、“11”。TLC,即3bit/cell,每个存储单元存储3比特数据,存储单元存在八种存储状态:“000”、“001”、“010”、“011”、“100”、“101”、“110”、“111”。可以理解非易失性存储器的存储单元也可以存储多余3比特数据。QLC,即4bit/cell,每个存储单元存储4比特数据,存储单元存在16中存储状态:“0000”、“0001”、“0010”、“0011”、“0100”、“0101”、“0110”、“0111”、“1000”、“1001”、“1010”、“1011”、“1100”、“1101”、“1110”、“1111”。

为了确定存储单元的存储状态,从而读出其存储的数据,对SLC型的非易失性存储器而言,在选中的字线上执行一次读取操作在字线上施加一次读取电压后感测数据,即可将对应的存储单元中存储的数据读出。但对于MLC和TLC等每存储单元存储多比特数据的非易失性存储器而言,由于每个存储单元的存储状态不止两种,因此需要对同一存储单元进行连续多次的读取操作在字线上施加多个不同大小的读取电压后感测存储的数据,才可以确定存储单元的实际存储状态,将该非易失性存储器存储的数据读出。

然而在数据存储过程中,当数据在闪存中存储一段时间后,存储在存储单元的电荷将会泄露,闪存中的阈值电压分布态将会向阈值电压较小的一侧偏移,如果使用在数据存储初期使用的读电压进行读取操作,将会出现读出数据的误码率较高,甚至超过ECC纠错能力的问题。

数据存储后最终能够被正确读出时所对应的最长存储时间称为数据保持(dataretention)时间,如何延长data retention时间,是本领域重要的研究方向。数据恢复技术是指通过对cell充入电子,使其阈值分布右移从而使误码降低到ECC纠错范围以内,从而正确解码的技术,但ECC也有一定的纠错范围,如果读出数据的原始误码率较高,将会超出差错控制编码的纠错能力,无法正确的恢复出写入的数据。

参考图2所示,为目前一种数据存储示意图,横坐标为阈值电压(threholdvoltage),纵坐标为存储单元的数量,图中以E、P1、P2、P3态为例进行说明,实线表示数据写入到闪存中的零时刻存储单元的阈值电压所形成的初始阈值电压分布态,虚线表示经过一段存储时间后闪存的阈值电压分布态,从图中可以看出,经过一段存储时间后,由于存储单元所保持的电荷泄漏,导致闪存的阈值电压分布态向阈值电压较小的一侧偏移,即分布态左移,如果这时候使用数据写入零时刻所使用的读电压Vread1、Vread2、Vread3对闪存进行读操作,将会导致读出数据的误码率较高。很有可能无法通过ECC校验,无法得到正确的存储数据。

数据保持错误是NAND Flash数据错误中最主要的成分,对NAND Flash可靠性影响最大,数据存储后最终能够被正确读出时所对应的最长存储时间成为数据保持(dataretention)时间,如何延长data retention时间,降低数据保持错误是本领域重要的研究方向。

此外,在读取NAND Flash中某个存储单元的数据时,会向这个单元(cell)的所在串(string)上的其他单元栅极施加一个大于单元所有阈值电压的导通电压,使单元处于导通态。由于导通电压较高,将会导致存储单元阈值电压增大,造成数据读取错误,称为readdisturb(读干扰)。

参见图3所示,图中阴影部分为受到读干扰的存储单元,参见图4所示,较高的导通电压会向这些单元内注入电子,单次读干扰所造成的干扰效应很小,对NAND Flash可靠性造成的影响较小,但每次读干扰都会积累下来,当经历几万次读操作后,读干扰效应将变的显著,参见图5所示,为目前一种数据存储示意图,横坐标为阈值电压(threhold voltage),纵坐标为存储单元的数量,图中以E、P1、P2、P3态为例进行说明,实线表示数据写入到闪存中的零时刻存储单元的阈值电压所形成的初始阈值电压分布态,虚线表示经过几万次读干扰后闪存的阈值电压分布态,从图中可以看出,由于每次读取存储单元中的数据时,较高的导通电压会向这些存储单元中注入电子,导致闪存的阈值电压分布态向阈值电压较大的一侧偏移,即分布态右移,如果这时候使用数据写入零时刻所使用的读电压Vread1、Vread2、Vread3对闪存进行读操作,会造成数据读取错误。

因此,如何减少存储器中的数据读干扰错误和数据保持错误,且不降低NANDFlash的性能和可靠性,是本领域亟待解决的技术问题。

基于以上技术问题,本申请提供了一种存储器的纠错方法及装置,当测到存储块的存储时长大于或等于第一预设时长时,或,存储块中的数据的误码率大于或等于第一预设阈值时,将存储块作为目标存储块,将热数据对应的热数据存储页标为无效,以使热数据存储页不再被访问,热数据为读取频率大于或等于第一预设频率的数据,热数据存储页为存储热数据的存储页。由于读取频率高的热数据产生的读干扰使目标存储块的阈值电压变大,可减轻由于数据保持错误导致的目标存储块的阈值电压变小,即减轻数据保持错误;同时由于热数据存储页被标为无效不被访问,可减轻热数据读取频率高而使热数据存储页的阈值电压变大带来的读干扰,即可同时减轻存储器的数据保持错误和数据读干扰错误。

基于以上思想,为使本申请的上述目的、特征、优点能够更加明显易懂,下面结合附图对本申请的具体实施方式进行详细说明。

首先,需要说明的是,本申请实施例提供的非易失性存储器的读取方法、装置及相关设备,不仅适用于NAND闪存存储器(2D,3D,MLC,TLC,QLC),还适用于磁阻存储器(Magnetoresistive Random Access Memory,MRAM)、相变存储器(Phase-Change RandomAccess Memory,PCRAM)、相变存储器和开关(Phase-Change Random Access Memory and aswitch,PCMS)、阻性存储器、铁电存储器(ferroelectric RAM,FRAM)、自旋转移转矩存储器(Spin Torque Transfer,STT)、热辅助的开关存储器(TAS)、千足虫存储器(Millipedememory)、浮动结栅存储器(FJG RAM)、电池备份RAM等其他非易失性存储器。该非易失性存储器中每个存储单元可存储3比特甚至更多数据。

参考图6所示,为本申请实施例提供的一种存储器的纠错方法的流程图,该方法可以包括:

S101,当检测到存储块的存储时长大于或等于第一预设时长时,或,所述存储块中的数据的误码率大于或等于第一预设阈值时,将所述存储块作为目标存储块。

在存储器中,通常来说,在一个块(block)中,每一层(layer)的存储单元的栅极通过一条字线连接字线译码器,构成一个页(page)。本申请实施例中,存储器可以为2D,3D,MLC、TLC、QLC中的一种,其存储单元具有多个阈值电压分布态。

因此,本申请实施例中,在对存储块进行写入时,可以预留一层空白页不写入数据,通常来说,可以预留一个存储块中最上层的一整层空白页,方便后续将热数据写入空白页中,以减轻存储块中的数据保持错误。

当检测到存储块的存储时长大于或等于第一预设时长时,或,存储块中的数据的误码率大于或等于第一预设阈值时,将存储块作为目标存储块。

具体来说,在NAND Flash中有些存储块数据擦写频繁,称为热数据存储块,热数据存储块中的数据由于读写操作频繁,读干扰效应显著;另一些存储块在存入数据后,很长时间不进行数据擦写,称为冷数据存储块。冷数据存储块中的数据存储时间较长,易出现数据保持错误。

因此,当检测到存储块的存储时间较长时,该存储块易出现数据保持错误,可以将该存储块作为目标存储块以便执行后续的存储器纠错方法,需要说明的是,第一预设时长根据不同的存储块可以有不同的设置,本申请实施例在此不作具体限定,可由本领域技术人员根据实际情况进行设定。

当检测到存储块中的数据的误码率已经大于或等于第一预设阈值时,说明该存储块中已经出现了数据保持错误,可以将该存储块作为目标存储块以便执行后续的存储器纠错方法,需要说明的是,第一预设阈值根据不同的存储块可以有不同的设置,本申请实施例在此不作具体限定,可由本领域技术人员根据实际情况进行设定。

S102:将热数据对应的热数据存储页标为无效,以使所述热数据存储页不再被访问;所述热数据为读取频率大于或等于第一预设频率的数据;所述热数据存储页为存储所述热数据的存储页;

在本申请实施例中,为了减少热数据存储页中的数据读干扰错误,首先可以将热数据对应的热数据存储页标为无效,以使热数据存储页不再被访问,从而该热数据页无法再进行读写擦操作,即减轻了热数据存储页的数据读干扰错误,存储器的数据读干扰错误因此被减轻。

具体来说,在读取NAND Flash中存储的数据时,有些数据的读取频率高,称为读热数据(read hot data),有些数据的读取频率低,称为读冷数据(read cold data),热数据为读取频率大于或等于第一预设频率的数据,相应的,存储热数据的存储页为热数据存储页。

可选的,上层操作系统以扇(sector)为最小操作单位,底层NAND Flash芯片以页(page)作为最小操作单位,所以需要在上层操作系统和底层NAND Flash之间建立一层转换层,称为FTL(Flash translation layer),转换层的功能包括实现逻辑页(logical page)和物理页(physical page)之间的相互映射。

具体的,上层操作系统能够访问到的页称为逻辑页,其地址为LPN(逻辑页码,logical page number),数据实际在NAND Flash中存储的页称为物理页,其地址为PPN(physical page number),当LPN对应的数据更新后,NAND Flash并不是直接更改PPN对应的数据,而是将该PPN标为无效(invalid),标为无效的PPN不会被访问到,将更新后的数据写到一个新的PPN,然后更新的LPN映射到相对应的新的PPN,实现了LPN和PPN的映射关系的更新,这个过程就称为逻辑页/物理页之间的相互映射。参见图7所示,为LPN和PPN之间的映射关系的示意图。

由于对非易失性存储器的读写、验证、清除等操作均可以以页为单位进行,因此,将热数据对应的热数据存储页标为无效,以使热数据存储页不再被访问。

首先,可选的,可以将所有符合条件的热数据页所对应的LPN放入一个表中,称为read hot page table(热数据页表),并根据LPN被读取次数的多少由大到小进行排序,以便后续进行数据保持错误恢复时取用。

在本申请实施例中,由于将热数据对应的热数据存储页标为无效,以使热数据存储页不再被访问,从而该热数据页无法再进行读写擦操作,即减轻了热数据存储页的数据读干扰错误,存储器的数据读干扰错误因此被减轻。

S103:复制所述热数据向所述目标存储块中的空白存储页写入所述热数据。

在现阶段,对数据保持错误积累较多的数据主要的处理方法是用ECC纠正后读出,写入到原位置或其他位置。这种方法会带来额外的读写擦操作,降低NAND Flash的性能;在现阶段,对数据读干扰错误积累较多的数据通常用ECC纠正后写入到原位置或其他位置,同样这种方法会带来额外的读写擦操作,降低NAND Flash的性能。

在本申请实施例中,为了减轻目标存储块中的数据保持错误,可以复制热数据并向目标存储块中的空白存储页写入热数据,由于热数据可以对整个目标存储块施加大量的读干扰,从而减轻了目标存储块中的数据保持错误。

需要说明的是,参见图8所示,数据保持错误表现为存储单元的阈值电压整体左移,而数据读干扰错误表现为存储单元的阈值电压整体右移。可以利用数据读干扰错误将因为数据保持错误左移的阈值电压移回一部分,从而恢复一部分数据保持错误。然而在利用数据读干扰错误来降低数据保持错误时,效果会逐渐减弱,当读取数据次数达到一定的阈值后,数据读干扰错误基本没有再继续减弱数据保持错误的效果。因此,对于数据保持错误严重的目标存储器,只能减轻其中的数据保持错误,而无法完全恢复其中的数据保持错误。

可选的,可以根据目标存储块中的误码率从热数据中选择对应的目标热数据,将目标热数据写入目标存储块中的空白存储页,以利用目标热数据的读干扰错误来恢复目标存储块中的数据保持错误。

具体的,可选的,可以根据误码率从热数据页表中选择对应的目标热数据页,将目标热数据页写入目标存储块中的空白存储页,当某个LPN被选中来恢复目标存储块中的数据保持错误时,将此LPN移出热数据页表,将该LPN对应的PPN标为无效,使该PPN无法被访问,并把这个PPN中的热数据写入空白存储页中,并更新LPN和PPN之间的映射关系,以利用目标热数据来恢复目标存储块中的数据保持错误。

举例来说,参见图9所示,当根据误码率选中LPN1来恢复目标存储块中的数据保持错误时,将LPN1移出热数据页表。将LPN1对应的PPN1标为无效(invalid),并把PPN1其中的热数据写入到空白存储页,新地址称为PPN,并把LPN1指向PPN。从而当进行读写操作时,可以利用热数据来恢复目标存储块中的数据保持错误。

此外,可选的,参见图9所示,还可以在目标存储块的数据保持错误恢复后,将PPN设为无效,将LPN重新指向PPN1。

在本申请的一个实施例中,还可以将目标存储块的原导通电压增大为第一预设电压,在读取目标存储块中的数据时,向目标存储块施加第一预设电压,以使目标存储块处于导通态。

由于增大导通电压可以增加数据读干扰错误,因此,适当的增加目标存储块的导通电压,增强读干扰效应,可以加快数据保持错误的恢复速度。

需要说明的是,本申请实施例在此不对第一预设电压作具体限定,可由本领域技术人员根据实际情况进行设定。

可选的,目标热数据可以包括一个或多个热数据页,以加快目标存储块的数据保持错误的恢复速度,目标热数据页为目标热数据页对应的数据页,不同读取频率的目标热数据对应不同的目标热数据页。即一个空白存储页可以存储多个热数据页,以便于加快数据保持错误的恢复速度。

举例来说,对于三阶单元存储器(TLC NAND Flash,Triple level cell NANDFlash)来说,包括low,middle,upper page三页,将这三页均写入热数据并写入目标存储块的空白存储页中,增加热数据的总读次数,增加数据读干扰,从而加快数据保持错误的恢复速度。

可选的,可以在对目标存储块进行写入时,预留多层空白存储页不写入,从而在不同的数据存储时刻,向空白存储页写入一个或多个目标热数据页,或在同一数据存储时刻,写入一个或多个目标热数据页。当写入目标热数据页后,等待对目标热数据的读写操作,以利用读干扰效应来减轻数据保持错误。

需要说明的是,根据存储器的不同,一个空白存储页中可以写入热数据页的多少也不同,例如TLC中的一个空白存储页最多可以写入三页热数据页。

举例来说,参见图10所示,可以通过在不同的数据存储时刻,向空白存储页中写入一个或多个目标存储页,从而利用多次数据恢复,延长数据保持时间,使误码率减小到ECC的可纠错范围内,从而实现对数据保持错误的恢复。

可选的,还可以在进行数据保持错误恢复的过程中,统计热数据页被读取的次数,当次数超过一定阈值后,读取此时的误码率,判断误码率是否减小到ECC的可纠错范围内,若达到,则停止进行数据保持错误的恢复,将目标存储块中的空白存储页设为无效,并将其中的热数据页复制到其他非冷数据页,若没有达到,则可以继续统计热数据页读取的次数,直到达到热数据页可以读取的次数的最大阈值。

本申请实施例提供了一种存储器的纠错方法,当测到存储块的存储时长大于或等于第一预设时长时,或,存储块中的数据的误码率大于或等于第一预设阈值时,将存储块作为目标存储块,将热数据对应的热数据存储页标为无效,以使热数据存储页不再被访问,热数据为读取频率大于或等于第一预设频率的数据,热数据存储页为存储热数据的存储页。由于读取频率高的热数据产生的读干扰使目标存储块的阈值电压变大,可减轻由于数据保持错误导致的目标存储块的阈值电压变小,即减轻数据保持错误;同时由于热数据存储页被标为无效不被访问,可减轻热数据读取频率高而使热数据存储页的阈值电压变大带来的读干扰,即可同时减轻存储器的数据保持错误和数据读干扰错误。

参见图11所示,为本申请实施例提供的一种存储器的纠错装置的示意图,包括:

目标存储块确定单元1101,用于当检测到存储块的存储时长大于或等于第一预设时长时,或,所述存储块中的数据的误码率大于或等于第一预设阈值时,将所述存储块作为目标存储块;

热数据存储页无效单元1102,用于将热数据对应的热数据存储页标为无效,以使所述热数据存储页不再被访问;所述热数据为读取频率大于或等于第一预设频率的数据;所述热数据存储页为存储所述热数据的存储页;

热数据写入单元1103,用于复制所述热数据向所述目标存储块中的空白存储页写入所述热数据。

可选的,所述热数据写入单元,包括:

目标热数据选择单元,用于根据所述误码率从所述热数据中选择对应的目标热数据;

目标热数据写入单元,用于将所述目标热数据写入所述目标存储块中的空白存储页。

可选的,所述装置还包括:

电压增大单元,用于将所述目标存储块的原导通电压增大为第一预设电压;

电压施加单元,用于在读取所述目标存储块中的数据时,向所述目标存储块施加所述第一预设电压,以使所述目标存储块处于导通态。

可选的,所述目标热数据包括:

一个或多个目标热数据页;

所述目标热数据页为所述目标热数据对应的数据页;不同读取频率的目标热数据对应不同的目标热数据页。

可选的,所述目标热数据写入单元,包括:

目标热数据页写入单元,用于在不同的数据存储时刻,向所述空白存储页写入一个或多个目标热数据页;或;在同一数据存储时刻,写入一个或多个目标热数据页;所述空白存储页包括多页。

本申请实施例提供了一种存储器的纠错装置,当测到存储块的存储时长大于或等于第一预设时长时,或,存储块中的数据的误码率大于或等于第一预设阈值时,将存储块作为目标存储块,将热数据对应的热数据存储页标为无效,以使热数据存储页不再被访问,热数据为读取频率大于或等于第一预设频率的数据,热数据存储页为存储热数据的存储页。由于读取频率高的热数据产生的读干扰使目标存储块的阈值电压变大,可减轻由于数据保持错误导致的目标存储块的阈值电压变小,即减轻数据保持错误;同时由于热数据存储页被标为无效不被访问,可减轻热数据读取频率高而使热数据存储页的阈值电压变大带来的读干扰,即可同时减轻存储器的数据保持错误和数据读干扰错误。

本说明书中的各个实施例均采用递进的方式描述,各个实施例之间相同相似的部分互相参见即可,每个实施例重点说明的都是与其他实施例的不同之处。尤其,对于装置实施例而言,由于其基本相似于方法实施例,所以描述得比较简单,相关之处参见方法实施例的部分说明即可。

以上所述仅是本申请的优选实施方式,虽然本申请已以较佳实施例披露如上,然而并非用以限定本申请。任何熟悉本领域的技术人员,在不脱离本申请技术方案范围情况下,都可利用上述揭示的方法和技术内容对本申请技术方案做出许多可能的变动和修饰,或修改为等同变化的等效实施例。因此,凡是未脱离本申请技术方案的内容,依据本申请的技术实质对以上实施例所做的任何的简单修改、等同变化及修饰,均仍属于本申请技术方案保护的范围内。

- 一种存储器的纠错方法、纠错装置和数据刷新方法

- 一种空间CCD图像存储器NAND闪存纠错编解码器及纠错方法