显示基板和显示装置

文献发布时间:2023-06-19 18:27:32

技术领域

本公开涉及显示技术领域,具体涉及一种显示基板和显示装置。

背景技术

微型有机发光二极管(Micro Organic Light-Emitting Diode,Micro-OLED)是近年来发展起来的微型显示器,硅基OLED是其中一种。硅基OLED采用成熟的互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,COMS)集成电路工艺制备,具有体积小,高分辨率(PPI)、高刷新率等优点,广泛应用在虚拟现实(Virtual Reality,VR)或增强现实(Augmented Reality,AR)近眼显示领域。

发明内容

本公开提供一种显示基板,具有显示区和环绕所述显示区的阴极环区,其中,所述显示基板包括:

衬底基板;

发光器件,设置在所述衬底基板上,并位于所述显示区;所述发光器件包括沿远离所述衬底基板的方向依次设置的:第一电极、发光层和第二电极;

供电电极,嵌设于所述衬底基板上,并位于所述阴极环区;

绝缘层,设置在所述衬底基板上,所述绝缘层上设置有暴露所述供电电极的第一过孔,所述第一过孔中设置有第一导电柱;

连接电极,位于所述绝缘层远离所述衬底基板的一侧,所述连接电极与所述第一导电柱接触,并与所述第二电极连接。

在一些实施例中,所述第一导电柱远离所述供电电极的端部超出所述绝缘层远离所述供电电极的表面,且超出部分具有第一高度;

所述连接电极的厚度大于所述第一高度。

在一些实施例中,所述第一高度小于或等于

在一些实施例中,所述第一导电柱远离所述供电电极的一端不高于所述绝缘层远离所述供电电极的表面。

在一些实施例中,所述连接电极与所述第二电极连接为一体,所述连接电极的材料包括透明导电材料。

在一些实施例中,所述第一导电柱的材料包括钨。

在一些实施例中,所述显示基板还包括:像素界定层,所述像素界定层设置在所述衬底基板上,并位于所述显示区内;所述像素界定层开设有像素开口,所述像素开口暴露出所述第一电极的表面,所述发光层位于所述像素开口中。

在一些实施例中,所述阴极环区包括依次嵌套的多个子环区,每个所述子环区中均设置有所述供电电极,相邻两个所述子环区之间设置有间隔区;

其中,在所述间隔区,所述连接电极与所述绝缘层接触。

在一些实施例中,所述绝缘层对应于每个所述供电电极的位置均设置有多个所述第一过孔。

在一些实施例中,所述显示基板还包括嵌设在所述衬底基板内的晶体管,所述第一电极与所述晶体管电连接,所述供电电极与所述晶体管的源极、漏极同层设置。

在一些实施例中,所述绝缘层上还设置有第二过孔,所述第二过孔暴露所述晶体管的漏极,所述第二过孔中设置有第二导电柱,所述第一电极通过所述第二导电柱与所述晶体管的漏极连接。

本公开还提供一种显示装置,其中,包括上述的显示基板。

附图说明

附图是用来提供对本公开的进一步理解,并且构成说明书的一部分,与下面的具体实施方式一起用于解释本公开,但并不构成对本公开的限制。在附图中:

图1为一实施例中提供的显示基板的平面图。

图2为一实施例中提供的显示基板的显示区的示意图。

图3为图1中的显示基板在阴极环区的结构示意图。

图4为本公开的一些实施例中提供的显示基板的区域分布示意图。

图5为本公开的一些实施例中提供的显示基板的结构示意图。

图6为本公开的一些实施例中的第一电极的示意图。

图7为本公开的一些实施例中提供的一种电路原理示意图。

图8为本公开的一些实施例中提供的电压控制电路和像素驱动电路的电路实现示意图。

具体实施方式

为使本公开实施例的目的、技术方案和优点更加清楚,下面将结合本公开实施例的附图,对本公开实施例的技术方案进行清楚、完整地描述。显然,所描述的实施例是本公开的一部分实施例,而不是全部的实施例。基于所描述的本公开的实施例,本领域普通技术人员在无需创造性劳动的前提下所获得的所有其他实施例,都属于本公开保护的范围。

这里用于描述本公开的实施例的术语并非旨在限制和/或限定本公开的范围。例如,除非另外定义,本公开使用的技术术语或者科学术语应当为本公开所属领域内具有一般技能的人士所理解的通常意义。应该理解的是,本公开中使用的“第一”、“第二”以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。除非上下文另外清楚地指出,否则单数形式“一个”、“一”或者“该”等类似词语也不表示数量限制,而是表示存在至少一个。“包括”或者“包含”等类似的词语意指出现在“包括”或者“包含”前面的元件或者物件涵盖出现在“包括”或者“包含”后面列举的元件或者物件及其等同,并不排除其他元件或者物件。“上”、“下”、“左”、“右”等仅用于表示相对位置关系,当被描述对象的绝对位置改变后,则所述相对位置关系也可能相应地改变。

在附图中,有时为了明确起见,夸大表示了各构成要素的大小、层的厚度或区域。因此,本公开的实施方式并不一定限定于该尺寸,附图中各部件的形状和大小不反映真实比例。

图1为一实施例中提供的显示基板的平面图,如图1所示,显示基板具有显示区AA和环绕该显示区AA的外围区域,其中,外围区域可以包括:虚设像素区PADA,阴极环区EA和绑定区BA。阴极环区EA环绕显示区AA,绑定区BA位于显示区AA的一侧,绑定区BA中设置有多个绑定电极PAD。

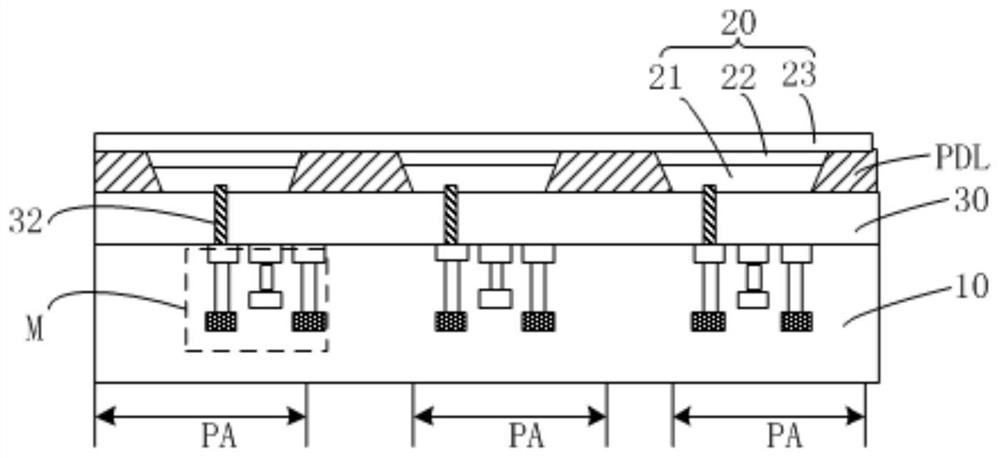

其中,图2为一实施例中提供的显示基板的显示区的示意图,如图2所示,显示区AA包括多个像素区PA,显示基板包括:衬底基板10和设置在衬底基板10上的像素驱动电路和发光器件20,其中,每个像素区PA均设置有像素驱动电路和发光器件20。像素驱动电路嵌设在衬底基板10中,且至少包括多个晶体管M。发光器件20设置在衬底基板10上,发光器件20包括沿远离衬底基板10的方向依次设置的第一电极21、发光层23和第二电极22,第一电极21与像素驱动电路连接,多个发光器件20的第二电极22可以连接为一体结构。

显示基板还包括设置在衬底基板10上的像素界定层PDL和绝缘层30,绝缘层30上对应于像素驱动电路的位置设置有第二过孔,第二过孔内设置有第二导电柱32,第一电极21通过第二导电柱32与像素驱动电路连接。像素界定层PDL位于绝缘层30远离衬底基板10的一侧,像素界定层PDL的第一部分位于第一电极21之间的间隔区域,第二部分位于第一电极21远离衬底基板10的一侧。像素界定层PDL上开设有多个像素开口,每个像素区PA均对应一个像素开口,像素开口暴露出第一电极21。发光层23位于像素开口中。

图3为图1中的显示基板在阴极环区的结构示意图,如图3所示,显示基板包括位于阴极环区EA的供电电极44,供电电极44嵌设于衬底基板10上。上述绝缘层30从显示区AA延伸至阴极环区EA。绝缘层30上设置有第一过孔,第一过孔暴露出供电电极44,第一过孔中设置有第一导电柱31。另外,在阴极环区EA还设置有第一导电电极41和第二导电电极42,第一导电电极41与发光器件20的第一电极21同步制作,第二导电电极42可以与发光器件20的第二电极22同步制作,且第一导电电极41和第二导电电极42接触。通过第一导电柱、第一导电电极41和第二导电电极42,可以将供电电极44上的电信号传输至每个发光器件20的第二电极22。

如图3所示,在阴极环区EA还设置有填充层43,填充层43的至少一部分位于第一导电电极41之间的间隔区域中,以防止后续形成的第二导电电极42在第一导电电极41之间的间隔位置发生断裂。其中,填充层43可以与像素界定层PDL同步制作。

其中,发光器件20为顶发射结构,第一电极21采用反射电极,其包括层叠设置的多个子电极层,第一导电电极41与第一电极21的结构、材料相同。例如,多个子电极层可以包括:依次设置的钛金属层、铝金属层、钛金属层、氧化铟锡(ITO)层。但是,由于工艺条件的限制,沉积的子电极层上会出现孔洞,以及会出现子电极层之间发生分离(peeling),从而导致第二导电电极42与第一导电电极41之间出现阻抗升高、接触不良等问题。另外,在利用光刻构图工艺制作填充层43时,很容易出现刻蚀残留的问题,这也会导致第二导电电极42与第一导电电极41接触不良,进而影响产品质量。

图4为本公开的一些实施例中提供的显示基板的区域分布示意图,图5为本公开的一些实施例中提供的显示基板的结构示意图,如图4和图5所示,显示基板具有显示区AA和环绕显示区AA的阴极环区EA,其中,显示基板包括:衬底基板10、发光器件20、供电电极44、绝缘层30、连接电极45。

其中,衬底基板10为硅基基板。发光器件20设置在衬底基板10上,并位于显示区AA。发光器件20可以包括沿远离衬底基板10的方向依次设置的:第一电极21、发光层23和第二电极22。每个发光器件20的发光层23可以单独发出红光、蓝光或绿光。

在一些实施例中,发光器件20采用顶发射结构,第一电极21采用反射电极,第二电极22采用透射电极,可选地,图6为本公开的一些实施例中的第一电极的示意图,如图5和图6所示,第一电极21可以包括沿远离衬底基板10的方向依次设置的第一钛金属层21a、铝金属层21b、第二钛金属层21c和透明导电层21d,第一钛金属层21a、第二钛金属层21c可以起到对铝金属层21b的保护作用,透明导电层21d可以为氧化铟锡层,可以起到空穴注入的作用。

其中,第一钛金属层21a的厚度可以在

在一些实施例中,第一电极21为阳极,第二电极22为阴极,多个发光器件20的第二电极22可以连接为一体。发光器件20还可以包括位于第一电极21与发光层23之间的空穴传输层,以及位于发光层23与第二电极22之间的电子传输层。

如图4所示,供电电极44嵌设于衬底基板10上,且位于阴极环区EA。供电电极44的数量可以为一个或多个。

绝缘层30设置在所述衬底基板10上,绝缘层30上对应于每个供电电极44的位置设置有第一过孔,第一过孔暴露供电电极44,第一过孔中设置有第一导电柱31。可选地,绝缘层30的材料可以包括硅氧化物(SiOx)、硅氮化物(SiNx)、氮氧化物(SiON)中的一者或多者,绝缘层30可以为单层结构,或者是多层结构。需要说明的是,在本公开实施例中,过孔暴露出某结构是指,过孔在衬底基板10上的正投影与该结构在衬底基板10上的正投影存在交叠,从而暴露出该结构的至少一部分。还需要说明的是,第一过孔中设置有第一导电柱31是指,第一导电柱31的至少一部分位于第一过孔中。

连接电极45位于绝缘层30远离衬底基板10的一侧,连接电极45与第一导电柱31直接接触,并与各发光器件20的第二电极22连接。

和图3所示的显示基板相比,图5所示的显示基板中,连接电极45与第一导电柱31直接接触,而不需要设置第一导电电极41,从而不会出现因第一导电电极41的孔洞、膜层分离等不良而导致连接电极45与第一导电柱31接触不良的情况,进而提高显示基板的质量。并且,由于不再设置第一导电电极41,因此不会出现由第一导电电极41而带来的电阻升高和压降问题,有利于改善显示效果。

如图4所示,阴极环区EA可以包括依次嵌套的多个子环区EA1,每个子环区EA1中均设置有供电电极44,每个供电电极44可以为封闭或半封闭的环状结构。相邻两个子环区EA1之间设置有间隔区。其中,绝缘层30对应于每个供电电极44的位置均设置有多个第一过孔,每个第一过孔内均设置有第一导电柱31,从而使得每个供电电极44均通过多个第一导电柱31与连接电极45连接,以保证连接电极45与供电电极44的电连接效果。其中,每个供电电极44所对应的多个第一过程均匀分布,例如,可以排成多行多列,以保证连接电极45上的电流分布更均一。

在一些实施例中,第一导电柱31的材料可以包括钨。采用钨金属可以保证导电通路的稳定性。

在一些实施例中,第一导电柱31远离供电电极44的一端(即第一导电柱31的顶端)不高于所述绝缘层30远离供电电极44的表面(即绝缘层30的上表面),也就是说,第一导电柱31整体位于第一过孔中,第一导电柱31的顶端与绝缘层30的上表面平齐,或者,第一导电柱31的顶端低于绝缘层30的上表面。

在另一些实施例中,为了保证连接电极45与第一导电柱31之间的连接可靠性,如图5所示,第一导电柱31的顶端超出绝缘层30的上表面,且超出部分具有第一高度。并且,连接电极45的厚度大于第一高度,以保证连接电极45的连续性。

在显示基板的制作过程中,可以先在绝缘层30上形成第一过孔,再在第一过孔内形成第一导电柱31,之后,利用化学机械抛光(CMP)工艺对第一导电柱31和绝缘层30整体进行抛光,由于抛光工艺对不同材料的抛光速率有所差异,因此,可以通过控制抛光时间,使得第一导电柱31的顶端与绝缘层30上表面平齐,或者略超出绝缘层30的上表面,例如,超出部分的高度(即上述第一高度)小于或等于

其中,连接电极45与各发光器件20的第二电极22可以连接为一体。连接电极45和第二电极22可以采用镁银合金,此时,为了保证发光器件20的出光效果,需要将连接电极45和第二电极22的厚度设置得较小。但是,考虑到第一导电柱31的顶端超出绝缘层30的上表面,如果连接电极45的厚度过小,将导致连接电极45在第一导电柱31的位置可能发生断裂,因此,为了保证连接电极45的连续性,在一些实施例中,连接电极45的厚度大于或等于

当连接电极45和第二电极22的厚度大于或等于

图7为本公开的一些实施例中提供的一种电路原理示意图,如图7所示,显示区AA中的多个像素区PA排成多行多列,每个像素区PA中设置有像素驱动电路以及与像素驱动电路电连接的发光器件20,像素驱动电路包括多个晶体管,该多个晶体管至少包括驱动晶体管。控制电路至少包括多个电压控制电路110,每个电压控制电路110与多个像素驱动电路101连接。例如,一个电压控制电路110与一行中的像素驱动电路101连接,该行像素驱动电路101中驱动晶体管的第一极共同连接该电压控制电路110,每个驱动晶体管的第二极与本显示单元的发光器件20的阳极连接,发光器件20的阴极连接第二电源信号VSS的输入端。电压控制电路110分别与第一电源信号VDD的输入端、初始化信号Vinit的输入端、复位控制信号RE的输入端和发光控制信号EM的输入端连接,电压控制电路110被配置为响应于复位控制信号RE,将初始化信号Vinit输出至驱动晶体管的第一极,控制对应的发光器件20复位。电压控制电路110还被配置为响应于发光控制信号EM,将第一电源信号VDD输出至驱动晶体管的第一极,以驱动发光器件20发光。通过一个显示行中的像素驱动电路101共同连接电压控制电路110,可以简化显示区AA中像素驱动电路101的结构,降低显示区AA中像素驱动电路101的占用面积,从而使显示区AA设置更多的像素驱动电路101和发光器件20,实现高PPI显示。电压控制电路110在复位控制信号RE的控制下将初始化信号Vinit输出至驱动晶体管的第一极,控制对应的发光器件20复位,可以避免上一帧发光时加载于发光器件20上的电压对下一帧发光的影响,可以改善残影现象。

在示例性实施方式中,3个不同颜色的像素区PA组成1个像素单元,3个像素区PA可以分别为红色像素区PA、绿色像素区PA以及蓝色像素区PA。在一些示例中,一个电压控制电路110可以连接同一行中两个相邻的显示单元中的像素驱动电路101,或可以连接同一行中三个或更多的像素区PA中的像素驱动电路101,在此不作限定。

图8为本公开的一些实施例中提供的电压控制电路和像素驱动电路的电路实现示意图。如图8所示,发光器件20的第一电极21与驱动晶体管M0的第二极D连接,发光器件20的第二电极22与第二电源信号VSS的输入端连接,第二电源信号VSS的电压一般为负电压或接地电压,初始化信号Vinit的电压也可以设置为接地电压。在一些示例中,发光器件20可以包括OLED(Organic Light-Emitting Diode,有机发光二极管),OLED可以是Micro-OLED或Mini-OLED,有利于实现高PPI显示。

在一些示例中,电压控制电路110与一行中的两个像素驱动电路101连接,像素驱动电路101包括驱动晶体管M0、第三晶体管M3、第四晶体管M4和存储电容Cst,电压控制电路110包括第一晶体管M1和第二晶体管M2。驱动晶体管M0、第一晶体管M1、第二晶体管M2、第三晶体管M3、第四晶体管M4均是制备在硅基村底中的金属氧化物半导体场效应管(MetalOxide Semiconductor,MOS)。第一晶体管Ml的栅极与复位控制信号RE的输入端连接,用于接收复位控制信号RE,第一晶体管Ml的第一极与初始化信号Vinit的输入端连接,用于接收初始化信号Vinit,第一晶体管Ml的第二极分别与对应的驱动晶体管M0的第一极S和第二晶体管M2的第二极连接。第二晶体管M2的栅极与发光控制信号EM的输入端连接,用于接收发光控制信号EM,第二晶体管M2的第一极与第一电源信号VDD的输入端连接,用于接收第一电源信号VDD,第二晶体管M2的第二极分别与对应的驱动晶体管M0的第一极S和第一晶体管Ml的第二极连接。在一些示例中,第一晶体管Ml与第二晶体管M2的类型可以不同,例如,第一晶体管Ml为N型晶体管,第二晶体管M2为P型晶体管,或者,第一晶体管Ml为P型晶体管,第二晶体管M2为N型晶体管。在一些可能的实现方式中,第一晶体管Ml与第二晶体管M2的类型可以相同,可以根据实际应用环境来设计确定,在此不作限定。

像素驱动电路101包括驱动晶体管M0、第三晶体管M3、第四晶体管M4和存储电容Cst。驱动晶体管M0的栅极G,驱动晶体管MO的第一极S与第一晶体管Ml的第二极和第二晶体管M2的第二极连接,驱动晶体管M0的第二极D与发光器件20的第一电极21连接。第三晶体管M3的栅极与第一扫描信号Sl的输入端连接,用于接收第一扫描信号SI,第三晶体管M3的第一极与数据信号DA的输入端连接,用于接收数据信号DA,第三晶体管M3的第二极与驱动晶体管M0的栅极G连接。第四晶体管M4的栅极与第二扫描信号S2的输入端连接,用于接收第二扫描信号S2,第四晶体管M4的第一极与数据信号DA的输入端连接,用于接收数据信号DA,第四晶体管M4的第二极与驱动晶体管M0的栅极G连接。存储电容Cst的第一端与驱动晶体管M0的栅极G连接,存储电容Cst的第二端与接地端GND连接。

图5中仅示意出了像素驱动电路中的驱动晶体管M0,以驱动晶体管为例,驱动晶体管M0包括有源层A、栅极G、源极S、漏极D和栅连接电极G0,可以通过掺杂工艺在硅基板上形成驱动晶体管M0的有源层A,有源层A包括源极接触区A1、漏极接触区A2以及位于二者之间的沟道区A0,源极S通过相应的导电柱50与源极接触区A1连接,漏极D通过相应的导电柱50与漏极接触区A2连接,栅连接电极G0通过相应的导电柱50与栅极G连接。

绝缘层30设置在衬底基板10上,绝缘层30上对应于每个驱动晶体管M0的位置设置有第二过孔,第二过孔暴露出驱动晶体管M0的漏极D,第二过孔中设置有第二导电柱32。其中,该第二导电柱32为钨棒。发光器件20设置在绝缘层30远离衬底基板10的一侧,发光器件20的第一电极21通过第二导电柱32与驱动晶体管M0的漏极D连接。

如图5所示,显示基板还包括:像素界定层PDL,像素界定层PDL的材料可以为无机材料,例如硅氧化物、硅氮化物或氮氧化物;也可以为有机材料,例如聚酰亚胺、亚克力或局对苯二甲酸乙二醇等。像素界定层PDL设置在绝缘层30远离衬底基板10的一侧,并位于显示区AA内。像素界定层PDL上开设有像素开口,像素开口暴露出所述第一电极21的表面,发光器件20的发光层23位于所述像素开口中。

在本公开实施例中,像素界定层PDL在衬底基板10上的正投影与阴极环区EA在衬底基板10上的正投影无交叠,在相邻的子环区之间的间隔区域,连接电极45与绝缘层30直接接触。也就是说,在形成像素界定层PDL时,先在衬底基板10上形成用于制作像素界定层PDL的绝缘材料,之后,利用光刻构图工艺在该绝缘材料上形成像素开口,并将阴极环区EA的绝缘材料全部去除,而无需保留图3中的填充部43,即,在刻蚀绝缘材料的过程中,刻蚀区域增大,从而有利于减少刻蚀残留,进而提高连接电极45与第一导电柱31的连接可靠性。

另外,由于连接电极45与多个第一导电柱31的顶端连接,第一导电柱31的顶端超出绝缘层30的上表面,因此,即便在制备过程中有少许绝缘材料的残留,这些残留也不会覆盖第一导电柱31顶端的端面,从而保证了连接电极45与第一导电柱31的连接可靠性。

如图4所示,显示基板还具有绑定区BA和金属走线区LA,绑定区BA位于显示区AA的一侧,金属走线区LA位于绑定区BA与阴极环区EA之间。显示基板还包括:位于绑定区BA中的绑定电极PAD以及位于金属走线区LA中的金属走线,如图5所示,绑定电极PAD和金属走线均嵌设于衬底基板10中。绝缘层30上开设有对应于绑定电极PAD的第三过孔V3,第三过孔V3暴露出绑定电极PAD。其中,绑定电极PAD、金属走线、供电电极44均可以与驱动晶体管M0的源极S、漏极D同层设置。

在一些实施例中,显示基板还可以包括封装层(未示出),封装层覆盖显示区AA、阴极环区EA和金属走线区LA,封装层可以为薄膜封装结构。

在一些实施例中,显示基板还可以包括盖板(未示出),盖板与位于封装层远离衬底基板10的一侧,且盖板与设置有封装层的衬底基板10之间通过密封胶固定。其中,封装层、密封胶和盖板可以均不覆盖绑定区BA。

本公开实施例还提供了一种显示装置,包括前述的显示基板。显示装置可以为虚拟现实装置、增强现实装置或近眼显示装置,或者可以为手机、平板电脑、电视机、显示器、笔记本电脑、数码相框、或导航仪,或任何其它具有显示功能的产品或部件。

在本公开提供的显示基板中,连接电极45与第一导电柱31直接接触,而不需要设置第一导电电极41,从而不会出现因第一导电电极41的孔洞、膜层分离等不良而导致连接电极45与第一导电柱31接触不良的情况,进而提高显示基板的质量,从而提高显示装置的质量。

可以理解的是,以上实施方式仅仅是为了说明本公开的原理而采用的示例性实施方式,然而本公开并不局限于此。对于本领域内的普通技术人员而言,在不脱离本公开的精神和实质的情况下,可以做出各种变型和改进,这些变型和改进也视为本公开的保护范围。

- 一种显示基板的制备方法、显示基板及显示装置

- 一种显示基板、显示面板及显示装置

- 一种显示基板、显示面板及显示装置

- 显示单元、显示基板及其制备方法、显示装置

- 阵列基板的制作方法、阵列基板以及显示装置

- 显示装置用基板、显示装置用基板的制造方法、显示装置、液晶显示装置、液晶显示装置的制造方法和有机电致发光显示装置

- 显示装置用基板、显示装置用基板的制造方法、显示装置、液晶显示装置、液晶显示装置的制造方法和有机电致发光显示装置