形成半导体器件的方法

文献发布时间:2023-06-19 19:18:24

相关申请的交叉引用

本申请基于并要求于2021年10月12日向韩国知识产权局提交的韩国专利申请No.10-2021-0135216的优先权,该申请的公开通过全文引用合并于此。

技术领域

本公开涉及一种形成半导体器件的方法,并且更具体地,涉及一种形成具有高纵横比的接触孔的方法。

背景技术

小型多功能电子设备可能需要高性能大容量的半导体器件。因此,半导体器件的集成密度增加,并且半导体器件的设计规则变得严格。因此,半导体器件可以包括具有高纵横比的接触孔。使用具有不良轮廓的硬掩模来形成具有高纵横比的接触孔可能是复杂且困难的。

发明内容

提供了形成半导体器件(例如,半导体器件的图案)的方法,该方法改进了掩模轮廓(例如,硬掩模轮廓),该掩模轮廓用于通过使用具有高选择性的掩模图案(例如,硬掩模图案)形成具有高纵横比的接触孔的工艺。

本公开不限于以上阐述的方面,并且附加方面部分地将在以下描述中阐述,且部分地将通过以下描述而变得清楚明白,或者可以通过实践所呈现的实施例来获知。

根据一些实施例,一种形成半导体器件(例如,半导体器件的图案)的方法可以包括:制备衬底(例如半导体衬底),在衬底上形成材料层;在材料层上形成包括硅(Si)的下硬掩模形成层;在下硬掩模形成层上形成包括氧化物的上硬掩模图案;通过使用上硬掩模图案作为蚀刻掩模并且使用包括金属氯化物的第一气体和包括氮化物的第二气体作为蚀刻气体蚀刻下硬掩模形成层,形成下硬掩模图案;以及通过使用下硬掩模图案作为蚀刻掩模蚀刻材料层,在材料层中形成多个接触孔。

根据一些实施例,一种形成半导体器件(例如,半导体器件的图案)的方法可以包括:制备衬底(例如,半导体衬底);在半导体衬底上形成模塑层和支撑形成层;在支撑形成层上形成掩模层(例如硬掩模形成层);通过使用氯化钛(TiCl

根据一些实施例,一种形成半导体器件(例如,半导体器件的图案)的方法可以包括:制备半导体衬底,在半导体衬底上形成材料层;在材料层上形成下硬掩模形成层,下硬掩模形成层包括硼化硅和硅(Si);在下硬掩模形成层上形成上硬掩模形成层,上硬掩模形成层包括氧化硅;在上硬掩模形成层上形成光刻胶图案;通过使用光刻胶图案作为蚀刻掩模蚀刻上硬掩模形成层,形成上硬掩模图案;通过使用上硬掩模图案作为蚀刻掩模并且使用氯化钛(TiCl

附图说明

根据以下接合附图的详细描述,将更清楚地理解本发明构思的示例实施例,在附图中:

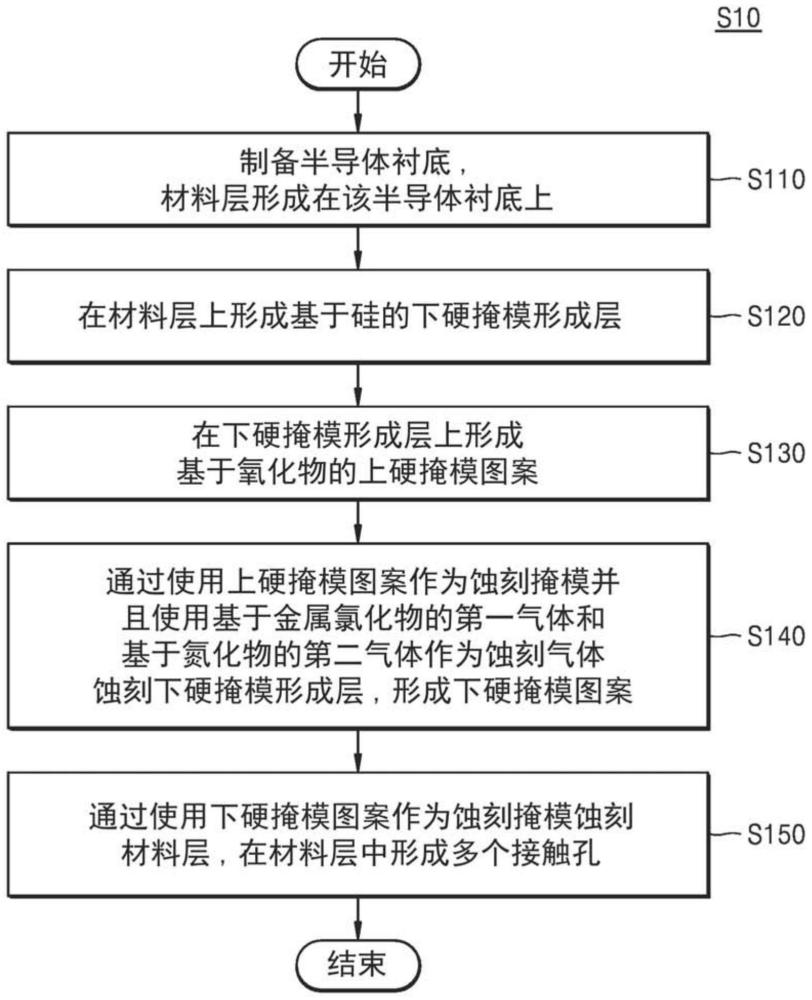

图1是示出了根据本发明的实施例的形成半导体器件的方法的流程图;

图2至图9是示出了根据本发明的实施例的形成半导体器件的方法的截面图;

图10是示出了根据本发明的实施例的通过形成半导体器件的方法制造的半导体器件中的多个导体(例如,下电极)的蜂窝结构布置的概念图;以及

图11A、图11B、图12A、图12B、图13A、图13B、图14A和图14B是示出了根据本发明的实施例的制造半导体器件的方法的图。

具体实施方式

在下文中,将参考附图详细描述本发明的示例实施例。

如本文所使用的,术语“高纵横比”是指约10:1或更高的深度与宽度(或深度与直径)比,并且术语“高选择性”是指约5:1或更高的蚀刻选择性。此外,如本文所使用的,术语“低纵横比”是指小于约10:1的深度与宽度(或深度与直径)比,并且术语“低选择性”是指小于约5:1的蚀刻选择性。

图1是示出了根据本发明的实施例的形成半导体器件图案的方法的流程图。

参考图1,形成半导体器件的方法S10(例如,形成半导体器件的图案的方法)可以包括第一操作S110至第五操作S150。在一些实施例中,那些第一操作S110至第五操作S150可以是顺序执行的过程。

在一些实施例中,可以与所描述的顺序不同地执行特定过程。例如,连续描述的两个过程可以基本上同时执行,或者可以相对于所描述的顺序以相反的顺序执行。

根据本发明,形成半导体器件的图案的方法S10可以包括:设置(例如,制备)半导体衬底的第一操作S110,在该半导体衬底上形成层(例如,包括材料的层);在该层上形成基于硅的下掩模层(例如,下硬掩模层或下硬掩模形成层)的第二操作S120;在下掩模层上形成基于氧化物的上掩模图案(例如,上硬掩模图案)的第三操作S130;通过使用上掩模图案作为蚀刻掩模并使用包括基于金属氯化物的第一气体和基于氮化物的第二气体的蚀刻气体蚀刻下掩模层来形成下掩模图案(例如,下硬掩模图案)的第四操作S140;通过使用下掩模图案作为蚀刻掩模蚀刻层来在层中形成多个接触孔的第五操作S150。在一些实施例中,第一气体可以包括金属和氯,并且第二气体可以包括氮。如本文所使用的,“基于A的气体或层”(或类似语言)可以指代包括元素或化合物A的气体或层。例如,基于硅的下掩模层是指包括硅的层,并且基于金属氯化物的气体是指包括金属氯化物的气体。在整个说明书中,在其中形成接触孔的层、下掩模层、上掩模图案和下掩模图案也可以分别被称为材料层、下硬掩模形成层、上硬掩模图案和下硬掩模图案。

小型多功能电子设备和高性能大容量半导体器件在电子行业中是优选的,因此半导体器件的集成密度增加,并且半导体器件的设计规则变得严格。因此,半导体器件可以包括具有高纵横比的接触孔。使用具有不良轮廓的硬掩模来形成具有高纵横比的接触孔是复杂且困难的。

根据本发明,根据形成半导体器件的图案的方法S10,可以在通过使用基于硅(Si)的硬掩模图案执行干法蚀刻以在蚀刻目标层中形成具有高纵横比的接触孔的过程中形成能够保护硬掩模图案的侧壁的金属保护层,从而改进在形成具有高纵横比的接触孔中产生(例如,形成)的不良硬掩模轮廓。

下面将参考图2至图9详细描述以上阐述的第一操作S110至第五操作S150。

图2至图9是示出了根据本发明的实施例的形成半导体器件图案的方法的截面图。

参考图2,材料层110、下硬掩模形成层120、上硬掩模形成层130和光掩模图案PM可以按所述顺序顺序地形成在半导体衬底101上。

半导体衬底101可以包括半导体材料,例如硅(Si)。在一些实施例中,半导体衬底101可以包括诸如锗(Ge)之类的半导体元素材料、和/或诸如碳化硅(SiC)、砷化镓(GaAs)、砷化铟(InAs)和/或磷化铟(InP)之类的化合物半导体材料。在一些实施例中,半导体衬底101可以具有绝缘体上硅(SOI)结构。半导体衬底101可以包括导电区域,例如掺杂杂质的阱、掺杂杂质的结构等。如本文所使用的,术语“和/或”包括关联列出的一个或多个项目的任意和所有组合。

半导体器件可以布置在半导体衬底101上。半导体器件可以包括存储器件和/或逻辑器件。此外,半导体器件可以包括多个不同类型的单独器件。多个单独器件可以包括例如晶体管、二极管、电容器或电阻器中的至少一个。

材料层110可以形成在半导体衬底101上。在一些实施例中,材料层110是蚀刻目标层并且可以包括绝缘材料。例如,材料层110可以通过单独形成氧化硅(Si

材料层110的类型和目的不限于本文所述的那些。在一些实施例中,材料层110是蚀刻目标层并且可以包括导电材料。材料层110可以由钨(W)、钨合金、铜(Cu)或铜合金形成。在一些实施例中,材料层110可以包括铝(Al)、钛(Ti)、钽(Ta)、钯(Pd)、铂(Pt)、钼(Mo)、金属硅化物或它们的组合。

下硬掩模形成层120可以形成在材料层110上。下硬掩模形成层120可以包括相对于材料层110具有高蚀刻选择性(即高选择性)的材料。通常,各种基于硅的材料和/或通过向基于硅的材料添加杂质获得的材料可以用作下硬掩模形成层120。在本发明的实施例中,下硬掩模形成层120可以包括例如包含硼化硅和硅(Si)的材料。然而,下硬掩模形成层120不限于此并且可以包括各种材料。

上硬掩模形成层130可以形成在下硬掩模形成层120上。通常,各种基于氧化物的绝缘材料可以用作上硬掩模形成层130。在本发明的实施例中,上硬掩模形成层130可以包括氧化硅(Si

在一些实施例中,下硬掩模形成层120的厚度(例如,在Z方向上的厚度)可以大于上硬掩模形成层130的厚度(例如,在Z方向上的厚度)。

可以在上硬掩模形成层130上施加光刻胶并通过曝光工艺和显影工艺对其进行图案化,从而形成光掩模图案PM。作为蚀刻目标层的材料层110中的待蚀刻区域可以由光掩模图案PM限定。在一些实施例中,可以在上硬掩模形成层130和光刻胶之间形成抗反射涂层(ARC)(未示出)。光掩模图案也可以被称为光刻胶图案。

在一些实施例中,光刻胶可用于正性显影,并且曝光部分(即,阈值量或更多光照射到其上的部分)可通过溶剂去除,未曝光部分(即,阈值量或更多光未照射到其上的部分)可以未被完全去除并且可以保留。然而,本发明不受限于此。在一些实施例中,光刻胶可用于负性显影以形成光掩模图案PM。

参考图3,可以通过使用光掩模图案PM作为蚀刻掩模来蚀刻上硬掩模形成层130(参见图2),从而形成上硬掩模图案130M。

在一些实施例中,当在上硬掩模形成层130(参见图2)上形成ARC时,也可以通过蚀刻ARC来形成抗反射图案。

上述蚀刻工艺可以是使用等离子体的干法蚀刻工艺。具体地,等离子体可以朝向半导体衬底101喷射并且可以包括工艺气体的离子和/或自由基,并且因此,等离子体可以用作蚀刻用等离子体,用于蚀刻在半导体衬底101上形成的上硬掩模形成层130(参见图2)。在一些实施例中,等离子体可以蚀刻上硬掩模形成层130。

参考图4,可以通过灰化和剥离工艺来去除光掩模图案PM(参见图3)。

接下来,可以通过使用上硬掩模图案130M作为蚀刻掩模并且使用基于金属氯化物的第一气体和基于氮化物的第二气体作为蚀刻气体EG来蚀刻下硬掩模形成层120。在一些实施例中,第一气体可以包括金属和氯,并且第二气体可以包括氮。

在一些实施例中,可以例如使用第一态气体(①)和第二态气体(②)作为蚀刻气体EG来蚀刻下硬掩模形成层120,第一态气体(①)包括基于金属氯化物的第一气体和基于氮化物的第二气体二者,第二态气体(②)包括基于金属氯化物的第一气体但不包括基于氮化物的第二气体。

在本发明的实施例中,基于金属氯化物的第一气体可以包括氯化钛(例如,四氯化钛TiCl

①第一态气体

化学反应式:下硬掩模形成层(SiB

②第二态气体

化学反应式:下硬掩模形成层(SiB

在一些实施例中,可以通过仅使用包括基于金属氯化物的第一气体和基于氮化物的第二气体二者的第三态气体(③)作为蚀刻气体来蚀刻下硬掩模形成层120。这里,针对下硬掩模形成层120与第三态气体(③)的反应的化学反应式如下。

③第三态气体

化学反应式:下硬掩模形成层(SiB

即,针对下硬掩模形成层120与第三态气体(③)的反应的化学反应式和针对下硬掩模形成层120与第一态气体(①)的反应的化学反应式可以基本相同。然而,虽然第一态气体(①)和第二态气体(②)可以交替使用,第三态气体(③)也可以单独使用。在一些实施例中,蚀刻气体可以由第三态气体(③)组成。第一态气体、第二态气体和第三态气体也可以分别被称为第一蚀刻气体、第二蚀刻气体和第三蚀刻气体。

参考图5,示出了下硬掩模形成层120的蚀刻从早期阶段到中期阶段执行的情形。

下硬掩模形成层120可以分为已经被蚀刻的上层120U和尚未被蚀刻的下层120L。即使在从蚀刻下硬掩模形成层120的早期阶段到中期阶段的时段期间,离子散射也可以发生在孔图案HP的内侧壁HPS处,孔图案HP形成在下硬掩模形成层120的上层120U中。即,当下硬掩模形成层120包括具有高选择性的材料时,因为在下硬掩模形成层120的蚀刻期间,下硬掩模形成层120的厚度比具有低选择性的硬掩模形成层的厚度减少相对较少,因此从蚀刻的早期阶段开始,离子散射可以发生在形成在下硬掩模形成层120的上层120U中的孔图案HP的内侧壁HPS处。

为了最小化由于离子散射造成的影响,在本发明的实施例中,基于金属氮化物的保护层140可以沿着上硬掩模图案130M的侧壁和下硬掩模形成层120的上层120U的侧壁(二者对应于孔图案HP的内侧壁HPS)形成。这里,蚀刻气体EG中包括的金属可以与保护层140中包括的金属相同。

如上所述,在本发明的实施例中,由于基于金属氯化物的第一气体可以包括氯化钛(例如,四氯化钛TiCl

参考图6和图7,示出了下硬掩模形成层120(参见图5)的蚀刻从中期阶段到后期阶段执行的情形。

可以通过使用上硬掩模图案130M作为蚀刻掩模来蚀刻下硬掩模形成层120(参见图5),从而形成下硬掩模图案120M。

因为在从蚀刻下硬掩模形成层120(参见图5)的中期阶段到后期阶段的时段中,包括具有高选择性的材料的下硬掩模形成层120(参见图5)的厚度由于蚀刻而变化相对较小,因此在下硬掩模形成层120中形成的孔图案HP的内侧壁HPS处可能仍然存在主要发生离子散射的地方。

因此,即使在下硬掩模形成层120(参见图5)中蚀刻执行到相当大的深度时,离子散射也可能在整个蚀刻过程中发生在下硬掩模形成层120中形成的孔图案HP的内侧壁HPS处。

如上所述,在本发明的实施例中,金属保护层140可以沿着上硬掩模图案130M的侧壁和下硬掩模图案120M的侧壁(二者对应于孔图案HP的内侧壁HPS)形成。

此外,蚀刻离子可以执行蚀刻直到孔图案HP的底部HPB,同时沿着在下硬掩模图案120M的侧壁上形成的金属保护层140具有高直线度。因此,由于在孔图案HP的底部HPB处的电荷弛豫,可以降低在等离子体蚀刻工艺中产生的自由基离子(e-)的电荷效应。

在本发明的实施例中,由于构成上硬掩模图案130M的材料与构成下硬掩模图案120M的材料不同,因此保护层140在它们之间的界面区域中的形成率可以相对低于其他区域中的形成率。因此,保护层140可以在上硬掩模图案130M和下硬掩模图案120M之间的界面区域中具有不平坦部分140C。保护层140的不平坦部分140C可以具有凹形。在一些实施例中,如图7所示,保护层140包括面向上硬掩模图案130M和下硬掩模图案120M的第一表面以及与第一表面相对的第二表面,并且第二表面包括与上硬掩模图案130M和下硬掩模图案120M之间的界面相邻的凹陷。因此,如图7所示,保护层140可以包括与上硬掩模图案130M和下硬掩模图案120M之间的界面相邻的部分,并且具有比保护层140的相邻部分更薄的厚度。

根据本发明,通过这一系列过程,能够保护孔图案HP的内侧壁HPS的金属保护层140可以在从基于硅(Si)的硬掩模形成层120(参见图5)形成下硬掩模图案120M的过程中形成,从而有效地改进下硬掩模图案120M中可能产生的不良掩模轮廓。

参考图8,可以通过使用上硬掩模图案130M和下硬掩模图案120M作为蚀刻掩模来蚀刻材料层110,从而在材料层110中形成多个接触孔110H。

在一些实施例中,多个接触孔110H可以形成为穿过材料层110,因此可以暴露半导体衬底101的顶表面的一部分。尽管为了便于描述,材料层110的厚度和多个接触孔110H的纵横比在图中被示为低,但是本发明不限于此。

参考图9,可以去除上硬掩模图案130M(参见图8)和下硬掩模图案120M(参见图8),从而完成在材料层110中形成精细图案(例如多个接触孔110H)的过程。

上硬掩模图案130M(参见图8)和下硬掩模图案120M(参见图8)二者可以通过例如湿法蚀刻工艺去除。可以通过使用湿法蚀刻溶液(例如氢氟酸溶液和/或缓冲氧化物蚀刻剂(BOE)溶液)来执行湿法蚀刻工艺。可以执行湿法蚀刻工艺,使得减小或最小化对材料层110和多个接触孔110H的影响。

再次参考图1,根据根据本发明的形成半导体器件的图案的方法S10,可以在通过使用基于硅(Si)的硬掩模图案执行干法蚀刻以在蚀刻目标层中形成高纵横比接触孔的过程中形成能够保护硬掩模图案的侧壁的金属保护层,从而改进在形成高纵横比接触孔时产生的不良硬掩模轮廓。

图10是示出了根据本发明的实施例的通过形成半导体器件图案的方法制造的半导体器件中的多个下电极的蜂窝结构布置的概念图。

参考图10,多个下电极220可以分别布置在六边形的第一顶点至第六顶点H1、H2、H3、H4、H5和H6以及六边形的中心点Hc处以形成蜂窝结构。此外,如图所示,多个下电极220可以以如下结构布置:蜂窝结构沿第一方向(X方向)和第二方向(Y方向)重复布置以彼此重叠。

具体地,多个下电极220可以以如下结构布置:中心六边形Hec(由实线示出)的第一顶点至第六顶点H1、H2、H3、H4、H5和H6分别变为六个相邻六边形的中心点,并且中心六边形Hec的中心点Hc由六个六边形共享。

例如,第二顶点H2可以是第二六边形He2(由点划线示出)的中心点,第五顶点H5可以是第五六边形He5(由虚线示出)的中心点,并且中心六边形Hec的中心点Hc可以由第二六边形He2和第五六边形He5共享,作为它们各自的六个顶点之一。

这里,由多个下电极220形成的蜂窝结构的六边形可以是正六边形。此外,共享六边形的中心点Hc的所有六个三角形可以是等边三角形。因此,在一个六边形中,相邻顶点之间的距离或每个顶点与中心点之间的距离可以彼此相等。

在多个下电极220中,纵横比(其是在X-Y平面上的宽度(例如,直径)与在第三方向(Z方向)上的高度的比率)可以非常大。例如,多个下电极220中的每一个的纵横比可以是大约10到大约30。此外,多个下电极220中的每一个的在X-Y平面上的直径可以是例如大约20nm至大约100nm,并且多个下电极220中的每一个的在第三方向(Z方向)上的高度可以是例如大约500nm至大约4000nm。需要注意的是,多个下电极220的结构不限于上述数值。

图11A至图14B示出了根据本发明的实施例的制造半导体器件的方法的图。

具体地,图11A、图12A、图13A和图14A是示出了根据本发明的实施例的制造半导体器件的方法的平面图。此外,图11B、图12B、图13B和图14B分别是沿图11A、图12A、图13A和图14A的线B-B'截取的截面图。

同时参考图11A和图11B,接触插塞211可以形成在半导体衬底101上的ILD 213中,蚀刻停止层215L可以形成在ILD 213和接触插塞211的顶表面上,然后模塑层225L可以形成在蚀刻停止层215L的顶表面上。

半导体衬底101可以包括例如半导体,例如硅(Si)或锗(Ge)。在一些实施例中,半导体衬底101可以包括化合物半导体,例如SiGe、SiC、GaAs、InAs或InP。因为半导体衬底101的描述与上面参考图2给出的基本相同,因此这里省略其详细描述。

模塑层225L可以包括例如氧化硅。例如,模塑层225L可以包括诸如BPSG、SOD、PSG、LPTEOS和/或PE-TEOS的材料。模塑层225L可以具有例如但不限于大约500nm至大约4000nm的厚度。

接下来,支撑形成层230L可以形成在模塑层225L上。支撑形成层230L可以包括例如诸如氮化硅和/或多晶硅的材料。支撑形成层230L可以具有例如但不限于大约20nm至大约150nm的厚度。

接下来,下硬掩模形成层120可以形成在支撑形成层230L上。因为下硬掩模形成层120的描述与上面参考图2给出的基本相同,因此这里省略其详细描述。

接下来,上硬掩模形成层可以形成在下硬掩模形成层120上,随后在上硬掩模形成层上施加光刻胶并通过曝光和显影工艺对光刻胶进行图案化,从而形成光掩模图案PM。

可以由光掩模图案PM限定要形成多个下电极220(参见图10)的区域。因为上硬掩模形成层的描述与上面参考图2给出的基本相同,因此这里省略其详细描述。此外,ARC(未示出)可以形成在上硬掩模形成层上。

接下来,可以通过使用光掩模图案PM作为蚀刻掩模来蚀刻上硬掩模形成层,从而形成上硬掩模图案130M。当ARC形成在上硬掩模形成层上时,抗反射图案也通过蚀刻ARC形成。

同时参考图12A和图12B,去除光掩模图案PM(参见图11B),然后可以通过使用上硬掩模图案130M作为蚀刻掩模来蚀刻下硬掩模形成层120(参见图11B),从而形成下硬掩模图案120M。

可以通过使用上硬掩模图案130M作为蚀刻掩模并且使用基于金属氯化物的第一气体和基于氮化物的第二气体作为蚀刻气体EG来蚀刻下硬掩模形成层120(参见图11B)。

在一些实施例中,可以通过交替使用第一态气体和第二态气体作为蚀刻气体EG来蚀刻下硬掩模形成层120(参见图11B),第一态气体包括基于金属氯化物的第一气体和基于氮化物的第二气体,第二态气体包括基于金属氯化物的第一气体但不包括基于氮化物的第二气体。

在本发明的实施例中,基于金属氮化物的保护层140可以沿着上硬掩模图案130M的侧壁和下硬掩模图案120M的侧壁形成。在一些实施例中,保护层140可以包括氮化钛(TiN)。保护层140作为蚀刻气体EG的副产物形成,且不需要形成保护层140的附加工艺。在一些实施例中,保护层140可以是使用蚀刻气体EG的蚀刻工艺的副产物。

同时参考图13A和13B,支撑形成层230L(参见图12B)、模塑层225L(参见图12B)和蚀刻停止层215L(参见图12B)可以通过使用上硬掩模图案130M和下硬掩模图案120M作为蚀刻掩模按照所述顺序被顺序地蚀刻。

因此,可以形成多个接触孔CH,并且接触插塞211的顶表面可以被接触孔CH暴露。接触孔CH可以具有第一直径D1。通过上述蚀刻,支撑形成层230L可以变成支撑图案层230,模塑层225L可以变成模塑图案225,并且蚀刻停止层215L可以变成蚀刻停止图案215。

当对模塑层225L(参见图12B)进行干法蚀刻时,多个接触孔CH可以均具有从其上端朝向其下端宽度减小的形状。然而,为了便于描述,示出了竖直形状的接触孔。在一些实施例中,可以通过过蚀刻在接触插塞211的顶表面处形成凹槽211G。在一些实施例中,可以在接触插塞211的顶表面处不形成凹槽。

同时参考图14A和14B,去除上硬掩模图案130M(参见图13B)和下硬掩模图案120M(参见图13B),然后要用作下电极的导电材料可以共形地形成在产生的产品的整个表面上。

接下来,执行节点分离工艺,从而沿着多个接触孔CH的底表面和侧表面形成具有圆柱形状的多个下电极220。节点分离工艺可以使用回蚀法和/或化学机械抛光(CMP)法。

要变成多个下电极220的导电材料可以包括金属氮化物、金属及其组合中的一种。例如,导电材料可以包括选自TiN、Ru、TaN、WN、Pt和Ir中的至少一种。导电材料可以通过化学气相沉积(CVD)法或原子层沉积(ALD)法形成,并且可以具有大约20nm至大约100nm的厚度。

彼此相邻的多个下电极220可以通过模塑图案225彼此绝缘和分离。当多个接触孔CH中的每一个具有从其上端朝向其下端宽度减小的形状时,这种形状也可以转移到多个下电极220。因此,多个下电极220中的每一个可以具有从其上端朝向其下端宽度减小的形状。

多个下电极220可以形成为使得每个下电极220的底部形成在凹槽211G中并且与凹槽211G接触。多个下电极220中的每一个的上端部分的外壁可以由支撑图案层230固定和支撑。

在通过根据本发明实施例的形成半导体器件的图案的方法制造的半导体器件中,在通过使用基于硅(Si)的硬掩模图案执行干法蚀刻以在蚀刻目标层中形成高纵横比接触孔CH的过程中形成能够保护硬掩模图案的侧壁的金属保护层,因此,高纵横比接触孔CH可以以期望的形状形成。

应注意的是,在一些替代实施例中,在流程图框中标记的功能/动作可以不以流程图中标记的顺序发生。例如,依赖于所涉及的功能/动作,连续示出的两个框实际上可以实质上同时执行,或者框有时候可以按照相反的顺序执行。此外,可以将流程图和/或框图的给定框的功能分成多个框和/或流程图和/或框图的两个或更多个框的功能可以至少部分地被集成。最后,在不脱离本发明的范围的情况下,可以在所示出的框之间添加/插入其他框,和/或可以省略框/操作。

尽管已经参考本发明的示例性实施例具体示出和描述了本发明,但是应当理解,在不脱离所附权利要求的范围的情况下,可以在其中进行形式和细节上的各种改变。

- 半导体器件以及形成半导体器件的方法

- 用于半导体器件的自对准结构、半导体结构及其形成方法

- 掩膜版及其制作方法、半导体器件的形成方法

- 半导体器件、半导体封装及制造半导体器件的方法

- 半导体器件及其制作方法、半导体器件测试方法

- 半导体器件用部材、以及半导体器件用部材形成液和半导体器件用部材的制造方法、以及使用该方法制造的半导体器件用部材形成液、荧光体组合物、半导体发光器件、照明装置和图像显示装置

- 半导体器件用部材、以及半导体器件用部材形成液和半导体器件用部材的制造方法、以及使用该方法制造的半导体器件用部材形成液、荧光体组合物、半导体发光器件、照明装置和图像显示装置