锁相回路电路

文献发布时间:2023-06-19 09:44:49

技术领域

本发明涉及一种锁相回路电路,特别是涉及一种具有可在工作周期调整模式及延迟锁相回路模式下操作的相位调整电路,以及精准控制预定死区时间的相位频率检测电路。

背景技术

锁相回路(Phase-locked loop,PLL)是一种利用反馈(Feedback)控制原理实现的频率及相位的同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。当参考时钟的频率或相位发生改变时,锁相回路会检测到这种变化,并且通过其内部的反馈系统来调节输出时钟,直到两者重新同步,这种同步又称为「锁相」(Phase-locked)。

在传统的PLL中,由于反馈路径中设置的N除频器,相位检测器(PD)及电荷泵(CP)的噪声在控制压控振荡器(Voltage-controlled oscillator,VCO)输出时被乘以N

然而,上述电路功能单一,而无法针对不同应用来操作在不同模式下。故,如何通过电路设计的改良,来进一步针对不同的应用提升电路效能,来克服上述的缺陷,已成为该项事业所欲解决的重要课题之一。

发明内容

本发明所要解决的技术问题在于,针对现有技术的不足提供一种锁相回路电路,具有可在工作周期调整模式及延迟锁相回路模式下操作的相位调整电路,以及精准控制预定死区时间的相位频率检测电路。

为了解决上述的技术问题,本发明所采用的其中一技术方案是,提供一种锁相回路电路,其包括延迟锁相回路及次取样锁相回路。延迟锁相回路用于将第一参考时钟及第二参考时钟锁相于输入时钟,其包括相位修正电路、积分器及第一次取样相位检测电路。相位修正电路,经配置以根据第一控制信号或第二控制信号调整该输入时钟,并产生该第一参考时钟及该第二参考时钟。积分器经配置以产生第一控制信号。第一次取样相位检测电路经配置以第二参考时钟对输出时钟取样,以产生第二控制信号。次取样锁相回路,经配置以预定的一锁相回路频率产生该输出时钟,且该输出时钟锁相于该第一参考信号,其包括第二次取样相位检测电路、相位频率检测电路、电压控制振荡器及第一除频器。第二次取样相位检测电路经配置以第一参考时钟对输出时钟取样,并输出一第三控制信号。相位频率检测电路经配置以接收第一参考时钟及除频信号,当第一参考时钟及除频信号之间的相位误差大于预定死区时间时,相位频率检测电路产生第四控制信号。电压控制振荡器经配置以依据第三控制信号及第四控制信号产生输出时钟。第一除频器经配置以将输出时钟除频以产生除频信号。其中,相位修正电路在工作周期调整模式及延迟锁相回路模式下操作,在工作周期调整模式下,积分器经配置以根据第一参考时钟及第二参考时钟产生第一控制信号,且相位修正电路依据第一控制信号调整输入时钟以产生第一参考时钟及该第二参考时钟。在延迟锁相回路模式下,相位修正电路依据第二控制信号调整输入时钟以产生第一参考时钟及第二参考时钟。

本发明的其中一有益效果在于,本发明所提供的锁相回路电路,具有可在工作周期调整模式及延迟锁相回路模式下操作的相位调整电路,在工作周期调整模式下可作为倍频器,且具有较低的抖动(Jitter)量,在延迟锁相回路模式下可作为次取样锁相回路中的相位延迟器,且使锁相回路(Phase Lock Loop,PLL)电路具有较低的突波(spur)。

本发明的另一有益效果在于,本发明所提供的锁相回路电路,具有精准控制预定死区时间的相位频率检测电路,通过形成具有相同延迟电路的相似路径,可产生较为精确的相位差信息及预定死区时间。

为使能更进一步了解本发明的特征及技术内容,请参阅以下有关本发明的详细说明与图式,然而所提供的图式仅用于提供参考与说明,并非用来对本发明加以限制。

附图说明

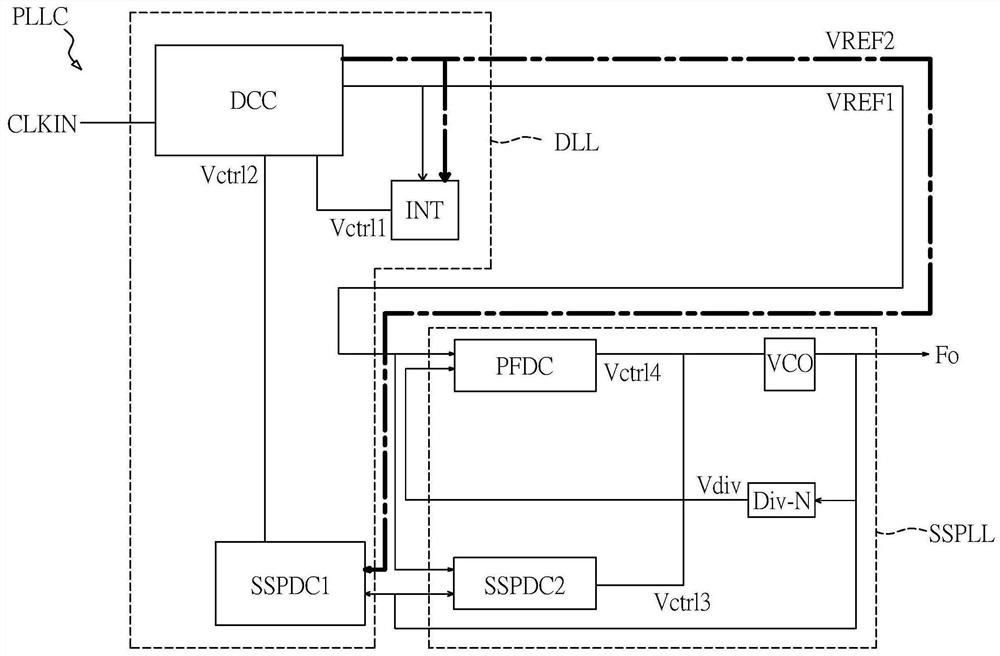

图1为本发明实施例的锁相回路电路的方块示意图。

图2为本发明的锁相回路电路的其中一种实施方式的细部电路图。

图3为本发明实施例的延迟锁相电路在工作周期调整模式及延迟锁相回路模式的电路架构图。

图4为本发明实施例的具有精确预定死区时间的相位频率检测器的细部电路图。

图5为本发明实施例的具有精确预定死区时间的相位频率检测器的信号时序图。

具体实施方式

以下是通过特定的具体实施例来说明本发明所公开有关“锁相回路电路”的实施方式,本领域技术人员可由本说明书所公开的内容了解本发明的优点与效果。本发明可通过其他不同的具体实施例加以施行或应用,本说明书中的各项细节也可基于不同观点与应用,在不悖离本发明的构思下进行各种修改与变更。另外,本发明的附图仅为简单示意说明,并非依实际尺寸的描绘,事先声明。以下的实施方式将进一步详细说明本发明的相关技术内容,但所公开的内容并非用以限制本发明的保护范围。

应当可以理解的是,虽然本文中可能会使用到“第一”、“第二”、“第三”等术语来描述各种元件或者信号,但这些元件或者信号不应受这些术语的限制。这些术语主要是用以区分一元件与另一元件,或者一信号与另一信号。另外,本文中所使用的术语“或”,应视实际情况可能包括相关联的列出项目中的任一个或者多个的组合。

参阅图1,其为本发明实施例的锁相回路电路的方块示意图。如图1所示,本发明实施例提供一种锁相回路电路PLLC,其包括延迟锁相回路DLL及次取样锁相回路SSPLL。延迟锁相回路DLL利用反馈(Feedback)控制原理,将所输出的第一参考时钟VREF1及第二参考时钟VREF2与其外部的输入时钟CLKIN保持同步,换言之,即是将第一参考时钟VREF1及第二参考时钟VREF2锁相于输入时钟CLKIN,进而实现频率及相位的同步。

如图1所示,延迟锁相回路DLL包括相位修正电路DCC、积分器INT及第一次取样相位检测电路SSPDC1。

相位修正电路DCC用于根据第一控制信号Vctrl1或第二控制信号Vctrl2调整输入时钟CLKIN,并产生第一参考时钟VREF1及第二参考时钟VREF2。可进一步参考图2,图2显示本发明的锁相回路电路的其中一种实施方式的细部电路图。

如图2所示,相位修正电路DCC包括第一低通滤波器LPF1、直流控制电路DC、直流偏移放大器DSA、放大器Amp,倍频电路FM及第二除频器Div2。

第一低通滤波器LPF1用来滤波输入时钟CLKIN以产生第一滤波后信号,直流控制电路DC,用来根据第一控制信号Vctrl1调整直流电压,直流偏移放大器,耦接第一低通滤波器LPF1及直流控制电路DC,包括两个晶体管T1、T2及电流源S1,用来根据滤波后信号及直流电压产生中间时钟。其中晶体管T1的栅极接收输入时钟CLKIN,中间时钟则通过此晶体管T1的漏极输出,并且此晶体管T1的源极通过电流源S1耦接接地端。另一晶体管T2的栅极接收输入时钟CLKIN的反相信号(由反相器产生),中间时钟则通过此晶体管T2的漏极输出,并且此晶体管T2的源极通过电流源S2耦接接地端。

第一低通滤波器LPF1包含并联的电容C1与电阻R1以及并联的电容C2与电阻R2。电容C1的一端耦接晶体管T1的漏极,另一端耦接系统电压信号VDD。电阻R1的一端耦接晶体管T1的漏极,另一端耦接该系统电压信号VDD。电容C2的一端耦接晶体管T2的漏极,另一端耦接系统电压信号VDD。电阻R2的一端耦接晶体管T2的漏极,另一端耦接系统电压信号VDD。

直流控制电路DC包含晶体管T3、晶体管T4及电流源S2。晶体管T3的栅极接收参考信号Vref(例如定电压),晶体管T3的漏极耦接晶体管T1的漏极,并且晶体管T3的源极通过电流源S2耦接接地端。晶体管T4的栅极接收第一控制信号Vctrl1,晶体管T4的漏极耦接晶体管T3的漏极,并且晶体管T4的源极通过电流源S2耦接接地端。

输入时钟CLKIN及其反相信号分别被晶体管T1及晶体管T2放大,且放大后的输入时钟CLKIN及放大后的反相信号被第一低通滤波电路LPF1滤波。滤波及放大后的信号(亦即中间时钟)由晶体管T1的漏极及晶体管T2的漏极输出。晶体管T1的漏极的直流电平及晶体管T2的漏极的直流电平由直流控制电路DC控制。通过调整参考信号Vref及第一控制信号Vctrl1可分别调整中间时钟的直流电平。

放大器Amp耦接直流偏移放大器DSA,用来放大中间时钟以产生放大后的中间时钟。倍频电路FM用于调整放大后的中间时钟的频率,以产生倍频信号CLKOUT。第二除频器Div2用于将倍频信号CLKOUT除频以产生第一参考时钟VREF1及第二参考时钟VREF2。经倍频电路FM(包含互斥或门ORG及延迟电路D)调整后,所输出的频率信号的频率为输入时钟CLKIN的两倍,但占空比同样维持在目标值。其中,除频器Div2将倍频电路FM所输出的倍频信号CLKOUT除频,使产生的第一参考时钟VREF1及第二参考时钟VREF2的频率与输入时钟CLKIN的频率相同,因此,使图2的相位修正电路DCC可以作为倍频电路。

积分器INT用于根据第一参考时钟VREF1及第二参考时钟VREF2产生第一控制信号Vctrl1,其电路细节将于下文中详述。

进一步,请参考图3,其为本发明实施例的延迟锁相电路在工作周期调整模式及延迟锁相回路模式的电路架构图。如图2及图3所示,积分器INT耦接直流偏移放大器DSA及直流控制电路DC,其根据第一参考时钟VREF1、第二参考时钟VREF2产生第一控制信号Vctrl1。其中,第一控制信号Vctrl1随着第一参考时钟VREF2及第二参考时钟VREF2之占空比之平均成分变化。

详细而言,当延迟锁相电路DLL进入工作周期调整模式时,积分器INT分别接收依据第一参考时钟VREF1及第二参考时钟VREF2之间的占空比差异产生的占空比参考信号CLKP、CLKPb、CLKN及CLKNb,再经过第三低通滤波电路LPF3滤波而产生第一控制信号Vctrl1。

举例而言,积分器340可以在第一参考时钟VREF1及第二参考时钟VREF2的相对占空比大于(或小于)一目标值(例如50%)时,降低(或提高)第一控制信号Vctrl1的电压电平。或者,当第一参考时钟VREF1及第二参考时钟VREF2的的占空比大于(或小于)该目标值时,提高(或降低)第一控制信号Vctrl1的电压电平。其中,第一控制信号Vctrl1的变化反应第一参考时钟VREF1及第二参考时钟VREF2的占空比的变化。因此,在工作周期调整模式下可作为倍频器使用,且使锁相回路(Phase LockLoop,PLL)电路具有较低的抖动(Jitter)量。

另一方面,第一次取样相位检测电路SSPDC1耦接于相位修正电路DCC,其以第二参考时钟VREF2对输出时钟Fo取样,以产生第二控制信号Vctrl2。如图2所示,第一次取样相位检测电路SSPDC1包括第一次取样相位检测器SSPD1及第一电荷泵CP1。

其中,第一次取样相位检测器SSPD1接收第二参考时钟VREF2及输出时钟Fo,用于以第二参考时钟VREF2对输出时钟Fo取样,并转换第二参考时钟VREF2及输出时钟Fo之间的相位误差以输出第一电荷泵控制信号对CPC1。而第一电荷泵CP1,依据第一电荷泵控制信号对CPC1产生第二控制信号Vctrl2。

进一步参考图3,在第一次取样相位检测电路SSPDC1中,经过第一次取样相位检测器/第一电荷泵SSPD1/CP1产生的控制信号可经过第四低通滤波器LPF4滤波,进而产生第二控制信号Vctrl2。其目的在于,在次取样锁相回路SSPLL之上,增加了次采样延迟锁定环(SSDLL),其使用与次取样锁相回路SSPLL相同的次取样相位检测电路,但其采样时钟为第一参考时钟VREF1的反相,即是第二参考时钟VREF2。因此,次取样锁相回路SSPLL使用上升沿对电压控制振荡器VCO的输出时钟Fo进行采样,能够使第二参考时钟VREF2的上升沿(即,第一参考时钟VREF1的下降沿)与输出时钟Fo过零点对齐。也因此,在延迟锁相回路模式下,可作为次取样锁相回路SSPLL中的相位延迟器,且具有较低的突波(spur)。

请复参考图1,次取样锁相回路SSPLL用于以预定的锁相回路频率产生输出时钟Fo,且输出时钟Fo锁相于第一参考信号VREF1。具体而言,次取样锁相回路SSPLL包括第二次取样相位检测电路SSPDC2、相位频率检测电路PFDC、电压控制振荡器VCO及第一除频器Div-N。

第二次取样相位检测电路SSPDC2用于以第一参考时钟VREF1对输出时钟Fo取样,并输出第三控制信号Vctrl3。

相位频率检测电路PFDC经配置以接收第一参考时钟VREF1及除频信号Vdiv,当第一参考时钟VREF1及除频信号之间的相位误差大于预定死区时间(Dead time)时,相位频率检测电路PFDC产生第四控制信号Vctrl4。

电压控制振荡器VCO依据第三控制信号Vctrl3及第四控制信号Vctrl4产生输出时钟Fo。第一除频器Div-N用于将输出时钟Fo除频,以产生除频信号Vdiv。

另一方面,当第一参考时钟VREF1及电压控制振荡器VCO输出的输出时钟Fo之间的相位误差很小时,相位频率检测电路PFDC检测到此相位误差小于预定死区时间,因此输出变为零。换言之,直到输出时钟Fo接近锁定前,电压控制振荡器VCO主要由第四控制信号Vctrl4进行控制,而在输出时钟Fo处于锁定状态时,则由第三控制信号Vctrl3控制电压控制振荡器VCO处于锁定状态。因此,在锁定状态下,次取样锁相回路SSPLL在反馈路径中不存在分频器,因而消除了分频器产生的噪声,同时免除其功率。进而,次取样锁相回路SSPLL可以实现非常低的相位噪声。

进一步说明次取样锁相回路SSPLL的细节。如图3所示,第二次取样相位检测电路SSPDC2包括第二次取样相位检测器SSPD2及第二电荷泵CP2。第二次取样相位检测器SSPDC2用于以第一参考时钟VREF1对输出时钟Fo取样,并转换第一参考时钟VREF1及输出时钟Fo之间的相位误差以输出第二电荷泵控制信号对CPC2。第二电荷泵CP2用于依据第二电荷泵控制信号对CPC2产生第三控制信号Vctrl3。

另一方面,亦如图2所示,相位频率检测电路PFDC包括相位频率检测器PFD及第三电荷泵CP3。

相位频率检测器PFD,接收第一参考时钟VREF1及除频信号Vdiv,当第一参考时钟VREF1及除频信号Vdiv之间的相位误差大于预定死区时间时,产生第三电荷泵控制信号对CPC3。第三电荷泵CP3经配置以依据第三电荷泵控制信号对CPC3产生第四控制信号Vctrl4。

再者,如图2所示,次取样锁相回路SSPLL还包括第二低通滤波器LPF2,用于滤波第三控制信号Vctrl3及第四控制信号Vctrl4以产生第二滤波后信号Vpf,而电压控制振荡器VCO则依据第二滤波后信号Vpf产生输出时钟Fo。以这种方式,第二次取样相位检测器SSPDC2及第二电荷泵CP2对电压控制振荡器VCO的输出时钟Fo进行取样,但却无法将N次的第一参考时钟VREF1的频率与此频率的其他谐波区分开。因此,次取样锁相回路SSPLL可能错误地锁定到不需要的分频比,因此需要频率锁定回路FLL来进行精确的频率锁定。此处,频率锁定回路FLL包括相位频率检测电路PFDC及第一除频器Div-N。

需要说明的是,电压控制振荡器VCO可为环形振荡器(Ring VCO),其具有较大的调整增益,也因此,其控制信号中的小幅变量将会造成电压控制振荡器VCO输出的输出时钟Fo的频率具有大幅变量。因此,需要针对次取样锁相回路SSPLL提供具有精确预定死区时间的频率锁定回路FLL,以在输出时钟Fo的频率距离锁定状态较远时操作。

进一步参考图4及图5所示,其分别为本发明实施例的具有精确预定死区时间的相位频率检测器的细部电路图及信号时序图。如图所示,相位频率检测器PFD包括多个正反器、多个延迟电路及逻辑门。详细而言,相位频率检测器PFD包括第一正反器DFF1、第二正反器DFF2、第三正反器DFF3、第四正反器DFF4、第一延迟电路DL1、第二延迟电路DL2、第一逻辑门及第二逻辑门。

第一正反器DFF1的时钟端接收与第一参考时钟VREF1相关的第一延迟信号VREF1d,输入端D接收系统电压信号VDD,重置端R接收第一重置信号rst1,以于输出端Q输出第一输出信号Vo1。其中,相位频率检测器PFD还包括第一延迟元件D1,将第一参考时钟VREF1延迟以产生第一延迟信号VREF1d。

第二正反器DFF2的时钟端接收与除频信号Vdiv相关的第二延迟信号Vdivd,输入端D接收系统电压信号VDD,重置端R接收第一重置信号rst1,以于输出端Q输出第二输出信号Vo2。其中,相位频率检测器PFD还包括第二延迟元件D2,将除频信号Vdiv延迟以产生第二延迟信号Vdivd。

第三正反器DFF3的时钟端接收第一延迟信号VREF1d,输入端D接收系统电压信号VDD,重置端R接收第二重置信号rst2,以于输出端

第四正反器DFF4,接收第二延迟信号Vdivd、系统电压信号VDD及第三重置信号rst3,以于输出端

第一延迟电路DL1,可包括一反相器电路INVC及可调延迟单元(Deadtime cell)Dc1,将第一输出信号Vo1经过反相器电路INVC后输出反相器信号dUP,并以可调延迟单元Dc1延迟一预定死区时间DT,以产生第三延迟信号dUP-D。其中,反相器电路INVC包括两个反相器,故反相器信号dUP波形与第一输出信号Vo1相同。

第二延迟电路DL2,可包括一反相器电路INVC及延迟单元(Deadtimecell)Dc2,将第二输出信号Vo2经过反相器电路INVC后输出反相器信号dDN,并以可调延迟单元Dc2延迟一预定死区时间DT,以产生第四延迟信号dDN-D。其中,反相器电路INVC包括两个反相器,故反相器信号dDN波形与第二输出信号Vo2相同。此外,第三输出信号Vo3及第四输出信号Vo4亦经过包括两个反相器的反相器电路INVC,亦维持相同波形。

第一逻辑门,例如可为第一与门AG1,接收第三输出信号Vo3及第三延迟信号dUP-D进行逻辑运算(AND运算),以产生第五控制信号dUP-DT。第二逻辑门,例如可为第二与门AG2,接收第四输出信号Vo4及第四延迟信号dDN-D进行逻辑运算,以产生第六控制信号dDN-DT。

其中,第五控制信号dUP-DT及第六控制信号dDN-DT作为第三电荷泵控制信号对CPC3。

再者,相位频率检测器PFD还包括第三逻辑门及第三延迟电路DL3,例如第三与门AG3,其接收第一输出信号Vo1及第二输出信号Vo2进行逻辑运算(AND运算),以产生第七控制信号CT7。第三延迟电路DL3包括第三可调延迟单元Dc3,将第七控制信号CT7延迟预定死区时间DT,并经过反相器INV进行反相处理,以产生第一重置信号rst1。需要说明的是,第一延迟电路DL1、第二延迟电路DL2及第三延迟电路DL3采用相同的延迟单元,如可调延迟单元Dc1、Dc2及Dc3。

详细而言,当第一参考时钟VREF1及除频信号Vdiv之间的相位误差不在预定死区时间DT的范围内时,与门AG1及AG2将分别输出由相位频率检测器PFD产生的第五控制信号dUP-DT及第六控制信号dDN-DT脉冲。当相位误差在预定死区时间DT的范围内时,与门AG1及AG2将不会输出第五控制信号dUP-DT及第六控制信号dDN-DT脉冲。

此外,相位频率检测电路PFD更通过形成具有相同延迟单元的相似路径,并同样具有延迟时间d,可产生较为精确的相位差信息及预定死区时间DT。

[实施例的有益效果]

本发明的其中一有益效果在于,本发明所提供的锁相回路电路,具有可在工作周期调整模式及延迟锁相回路模式下操作的相位调整电路,在工作周期调整模式下可作为倍频器,且具有较低的抖动(Jitter)量,在延迟锁相回路模式下可作为次取样锁相回路中的相位延迟器,且具有较低的突波(spur)。

本发明的另一有益效果在于,本发明所提供的锁相回路电路,具有精准控制预定死区时间的相位频率检测电路,通过形成具有相同延迟电路的相似路径,可产生较为精确的相位差信息及预定死区时间。

以上所公开的内容仅为本发明的优选可行实施例,并非因此局限本发明的权利要求,所以凡是运用本发明说明书及图式内容所做的等效技术变化,均包含于本发明的权利要求范围内。

【符号说明】

锁相回路电路:PLLC

延迟锁相回路:DLL

次取样锁相回路:SSPLL

第一参考时钟:VREF1

第二参考时钟:VREF2

输入时钟:CLKIN

相位修正电路:DCC

积分器:INT

第一次取样相位检测电路:SSPDC1

第二控制信号:Vctrl2

第一低通滤波器:LPF1

直流控制电路:DC

直流偏移放大器:DSA

放大器:Amp

倍频电路:FM

第二除频器:Div2

晶体管:T1、T2、T3、T4

电流源:S1、S2

系统电压信号:VDD

电容:C1、C2

电阻:R1、R2

参考信号:Vref

第三低通滤波电路:LPF3

输出时钟:Fo

第一次取样相位检测器:SSPD1

第一电荷泵控制信号对:CPC1

第四低通滤波器:LPF4

电压控制振荡器:VCO

第二次取样相位检测电路:SSPDC2

相位频率检测电路:PFDC

第一除频器:Div-N

第三控制信号:Vctrl3

除频信号:Vdiv

第四控制信号:Vctrl4

第二次取样相位检测器:SSPD2

第二电荷泵:CP2

第二电荷泵控制信号对:CPC2

相位频率检测器:PFD

第三电荷泵:CP3

第三电荷泵控制信号对:CPC3

第二低通滤波器:LPF2

第二滤波后信号:Vpf

频率锁定回路:FLL

第一正反器:DFF1

第二正反器:DFF2

第三正反器:DFF3

第四正反器:DFF4

第一延迟电路:DL1

第二延迟电路:DL2

第一延迟信号:VREF1d

第二延迟信号:Vdivd

输入端:D

重置端:R

第一重置信号:rst1

输出端:Q、

第一输出信号:Vo1

第一延迟元件:D1

第二输出信号:Vo2

第二延迟元件:D2

第二重置信号:rst2

第三输出信号:Vo3

第三重置信号:rst3

第四输出信号:Vo4

反相器电路:INVC

反相器信号:dUP、dDN

可调延迟单元:Dc1、Dc2、Dc3

预定死区时间:DT

延迟时间:d

第三延迟信号:dUP-D

第一与门:AG1

第二与门:AG2

第五控制信号:dUP-DT

第六控制信号:dDN-DT

第七控制信号:CT7

反相器:INV

第一控制信号:Vctrl1

互斥或门:ORG

第一电荷泵:CP1

第三延迟电路:DL3

第三与门:AG3

第四延迟信号:dDN-D

占空比参考信号:CLKP、CLKPb、CLKN及CLKNb

倍频信号:CLKOUT。

- 基于锁相回路的时钟产生电路以及锁相回路电路

- 延迟锁相回路、回路滤波器及延迟锁相回路的锁相的方法