一种实现CORDIC旋转模式下近似计算的装置和方法

文献发布时间:2023-06-19 09:58:59

技术领域

本发明涉及坐标旋转计算技术领域,尤其是实现CORDIC旋转模式下近似计算的方法和装置。

背景技术

坐标旋转数字计算机DORDIC(Coordinate Rotation Digital Computer)最早由Volder J在1959年提出。CORDIC算法是一种循环迭代算法,基本思想是通过一系列固定的,与运算基数有关的角度不断偏摆迭代以逼近所需的旋转角度。Cordic算法通过简单的加法和移位操作就可以完成三角函数的计算。

参见图1,在xy坐标平面上将点(x

x

y

通过提取因数cosθ,方程可写成下面的形式:

x

y

两边同时除以cosθ,得到伪旋转方程式:

其中,

tanθ

式中,i为迭代次数,故迭代过程中,式(5)、式(6)的方程改写为:

如上所述,将各种可能的旋转角度加以限制满足关系式tanθ

对于每次迭代而言,前面所示的伪旋转现在可以表示为:

符号d

迭代中引入名为角度累加器的第三个等式,用于追踪每次迭代中旋转的角度的叠加:

z

式中,z值为要旋转的总角度,旋转的目标是使z

在旋转模式中,d

d

d

现有实现CORDIC算法的一次迭代运算硬件电路100如图2所示,初始的X坐标通过数据选择器101后存入X坐标寄存器103,初始的Y坐标通过数据选择器102后存入Y坐标寄存器105,X坐标寄存器103的值一方面直接传入加法器108第一输入端,一方面通过移位器106传入加法器109第二输入端,Y坐标寄存器105的值一方面直接传入加法器109第一输入端,一方面通过移位器107传入加法器108第二输入端,加法器108的计算结果传回至数据选择器101并存入X坐标寄存器103,加法器109的计算结果传回至数据选择器102并存入Y坐标寄存器105,如此完成一次迭代计算。迭代计算中,根据迭代计数器104所记录的迭代的次数i来确定移位器106和移位器107的移位数,同时,参考式(12)、式(13),方向控制器110根据迭代中要旋转的角度方向来调整送入加法器108第二输入端和加法器109第二输入端的数值是取正值还是取负值。数据选择控制器111同时控制数据选择器101和数据选择器102的输出值。

现有的CORDIC算法根据数据的位数所需精度选择需要迭代的次数,通常迭代次数与数据位数相同,如计算的数据是16位,为了获得可靠精度,则需要进行16次迭代运算。

但是在集成电路中,加法计算单元由于较难处理进位链,导致一次迭代延时大,周期长,难以提升系统时钟频率。如图3所示,一个8位的加法器,由8个全加器(adder)构成,ci为进位链,si的计算结果依赖于ci的计算结果,全加器的电路结构如图4所示。因此,s7的输出以及整个加法和的得出与前面7个全加器的结果都相关联,具有很大的时延。假设一个全加器计算ci的时延为tc,则s7的计算时延大于7*tc。

由此可见,降低加法计算单元的延时或寻找一种更快的运算方式成为在进行CORDIC运算时提升效率的关键。

发明内容

为了解决上述问题,本发明提出在CORDIC旋转模式下,在求解旋转向量迭代过程中,采用具有进位保留器结构的压缩加法器替换普通进位加法器,在集成电路设计中,可以显著提升该部分的时钟频率。

本发明通过以下技术方案实现的:

本发明提出一种实现CORDIC旋转模式下近似计算的装置,包括第一数据选择器、第二数据选择器、数据选择控制器、X坐标进位项寄存器、X坐标和值项寄存器、Y坐标进位项寄存器、Y坐标和值项寄存器、第一移位器、第二移位器、第三移位器、第四移位器、迭代记数器、第一压缩加法器、第二压缩加法器和方向控制器,所述第一数据选择器的第一输入端接入X坐标初始值,所述第一数据选择器的第一输出端连接所述X坐标进位项寄存器,所述X坐标进位项寄存器还分别连接所述第一压缩加法器的第一输入端和所述第一移位器,所述第一数据选择器的第二输出端连接所述X坐标和值项寄存器,所述X坐标和值项寄存器还分别连接所述第一压缩加法器的第二输入端和所述第二移位器,所述第二数据选择器的第一输入端接入Y坐标初始值,所述第二数据选择器的第一输出端连接所述Y坐标进位项寄存器,所述Y坐标进位项寄存器还分别连接所述第二压缩加法器的第一输入端和所述第三移位器,所述第二数据选择器的第二输出端连接所述Y坐标和值项寄存器,所述Y坐标和值项寄存器还分别连接所述第二压缩加法器的第二输入端和所述第四移位器,所述第一移位器还连接所述第二压缩加法器的第三输入端,所述第二移位器还连接所述第二压缩加法器的第四输入端,所述第三移位器还连接所述第一压缩加法器的第三输入端,所述第四移位器还连接所述第一压缩加法器的第四输入端,所述迭代记数器分别连接所述第一移位器、所述第二移位器、所述第三移位器和所述第四移位器,所述第一压缩加法器的第一输出端连接所述第一数据选择器的第二数据输入端,所述第一压缩加法器的第二输出端连接所述第一数据选择器的第三数据输入端,所述第二压缩加法器的第一输出端连接所述第二数据选择器的第二数据输入端,所述第二压缩加法器的第二输出端连接所述第二数据选择器的第三数据输入端,所述数据选择控制器同时控制第一数据选择器和所述第二数据选择器的数据输出,所述方向控制器同时控制输入所述第一压缩加法器的第三输入端和第四输出端以及输入所述第二压缩加法器的第三输入端和第四输出端的数值正负号。

进一步地,所述第一压缩加法器和所述第二压缩加法器结构相同,均包括相级联的多个5-3压缩器,所述5-3压缩器的数目与其处理的数据位数相同,所述5-3压缩器设有四个数值输入端、一个进位项输出端、两个数值输出端和一个进位输出端,上一级所述5-3压缩器的进位项输出端连接下一级所述5-3压缩器的进位项输入端。

进一步地,所述5-3压缩器包括第一与门、第一异或门、第二异或门、第二与门、第三异或门、或门、第四异或门和第三数据选择器,所述5-3压缩器的第一数值输入端分别连接所述第一与门的第一输入端和所述第一异或门的第一输入端,所述5-3压缩器的第二数值输入端分别连接所述第一与门的第二输入端和第一异或门的第二输入端,所述所述5-3压缩器的第三数值输入端分别连接所述第二与门的第一输入端和所述第二异或门的第一输入端,所述所述5-3压缩器的第四数值输入端分别连接所述第二异或门的第二输入端和所述第三数据选择器的第一输入端,所述第一与门的输出端连接所述或门的第一输入端,所述第一异或门的输出端分别连接所述第二与门的第二输入端和所述第三异或门的第一输入端,所述第二异或门的输出端连接所述第三异或门的第二输入端,所述第二与门的输出端连接所述或门的第二输入端,所述第三异或门的输出端分别连接所述第四异或门的第一输入端和所述第三数据选择器的控制端,所述5-3压缩器的进位项输入端分别连接所述第四异或门的第二输入端和所述第三数据选择器的第二输入端,所述或门的输出端作为所述5-3压缩器的进位项输出端,所述第四异或门的输出端作为所述5-3压缩器的和值项输出端,所述第三数据选择器的输出端作为所述5-3压缩器的进位项输出端。

本发明还提出一种实现CORDIC旋转模式下近似计算的方法,采用上述实现CORDIC旋转模式下近似计算的装置运行,包括如下步骤:

S1:通过第一数据选择器向X坐标进位项寄存器存入初始值0以及向X坐标和值项寄存器存入初始值x0,通过第二数据选择器向Y坐标进位项寄存器存入初始值0以及向Y坐标和值项寄存器存入初始值x0,迭代记数器数值置为0;

S2:X坐标进位项寄存器的数值存入第一移位器,X坐标和值项寄存器的数值存入第二移位器,Y坐标进位项寄存器的数值存入第三移位器,Y坐标和值项寄存器的数值存入第四移位器,第一移位器、第二移位器、第三移位器和第四移位器均向右移位,移位位数为迭代记数器的当前数值;完成以上操作后,迭代计数器数值加1;

S3:X坐标进位项寄存器、X坐标和值项寄存器、第三移位器和第四移位器的数值均输入第一压缩加法器进行计算,Y坐标进位项寄存器、Y坐标和值项寄存器、第一移位器和第二移位器的数值均输入第二压缩加法器进行计算,其中,第一移位器、第二移位器、第三移位器和第四移位器的数值均由方向控制器根据当前迭代中要旋转的角度方向来确定正负号;

S4:第一压缩加法器输出的当前X值进位项通过第一数据选择器存入X坐标进位项寄存器,第一压缩加法器输出的当前X值和值项通过第一数据选择器存入X坐标和值项寄存器,第二压缩加法器输出的当前Y值进位项通过第二数据选择器存入Y坐标进位项寄存器,第二压缩加法器输出的当前Y值和值项通过第二数据选择器存入Y坐标和值项寄存器;

S5:重复步骤S2至S4,直至迭代记数器数值等于装置处理的数据位数减2;

S6:使用普通进位加法器计算当前X值进位项与当前X值和值项之和作为最终X坐标值,以及使用普通进位加法器计算当前Y值进位项与当前Y值和值项之和作为最终Y坐标值。

本发明的有益效果:

本发明将现有技术中的普通进位加法器替换为具有进位保留器结构的压缩加法器,通过在n-1次迭代过程中,使用5-3压缩器替换全加器,降低CORDIC运算中由加法进位链带来的时延,从而显著提高了系统的运行时钟。

附图说明

图1为点(x0,y0)旋转到点(x1,y1)示意图;

图2为现有技术实现CORDIC算法的一次迭代运算硬件电路示意图;

图3为现有技术加法器结构示意图;

图4为现有技术全加器结构示意图;

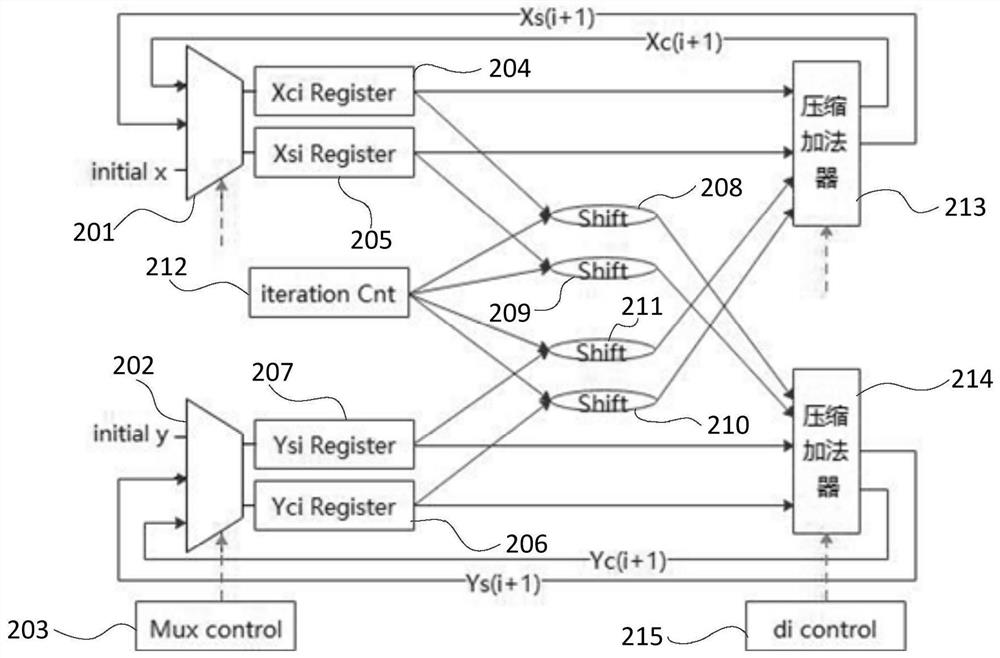

图5为本发明的一种实现CORDIC旋转模式下近似计算的装置结构示意图;

图6为本发明的第一压缩加法器和第二压缩加法器结构示意图;

图7为本发明的5-3压缩器结构示意图。

具体实施方式

为了更加清楚、完整的说明本发明的技术方案,下面结合附图对本发明作进一步说明。

参见图5,本发明提出一种实现CORDIC旋转模式下近似计算的装置实施例,包括第一数据选择器201、第二数据选择器202、数据选择控制器203、X坐标进位项寄存器204、X坐标和值项寄存器205、Y坐标进位项寄存器206、Y坐标和值项寄存器207、第一移位器208、第二移位器209、第三移位器210、第四移位器211、迭代记数器212、第一压缩加法器213、第二压缩加法器214和方向控制器215,第一数据选择器201的第一输入端接入X坐标初始值,第一数据选择器201的第一输出端连接X坐标进位项寄存器204,X坐标进位项寄存器204还分别连接第一压缩加法器213的第一输入端和第一移位器208,第一数据选择器201的第二输出端连接X坐标和值项寄存器205,X坐标和值项寄存器205还分别连接第一压缩加法器213的第二输入端和第二移位器209,第二数据选择器202的第一输入端接入Y坐标初始值,第二数据选择器202的第一输出端连接Y坐标进位项寄存器206,Y坐标进位项寄存器206还分别连接第二压缩加法器214的第一输入端和第三移位器210,第二数据选择器202的第二输出端连接Y坐标和值项寄存器207,Y坐标和值项寄存器207还分别连接第二压缩加法器214的第二输入端和第四移位器211,第一移位器208还连接第二压缩加法器214的第三输入端,第二移位器209还连接第二压缩加法器214的第四输入端,第三移位器210还连接第一压缩加法器213的第三输入端,第四移位器211还连接第一压缩加法器213的第四输入端,迭代记数器212分别连接第一移位器208、第二移位器209、第三移位器210和第四移位器211,第一压缩加法器213的第一输出端连接第一数据选择器201的第二数据输入端,第一压缩加法器213的第二输出端连接第一数据选择器201的第三数据输入端,第二压缩加法器214的第一输出端连接第二数据选择器202的第二数据输入端,第二压缩加法器214的第二输出端连接第二数据选择器202的第三数据输入端,数据选择控制器203同时控制第一数据选择器201和第二数据选择器202的数据输出,方向控制器215同时控制输入第一压缩加法器213的第三输入端和第四输出端以及输入第二压缩加法器214的第三输入端和第四输出端的数值正负号。

具体地,本发明根据CORDIC迭代的特点,应用一种运算结构,将现有技术中的普通进位加法器替换为采用进位保留器结构的压缩加法器。在原理上,本发明将原来每个全加器计算的si和c(i+1)分别保留,c(i+1)并不参与下一级的全加器计算,而是,将所有的si组合起来构成一个新加数Xs,命名为和值项,以及,将所有的c(i+1)组合起来构成另一个新加数Xc,命名为进位项。其中,c(i+1)比si权重高一位。在CORDIC运算中,由于加法(或减法)是迭代的,可以将压缩后的结果直接作为下一次迭代运算的输入,后级迭代再压缩直接输出,重复以上运算的迭代次数后,在最后一次迭代再进行总的加减运算。这种方式省略了n-1次(n为总的迭代次数,也即为装置处理的数据位数)迭代的加法进位时间,从而加快运行速度。

在结构上,本发明将采用进位保留器结构的压缩加法器应用到CORDIC电路中,每次压缩后获得和值项Xs和进位项Xc。相比原电路,由于没有对输入直接相加,而是对进位项进行了保留,为了使保留项参与下一级计算,需要增加一个寄存器保存新增项。

第一压缩加法器213的四个输入端的输入数值分别为进位项Xci、和值项Xsi、Yci_shift和Ysi_shift;第二压缩加法器214的四个输入端的输入数值为进位项Yci、和值项Ysi、Xci_shift和Xsi_shift。其中Xci_shift、Xsi_shift、Yci_shift、Ysi_shift是被加还是被减由判断算子di的符号控制,下面以第一压缩加法器为例分别讨论被加的情况和被减的情况。

如果被加,即四个数相加,有:Xci+Xsi+Yci_shift+Ysi_shift,即总共有4个加数。

如果被减,即两个数减去两个数,则在送入第一压缩加法器213之前还需进行数据符号处理。在数字处理中,减去一个数,就等于对该数取反再加1,即-x=~x+1。在运算中,如果di的符号控制Yci_shift和Ysi_shift的符号为负,则在移位之前,先进行-x=~x+1操作,即对Yci和Ysi分别进行取反加1。考虑到+1操作带来的延时,以及后面要进行的移位操作,这里对-x做近似处理取~x。由于舍去的是最后位比特,以及后面要进行的移位操作,其带来的近似误差最大为1/2

Xci+Xsi+(~Yci_shift)+(~Ysi_shift)。

参见图6,进一步地,第一压缩加法器213和第二压缩加法器214结构相同,均包括相级联的多个5-3压缩器,5-3压缩器的数目与其处理的数据位数相同,5-3压缩器设有四个数值输入端、一个进位项输出端、两个数值输出端和一个进位输出端,上一级5-3压缩器的进位项输出端连接下一级5-3压缩器的进位项输入端。

需要说明的是,由于5-3压缩器加法器对输入顺序没有要求,四个数值输入端任意顺序输入数据,最终计算的结果都是相同的。

参见图7,进一步地,5-3压缩器包括第一与门301、第一异或门302、第二异或门303、第二与门304、第三异或门305、或门306、第四异或门307和第三数据选择器308,5-3压缩器的第一数值输入端xi1分别连接第一与门301的第一输入端和第一异或门302的第一输入端,5-3压缩器的第二数值输入端xi2分别连接第一与门301的第二输入端和第一异或门302的第二输入端,5-3压缩器的第三数值输入端xi3分别连接第二与门304的第一输入端和第二异或门303的第一输入端,5-3压缩器的第四数值输入端xi4分别连接第二异或门303的第二输入端和第三数据选择器308的第一输入端,第一与门301的输出端连接或门306的第一输入端,第一异或门302的输出端分别连接第二与门304的第二输入端和第三异或门305的第一输入端,第二异或门303的输出端连接第三异或门305的第二输入端,第二与门304的输出端连接或门306的第二输入端,第三异或门305的输出端分别连接第四异或门307的第一输入端和第三数据选择器308的控制端,5-3压缩器的进位项输入端Carry(i-1)分别连接第四异或门307的第二输入端和第三数据选择器308的第二输入端,或门306的输出端作为5-3压缩器的进位项输出端Carryi,第四异或门307的输出端作为5-3压缩器的和值项输出端si,第三数据选择器308的输出端作为5-3压缩器的进位项输出端ci。

具体地,进位项输出端Carryi是下一级5-3压缩器的进位项,从图7的结构可以发现Carryi只与当前输入有关,而与Carry(i-1)无关。5-3压缩器的总时延关键路径为si,即三级异或门的时延,与全加器相当。

本发明所采用5-3压缩器相较于现有技术的全加器结构,面积增大了约60%,但是在数据位为16比特的情况下速度快了10倍以上,而且对于数据位越多的计算,牺牲面积换来的速度提升更加显著。

本发明还提出一种实现CORDIC旋转模式下近似计算的方法实施例,采用上述实现CORDIC旋转模式下近似计算的装置运行,包括如下步骤:

S1:通过第一数据选择器201向X坐标进位项寄存器204存入初始值0以及向X坐标和值项寄存器205存入初始值x0,通过第二数据选择器202向Y坐标进位项寄存器206存入初始值0以及向Y坐标和值项寄存器207存入初始值x0,迭代记数器212数值置为0;

S2:X坐标进位项寄存器204的数值存入第一移位器208,X坐标和值项寄存器205的数值存入第二移位器209,Y坐标进位项寄存器206的数值存入第三移位器210,Y坐标和值项寄存器207的数值存入第四移位器211,第一移位器208、第二移位器209、第三移位器210和第四移位器211均向右移位,移位位数为迭代记数器212的当前数值;完成以上操作后,迭代计数器212数值加1;

S3:X坐标进位项寄存器204、X坐标和值项寄存器205、第三移位器210和第四移位器211的数值均输入第一压缩加法器213进行计算,Y坐标进位项寄存器206、Y坐标和值项寄存器207、第一移位器208和第二移位器209的数值均输入第二压缩加法器214进行计算,其中,第一移位器208、第二移位器209、第三移位器210和第四移位器211的数值均由方向控制器215根据当前迭代中要旋转的角度方向来确定正负号;

S4:第一压缩加法器213输出的当前X值进位项Xc(i+1)通过第一数据选择器201存入X坐标进位项寄存器204,第一压缩加法器213输出的当前X值和值项Xs(i+1)通过第一数据选择器201存入X坐标和值项寄存器205,第二压缩加法器214输出的当前Y值进位项Yc(i+1)通过第二数据选择器202存入Y坐标进位项寄存器206,第二压缩加法器214输出的当前Y值和值项Ys(i+1)通过第二数据选择器202存入Y坐标和值项寄存器207;

S5:重复步骤S2至S4,直至迭代记数器212数值等于装置处理的数据位数减2;

S6:使用普通进位加法器计算当前X值进位项Xc(n-1)与当前X值和值项Xs(n-1)之和作为最终X坐标值,以及使用普通进位加法器计算当前Y值进位项Yc(n-1)与当前Y值和值项Ys(n-1)之和作为最终Y坐标值。

其中,步骤S3中第一移位器208、第二移位器209、第三移位器210和第四移位器211的数值均由方向控制器215根据当前迭代中要旋转的角度方向来确定正负号,具体通过式(12)、式(13)进行计算来确定判决算子di的正负号。

需要说明的是,假设装置处理的数据位数为n,则步骤S2至S4重复进行(n-1)次,即迭代计数器212数值从0增加到(n-2)。在(n-1)次迭代中,使用和值项Xs、Ys和进位项Xc、Yc进行迭代,但是在第n次计算时,需要将它们相加合并计算出来得到一个值,即X坐标的最终值(Xs+Xc)和Y坐标的最终值(Ys+Yc)。在第n次计算时,可以使用普通进位加法器,该普通进位加法器可设置于图5中的压缩加法器213和压缩加法器214后面,普通进位加法器为现有技术,在图5中没有画出。为了提升普通进位加法器的运行时钟从而匹配使用5-3压缩器带来的益处,可在普通进位加法器插入寄存器流水线。在如图2所示的现有技术实现CORDIC算法的一次迭代运算硬件电路并不能使用在普通进位加法器插入寄存器流水线的方式提升系统运行时钟,这是因为图2中存在反馈电路(例如,从加法器108输出给数据选择器101),在正向链路插入延迟寄存器,则在反向链路必须插入等量的反延迟寄存器,而反延迟在物理上是不可实现的。

当然,本发明还可有其它多种实施方式,基于本实施方式,本领域的普通技术人员在没有做出任何创造性劳动的前提下所获得其他实施方式,都属于本发明所保护的范围。

- 一种实现CORDIC旋转模式下近似计算的装置和方法

- 基于混合模式CORDIC算法的低延时基本超越函数实现方法及装置