一种GaN HEMT器件中选择性去除GaN的方法及器件

文献发布时间:2023-06-19 10:32:14

技术领域

本发明涉及晶体管技术领域,特别是涉及一种GaN HEMT器件中选择性去除GaN的方法及器件。

背景技术

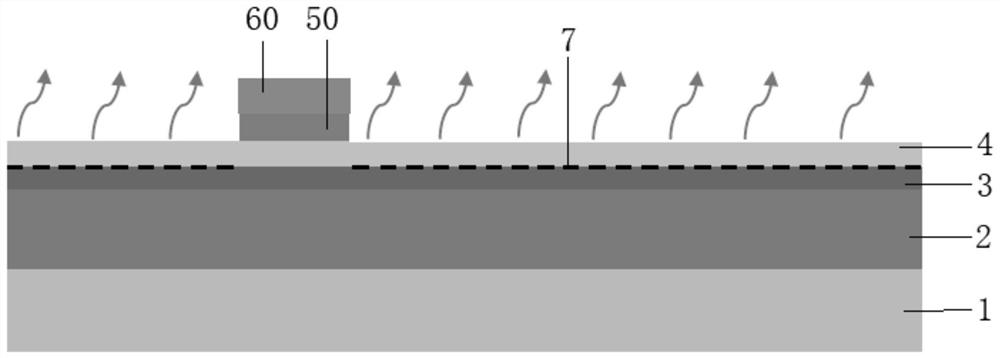

GaN HEMT(高电子迁移率晶体管)是一种常开型器件(阈值电压Vth<0V),其在GaN沟道层和AlGaN势垒层之间的界面区域存在二维电子气(2DEG),如图1所示。

目前,在商业产品中普遍采用最可靠的方法来实现常关型HEMT器件(Vth> 0V)为:在常开型HEMT结构的顶部使用p-GaN盖层来完全耗尽二维电子气(2DEG)。当p-GaN栅极偏压高于阈值电压(Vgs> Vth)或当p-GaN盖层被完全去除时,除栅极区域以外的区域中,二维电子气(2DEG)会重新形成,如图2所示。

通常使用干法蚀刻技术去除p-GaN盖层,直到蚀刻工艺通过数字蚀刻(在表面上形成薄的蚀刻副产物层并去除)等不同的选择到达下部的AlGaN势垒层处停止,终点检测(挥发性气体种类信号变化)和高蚀刻选择性(GaN-AlGaN蚀刻选择性>10:1)配方(例如,Cl

如图3a示出了一种常关“增强型”(Vth> 0V)p-GaN栅极HEMT的初始外延结构,其二维电子气(2DEG)在GaN沟道层与AlGaN势垒层之间的界面处完全耗尽。初始AlGaN层厚度5〜25nm,使得器件Vth在预定范围内,例如1〜2V。如图3b所示:通过标准光刻方法对p-GaN层进行构图,并按常规干法蚀刻去除掉除栅极区域以外的所有p-GaN层。但是,即使蚀刻时采用高GaN-AlGaN选择性蚀刻配方,在干法蚀刻过程中也不可避免地损坏AlGaN势垒表面。

发明内容

本发明的一个目的是提供一种GaN HEMT器件中选择性去除GaN的方法。

为达到上述目的,本发明采用的技术方案是:

一种GaN HEMT器件中选择性去除GaN的方法,包括以下步骤:

步骤1:

(1)、形成外延结构:在基层上生长缓冲层,在缓冲层上生长沟道层,在沟道层上生长势垒层,在势垒层上生长p-GaN层,

(2)、在p-GaN层上沉积钝化层,

步骤2:

对钝化层进行蚀刻,仅保留用于形成栅极的p-GaN区域上方的钝化区域,

步骤3:

对p-GaN层的进行热分解,直至除p-GaN区域以外的所有p-GaN层完全去除。

优选地,在步骤2后、步骤3前,先对除p-GaN区域以外的所有p-GaN层进行蚀刻,保留p-GaN层的厚度在5〜25nm之间。

优选地,所述的p-GaN层生长的厚度为50-200nm。

优选地,在步骤3中:对p-GaN层热分解的温度大于600℃。

优选地,在步骤3中:在真空或氢气或氮气或氮氢混合气的氛围下对p-GaN层的进行热分解。

优选地,在步骤3中:采用管式炉或RTP工具或MOCVD室对p-GaN层的进行热分解。

优选地,在步骤3中:通过轮廓仪或AFM扫描来测量p-GaN区域的高度,以确认已完全去除p-GaN层。

优选地,所述的缓冲层为GaN或AlGaN层,所述的沟道层为GaN层,所述的势垒层为AlGaN层。

优选地,所述的钝化层为SiO

本发明的另一个目的是提供一种器件。

为达到上述目的,本发明采用的技术方案是:

一种器件,其包括由所述的GaN HEMT器件中选择性去除GaN的方法形成的结构。

由于上述技术方案运用,本发明与现有技术相比具有下列优点:

本发明的方法通过热分解将GaN完全去除后,下面的AlGaN“停止”层保持不受损,从而保持二维电子气(2DEG)完整性,提升了器件的性能和质量。

附图说明

附图1为传统的常开“耗尽型”GaN HEMT;

附图2为常关“增强型”HEMT;

附图3a为常关“增强型”p-GaN栅极HEMT的初始外延结构;

附图3b为图3a中干法蚀刻后的结构;

附图4-1至4-4为本实施例中选择性去除GaN的工艺流程图;

附图5为p-GaN层的热分解速率与温度关系示意图。

以上附图中:

1、基层;2、缓冲层;3、沟道层;4、势垒层;5、p-GaN层;50、p-GaN区域;6、钝化层;60、钝化区域;7、二维电子气;8、栅极;9、源极;10、漏极。

具体实施方式

下面将结合附图对本发明的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

一种GaN HEMT器件中选择性去除GaN的方法,包括以下步骤:

步骤1:

(1)、形成外延结构,可以采用常关“增强型”p-GaN栅极HEMT的初始外延结构,具体为在基层1上生长缓冲层2,在缓冲层2上生长沟道层3,在沟道层3上生长势垒层4,在势垒层4上生长p-GaN层5。p-GaN层5生长的厚度为50-200nm。在本实施例中:缓冲层2为GaN或AlGaN层,沟道层3为GaN层,势垒层4为AlGaN。

(2)、在p-GaN层5上沉积钝化层6,钝化层为SiO

步骤2:

通过标准光刻对钝化层6进行构图,然后对钝化层6向下蚀刻到p-GaN层5表面,仅保留用于形成栅极的p-GaN区域50上方的钝化区域60,使二维电子气7在除p-GaN区域50下方以外的沟道层3与势垒层4之间的界面处出现,如图4-2所示。

步骤3:

对除p-GaN区域50以外的所有p-GaN层5进行干法蚀刻,保留p-GaN层5的厚度在5〜25nm之间,这样可以减少在步骤4中p-GaN层5完全热分解的时间,如图4-3所示。

步骤4:

将整个外延晶片放在真空或氢气或氮气或氮氢混合气的高温环境,其温度大于600℃,可以采用如管式炉、RTP工具、MOCVD室等,放置适当的时间,以热分解p-GaN层5,热分解过程中:可以通过轮廓仪或AFM(原子力显微镜)扫描来测量p-GaN区域50的高度,以确认已完全去除p-GaN,直至除p-GaN区域50以外的所有p-GaN层5完全去除,如图4-4所示。在该步骤之后,通过AFM扫描,势垒层4的AlGaN表面呈现出与刚生长的AlGaN表面(<0.3nm RMS厚度)相同的形态,无任何的表面损伤和损耗。

如图5所示:p-GaN层5的热分解速率随温度的升高而加快。

在本实施例中:Ga-N(形成焓-110kJ / mol)和Al-N(-318kJ)的键合能差 / mol)被用来实现从下方的AlGaN势垒层中完全去除GaN层(AlGaN中的Al%可以从10%到100%AlN变化),通过热分解将GaN完全去除后,下面的AlGaN“停止”层保持不受损,从而保持二维电子气(2DEG)完整性。

上述实施例只为说明本发明的技术构思及特点,其目的在于让熟悉此项技术的人士能够了解本发明的内容并据以实施,并不能以此限制本发明的保护范围。凡根据本发明精神实质所作的等效变化或修饰,都应涵盖在本发明的保护范围之内。

- 一种GaN HEMT器件中选择性去除GaN的方法及器件

- 一种基于再生长技术降低GaN HEMT器件欧姆接触电阻的方法及GaN HEMT器件