一种非易失性存储器及其验证读取方法

文献发布时间:2023-06-19 11:26:00

技术领域

本发明主要涉及半导体技术,尤其涉及一种非易失性存储器及其验证读取方法。

背景技术

半导体存储器可以包括易失性存储器(volatile memory,VM)和非易失性存储器(non-volatile memory,NVM)。易失性存储器通常可以作为操作系统或其他正在运行程序的临时存储介质,如内存。当电源关闭时,易失性存储器不能保留数据。非易失性存储器则用于存储需长期保留的数据,如硬盘。在突然断电或关闭电源的时候,非易失性存储器仍会保留数据。非易失性存储器的示例包括闪存(Flash memory)、只读存储器ROM或电可擦出可编程只读EEPROM等。

3D-Nand flash芯片,在越来越多的领域体现出广泛的应用价值。如智能手机、固态存储、SD Card和USB等方面。即将迎来的5G时代更是对云存储和云交互带来很多机会与挑战,这也就对存储器的性能提出了更高的要求。

发明内容

本发明要解决的技术问题是提供一种非易失性存储器及其验证读取方法,有效减小非易失性存储器在编程验证的预脉冲期间产生的峰值功耗。

为解决上述技术问题,本发明提供了一种非易失性存储器,包括:存储单元阵列,包括多条存储串,每条存储串包括多个存储单元、底部选择管和顶部选择管;多条字线,分别连接所述多个存储单元;串选择线,连接到所述顶部选择管;地选择线,连接到所述底部选择管;控制器,被配置为在验证读取阶段之前的预脉冲阶段中,控制地选择线使将选择的存储串和/或非选择的存储串的底部选择管关断;

控制字线使各存储串中的存储单元导通;

控制串选择线使选择的存储串中的顶部选择管和/或非选择的存储串中的顶部选择管关断以进行预脉冲。

在本发明的一实施例中,所述控制器还被配置为在所述预脉冲阶段中,控制串选择线使选择的存储串中的顶部选择管关断并使非选择的存储串中的顶部选择管导通以对选择存储串进行预脉冲。

在本发明的一实施例中,所述控制器还被配置在所述验证读取阶段中,将选择的存储串的底部选择管打开;关断非选择的存储串的顶部选择管、选通选择的存储串的顶部选择管;以及向非选中字线施加导通电压并向选中字线施加编程验证电压。

在本发明的一实施例中,所述多条存储单元字线分别与多个存储单元的栅极连接;所述串选择线与所述顶部选择管的栅极连接;所述地选择线与所述底部选择管的栅极连接。

在本发明的一实施例中,所述验证读取阶段紧接所述预脉冲阶段。

在本发明的一实施例中,所述非易失性存储器是3D NAND存储器。

本发明还提供一种非易失性存储器的验证读取方法,所述非易失性存储器包括存储单元阵列,所述存储单元阵列包括多条存储串,每条存储串包括多个存储单元、底部选择管和顶部选择管,所述非易失性存储器还包括多条字线、地选择线和串选择线;其中,所述多条字线分别连接所述多个存储单元,所述串选择线连接到所述顶部选择管,所述地选择线连接到所述底部选择管;所述方法包括在验证读取阶段之前的预脉冲阶段中,控制地选择线使将选择的存储串和/或非选择的存储串的底部选择管关断;控制字线使各存储串中的存储单元导通;控制串选择线使选择的存储串中的顶部选择管和/或非选择的存储串中的顶部选择管关断以进行预脉冲。

在本发明的一实施例中,所述方法在所述预脉冲阶段中,控制串选择线使选择的存储串中的顶部选择管关断并使非选择的存储串中的顶部选择管导通以对选择存储串进行预脉冲。

在本发明的一实施例中,所述方法还包括在所述验证读取阶段中,将选择的存储串的底部选择管打开;关断非选择的存储串的顶部选择管、选通选择的存储串的顶部选择管;以及向非选中字线施加导通电压并向选中字线施加编程验证电压。

本发明还提供一种非易失性存储器的编程方法,所述非易失性存储器包括存储单元阵列,所述存储单元阵列包括多个存储单元,所述方法包括以下步骤:

对所述多个存储单元施加编程信号;根据前述任一项所述的方法对所述多个存储单元进行编程验证。

与现有技术相比,本发明具有以下优点:在非易失性存储器的验证读取阶段之前的预脉冲期间,将选择串和/或非选择串的底部选择管关断,故在预脉冲阶段中,选择串或非选择串的存储单元的晶体管不导通,从而降低功耗。同时,本申请的技术方案中,在预脉冲阶段,对于非选择的存储串,选通非选中字线;对于选择的存储串,选通选中字线。因而本申请的技术方案亦可实现防止存储串之间的热载流子注入串扰。

附图说明

附图是为提供对本申请进一步的理解,它们被收录并构成本申请的一部分,附图示出了本申请的实施例,并与本说明书一起起到解释本发明原理的作用。附图中:

图1是本发明一实施例的非易失性存储器的功能框图。

图2是一种可用于本发明实施例的存储阵列的电路示意图。

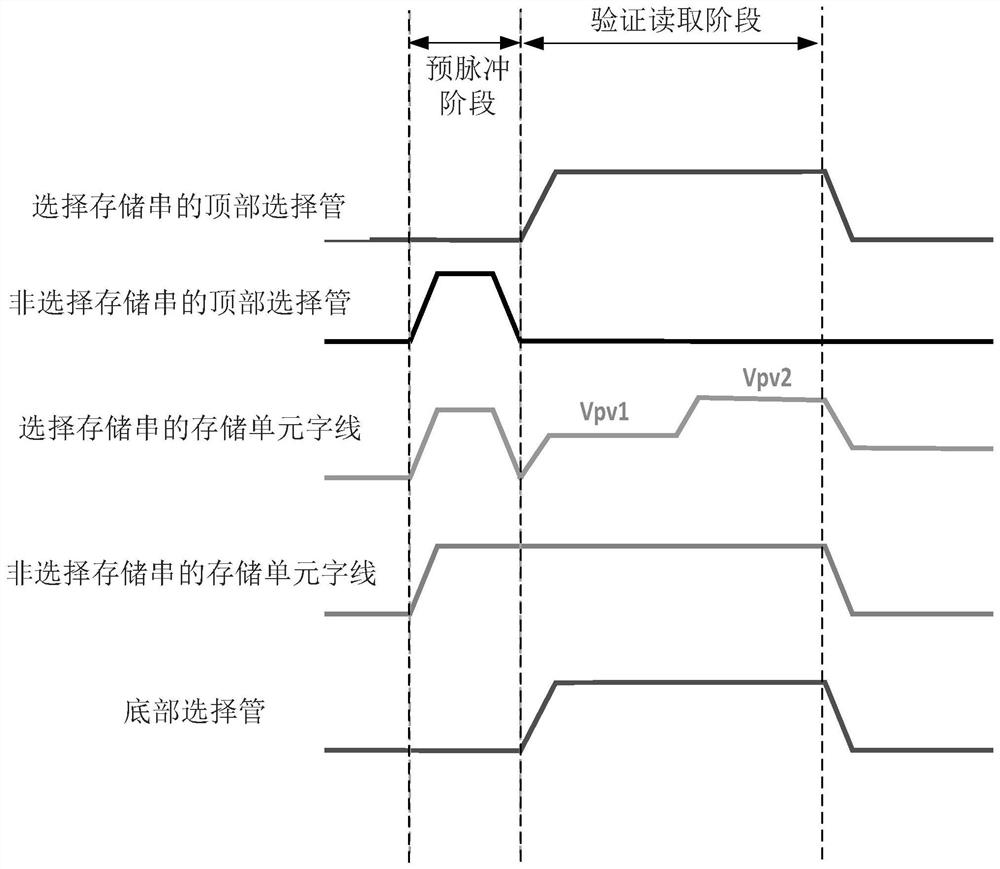

图3是本发明一实施例的非易失性存储器编程在预脉冲阶段和读取阶段的波形图。

图4是本发明一实施例的非易失性存储器在预脉冲阶段的功耗与先前技术方案在预脉冲阶段的功耗对比示意图。

具体实施方式

为让本发明的上述目的、特征和优点能更明显易懂,以下结合附图对本发明的具体实施方式作详细说明。

在下面的描述中阐述了很多具体细节以便于充分理解本发明,但是本发明还可以采用其它不同于在此描述的其它方式来实施,因此本发明不受下面公开的具体实施例的限制。

在本申请的描述中,需要理解的是,方位词如“前、后、上、下、左、右”、“横向、竖向、垂直、水平”和“顶、底”等所指示的方位或位置关系通常是基于附图所示的方位或位置关系,仅是为了便于描述本申请和简化描述,在未作相反说明的情况下,这些方位词并不指示和暗示所指的装置或元件必须具有特定的方位或者以特定的方位构造和操作,因此不能理解为对本申请保护范围的限制。

本申请中使用了流程图用来说明根据本申请的实施例的系统所执行的操作。应当理解的是,前面或下面操作不一定按照顺序来精确地执行。相反,可以按照倒序或同时处理各种步骤。同时,或将其他操作添加到这些过程中,或从这些过程移除某一步或数步操作。

本申请的实施例描述一种非易失性存储器及其编程方法。

图1是本发明一实施例的非易失性存储器的功能框图。参考图1所示,该非易失性存储器包括存储单元阵列11和控制器12。该存储单元阵列11包括多个存储单元,该存储单元可以是闪存存储单元,如3D NAND闪存存储单元。

在本实施例中,存储单元阵列11中包括的每个存储单元可以是其中存储1位数据的单极存储单元SLC,或者是其中可以存储2位或更多位数据的多级存储单元(MLC),如MLC、TLC和QLC等,或者是单级存储单元和多级存储单元的任意组合。

在本实施例中,存储单元阵列11中的存储单元可以连接到字线WL和位线BL。同时,存储单元阵列11还可以连接到其他的选择线如串选择线SSL、地选择线GSL等。具体地,存储单元阵列11可以经由字线WL或者选择线(SSL和/或GSL)连接到字线解码器15,并进一步地的连接到电压发生器16。存储单元阵列11可以经由位线BL连接到位线解码器13,并进一步地的连接到输入输出(I/O)电路14。控制器12分别与位线解码器13、I/O电路14、字线解码器15和电压发生器16相连接。

当需要对某一个或多个存储单元进行擦除、编程、读写或验证操作时,控制器12可以将该一个或多个存储单元的地址发送到位线解码器13和字线解码器15,再经由位线解码器13通过位线BL寻址,以及经由字线解码器15通过字线WL寻址。

在一些实施例中,位线解码器13和字线解码器15的功能可以由一个统一的地址解码器来实现。该地址解码器还可包括地址缓冲器等组件。

I/O电路14一方面可以从控制器12和/或外部接收数据并将所接收的数据存储到存储单元阵列11中以进行写操作,另一方面可以从存储单元阵列11中读取数据并将所读取的数据输出到控制器12和/或外部以进行读操作。

电压发生器16可以响应于来自控制器12的控制信号,生成用于对存储单元阵列11执行擦除、编程、读写和验证等操作的各种电压。具体地,电压发生器16可以生成字线电压,例如编程电压(或写入电压)、编程抑制电压、读取电压和验证电压等。电压发生器16可以生成位线电压,例如位线强制电压或禁止电压。

控制器12可以输出控制信号到位线解码器13、I/O电路14、字线解码器15和电压发生器16。例如,控制器12可以输出电压控制信号到电压发生器16,将字线地址输出到字线解码器15,将位线地址输出到位线解码器13,将写数据输出到I/O电路14并且从I/O电路14接收读出的数据。

在一些实施例中,控制器12控制位线解码器13选择某些位线BL,并控制字线解码器15选择某些位线WL,通过电压发生器16对这些位线BL和字线WL施加一定的电压。例如,在读取操作期间,可以将读取电压施加到所选的字线WL,对于禁止读取的存储单元,将读取禁止电压施加到未选择的位线BL。在编程操作期间,可以将编程电压和验证电压施加到所选的字线WL,并将编程抑制电压施加到未选择的位线BL。

本发明实施例的控制器12还可以包括处理器、I/O接口等组件。控制器12对位线解码器13、I/O电路14、字线解码器15和电压发生器16的控制逻辑并不限于上述内容。该控制器12还可以实现其他任何本领域技术人员可以理解的用于非易失性存储器的逻辑控制功能。

在一些实施例中,控制器12可以基于软件来指示存储单元阵列11执行所需的存储器操作。

存储单元阵列11可包括多条存储串(String,STR)。每条存储串包括多个存储单元(Memory Cell,MC),还包括底部选择管(BSG)和顶部选择管(TSG)。

图2是一种可用于本发明实施例的存储阵列的电路示意图。图2中,每个黑实心点代表一个存储单元。该存储阵列结构包括在三维空间内阵列排布的多个存储单元,构成多个存储串,位于同一个存储串内的存储单元的沟道在物理上连接。每一个存储串的顶部的晶体管为顶部选择管,顶部选择管连接至位线,存储串底部的晶体管为底部选择管,不同存储串之间通过顶部选择管和底部选择管区分。位于同一层内的多个存储单元组成存储行,位于不同存储串但位于同一存储行内的存储单元的栅极在物理上相连接,均连接至同一字线。

在对所述存储结构中的某一存储单元进行读取操作时,需要确定选中的存储单元所在的存储串以及所在的行,所述选中的存储单元所在的存储串作为选择存储串,所在行作为选中行。例如,要读取图2的选中存储单元201的信息,需要对串选择线和地选择线施加驱动电压,分别打开该选中存储单元所在选择存储串的顶部选择管1和底部选择管1,将所述存储单元所在行以外的非选中行的字线1和字线3施加导通电压,从而将该选择存储串的沟道导通;并且关断非选择存储串的顶部选择管2和底部选择管2,避免其他非选择存储串的沟道被导通;在选中行的字线2上加读取电压,对选中的存储单元内的信息进行读取。

待读取的存储单元所在的存储串作为选择存储串,待读取的存储单元所在存储行作为选中行,连接至选中行的字线作为选中字线。本申请的技术方案,在对存储单元进行读取之前,存在一个预脉冲阶段。

图3是本发明一实施例的非易失性存储器编程在预脉冲阶段和读取阶段的波形图。

在一实施例中,如图3所例示,在存储器的验证读取阶段之前的预脉冲阶段中,非易失性存储器的控制器被配置为:控制地选择线使将选择的存储串和/或非选择的存储串的底部选择管关断。在一些情形中,例如将选择的存储串和非选择的存储串的底部选择管都关断。同时,控制字线使各存储串中的存储单元导通,控制串选择线使选择的存储串中的顶部选择管和/或非选择的存储串中的顶部选择管关断以进行预脉冲。

在一些实施例中,在非易失性存储器的验证读取阶段,将选择的存储串的底部选择管打开(即导通);关断非选择的存储串的顶部选择管、选通选择的存储串的顶部选择管;以及向非选中字线施加导通电压并向选中字线施加施加编程验证电压,Vpv1、Vpv2例如为不同阶的编程验证电压。验证读取阶段可紧邻预脉冲阶段。在一实施例中,在验证读取阶段将选择的存储串和非选择的存储串的底部选择管打开,在实际的情形中,如果在之前的预脉冲阶段,选择的存储串或非选择的存储串的底部选择管已处于打开状态,则在验证读取阶段,仍维持其打开阶段即可。如果在之前的预脉冲阶段,选择的存储串或非选择的存储串皆处于关断状态,则在验证读取阶段,需将选择的存储串或非选择的存储串的底部选择管接变为打开状态,如图3的波形所示意。

选择的存储串即读取数据的存储单元201位于的存储串,其余则为非选择的存储串。故选择的存储串和非选择的存储串在非易失性存储器编程的过程中可随着读取数据的存储单元的变化而变化,但在一读取数据的特定时刻,此时的选择的存储串是确定的。

图4是本发明一实施例的非易失性存储器编程的功耗对比示意图。

本申请的技术方案中,在预脉冲(Prepulse)阶段中,因选择串和/或非选择串的底部选择管关断,具体例如可通过对连接到底部选择管栅极的地选择线的施加电压的控制来实现。故在预脉冲阶段中,选择串或非选择串的存储单元的晶体管不导通,从而降低功耗。同时,因本申请的技术方案中,在预脉冲阶段,对于非选择的存储串,选通非选中字线;对于选择的存储串,选通选中字线。即在预脉冲阶段,控制字线使各存储串中的存储单元导通。因而本申请的技术方案亦可实现防止存储串之间的热载流子注入(Hot CarrierInjection,HCI)串扰。

存储单元的导通并不意味着存储串的导通,存储串的导通还需要对顶部选择管和底部选择管作相应的控制。

经过预脉冲阶段的操作,对于存储阵列中的存储单元,在之后的验证读取阶段,其阈值电压不会轻易发生改变,保证非易失性存储器的读取性能。

而在先前的技术方案中,在读取阶段之前的预读取阶段(与本申请技术方案中的预脉冲阶段实际为同一时段),对于选择存储串和非选择存储串,底部选择管和顶部选择管皆会被打开(即导通),同时,非选择存储串的存储单元字线亦需置高,使多个存储单元对应的晶体管导通。此时,在预读取阶段,非易失存储器产生的功耗较大。对于移动设备,例如智能手机来说,电量的消耗就较大,从而降低设备的续航时间,影响用户的使用体验。

而本申请的技术方案,在非易失性存储器的读取阶段之前的预脉冲阶段,如前述,因选择串或非选择串的底部选择管关断。故在预脉冲阶段中,选择串或非选择串的存储单元的晶体管不导通,从而降低功耗。同时,本申请的技术方案中,在预脉冲阶段,对于非选择的存储串,选通非选中字线;对于选择的存储串,选通选中字线。因而本申请的技术方案亦可实现防止存储串之间的热载流子注入(Hot Carrier Injection,HCI)串扰。

图4是本申请一实施例的非易失性存储器在预脉冲阶段的功耗与先前技术方案在预脉冲阶段的功耗对比示意图。根据图4可得,与先前技术相比,本申请的技术方案在非易失性存储器编程验证的预脉冲阶段,表征峰值功耗的参数Icc的值明显减小。根据测试,在非易失性存储器编程验证的预脉冲阶段,在选择串和非选择串的底部选择管皆关断的情形,峰值功耗降低可达17%,从而降低设备的电量消耗,利于延长设备的续航时间,保证用户体验。

本申请还提供一种非易失性存储器的验证读取方法,非易失性存储器包括存储单元阵列,存储单元阵列包括多条存储串,每条存储串包括多个存储单元、底部选择管和顶部选择管,非易失性存储器还包括多条字线、地选择线和串选择线;其中,多条字线分别连接多个存储单元,串选择线连接到顶部选择管,地选择线连接到底部选择管。

在一些实施例中,非易失性存储器的验证读取方法,包括在验证读取阶段之前的预脉冲阶段中,控制地选择线使将选择的存储串和/或非选择的存储串的底部选择管关断;控制字线使各存储串中的存储单元导通;控制串选择线使选择的存储串中的顶部选择管和/或非选择的存储串中的顶部选择管关断以进行预脉冲。

在另一实施例中,非易失性存储器的编程验证方法,在预脉冲阶段中,控制串选择线使选择的存储串中的顶部选择管关断并使非选择的存储串中的顶部选择管导通以对选择存储串进行预脉冲。

在一实施例中,本申请的非易失性存储器的编程验证方法,还包括在验证读取阶段中,将选择的存储串的底部选择管打开;关断非选择的存储串的顶部选择管、选通选择的存储串的顶部选择管;以及向非选中字线施加导通电压并向选中字线施加编程验证电压。。

本申请的非易失性存储器的验证读取方法,可降低非易失性存储器编程验证的预脉冲阶段的峰值功耗,从而降低设备的电量消耗,利于延长设备的可使用时间。

本申请还提供一种非易失性存储器的编程方法,所述方法包括以下步骤:对所述多个存储单元施加编程信号;根据前述的方法对非易失性存储器的多个存储单元进行编程验证。

本申请的技术方案中,预脉冲阶段和验证读取阶段可合并称为编程验证阶段。编程验证阶段位于编程阶段之后。

上文已对基本概念做了描述,显然,对于本领域技术人员来说,上述发明披露仅仅作为示例,而并不构成对本申请的限定。虽然此处并没有明确说明,本领域技术人员可能会对本申请进行各种修改、改进和修正。该类修改、改进和修正在本申请中被建议,所以该类修改、改进、修正仍属于本申请示范实施例的精神和范围。

同时,本申请使用了特定词语来描述本申请的实施例。如“一个实施例”、“一实施例”、和/或“一些实施例”意指与本申请至少一个实施例相关的某一特征、结构或特点。因此,应强调并注意的是,本说明书中在不同位置两次或多次提及的“一实施例”或“一个实施例”或“一替代性实施例”并不一定是指同一实施例。此外,本申请的一个或多个实施例中的某些特征、结构或特点可以进行适当的组合。

应当注意的是,为了简化本申请披露的表述,从而帮助对一个或多个发明实施例的理解,前文对本申请实施例的描述中,有时会将多种特征归并至一个实施例、附图或对其的描述中。但是,这种披露方法并不意味着本申请对象所需要的特征比权利要求中提及的特征多。实际上,实施例的特征要少于上述披露的单个实施例的全部特征。

虽然本申请已参照当前的具体实施例来描述,但是本技术领域中的普通技术人员应当认识到,以上的实施例仅是用来说明本申请,在没有脱离本申请精神的情况下还可作出各种等效的变化或替换,因此,只要在本申请的实质精神范围内对上述实施例的变化、变型都将落在本申请的权利要求书的范围内。

- 一种非易失性存储器及其验证读取方法

- 具有使用多页的组合验证的加速的写入后读取的非易失性存储器的方法