地址扩展电路、通信接口芯片及通信系统

文献发布时间:2023-06-19 11:35:49

技术领域

本发明涉及集成电路技术领域,尤其涉及一种地址扩展电路、通信接口芯片及通信系统。

背景技术

内置集成电路(Inter-Integrated Circuit,I2C)是一种两线式通信接口,其被配置成使用包括串行数据线(Serial Data Line,SDA)和串行时钟线(Serial CLock,SCL)的总线来进行主机和从机之间的串行通信。其中,主机首先发出指令等信息,从机应答后,主机继续发送指令、数据等,或由从机发送数据然后主机应答。

从机可以是多个电子设备,为了通信时不发生冲突,每个从机都要有一个唯一的地址。常用的做法是,从机通过在地址引脚接电源或接地,实现确定的地址。而多个从机要实现多个地址,每个从机就需要有多个地址引脚,它们构成唯一的组合,从而形成与别的从机不同的地址。系统中从机的数目越多,需要的地址引脚就会越多,芯片尺寸则会增大,系统应用的成本也会相应增加。

公开号为CN109101448A的中国发明专利公开了一种地址扩展电路和具有该电路的I2C通信接口芯片,第一触发模块根据第一信号和第二信号产生触发信号,第一信号为延时后的地址信号,第二信号为时钟线接口端输出的时钟信号,第二触发模块根据第一信号、第二信号和触发信号产生第一地址信号,第三触发模块根据第一信号、第二信号和触发信号产生第二地址信号,第四触发模块根据第一信号、第二信号和触发信号产生第三地址信号,地址编码器根据第一地址信号、第二地址信号和第三地址信号生成地址编码,且当地址端分别与电源端、接地端、数据线接口端和时钟线接口端相连时,地址编码器生成的地址编码各不相同,从而可以在不增加端口的情况下,实现芯片地址的扩展。但该技术方案电路复杂,占用的芯片面积大,成本较高。

公开号为CN108959155A的中国发明专利公开了一种地址扩展电路和I2C通信接口芯片,包括第一触发模块至第三触发模块和地址编码器;第一触发模块根据第一信号和第二信号产生第一地址信号,第一信号为与地址端相连的延时电路输出的延时后的地址信号,第二信号为时钟线接口端输出的时钟信号;第二触发模块根据第一信号和第二信号产生第二地址信号;第三触发模块根据第一信号和第二信号产生第三地址信号;地址编码器根据第一地址信号、第二地址信号和第三地址信号生成地址编码,且当地址端分别与电源端、接地端、数据线接口端和时钟线接口端相连时,地址编码器生成的地址编码各不相同,从而可以在不增加端口的情况下,实现芯片地址的扩展。但该技术方案电路复杂,占用的芯片面积大,成本较高。

因此,有必要提供一种新型的地址扩展电路、通信接口芯片及通信系统以解决现有技术中存在的上述问题。

发明内容

本发明的目的在于提供一种地址扩展电路、通信接口芯片及通信系统,在不增加地址引脚的前提下,实现从机地址扩展。

为了实现上述目的,本发明的所述地址扩展电路,包括:

第一触发模块,用于接收地址端口信号,以产生第一地址信号;

第二触发模块,用于接收串行数据线端口信号和所述地址端口信号,以产生第二地址信号;以及

编码模块,与所述第一触发模块和所述第二触发模块连接,以根据所述第一地址信号和所述第二地址信号生成芯片地址编码。

所述地址扩展电路的有益效果在于:第一触发模块用于接收地址端口信号,以产生第一地址信号,第二触发模块用于接收串行数据线端口信号和所述地址端口信号,以产生第二地址信号,编码模块与所述第一触发模块和所述第二触发模块连接,以根据所述第一地址信号和所述第二地址信号生成芯片地址编码,能够在不增加地址引脚的前提下,实现从机地址扩展。

优选地,所述第一触发模块包括第一延时单元、第一异或门和第一触发器,所述第一延时单元的输出端与所述第一异或门的第一输入端连接,所述第一延时单元的输入端和所述第一异或门的第二输入端用于接收所述地址端口信号,所述第一异或门的输出端与所述第一触发器的时钟端连接,所述第一触发器的数据端接电源电压,所述第一触发器的输出端输出所述第一地址信号。其有益效果在于:便于根据地址端口信号生成第一地址信号。

进一步优选地,所述第一触发器为上升沿触发的异步复位触发器。

优选地,所述第二触发模块包括第一反相器、第二延时单元和第二触发器,所述第一反相器的输入端用于接收所述地址端口信号,所述第一反相器的输出端接所述第二延时单元的输入端,所述第二延时单元的输出端接所述第二触发器的数据端,所述第二触发器的时钟端用于接收所述串行数据线端口信号,所述第二触发器的输出端输出所述第二地址信号。其有益效果在于:便于根据地址端口信号和串行数据线端口信号生成第二地址信号。

进一步优选地,所述第二触发器为下降沿触发的异步复位触发器。

优选地,所述编码模块包括第二异或门、第二反相器和第三反相器,所述第二异或门的第一输入端用于接收所述第一地址信号,所述第二异或门的第二输入端用于接收所述第二地址信号,所述第二异或门的输出端与所述第二反相器的输入端连接,所述第二反相器的输出端输出第一芯片地址编码,所述第三反相器的输入端用于接收所述第二地址信号,所述第三反相器的输出端输出第二芯片地址编码。其有益效果在于:便于根据第一地址信号和第二地址信号生成第一芯片地址编码和第二芯片地址编码。

本发明还提供了一种通信接口芯片,包括至少一个所述地址扩展电路。

所述通信接口芯片的有益效果在于:包括至少一个所述地址扩展电路,能够在不增加地址引脚的前提下,实现从机地址扩展。

优选地,所述通信接口芯片还包括电源端口、地电平端口、串行数据线端口、串行时钟线端口和至少一个地址端口,所述地址端口与所述电源端口、所述地电平端口、所述串行数据线端口或所述串行时钟线端口中的任意一个端口连接,以向所述地址扩展电路传输地址端口信号。其有益效果在于:能够生成四组芯片地址编码。

进一步优选地,所述地址扩展电路的数量与所述地址端口的数量相适配。

本发明还提供了一种通信系统,包括:

主机;

至少一个从机,所述从机包括所述通信接口芯片;以及

I2C总线,用于连接所述主机和所述从机,以实现所述主机和所述从机之间的通讯。

所述通信系统的有益效果在于:所述从机包括所述通信接口芯片,能够在不增加地址引脚的前提下,实现从机地址扩展。

优选地,所述I2C总线包括串行数据线和串行时钟线,所述串行数据线连接所述主机的串行数据线端口和所述从机的串行数据线端口,所述串行时钟线连接所述主机的串行时钟线端口和所述从机的串行时钟线端口。其有益效果在于:实现了主机与从机之间的通信连接。

进一步优选地,所述通信系统还包括上拉电阻,所述串行数据线和所述串行时钟线分别通过所述上拉电阻与电源电压连接。

附图说明

图1为本发明一些实施例中通信系统的结构示意图;

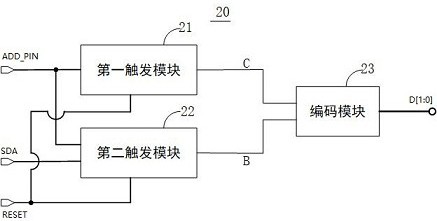

图2为本发明一些实施例中地址扩展电路的电路框图;

图3为本发明一些实施例中地址扩展电路的电路图;

图4为本发明一些实施例中地址端口与电源端口连接时地址扩展电路的时序图;

图5为本发明一些实施例中地址端口与地电平端口连接时地址扩展电路的时序图;

图6为本发明一些实施例中地址端口与串行数据线端口连接时地址扩展电路的时序图;

图7为本发明一些实施例中地址端口与串行时钟线端口连接时地址扩展电路的时序图。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。除非另外定义,此处使用的技术术语或者科学术语应当为本发明所属领域内具有一般技能的人士所理解的通常意义。本文中使用的“包括”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。

针对现有技术存在的问题,本发明的实施例提供了一种通信系统,所述通信系统包括主机、至少一个从机和I2C总线,所述I2C总线用于连接所述主机和所述从机,以实现所述主机和所述从机之间的通讯,所述从机包括通信接口芯片。

一些实施例中,所述串行总线包括串行数据线和串行时钟线,所述主机和所述从机均具有串行数据线端口和串行时钟线端口,所述串行数据线连接所述主机的串行数据线端口和所述从机的串行数据线端口,所述串行时钟线连接所述主机的串行时钟线端口和所述从机的串行时钟线端口。

一些实施例中,所述串行数据线和所述串行时钟线分别通过上拉电阻与电源电压连接。

图1为本发明一些实施例中通信系统的结构示意图。参照图1,所述通信系统10包括主机11、第一从机12、第二从机13和I2C总线(图中未标示)。

一些实施例中,所述主机具有第一串行数据线端口和第一串行时钟线端口。

一些实施例中,所述第一从机具有第二串行数据线端口和第二串行时钟线端口。

一些实施例中,所述第二从机具有第三串行数据线端口和第三串行时钟线端口。

一些实施例中,所述I2C总线包括串行数据线和串行时钟线,所述串行数据线包括第一串行数据线和第二串行数据线,所述串行时钟线包括第一串行时钟线和第二串行时钟线。

一些实施例中,参照图1,所述第一串行数据线121的一端连接所述主机11的第一串行数据线端口,所述第一串行数据线121的另一端连接所述第一从机12的第二串行数据线端口,所述第二串行数据线131的一端连接于所述第一串行数据线121的第一节点1211,所述第二串行数据线131的另一端连接所述第二从机的第三串行数据线端口,所述第一串行数据线121和所述第二串行数据线131构成所述串行数据线。

一些实施例中,参照图1,所述第一串行时钟线122的一端与所述主机11第一串行时钟线端口连接,所述第一串行时钟线122的另一端与所述第一从机12的第二串行时钟线端口连接,所述第二串行时钟线132的一端连接于所述第一串行时钟线122的第二节点1221,所述第二串行时钟线132的另一端连接所述第二从机13包括第三串行时钟线端口,所述第一串行时钟线122和所述第二串行时钟线132构成所述串行时钟线。

一些实施例中,参照图1,所述上拉电阻包括第一上拉电阻1212和第二上拉电阻1222,所述第一上拉电阻1212的一端连接于所述第一串行数据线121的第三节点1213,所述第三节点1213位于所述第一节点1211和所述第一串行数据线端口之间,所述第一上拉电阻1212的另一端接电源电压,所述第二上拉电阻1222的一端连接于所述第一串行时钟线122的第四节点1223,所述第四节点1223位于所述第二节点1221和所述第一串行时钟线端口之间,所述第二上拉电阻1222的另一端接电源电压。

一些实施例中,所述从机包括通信接口芯片,所述通信接口芯片包括至少一个地址扩展电路。

一些实施例中,所述通信接口芯片还包括电源端口、地电平端口、串行数据线端口、串行时钟线端口和至少一个地址端口,所述地址端口用于与所述电源端口、所述地电平端口、所述串行数据线端口或所述串行时钟线端口中的任意一个端口连接,以向所述地址扩展电路传输地址端口信号。具体地,所述通信接口芯片的串行数据线端口即所述从机的串行数据线端口,所述通信接口芯片的串行时钟线端口即所述从机的串行时钟线端口。

一些实施例中,所述地址端口与所述电源端口、所述地电平端口、所述串行数据线端口或所述串行时钟线端口共4种连接方式,可以得到4个芯片地址编码。当增加所述地址端口的数量时,例如n个所述地址端口,则可以实现4

一些实施例中,所述地址扩展电路的数量与所述地址端口的数量相适配。具体地,所述地址扩展电路的数量等于所述地址端口的数量。

图2为本发明一些实施例中地址扩展电路的电路框图。参照图2,所述地址扩展电路20包括:

第一触发模块21,用于接收地址端口信号ADD_PIN,以产生第一地址信号;

第二触发模块22,用于接收串行数据线端口信号SDA和所述地址端口信号ADD_PIN,以产生第二地址信号;以及

编码模块23,与所述第一触发模块21和所述第二触发模块22连接,以根据所述第一地址信号和所述第二地址信号生成芯片地址编码,所述芯片地址编码包括第一芯片地址编码和第二芯片地址编码。具体地,所述地址端口信号为ADD_PIN,所述第一地址信号为C,所述第二地址信号为B,所述芯片地址编码为ID[1:0],所述第一芯片地址编码为ID[1]和所述第二芯片地址编码为ID[0]。

一些实施例中,参照图2,所述第一触发模块21和所述第二触发模块22还均具有复位端,用于接收复位信号RESET。

图3为本发明一些实施例中地址扩展电路的电路图。参照图3,所述第一触发模块21包括第一延时单元211、第一异或门212和第一触发器213,所述第一延时单元211的输出端与所述第一异或门212的第一输入端连接,所述第一延时单元21的输入端和所述第一异或门212的第二输入端接所述地址端口信号ADD_PIN,所述第一异或门212的输出端与所述第一触发器的时钟端连接,所述第一触发器213的数据端接电源电压,所述第一触发器213的输出端输出所述第一地址信号,所述第一触发器213的复位端RST即所述第一触发模块的复位端,用于接收复位信号RESET。具体地,所述第一延时单元211的输入端和所述第一异或门212的第二输入端均与所述地址端口(图中未示出)连接,所述第一触发器213为上升沿触发的异步复位触发器。

一些实施例中,参照图3,所述第二触发模块22包括第一反相器221、第二延时单元222和第二触发器223,所述第一反相器221的输入端用于接收所述地址端口信号ADD_PIN,所述第一反相器221的输出端接所述第二延时单元222的输入端,所述第二延时单元222的输出端接所述第二触发器223的数据端,所述第二触发器223的时钟端接所述串行数据线端口信号SDA,所述第二触发器223的复位端RST即所述第二出发模块的复位端,用于接收复位信号RESET,所述第二触发器223的输出端输出所述第二地址信号。具体地,所述第一反相器221的输入端与所述地址端口(图中未示出)连接,所述第二触发器223的时钟端与所述串行数据线端口(图中未示出)连接,所述第二触发器223为下降沿触发的异步复位触发器。

一些实施例中,参照图3,所述编码模块23包括第二异或门231、第二反相器232和第三反相器233,所述第二异或门231的第一输入端用于接收所述第一地址信号,所述第二异或门231的第二输入端用于接收所述第二地址信号,所述第二异或门231的输出端与所述第二反相器232的输入端连接,所述第二反相器232的输出端输出第一芯片地址编码,所述第三反相器233的输入端用于接收所述第二地址信号,所述第三反相器233的输出端输出第二芯片地址编码。具体地,所述第二异或门231的第一输入端与所述第一触发器213的输出端连接,所述第二异或门231的第二输入端与所述第二触发器223的输出端连接,所述第三反相器233的输入端与所述第二触发器223的输出端连接。图3中,delay表示延时单元,XOR表示异或门,X表示第一输入端,Y表示第二输入端,Z表示输出端。

一些实施例中,所述第一触发器和所述第二触发器还均具有复位端,用于接收复位信号。当所述通信接口芯片上电复位时,向所述第一触发器和所述第二触发器发送复位信号,以对所述第一触发器和所述第二触发器进行复位,所述第一触发器和所述第二触发器复位后,所述第一触发器输出的第一地址信号为地电平0,所述第二触发器输出的第二地址信号为地电平0。

图4为本发明一些实施例中地址端口与电源端口连接时地址扩展电路的时序图。参照图4,图中SCL为所述串行时钟线端口信号,用于表示时钟变化,SDA为所述串行数据线端口信号,C为所述第一地址信号,ID[1]为所述第一芯片地址编码,ID[0]为所述第二芯片地址编码。所述地址端口与所述地电平端口连接时,所述第一地址信号一直为地电平,所述第二地址信号在所述串行数据线端口信号的下降沿后变为高电平,输入所述编码模块后,所述编码模块输出所述第一芯片地址编码为0,输出所述第二芯片地址编码为0。其中,0表示逻辑低电平。

图5为本发明一些实施例中地址端口与地电平端口连接时地址扩展电路的时序图。参照图5,图中SCL为所述串行时钟线端口信号,用于表示时钟变化,SDA为所述串行数据线端口信号,C为所述第一地址信号,ID[1]为所述第一芯片地址编码,ID[0]为所述第二芯片地址编码。所述地址端口与所述电源端口连接,所述第一地址信号一直为低电平,所述第二地址信号一直为低电平,输入所述编码模块后,所述编码模块输出第一芯片地址编码为1,输出所述第二芯片地址编码为1。其中,1表示逻辑高电平。

图6为本发明一些实施例中地址端口与串行数据线端口连接时地址扩展电路的时序图。参照图6,图中SCL为所述串行时钟线端口信号,用于表示时钟变化,SDA为所述串行数据线端口信号,C为所述第一地址信号,ID[1]为所述第一芯片地址编码,ID[0]为所述第二芯片地址编码。所述地址端口与所述串行数据线端口连接,所述第一地址信号在所述串行数据线端口信号的上升沿后变为高电平,所述第二地址信号一直为低电平,输入所述编码模块后,所述编码模块输出第一芯片地址编码为0,输出所述第二芯片地址编码为1。

图7为本发明一些实施例中地址端口与串行时钟线端口连接时地址扩展电路的时序图。参照图7,图中SCL为所述串行时钟线端口信号,用于表示时钟变化,SDA为所述串行数据线端口信号,C为所述第一地址信号,ID[1]为所述第一芯片地址编码,ID[0]为所述第二芯片地址编码。所述地址端口与所述串行时钟线端口连接,所述第一地址信号在所述串行数据线端口信号变为上升沿后变为高电平,所述第二地址信号在所述串行数据线端口信号的下降沿后变为高电平,输入所述编码模块后,所述编码模块输出第一芯片地址编码为1,输出所述第二芯片地址编码为0。

一些实施例中,在经过所述串行数据线端口信号和所述串行时钟线端口信号的变化后,所述第一芯片地址编码和所述第二芯片地址编码会被锁定,其后所述串行数据线端口信号和所述串行时钟线端口信号的改变均不会再次改变所述第一芯片地址编码和所述第二芯片地址编码。其中,所述串行数据线端口信号和所述串行时钟线端口信号的变化是I2C通信系统中必然会发生的。

虽然在上文中详细说明了本发明的实施方式,但是对于本领域的技术人员来说显而易见的是,能够对这些实施方式进行各种修改和变化。但是,应理解,这种修改和变化都属于权利要求书中所述的本发明的范围和精神之内。而且,在此说明的本发明可有其它的实施方式,并且可通过多种方式实施或实现。

- 地址扩展电路、通信接口芯片及通信系统

- 地址扩展电路和具有该电路的I2C通信接口芯片