一种智能阻抗分析式回收数据的方法以及系统

文献发布时间:2024-01-17 01:26:37

技术领域

本发明涉及一种数据回读领域,特别是涉及一种智能阻抗分析式回收数据的方法以及系统。

背景技术

弹载飞行结束后,有效信息存放于存储器内。通常情况下,存储器的落地环境都比较恶劣。如果不对存储器进行高效快速的系统阻抗分析,就贸然给存储器加电直接进行读数操作。读数过程中的操作风险极大,可能会导致不可逆的硬件损坏甚至造成数据的永久性丢失。

以太网硬件系统跨时钟域架构的设计,导致在线速条件下长时间的测试会出现丢包现象。针对该现象,在标准UDP协议的基础上加入了重传机制,实现对以太网链路的优化,增强读数系统的可靠性。

目前,市面上存在大量阻抗测试设备。比如,南京邮电大学陈禹,渠吉庆等人研究的网络阻抗测试仪,能够在误差2%之内测出负载的阻抗模值。但是,类似的阻抗测试设备仅能实现单路的负载阻抗测试,而存储器系统的阻抗测试负载工作量大,单一阻抗测试耗费周期长、系统智能化程度低。需要有专门的航天配套设备,针对特定的存储器硬件电路,设计出配套的智能阻抗测试设备,能够实现多路负载同时测试,实现阻抗测试功能的智能化。

目前测试阻抗和数据回读均需要分开进行,操作繁琐,器件之间并不能友好的兼容,造成工作效率低。

综上所述可以看出,如何将阻抗测试和数据回读实现一体化控制是目前有待解决的问题。

发明内容

本发明的目的是提供一种智能阻抗分析式回收数据的方法以及系统,解决了现有技术中测试阻抗和数据回读需要分开进行的弊端。

为解决上述技术问题,本发明提供一种智能阻抗分析式回收数据的方法,包括:

设置一阻抗测试指令;

将所述阻抗测试指令通过以太网收发器传输至FPGA中,控制所述FPGA进行阻抗测试;

将所述测试阻抗指令输入阻抗测试模块中,激活正向和反向测试指令;

根据所述正向和反向测试指令控制阻抗测试电路对待测负载进行智能正向、反向电阻测试,直至达到预设精度值的正向电阻值和反向电阻值;

判断所述正向电阻值和所述反向电阻值是否满足正常阻抗范围;

若不满足,则所述FPGA反馈所述待测负载异常;

若满足,则设置数据回读指令传输至所述FPGA中,并根据所述数据回读指令读取所述待测负载的数据。

优选地,所述根据所述正向和反向测试指令控制阻抗测试电路对待测负载进行智能正向、反向电阻测试,直至达到预设精度值的正向电阻值和反向电阻值包括:

S1:利用所述阻抗测试电路的最低量程对所述待测负载进行正反向电阻测试,得到正向和反向电阻值;

S2:判断所述正向和反向电阻值的精度是否满足预设精度;

S3:若不满足,则增加所述阻抗测试电路的测量量程,重新进行正向、反向电阻测试,将测试结果返回步骤S2中进行重新判断;

S4:若满足,则将所述正向电阻值和所述反向电阻值反馈至所述FPGA。

优选地,将所述正向电阻值和所述反向电阻值上传至所述FPGA中,通过分压法计算得到待测负载的阻抗值;

将所述待测负载的阻抗值反馈,并判断所述待测负载的阻抗值是否满足正常阻抗范围。

优选地,所述设置数据回读指令传输至所述FPGA中,并根据所述数据回读指令读取所述待测负载的数据包括:

当所述待测负载的阻抗值满足所述正常阻抗范围时;

控制所述FPGA给所述待测负载供电,并设置所述数据回读指令通过所述FPGA发送至所述待测负载;

提取所述待测负载的数据至所述FPGA;

控制所述FPGA通过所述以太网收发器上传所述待测负载的数据。

优选地,所述控制所述FPGA通过所述以太网收发器上传所述待测负载的数据包括:

控制所述FPGA中的FIFO模块读取所述待测负载的数据;

通过所述以太网收发器将所述待测负载的数据进行分批上传;

校验每次上传的数据是否连续;

若所述上传的数据连续,则继续检测下次上传的数据;

若所述上传的数据不连续,则触发重传指令重新读取本次上传的数据,再校验上传数据是否连续,当连续预设次数重传失败,则停止数据上传,并反馈回读异常。

优选地,所述若所述上传的数据连续,则继续检测下次上传的数据后还包括:

当达到回读预设数据量时,判断所述FPGA是否为回读状态;

若所述FPGA是所述回读状态,则继续上传数据;

若所述FPGA不是所述回读状态,则停止上传数据,等待下一次数据回读指令。

本发明还提供了一种智能阻抗分析式回收数据的系统,包括:

上位机,用于发送阻抗测试指令和数据回读指令;

以太网收发器,用于传输所述上位机发送的阻抗测试指令和数据回读指令,并将测试的阻抗数据和回读的数据上传至所述上位机;

FPGA模块,用于接收所述阻抗测试指令和数据回读指令,并根据所述阻抗测试指令进行智能阻抗测试,根据所述数据回读指令进行数据回读,所述FPGA模块包括:

发送单元,用于接收所述数据回读指令,发送读取数据指令;

解码单元,用于将待测负载中的数据进行解码;

接收单元,用于接收所述解码单元解码之后的数据;

FIFO单元,用于将所述接收单元中的数据按照预设排序方式上传至所述以太网收发器中;

阻抗测试电路,用于接收阻抗测试指令,智能测试待测负载的阻抗值,并将阻抗值反馈至所述FPGA中。

优选地,所述阻抗测试电路包括:

电源模块,所述电源模块包括供电电源和多个不同阻值的电阻;

矩阵开关,所述矩阵开关设置多组测试端口,每组端口设置两个端口,所述每个端口均并联设置第一控制开关和第二控制开关;

其中,所有第一控制开关均连接所述电压模块的正极,所有第二控制开关均连接所述电压模块的负极;

电压采集装置,所述电压采集模块的正极连接所述电源模块的正极,所述电压采集模块的负极连接所述电源模块的负极,与所述矩阵开关并联。

优选地,所述发送模块采用RS-422发送模块。

优选地,所述以太网收发器和所述FPGA模块之间还包括:时钟模块和复位模块。

本发明所提供的一种智能阻抗分析式回收数据的方法,将数据回读指令通过以太网收发器传输至FPGA中,FPGA启动测试阻抗指令,阻抗测试模块接收阻抗测试指令,对待测负载进行正向反向测试,直至达准确精度的阻值,并判断待测负载的阻值是否满足正常阻抗范围;当待测负载的阻抗满足正常阻抗范围时,FPGA再输出数据回读指令,提取待测负载中的数据,将所提取的数据上传,实现数据回读的过程。本发明将智能阻抗测试与数据回读结合起来,不在需要测试阻抗与数据回读进行分布,对硬件起到很好的保护作用,避免了不必要的经济损失,提高工作效率以及稳定性。

附图说明

为了更清楚的说明本发明实施例或现有技术的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单的介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

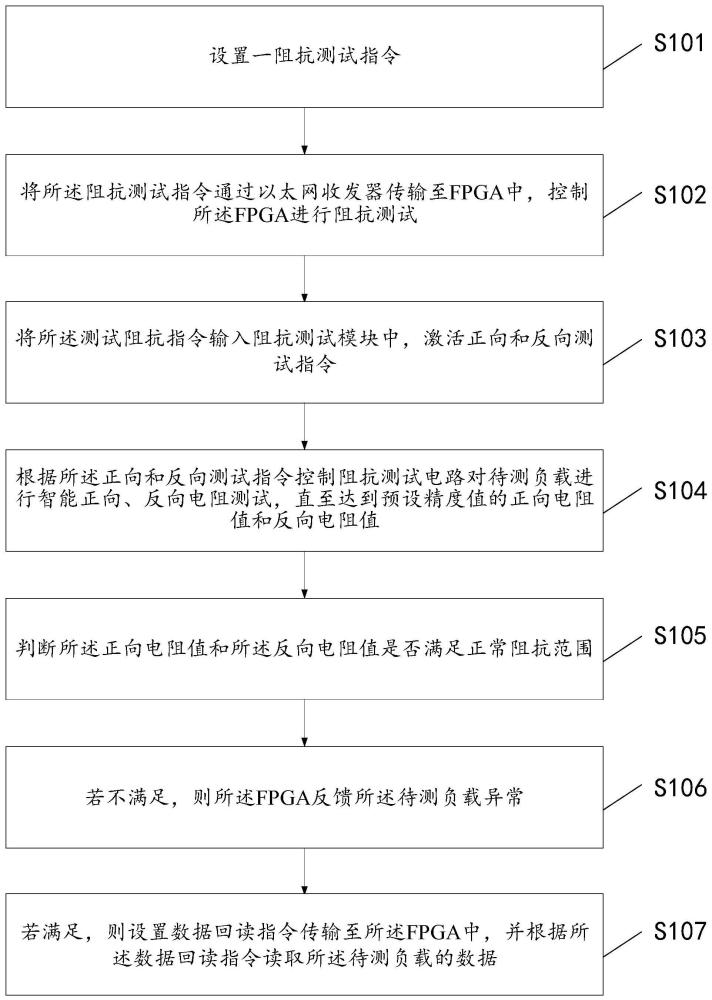

图1为本发明所提供的智能阻抗分析式回收数据的方法的第一种具体实施例的流程图;

图2为本发明所提供的智能阻抗分析式回收数据的方法的第二种具体实施例的流程图;

图3为本发明所提供的阻抗测试软件的步骤流程图;

图4为本发明所提供的智能阻抗分析式回收数据的系统的结构框图;

图5为本发明所提供的阻抗测试电路的原理图;

图6为本发明所提供的FPGA内部系统框图;

图7为本发明所提供的以太网接口示意图。

具体实施方式

本发明的核心是提供一种智能阻抗分析式回收数据的方法,通过智能检测待测负载的阻抗值,对待测软件起到了保护作用,然后再进行数据回读,将数据回读至上位机中,进行数据分析。

为了使本技术领域的人员更好地理解本发明方案,下面结合附图和具体实施方式对本发明作进一步的详细说明。显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

请参考图1,图1为本发明所提供的智能阻抗分析式回收数据的方法的第一种具体实施例的流程图;具体操作步骤如下:

步骤S101:设置一阻抗测试指令;

步骤S102:将所述阻抗测试指令通过以太网收发器传输至FPGA中,控制所述FPGA进行阻抗测试;

步骤S103:将所述测试阻抗指令输入阻抗测试模块中,激活正向和反向测试指令;

步骤S104:根据所述正向和反向测试指令控制阻抗测试电路对待测负载进行智能正向、反向电阻测试,直至达到预设精度值的正向电阻值和反向电阻值;

步骤S105:判断所述正向电阻值和所述反向电阻值是否满足正常阻抗范围;

步骤S106:若不满足,则所述FPGA反馈所述待测负载异常;

步骤S107:若满足,则设置数据回读指令传输至所述FPGA中,并根据所述数据回读指令读取所述待测负载的数据。

在本实施例中,首先将数据回读指令通过以太网收发器传输至FPGA中,FPGA启动测试阻抗指令,阻抗测试模块接收阻抗测试指令,对待测负载进行正向反向测试,直至达准确精度的阻值,并判断待测负载的阻值是否满足正常阻抗范围;当待测负载的阻抗满足正常阻抗范围时,FPGA再输出数据回读指令,提取待测负载中的数据,将所提取的数据上传,实现数据回读的过程。本发明将智能阻抗测试与数据回读结合起来,不在需要测试阻抗与数据回读进行分布,对硬件起到很好的保护作用,避免了不必要的经济损失,提高工作效率以及稳定性。

基于上述实施例,在本实施例中详细说明了如何实现智能阻抗测试以及数据回读的步骤,请参考图2,图2为本发明所提供的智能阻抗分析式回收数据的方法的第二种具体实施例的流程图;具体步骤如下:

步骤S201:利用阻抗测试电路的最低量程对所述待测负载进行正反向电阻测试,得到正向和反向电阻值;

阻抗测试电路接收FPGA发送的阻抗测试指令,将待测负载接入阻抗测试电路中,同时可接入多个负载,同时实现多组负载测量。

将阻抗测试电路设置为最低测试量程,然后闭合正向测试电路的开关,得到一待测负载的正向电阻,然后再对下一个待测负载测试,依次控制开关闭合,实现对多个负载的正向阻抗检测;然后再控制反向测试开关,采用上述原理,实现反向阻抗测试,得到待测负载的反向电阻。

步骤S202:判断正向和反向电阻值的精度是否满足预设精度;

步骤S203:若不满足,则增加阻抗测试电路的测量量程,重新进行正向、反向电阻测试,将测试结果返回步骤S202中进行重新判断;

步骤S204:若满足,则将所述正向电阻值和所述反向电阻值反馈至所述FPGA;

判断待测负载的精度是否满足1%的精度值,若不满足,则切换量程,然后再对需要检测的待测负载进行正向反向电阻检测,直至检测精度满足1%,或者是达到最大阻值。

然后将所有待测负载的阻值反馈至FPGA中以及通过以太网上传至上位机,阻抗测试步骤流程图如图3所示。

步骤S205:当所述待测负载的电阻值满足所述正常阻抗范围时;

步骤S206:控制所述FPGA给所述待测负载供电,并控制所述FPGA发送读取数据指令至所述待测负载;

然后FPGA判断每一个待测负载的阻值是否符合正常阻抗范围;若不符合,则反馈数据阻抗异常;若符合,则启动数据回读指令进行数据回读。

步骤S207:提取所述待测负载的数据至所述FPGA;

步骤S208:控制所述FPGA通过所述以太网收发器上传所述待测负载的数据。

控制所述FPGA中的FIFO模块读取所述待测负载的数据;

通过所述以太网收发器将所述待测负载的数据进行分批上传;

校验每次上传的数据是否连续;

若所述上传的数据连续,则继续检测下次上传的数据;

若所述上传的数据不连续,则触发重传指令重新读取所述待测负载的数据,再校验上传数据是否连续,当连续预设次数重传失败,则停止数据上传,并反馈回读异常;

在所述上传的数据的过程中,每达到回读预设数据量判断所述FPGA是否为回读状态;

若所述FPGA是所述回读状态,则继续上传数据;

若所述FPGA不是所述回读状态,则停止上传数据,等待下一次数据回读指令。

上位机下发“开始读数”指令的状态下,每下发一次数据请求f_req,回读数据量为64k,数据由FIFO读出写入RAM,通过以太网接口将数据读回。上位机采取抓包的方式进行数据判断,每抓取到64k数据对帧计数进行一次校验。如果校验失败,则触发重传机制,此时重传指令f_cc_req有效,重新在RAM中读取64k数据再次校验,若仍旧不连续,则继续触发重传机制,连续十次重传校验失败,立即停止下载数据。如果数据校验正常,则进行下一次数据请求,继续读64k数据,完成一次数据请求将f_wr_ram_end_flag标志位拉高一次。与此同时,在64k数据读取的过程中,每回读8k判断一次是否还在开始读数状态,若指令无效,则停止读数,等待上位机下达下一次开始读数指令。

在本实施例中,介绍了本发明智能测试阻抗的详细步骤,能够对待测负载进行正向反向的测试阻抗,然后对每次测试的阻抗值进行判断分析,不满足预设精度的均增加量程进行再次测量,直至达到预设的精度,并且可以实现多个待测负载同时测量,提高测量效率,并且智能监测更加准确。然后判断待测负载阻抗是否属于正常阻抗范围,然后在进行输出回读,在数据回读过程中还设置校验数据以及检测是否回读状态检测指令,能够使数据连续,保证实时读取数据,避免了在数据传输过程中的丢失现象,提高了工作效率。

本实施例提供了一种智能阻抗分析式回收数据的系统,请参考图4,图4为本发明所提供的智能阻抗分析式回收数据的系统的结构框图;具体结构如下:

上位机,用于发送阻抗测试指令和数据回读指令;

以太网收发器,用于传输所述上位机发送的阻抗测试指令和数据回读指令,并将测试的阻抗数据和回读的数据上传至所述上位机;

FPGA模块,用于接收所述阻抗测试指令和数据回读指令,并根据所述阻抗测试指令进行智能阻抗测试,根据所述数据回读指令进行数据回读,所述FPGA模块包括:

发送单元,用于接收所述数据回读指令,发送读取数据指令;

解码单元,用于将待测负载中的数据进行解码;

接收单元,用于接收所述解码单元解码之后的数据;

FIFO单元,用于将所述接收单元中的数据按照预设排序方式上传至所述以太网收发器中;

阻抗测试电路,用于接收阻抗测试指令,智能测试待测负载的阻抗值,并将阻抗值反馈至所述FPGA中。

该阻抗分析式数据回收系统基于以太网、RS-422、LVDS接口,采用FPGA作为主控制器,具备对存储器事后阻抗测试和数据回收功能。

在飞行结束后,存储器硬件状态不明。在数据回读前,必须对存储器各供电线路负载电阻进行正向和反向测量,确保所有供电接口无开路短路现象。阻抗测试时,上位机软件通过以太网接口下发测试指令,回收读数装置根据指令内容控制对应开关通道闭合,计算完成后将结果由以太网接口回传至上位机界面。阻抗测试结束,存储器硬件状态良好,进入数据回收阶段。其传输链路分为指令传输链路和数据传输链路。上位机通过以太网接口下发读数指令,读数装置响应后根据自身FIFO容量通过rs-422接口发送指令至存储器。指令有效的状态下,存储器将内部数据通过LVDS总线经串化器串化后发出,回收读数装置接收LVDS数据后解串缓存。上位机通过以太网接口将数据由回收读数系统读回,完成一次数据的回读。

请参考图5,图5为本发明所提供的阻抗测试电路的原理图;如下:

电源模块,所述电源模块包括供电电源和多个不同阻值的电阻;

矩阵开关,所述矩阵开关设置多组测试端口,每组端口设置两个端口,所述每个端口均并联设置第一控制开关和第二控制开关;

其中,所有第一控制开关均连接所述电压模块的正极,所有第二控制开关均连接所述电压模块的负极;

电压采集装置,所述电压采集模块的正极连接所述电源模块的正极,所述电压采集模块的负极连接所述电源模块的负极,与所述矩阵开关并联。

如图中所示,本发明所提供的阻抗测试电路具有四种测量档位,分别采用20Ω、200Ω、2KΩ和20KΩ四种分压电阻进行串联,通过数值分析确定,若要保证测试精度在1%以内,各量程对应的测试电阻范围分别为2.54Ω~160Ω、25.4Ω~1.6KΩ、254Ω~16KΩ、2.54KΩ~160KΩ。

在矩阵开关中共用72个控制开关,每4个开关检测一个负载,本发明所提供的阻抗测试电路可以同时检测18个待测负载的阻抗,在每4个开关中,基数开关数连接电压源的正极,偶数开关数连接所述电压源的负极,通过这种特殊的连接结构实现正向反向测试阻抗,并且可实现多组负载同时进行测量。

测量原理如下:以负载电阻1测试为例,当上位机发出“正向”测试指令,FPGA控制K1、K4闭合,电流从负载电阻1的a端流向b端,负载电阻两端产生电压,通过采集对应电压可以得到正向电阻值;当上位机发出“反向”测试指令,FPGA控制K2、K3闭合,电流从负载电阻1的b端流向a端,同样可以得到反向电阻值。

阻抗测试回路指通过上位机软件发出相应指令给测试台,测试台根据指令内容控制开关切换至对应通道,并完成测量,最终将测量结果返回给上位机。

在FPGA模块中包括:复位模块、时钟模块、千兆以太网模块和控制模块,内部结构如图6所示:

RS-422发送单元,用于接收所述数据回读指令,发送读取数据指令;

8b/10b解码单元,用于将待测负载中的数据进行解码;

LVDS接收单元,用于接收所述解码单元解码之后的数据;

FIFO单元,用于将所述接收单元中的数据按照预设排序方式上传至所述以太网收发器中;

本发明为了避免出现指令误判现象,RS-422发送端指令连发三次,相邻两次之间相隔10ms。存储器接收端对指令采取“3判3”的判别方式,若收到第一条指令后15ms内没有收到下一条,则跳出该状态重新等待第一条指令。由于RS-422速率较于LVDS慢,流速差值会造成fifo产生丢数现象。设计采取“半满即满”的原则,提前将“满”标志返回。

以太网模块的主要功能有两个,包括下发读数指令和数据回传,考虑到以太网硬件电路造成的跨时钟域速率不匹配导致会有FIFO溢出的考虑。以太网传输速率达到40M,能够保障数据的快读回读。

其中,RS-422电路选用ADM2682EBRIZ芯片,发送时驱动器将TTL信号转化为RS-422差分信号进行输出,增强了系统的抗干扰能力。LVDS接收电路选用SN65LV1224B芯片,考虑到传统LVDS只能满足短距离的高速数据传输条件,在设计中用到了自适应均衡器DS10BR150TSD来增强信号的驱动能力和补偿能力。另外,为了保证数据传输中的直流平衡,加入了8b/10b编解码技术。

RS-422接口采用自主设计IP核,能够轻松更改码率,停止位位数,数据位宽等信息,系统通用化程度高,可配置性强。

以太网电路选用88E1111-BAB-I作为数据收发芯片,其主要功能是负责建立上位机和数据回收装置之间的通信。信号经过网络变压器HR911130C网络接口隔离后输出,有效的抑制了噪声的干扰,接口电路图如图7所示。

本发明具体实施例还提供了一种智能阻抗分析式回收数据的设备,包括:存储器,用于存储计算机程序;处理器,用于执行所述计算机程序时实现上述一种智能阻抗分析式回收数据的方法的步骤。

本发明具体实施例还提供了一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现上述一种智能阻抗分析式回收数据的方法的步骤。

本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其它实施例的不同之处,各个实施例之间相同或相似部分互相参见即可。对于实施例公开的装置而言,由于其与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

专业人员还可以进一步意识到,结合本文中所公开的实施例描述的各示例的单元及算法步骤,能够以电子硬件、计算机软件或者二者的结合来实现,为了清楚地说明硬件和软件的可互换性,在上述说明中已经按照功能一般性地描述了各示例的组成及步骤。这些功能究竟以硬件还是软件方式来执行,取决于技术方案的特定应用和设计约束条件。专业技术人员可以对每个特定的应用来使用不同方法来实现所描述的功能,但是这种实现不应认为超出本发明的范围。

结合本文中所公开的实施例描述的方法或算法的步骤可以直接用硬件、处理器执行的软件模块,或者二者的结合来实施。软件模块可以置于随机存储器(RAM)、内存、只读存储器(ROM)、电可编程ROM、电可擦除可编程ROM、寄存器、硬盘、可移动磁盘、CD-ROM、或技术领域内所公知的任意其它形式的存储介质中。

以上对本发明所提供的一种智能阻抗分析式回收数据的方法以及系统进行了详细介绍。本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以对本发明进行若干改进和修饰,这些改进和修饰也落入本发明权利要求的保护范围内。

- 一种交互式大数据智能异常检测系统和方法

- 一种分布式存储的回收站数据管理方法及相关装置

- 一种智能化数据采集、监控与分析系统及方法

- 应用于电化学测量的便携式阻抗谱分析仪及阻抗谱分析方法

- 应用于电化学测量的便携式阻抗谱分析仪及阻抗谱分析方法