包含结构化玻璃制品的电子封装件及其制造方法

文献发布时间:2023-06-19 09:24:30

相关申请的交叉引用

本申请根据35 U.S.C.§119,要求2018年4月3日提交的第62/652,271号美国临时申请的优先权权益,其内容通过引用全文纳入本文。

背景

1.技术领域

本公开涉及电子封装件及其制造方法,所述电子封装件包括位于结构化玻璃制品内的微处理器。

2.背景技术

电子装置,例如移动装置、消费电子器件、计算装置等,包括各种电子部件,例如微处理器、存储芯片、无源部件和/或射频(RF)部件。这些电子部件可以相互电连接并且可以配合执行电子装置的各种功能。在常规构造中,其中的每个电子部件可以单独地连接至基材以形成“封装件”,并且单独的封装件可以在电子装置内彼此电连接,例如以层叠封装(package on package,PoP)的构造彼此电连接。电子部件还可以或替代性地单独地连接到印刷电路板(PCB)。电子部件的单独封装和/或PCB所占据的空间促进形成了电子部件占据的几何空间,在一些应用中,例如当将电子部件被并入到移动装置中时,期望最大程度地减小电子部件所占据的空间(即,使电子部件的形状因子最小化)。另外,电子部件的单独封装可增加电子部件之间的距离,导致处理延时和功耗增加。

在一些常规构造中,电子部件可以安装于聚合物基材和/或可以通过聚合物粘合剂连接到基材。随着电子部件在操作期间被加热和冷却,电子部件与聚合物基材和/或聚合物粘合剂的热膨胀系数(CTE)的错配可造成聚合物基材和/或聚合物粘合剂以不同于电子部件的速率膨胀和收缩。聚合物基材和/或聚合物粘合剂与电子部件的膨胀和收缩差异可在聚合物基材和/或聚合物粘合剂与电子部件之间的界面处造成应力,这可导致基材和/或电子部件失效。

另外,电子部件可能发送和接收宽的频率范围内的信号,在相对较高的频率下,聚合物基材和/或聚合物粘合剂的介电常数可导致信号丢失,并且吸收由电子部件发送和接收的至少一部分信号。

因此,需要具有最小形状因子的电子部件封装。还需要使信号丢失最小化以及与热膨胀相关的应力最小化的电子部件封装。

发明内容

在一个实施方式中,电子封装组件包括玻璃基材,微处理器以及微电子部件,所述玻璃基材包括上玻璃包覆层、下玻璃包覆层、与上玻璃包覆层和下玻璃包覆层连接的玻璃芯体层、位于上玻璃包覆层或下玻璃包覆层的一者内的第一腔体和位于上玻璃包覆层或下玻璃包覆层的一者内的第二腔体,其中,上玻璃包覆层和下玻璃包覆层在蚀刻剂中的蚀刻速率比玻璃芯体层高,所述微处理器位于第一腔体内,所述微电子部件位于第二腔体内。

在另一个实施方式中,一种晶片级电子封装组件包括玻璃基材,多个微处理器以及多个微电子部件,所述玻璃基材包括上玻璃包覆层、下玻璃包覆层、与上玻璃包覆层和下玻璃包覆层连接的玻璃芯体层、位于上玻璃包覆层或下玻璃包覆层的一者内的多个第一腔体和位于上玻璃包覆层或下玻璃包覆层的一者内的多个第二腔体,其中,上玻璃包覆层和下玻璃包覆层在蚀刻剂中的蚀刻速率比玻璃芯体层高,所述多个微处理器位于所述多个第一腔体内,所述多个微电子部件位于所述多个第二腔体内。

在另一个实施方式中,一种用于形成电子封装组件的方法包括:向玻璃基材的表面施加掩模,所述玻璃基材包括连接到玻璃芯体层的玻璃包覆层,从而将掩模设置在玻璃包覆层上,所述掩模包括一个或多个开口区域,在所述开口区域处,玻璃包覆层保持不被掩模覆盖,所述玻璃包覆层在蚀刻剂中的蚀刻速率比玻璃芯体层高;将玻璃基材暴露于蚀刻剂,从而选择性地蚀刻一部分的玻璃包覆层并且在玻璃基材中形成一个或多个腔体;以及将微电子部件放置在玻璃基材的一个或多个腔体内。

应理解,前面的一般性描述和以下的具体实施方式都仅仅是示例性的,并且旨在提供用于理解所要求保护的主题的性质和特性的总体评述或框架。所附附图提供了进一步理解,附图被结合在本说明书中并构成说明书的一部分。附图说明了一种或多种实施方式,并与说明书一起用来解释各种实施方式的原理和操作。

附图简要说明

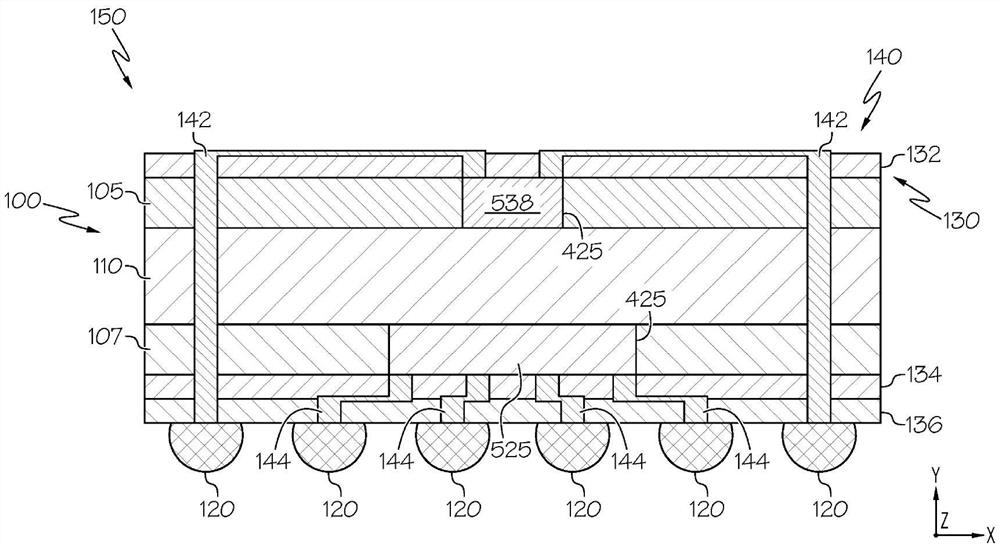

图1根据本文所示和所述的一个或多个实施方式,示意性地描绘了包括微处理器和存储芯片的电子封装组件的截面图;

图2根据本文所示和所述的一个或多个实施方式,示意性地描绘了包括微处理器和多个存储芯片的另一种电子封装组件的截面图;

图3根据本文所示和所述的一个或多个实施方式,示意性地描绘了包括微处理器和多个存储芯片的另一种电子封装组件的截面图,其中,存储芯片位于微处理器的下方;

图4根据本文所示和所述的一个或多个实施方式,示意性地描绘了包括微处理器、多个存储芯片以及与散热器热连接的热通孔的另一种电子封装组件的截面图;

图5根据本文所示和所述的一个或多个实施方式,示意性地描绘了包括位于同一玻璃包覆层中的微处理器和多个存储芯片的另一种电子封装组件的截面图;

图6根据本文所示和所述的一个或多个实施方式,示意性地描绘了包括无源元件和存储芯片的另一种电子封装组件的截面图;

图7根据本文所示和所述的一个或多个实施方式,示意性地描绘了包括多个无源元件的另一种电子封装组件的截面图;

图8根据本文所示和所述的一个或多个实施方式,示意性地描绘了包括多个无源元件的另一种电子封装组件的截面图;

图9根据本文所示和所述的一个或多个实施方式,示意性地描绘了包括无源和模拟RF装置的另一种电子封装组件的截面图;

图10根据本文所示和所述的一个或多个实施方式,示意性地描绘了包括无源和模拟RF装置的另一种电子封装组件的截面图;

图11根据本文所示和所述的一个或多个实施方式,示意性地描绘了玻璃基材的截面图;

图12根据本文所示和所述的一个或多个实施方式,示意性描绘了通过掩模而选择性暴露于蚀刻剂以在包覆层中形成腔体的图11的玻璃基材的截面图;

图13根据本文所示和所述的一个或多个实施方式,示意性地描绘了在图11和图12的玻璃基材中形成腔体并移除掩模之后,该玻璃基材的截面图;

图14根据本文所示和所述的一个或多个实施方式,示意性地描绘了在图11和图12的玻璃基材中形成腔体并移除掩模之后,该玻璃基材的透视图;

图15根据本文所示和所述的一个或多个实施方式,示意性地描绘了重构晶片和/或面板级封装件的截面图;并且

图16根据本文所示和所述的一个或多个实施方式,示意性地描绘了图15的重构晶片和/或面板级封装件的透视图。

具体实施方式

现将对附图所示的示例性实施方式进行详细说明。只要可能,在附图中将使用相同的附图标记来表示相同或类似的部分。附图中的各部件不一定按比例绘制,而是着重于说明示例性实施方式的原理。

数值,包括范围的端点,在本文中可表示为数值前带有“约”、“大约”等的近似值。在这些情况中,其他实施方式包括具体的数值。无论数值是否表示为近似值,在本公开中包括两种实施方式:一种表示为近似,另一种不表示为近似。还应理解,每个范围的端点在与另一个端点有关及独立于另一个端点时都是重要的。

在各个实施方式中,一种电子封装组件包括玻璃基材,所述玻璃基材包括上玻璃包覆层,连接到上玻璃包覆层的玻璃芯体层,以及连接到玻璃芯体层的下玻璃包覆层。多个电子部件,例如微处理器、存储芯片、无源元件及模拟RF装置可以位于玻璃基材的腔体内。通过在同个电子封装组件内包含多个电子部件,电子部件之间的距离可以最小化,从而减少了时延并且使得电子封装组件的形状因子最小化。另外,通过采用玻璃基材,可以使介电损耗和热应力最小化。为了帮助在上玻璃包覆层和下玻璃包覆层内形成精确腔体,上玻璃包覆层和下玻璃包覆层在蚀刻剂中的蚀刻速率可以比玻璃芯体层高,和/或可以具有更高的光敏性,以促进上玻璃包覆层和下玻璃包覆层的光机械加工,如本文更详细描述的。

本文所用的术语“微电子元件”可以用于一般性地描述存储芯片、无源元件、模拟RF装置和无源RF装置等。

首先参考图1,该图示意性描绘了电子封装组件150的截面图。在图1所示的实施方式中,电子封装组件150包括微处理器525和微电子元件,即存储芯片538,它们均位于玻璃基材100上。具体地,微处理器525和存储芯片538各自位于在玻璃基材100内形成的腔体425内。玻璃基材100连同微处理器525和存储芯片538可以被位于玻璃基材100的顶部和底部的一个或多个聚合物介电层130覆盖。在图1所示的实施方式中,电子封装组件150包括位于玻璃基材100顶部上的上聚合物介电层132,并且包括位于玻璃基材100的底部的一对下聚合物介电层134、136。聚合物介电层130可以由具有用于封装电子器件的期望介电性质的任何合适聚合物形成,并且可以通过任何合适的方法形成。

电子封装组件150还包括延伸通过聚合物介电层130和玻璃基材100的通孔140。通孔140使微处理器525和存储芯片538电耦合和/或通信耦合到位于下聚合物介电层136的底部的焊料突起120。在图1所示的实施方式中,电子封装组件150包括一对通孔142,其在存储芯片538与一对焊料突起120之间延伸通过玻璃基材100。电子封装组件150还包括通孔144,其在微处理器525与一组焊料突起120之间延伸通过下聚合物介电层134、136。在一些实施方式中,通孔140也可以在微处理器525与存储芯片538之间直接延伸。通孔140可以由适于传导电信号的任何材料形成,例如铜等,并且可以通过任何合适的方法形成,例如,溅射沉积、膏体填充或镀覆(保形或填充),或它们的任何组合。

存储芯片538一般是具有集成电路的硅基结构,其可以用于临时或永久地储存数据和程序。微处理器525一般也为硅基结构,并且一般可以包括如可以用于移动应用的具有片上系统(SoC)集成电路的应用处理器。在其他实施方式中,微处理器525可以包括通用微处理器。

玻璃基材100包括多个玻璃层,在图1描绘的实施方式中,玻璃基材100包括玻璃中心芯体110,其连接于上玻璃包覆层105和任选的下玻璃包覆层107。上玻璃包覆层105在垂直方向上(即,在所描绘的+y方向上)位于玻璃中心芯体110的上方,并且下玻璃包覆层107在垂直方向上位于玻璃中心芯体110的下方。在一些实施方式中,玻璃中心芯体110、上玻璃包覆层105和下玻璃包覆层107彼此直接熔合并且在它们之间没有任何粘合剂、聚合物层、涂层等。在另一些实施方式中,使用粘合剂等将玻璃中心芯体110、上玻璃包覆层105和下玻璃包覆层107彼此连接。

玻璃中心芯体110、上玻璃包覆层105和下玻璃包覆层107可具有任何合适的玻璃组合物并且可以使用任何合适的工艺来制造。合适的玻璃组合物的实例可包括碱土金属铝硼硅酸盐玻璃、锌硼硅酸盐玻璃和钠钙玻璃以及玻璃陶瓷,例如富含氧化镁、氧化钇、氧化铍、氧化铝或氧化锆的那些。一般而言,玻璃中心芯体110、上玻璃包覆层105和下玻璃包覆层107可具有’451专利或‘266申请中论述的任何一种组合物,或者可使用’451专利或‘266申请中论述的任何一种工艺来制造,所述文献各自在本说明书的结尾处有引用。

在实施方式中,上玻璃包覆层105、下玻璃包覆层107和玻璃中心芯体110中的至少一者具有不同的物理尺寸和/或玻璃组合物,这些物理尺寸和/或玻璃组合物便于相对于玻璃中心芯体110选择性移除上玻璃包覆层105和下玻璃包覆层107中的至少一者,以形成腔体425。

例如,在一些实施方式中,上玻璃包覆层105和下玻璃包覆层107具有相同的玻璃组合物,而玻璃中心芯体110具有不同的玻璃组合物。具体地,在一些实施方式中,上玻璃包覆层105、下玻璃包覆层107和玻璃中心芯体110的玻璃组合物可不同,以使得上玻璃包覆层105、下玻璃包覆层107和玻璃中心芯体110在蚀刻剂中的耐久性不同。例如,可期望上玻璃包覆层105和下玻璃包覆层107中的一者或两者在蚀刻剂中的溶解速率与玻璃中心芯体110不同。上玻璃包覆层105、下玻璃包覆层107和玻璃中心芯体110之间的不同耐久性使得可在玻璃基材100的表面中形成腔体425。例如,上玻璃包覆层105和下玻璃包覆层107在蚀刻剂中可具有足够高的溶解速率,以使得它们能够被蚀刻而形成腔体425。另一方面,玻璃中心芯体110在蚀刻剂中可具有足够低的溶解速率,以使得其基本上不易被蚀刻。玻璃中心芯体110在蚀刻剂中的溶解速率可以为零或足够接近零,以使得其不易被蚀刻到任何显著的程度。因此,玻璃中心芯体110可起到蚀刻停止的作用以限制使用蚀刻剂可将玻璃基材100蚀刻到的深度。

在其他实施方式中,例如,在腔体425由除湿法蚀刻之外的工艺形成的实施方式中,上玻璃包覆层105、下玻璃包覆层107和玻璃中心芯体110可以具有相同或基本相同的玻璃组合物。

在实施方式中,上玻璃包覆层105、下玻璃包覆层107和玻璃中心芯体110的厚度(在如图所示的y方向上评估)可以基于微处理器525和/或存储芯片538的厚度(在如图所示的y方向上评估)来选择。具体地,可以对上玻璃包覆层105和下玻璃包覆层107的厚度进行选择,以使其分别对应于存储芯片538和微处理器525的厚度(在如图所示的y方向上评估)。在一些实施方式中,上玻璃包覆层105和下玻璃包覆层107中的一者或两者的厚度在50微米(μm)至100μm之间选择。但应理解,上玻璃包覆层105和下玻璃包覆层107可具有其他厚度,尤其是当与厚度小于或大于所公开的厚度的存储芯片538和微处理器525一起使用时。在一些实施方式中,上玻璃包覆层105和下玻璃包覆层107具有相同的厚度,因此玻璃基材100在垂直方向上是对称的。在另一些实施方式中,上玻璃包覆层105和下玻璃包覆层107可以具有不同的厚度,例如,在微处理器525和存储芯片538具有不同厚度的实施方式中。

相比于存储芯片538和微处理器525单独封装的常规构造,通过将存储芯片538放置在与微处理器525相同的电子封装组件150中,可以最大程度地减小存储芯片538与微处理器525之间的物理距离。例如,在存储芯片538和微处理器525被放置在分开的封装件的常规构造中,存储芯片538可以位于微处理器525的上方或下方,例如,PoP构造,或者微处理器525与存储芯片538并排放置(即,在如图所示的z方向或x方向上)。然而,相比于微处理器525和存储芯片538被包封在同一电子封装组件150内的图1描绘的实施方式,将存储芯片538和微处理器525并排放置增加了存储芯片538和微处理器525(以及它们周围的封装件)在z方向和/或x方向上所占据的空间。例如,相比于当单独封装微处理器525和存储芯片538并使它们相互并排放置时的情况,通过将微处理器525和存储芯片538封装在同一封装件中,微处理器525和存储芯片538所占据的空间可以减小最高95%。

类似地,相比于微处理器525和存储芯片538被封装在同一电子封装组件150内的图1描绘的实施方式,在存储芯片538和微处理器525被放置在分别的封装件中并且存储芯片538位于微处理器525的上方或下方的常规构造中,存储芯片538和微处理器525在y方向上所占据的空间增加。具体地,相比于微处理器525和存储芯片被封装在同一电子封装组件150内的图1描绘的实施方式,当微处理器525和存储芯片538被放置在分别的封装件中时,焊料突起在垂直方向上常规位于分别的封装件之间以增加微处理器525与存储芯片538之间的连接,由此增加了微处理器525和存储芯片538(及它们周围的封装件)所占据的空间。焊料突起的直径通常在100μm至200μm之间,因此,通过将微处理器525和存储芯片538封装在同一封装件中,微处理器525和存储芯片538(及相关封装)所占据的空间在如图所示的y方向上可以减小多达200μm。由此,可以最大程度地减小微处理器525和存储芯片538(及围绕封装件的封装)所占据的空间,从而使微处理器525和存储芯片538的形状因子最小化。最小化的形状因子在空间可能有限的移动应用中可以特别有利。

另外,减少焊料突起的层也可以减少信号丢失。例如,如上所述,在微处理器525和存储芯片538被分开封装的常规构造中,焊料突起在垂直方向上常规位于分别的封装件之间,以在微处理器525封装件与存储芯片538封装件之间建立连接。微处理器525和存储芯片538也可以位于印刷电路板上,并且焊料突起位于印刷电路板与堆叠的微处理器525和存储芯片538之间。因此,在微处理器525位于存储芯片538下方的实例中,对于要在存储芯片538与印刷电路板之间通过的电信号,该信号将首先行进通过存储芯片538与微处理器525封装件之间的焊料突起,然后通过微处理器525封装件与印刷电路板之间的焊料突起,最终通过两个单独的焊料突起层。

相较之下,通过将微处理器525与存储芯片538封装在同一封装件中,去往或来自微处理器525和存储芯片538的信号可以仅需通过通孔140和焊料突起120的单个层。焊料突起一般可以由材料复合物形成,该材料复合物有助于焊料突起的制造,但是可能带来电信号的丢失。因此,通过限制制造电连接所需的焊料突起的数目,可以减少信号丢失。

另外,相比于存储芯片538独立于微处理器525封装的常规构造,将存储芯片538和微处理器525放置在同一电子封装组件150中减小了微处理器525与存储芯片538之间的物理距离。例如,在微处理器525和存储芯片538被分别封装的常规构造中,微处理器525和存储芯片538可能彼此间隔开,以使微处理器525与存储芯片538之间的路径长度(例如,沿着电通路评估的微处理器525与存储芯片538之间的距离)在8毫米(mm)至18mm之间。相较之下,通过将微处理器525与存储芯片538封装在同一封装件内,微处理器525与存储芯片538之间的路径长度可减小到200μm至800μm,包括端点。不囿于理论,微处理器525能够以比存储芯片538发送和接收电信号的时间更快的速度进行计算。由此,微处理器525与存储芯片538之间的距离可以限制微处理器525进行操作的时间。因此,相比于微处理器525和存储芯片538被分别封装的常规构造,通过最大程度地减小微处理器525与存储芯片538之间的距离,例如,通过将微处理器525和存储芯片538包封在同一电子封装组件150中,可以使微处理器525的时延最小化。

相比于存储芯片538和微处理器525位于聚合物基材上的常规构造,玻璃基材100还可以减少在存储芯片538与微处理器525之间发送的信号的延迟和串扰。不囿于理论,期望利用介电常数相对较低的基材以使基材上的电子部件之间发送的信号的串扰最小化并且使传播延迟最小化。聚合物,例如常规封装中所用的那些,可能具有相当大的介电常数,并且在不同频率下也可能具有大的介电常数范围。相较之下,玻璃,例如可以用于玻璃基材100的玻璃,可具有相对较低的介电常数,其在大的频率范围内维持相对稳定。在一个实例中,玻璃基材100的上玻璃包覆层105、下玻璃包覆层107和玻璃中心芯体110在10千兆赫(GHz)下的损耗正切可以为约0.004至0.042,并且在60GHz下的损耗正切可以为约0.006至0.054。相较之下,在10GHz下,常规聚合物的损耗正切可比玻璃基材的高多达10倍。因此,相比于利用基于聚合物的基材的电子封装件,通过利用玻璃基材100来形成电子封装组件150,电子封装组件150可以提供介电常数相对较低的介质,其在相对较高的频率下保持稳定。

另外,玻璃基材100可以为存储芯片538和微处理器525提供基材,其在热变化下以与存储芯片538和微处理器525相似的方式膨胀和收缩。例如,存储芯片538和微处理器525一般是基于半导体的结构,并且热膨胀系数为每℃约百万分之2-3(2-3ppm/℃)。上玻璃包覆层105和下玻璃包覆层的CTE可以为约7.6-9.5ppm/℃,包括端点,并且玻璃中心芯体层110的CTE可以为约7.5-9.1ppm/℃,包括端点。相较之下,常规用于电子部件封装的聚合物(例如FR-4层压件)的CTE为14至17ppm/℃。因此,相比于用于常规电子部件封装的聚合物,玻璃基材100的CTE更接近于存储芯片538和微处理器525的CTE。相比于常规基于聚合物的基材,通过更紧密地匹配存储芯片538和微处理器525的CTE,玻璃基材100在热变化下可以与存储芯片538和微处理器525相似的方式膨胀和收缩,由此减小了在存储芯片538/微处理器525与玻璃基材100之间的界面处的应力。另外,当加热和冷却玻璃基材100时,玻璃基材100的相当低的CTE可以有助于减少电子封装组件150的翘曲。

应理解,可对图1所示的玻璃基材100的实施方式进行多种改变。例如,在一些实施方式中,玻璃基材100可仅包括两个玻璃层,例如,上玻璃包覆层105和玻璃中心芯体110。在另一些实施方式中,玻璃基材100可包括四个或更多个玻璃层。还考虑了多种其他变化形式。

参考图2,在另一个实施方式中,电子封装组件150包括多个位于玻璃基材100的腔体425内的存储芯片538。与图1所示的实施方式一样,玻璃基材100包括上玻璃包覆层105、玻璃中心芯体110和下玻璃包覆层107。电子封装组件150还包括位于下玻璃包覆层107的腔体425内的微处理器525。然而,在图2所示的实施方式中,电子封装组件150包括位于上玻璃包覆层105的腔体425内的多个存储芯片538。相比于图1所示的实施方式,电子封装组件150可以包括从存储芯片538延伸到焊料突起120的额外的通孔142,并且可以额外地包括位于上聚合物介电层132上方的另一个上聚合物介电层133,以承载额外的通孔142。与上文所述及图1所示的实施方式相同,通过将存储芯片538和微处理器525包含在同一电子封装组件150内,可以最大程度地减小存储芯片538与微处理器525之间的距离,从而减少微处理器525的时延并使电子封装组件150的形状因子最小化。另外,如上所述,通过采用玻璃基材100,可以使介电损耗和热应力最小化。

参考图3,在另一个实施方式中,类似于图2描绘的实施方式,电子封装组件150包括多个位于玻璃基材100的腔体425内的存储芯片538。在图3描绘的实施方式中,存储芯片538位于下玻璃包覆层107中的腔体425内,而微处理器525位于上玻璃包覆层105的腔体425内。由于存储芯片538位于下玻璃包覆层107内,因此,相比于位于上玻璃包覆层105内的微处理器525,存储芯片538更靠近焊料突起120定位。通过靠近焊料突起120定位存储芯片538,可以减少将存储芯片538连接到焊料突起120所需的通孔142的数目,当电子封装组件150包括多个存储芯片538时,这可能是特别期望的。类似于上文所述及图1和2描绘的实施方式,通过将存储芯片538和微处理器525包含在同一电子封装组件150内,可以最大程度地减小存储芯片538与微处理器525之间的距离,从而减少微处理器525的时延并使电子封装组件150的形状因子最小化。另外,如上所述,通过采用玻璃基材100,可以使介电损耗和热应力最小化。

参考图4,该图描绘了电子封装组件150的另一个实施方式。在图4所示的实施方式中,电子封装组件150包括热通孔562,其热耦合到微处理器525和位于电子封装组件150底部上的散热器564。散热器564位于电子封装组件150的底部上,并且热通孔562在微处理器525与散热器564之间向上延伸通过玻璃基材100。热通孔562和散热器564用于将来自微处理器525的热耗散到围绕电子封装组件150的周围介质,并且可以帮助将微处理器525保持在可接受的工作温度内。热通孔562和散热器564可以由适于传输热能的任何材料形成,例如铜、铜合金等,并且可以通过任何合适的方法形成。与上文所述及图1-3所示的实施方式相同,通过将存储芯片538和微处理器525包含在同一电子封装组件150内,可以最大程度地减小存储芯片538与微处理器525之间的距离,从而减少微处理器525的时延并使电子封装组件150的形状因子最小化。另外,如上所述,通过采用玻璃基材100,可以使介电损耗和热应力最小化。

参考图5,该图描绘了电子封装组件150的另一个实施方式。在图5所示的实施方式中,微处理器525和存储芯片538各自位于下玻璃包覆层107内。虽然图5所示的实施方式中的玻璃基材100包括玻璃中心芯体110、上玻璃包覆层105和下玻璃包覆层107,但应理解,可以省略上玻璃包覆层105。与上文所述及图1-4所示的实施方式相同,通过将存储芯片538和微处理器525包含在同一电子封装组件150内,可以最大程度地减小存储芯片538与微处理器525之间的距离,从而减少微处理器525的时延并使电子封装组件150的形状因子最小化。另外,如上所述,通过采用玻璃基材100,可以使介电损耗和热应力最小化。

参考图6,其描绘了电子封装组件150的另一个实施方式,其中,除了微处理器525和一个或多个存储芯片538之外,电子封装组件150还包括无源元件540。具体地,电子封装组件150包括位于上玻璃包覆层105的腔体425内的一对无源元件540和存储芯片538,并且包括位于下玻璃包覆层107的腔体425内的微处理器525。

无源元件540一般可以包括硅基部件,其不产生功率,而是耗散、储存和/或释放功率,例如电感器、电容器、电阻等,并且可以通过多层共烧陶瓷(MLCC)工艺等制造。无源元件540一般比微处理器525相对更厚(在如图所示的y方向上评估),并且厚度可以大于200μm。因此,在图6所示的实施方式中,上玻璃包覆层105的厚度可以选择为对应于无源元件540的厚度,而下玻璃包覆层107可以选择为相对较小的厚度,以对应微处理器525的厚度,因此玻璃基材100具有不对称的截面。

与上文所述及图1-5描绘的实施方式相同,通过将无源元件540、存储芯片538和微处理器525包含在同一电子封装组件150内,可以最大程度地减小存储芯片538与微处理器525之间以及无源元件540与微处理器525之间的距离,从而减少微处理器525的时延并使电子封装组件150的形状因子最小化。另外,如上所述,通过采用玻璃基材100,可以使介电损耗和热应力最小化。图6描绘的实施方式中的无源元件540可以用于噪声抑制以在电子封装组件150中减弱不期望的频率,这可以进一步突出通过利用玻璃基材100来最小化信号丢失和介电损耗的益处。

参考图7,该图描绘了电子封装组件150的另一个实施方式。与上文所述和图6描绘的实施方式一样,电子封装组件150包括位于玻璃基材100内的多个无源元件540。在图7描绘的实施方式中,无源元件540位于下玻璃包覆层107中的腔体425内,而微处理器525位于上玻璃包覆层105的腔体425内。由于无源元件540位于下玻璃包覆层107内,因此,相比于位于上玻璃包覆层105内的微处理器525,无源元件540更靠近焊料突起120定位。通过靠近焊料突起120定位无源元件540,可以减少将无源元件连接到焊料突起120所需的通孔142的数目,当电子封装组件150包括多个无源元件540时,这可能是特别期望的。类似于上文所述及图7所示的实施方式,通过将无源元件540和微处理器525包含在同一电子封装组件150内,可以最大程度地减小无源元件540与微处理器525之间的距离,从而减少微处理器525的时延并使电子封装组件150的形状因子最小化。另外,如上所述,通过采用玻璃基材100,可以使介电损耗和热应力最小化。

参考图8,该图描绘了包括无源元件540的电子封装组件150的另一个实施方式。在图8所示的实施方式中,电子封装组件150包括延伸通过玻璃基材100的厚度的一对无源元件541。类似于上文所述及图6和7所示的实施方式,通过将无源元件540、541和微处理器525包含在同一电子封装组件150内,可以最大程度地减小无源元件540、541与微处理器525之间的距离,从而减少微处理器525的时延并使电子封装组件150的形状因子最小化。另外,如上所述,通过采用玻璃基材100,可以使介电损耗和热应力最小化。

参考图9,该图描绘了电子封装组件150的另一个实施方式。电子封装组件150包括玻璃基材100,其包括上玻璃包覆层105、玻璃中心芯体110和下玻璃包覆层107,并且微处理器525位于下玻璃包覆层107的腔体425内。在图9描绘的实施方式中,电子封装组件150包括一个或多个RF装置。具体地,电子封装组件150包括位于电子封装组件150的顶部上(即,位于如图所示的上聚合物介电层133的顶部上)的一个或多个无源RF装置530。无源RF装置530一般可以包括位于电子封装组件上的天线、波导、平衡转换器等。

电子封装组件150还包括一对第一模拟RF装置532和第二模拟RF装置534,它们各自位于玻璃基材100的上玻璃包覆层105内的相应腔体425内。在实施方式中,第一模拟RF装置532和第二模拟RF装置534是硅基结构,并且第一模拟RF装置532中的一者或多者可以与第二模拟RF装置534不同。例如,在一些实施方式中,第一模拟RF装置532可以包括放大器等,并且第二模拟RF装置可以包括转换器、多路转切器等。

一般而言,第一模拟RF装置532和第二模拟RF装置534的厚度通常大于微处理器525的厚度(在如图所示的y方向上评估)。在一些实施方式中,第一模拟RF装置532和第二模拟RF装置534的厚度在约200μm至300μm之间,包括端点。因此,在图9所示的实施方式中,上玻璃包覆层105的厚度可以选择为对应于第一模拟RF装置532和第二模拟RF装置534的厚度,而下玻璃包覆层107可以选择为相对较小的厚度,以对应于微处理器525的厚度,因此玻璃基材100具有不对称的截面。

类似于上文所述的实施方式,通过将模拟RF装置532、534,无源RF装置530和微处理器525包含在同一电子封装组件150内,可以最大程度地减小无源元件540、541与微处理器525之间的距离,从而减少微处理器525的时延并使电子封装组件150的形状因子最小化。另外,如上所述,通过采用玻璃基材100,可以使介电损耗和热应力最小化。另外,模拟RF装置532、534以及无源RF装置530可以在宽的频率范围下工作。例如,在一些实施方式中,模拟RF装置532、534以及无源RF装置530可以在高至100GHz下工作。如上所述,聚合物基材的介电常数在高频率下可显著增加,导致高频率下介电损耗和信号丢失,并且在这样的高频率下,聚合物基材可能变得不稳定。因此,相比于常规构造,通过用玻璃基材100安装模拟RF装置532、534和无源RF装置530,可使介电损耗和信号丢失最小化。

参考图10,该图描绘了电子封装组件150的另一个实施方式。电子封装组件150包括玻璃基材100,其具有第一模拟RF装置532和第二模拟RF装置534,以及位于电子封装组件150的顶部上的无源RF装置530。在图10所示的实施方式中,电子封装组件150还包括位于上玻璃包覆层105的腔体425内的存储芯片538。

类似于图9所示的实施方式,通过将模拟RF装置532、534,无源RF装置530和微处理器525包含在同一电子封装组件150内,可以最大程度地减小无源元件540、541与微处理器525之间的距离,从而减少微处理器525的时延并使电子封装组件150的形状因子最小化。另外,如上所述,通过采用玻璃基材100,可以使介电损耗和热应力最小化。另外,模拟RF装置532、534以及无源RF装置530可以在宽的频率范围下工作。例如,在一些实施方式中,模拟RF装置532、534以及无源RF装置530可以在高至100GHz下工作。如上所述,聚合物基材的介电常数在高频率下可显著增加,导致高频率下介电损耗和信号丢失,并且在这样的高频率下,聚合物基材可能变得不稳定。因此,相比于常规构造,通过用玻璃基材100安装模拟RF装置532、534和无源RF装置530,可使介电损耗和信号丢失最小化。

现应理解,根据本公开所述的电子封装组件150可以包括多个电子部件,例如微处理器、无源元件、以及无源和有源RF装置。如上所述,通过将电子部件定位在玻璃基材内,可以使微处理器的时延以及电子封装组件的形状因子最小化。另外,由于相比于常规聚合物基材,玻璃基材的CTE更接近电子部件的CTE,因此,相比于常规构造,热应力得到了减小。另外,相比于使用聚合物基材的常规构造,当电子封装组件内包含RF装置时可能经历的介电损耗,尤其是高频率工作条件下的介电损耗可以最小化。

为了将电子部件定位并保留在玻璃基材的腔体内,尤其是在不依赖于聚合物粘合剂的情况下,期望形成尺寸精确的腔体来容纳电子部件。下文描述了在玻璃基材内形成尺寸精确的腔体的方法。

首先参考图11,其描绘了玻璃基材100,所述玻璃基材100包括上玻璃包覆层105、下玻璃包覆层107和玻璃中心芯体110。如上所述,上玻璃包覆层105、下玻璃包覆层107和玻璃中心芯体110的玻璃组合物可不同,以使得上玻璃包覆层105、下玻璃包覆层107和玻璃中心芯体110在蚀刻剂中的耐久性不同。例如,可期望上玻璃包覆层105和下玻璃包覆层107中的一者或两者在蚀刻剂中的溶解速率与玻璃中心芯体110不同。

综合参考图12和13,在玻璃基材100中形成腔体425以将玻璃基材转变成如本文所述的结构化制品。可使用图12所示的方法在玻璃基材100的表面中形成腔体425。在一些实施方式中,该方法包括:在玻璃基材100的表面上形成掩模215。例如,在上玻璃包覆层105和/或下玻璃包覆层107的表面上形成掩模215。可通过印刷(例如,喷墨印刷、凹版印刷、丝网印刷或另外的印刷工艺)或另外的沉积工艺来形成掩模215。在一些实施方式中,掩模215耐蚀刻剂(例如,将要用于在玻璃基材100中蚀刻腔体425的蚀刻剂)。例如,掩模215可包含丙烯酸酯、多官能丙烯酸酯正乙烯基己内酰胺或另外合适的掩模材料。在一些实施方式中,掩模215由包含底漆并且所述底漆用于增强掩模与玻璃基材100之间的粘性的油墨材料形成。这种增强的粘性可减少蚀刻剂在掩模215与玻璃基材100之间渗漏,这可有助于实现本文所述的精确腔体。

在一些实施方式中,掩模215包括一个或多个开口区域,在所述开口区域处,玻璃基材100保持不被覆盖。掩模215的开口区域可具有与要在玻璃基材100中形成的腔体425的所需图案对应的图案。例如,掩模215的图案可以是规则重复的矩形形状的阵列(例如,用于接收如本文所述的微处理器/电子部件)。在这样的实施方式中,由掩模215图案化的形状可紧密对应于微处理器/电子部件的形状。也可采用其他形状,并且所述形状可紧密对应于电子部件的形状或者能够将电子部件稳固地保持在玻璃基材100上的位置中。因此,掩模215可被构造成蚀刻掩模,从而能够如本文所述选择性地蚀刻上玻璃包覆层105和/或下玻璃包覆层107,并且在玻璃基材100中形成腔体425。

在一些实施方式中,将其上设置有掩模215的玻璃基材100暴露于蚀刻剂220。例如,如图12所示,使上玻璃包覆层105和/或下玻璃包覆层107接触蚀刻剂220,从而选择性地蚀刻未被掩模215覆盖的相应的玻璃包覆层的暴露部分,并且在玻璃基材中形成腔体425,由此将基材转变成成形制品。在一些实施方式中,将其上设置有掩模215的玻璃基材100暴露于处于蚀刻温度下的蚀刻剂220,暴露一定的蚀刻时间。例如,蚀刻温度为约20℃、约22℃、约25℃、约30℃、约35℃、约40℃、约45℃或约50℃,或者由所述数值的任何组合限定的任何范围。较低的蚀刻温度可有助于在蚀刻期间保持掩模215的完整性,而这可使蚀刻时间增加和/或改进如本文所述的腔体形状。附加或替代性地,蚀刻时间可以是约10分钟、约15分钟、约20分钟、约25分钟、约30分钟、约35分钟、约40分钟、约45分钟、约50分钟、约55分钟、约60分钟、约65分钟、约70分钟、约75分钟、约80分钟、约85分钟、或约90分钟,或者由所述数值的任何组合限定的任何范围。相对较长的蚀刻时间能够实现如本文所述的腔体425的基本上直的侧壁。

在一些实施方式中,上玻璃包覆层105和/或下玻璃包覆层107比玻璃中心芯体110蚀刻至少快1.5倍,至少快2倍,至少快5倍,至少快10倍,至少快20倍,或至少快100倍。附加或替代性地,上玻璃包覆层105和/或下玻璃包覆层107的蚀刻速率与玻璃中心芯体110的蚀刻速率的比值为约5、约10、约15、约20、约25、约30、约35、约40、约45、约50、约55、约60、约65、约70、约75、约80、约85、约90、约95、约100,或者由所述数值的任何组合限定的任何范围。

在一些实施方式中,所述形成腔体425包括:基本上完全蚀刻穿过上玻璃包覆层105和/或下玻璃包覆层107,以在腔体的底部处暴露一部分玻璃中心芯体110。因此,腔体425的侧壁由上玻璃包覆层105和/或下玻璃包覆层107限定,并且腔体425的底板由玻璃中心芯体110限定。在一些实施方式中,在形成腔体425期间,玻璃中心芯体110基本上不被蚀刻。因此,玻璃中心芯体110起到确定腔体425的深度的蚀刻停止作用。

虽然上文描述了湿法蚀刻,但是光机械加工也可以提供合适的方法来在上玻璃包覆层105和/或下玻璃包覆层内形成腔体425。例如,可以对玻璃基材100的部分暴露能量源,例如激光、紫外辐射源等,并且可以形成裂纹和/或使对能量源光敏的玻璃基材100的暴露部分结晶。玻璃基材100的结晶/开裂部分接着在蚀刻剂中具有相对较高的蚀刻速率,并且可以通过将玻璃基材暴露于蚀刻剂来去除。

在这些实施方式中,上玻璃包覆层105、下玻璃包覆层107和玻璃中心芯体110的玻璃组合物可不同,以使得上玻璃包覆层105和下玻璃包覆层107的光敏性与玻璃中心芯体110的不同。例如,可期望玻璃中心芯体110比上玻璃包覆层105和下玻璃包覆层107具有更低的光敏性。玻璃中心芯体110与上玻璃包覆层105和下玻璃包覆层107之间的不同光敏性可帮助在玻璃基材100的表面中形成腔体425。例如,上玻璃包覆层105和下玻璃包覆层107可具有足够的光敏性,使得它们可被光加工而形成腔体425。另一方面,玻璃中心芯体110可具有足够的非光敏性,以使得其不易被光加工。

在一些实施方式中,所述一个或多个腔体的底板具有光学品质。例如,腔体425的底板的表面粗糙度为至多约50nm、至多约40nm、至多约30nm、至多约20nm、至多约10nm、至多约9nm、至多约8nm、至多约7nm、至多约6nm、或者至多约5nm。这种低表面粗糙度可通过玻璃中心芯体110所提供的蚀刻停止和/或蚀刻期间搅拌蚀刻剂以从腔体移除蚀刻副产物来实现。附加或替代性地,这种低表面粗糙度能够使光通过底板(例如,用于对设置在腔体内的物体或材料进行光学激活和/或分析)而不会显著畸变。

在一些实施方式中,所述一个或多个腔体的底板基本上是平坦的。例如,沿着腔体的周界的第一位置处的腔体的第一深度与沿着腔体的周界并且与第一位置相对(例如,直径上相对)的第二位置处的腔体的第二深度之间的差为至多约5μm、至多约4μm、至多约3μm、至多约2μm、至多约1μm、至多约0.9μm、至多约0.8μm、至多约0.7μm、至多约0.6μm、至多约0.5μm、至多约0.4μm、至多约0.3μm、至多约0.2μm、或者至多约0.1μm。这种低的深度差可通过玻璃中心芯体110所提供的蚀刻停止来实现。例如,腔体的深度可以主要由上玻璃包覆层105和/或下玻璃包覆层107的厚度决定,而不会因为蚀刻温度和/或蚀刻时间改变而显著改变。

在一些实施方式中,腔体425的侧壁305基本上是垂直的(例如,侧壁基本上垂直于腔体425的底板310)。例如,在腔体425的侧壁305与底板310之间形成的角为约90°,或约80°至约100°。附加或替代性地,在腔体的顶部处(例如,在玻璃基材的表面附近)的腔体宽度与在腔体的底部处(例如,在腔体的底板附近)的腔体宽度之间的差为至多约1mm、至多约0.9mm、至多约0.8mm、至多约0.7mm、至多约0.6mm、或至多约0.5mm。在一些这样的实施方式中,腔体的深度为至少约50μm、至少约60μm、至少约70μm、至少约80μm、或者至少约90μm。这种低的侧壁角可通过增加蚀刻时间来实现,而玻璃芯体层110所提供的蚀刻停止使得增加蚀刻时间成为可能。例如,可以延长蚀刻时间以在腔体的底部附近移除侧壁与底板之间的相交处的材料而不显著增加腔体的深度。相比于常规的湿法蚀刻工艺,移除这些材料可得到更直(例如垂直)的侧壁。

在一些实施方式中,在形成腔体425后,从玻璃基材100移除掩模215。例如,所述移除掩模215包括:使掩模与溶剂接触,由此从玻璃基材的表面移除掩模。在一些实施方式中,溶剂是水。例如,所述移除掩模215包括:将其上设置有掩模215的玻璃基材100浸没到水中,由此从玻璃基材的表面移除掩模。

现在参考图13-14,其分别描绘了在其中形成有腔体425并且从其中移除了掩模215的玻璃基材100的截面示意图和透视图。

腔体425的一个优点是它们可以使用常规加工技术通常不可得到的精度来形成。在玻璃中心芯体110不受蚀刻过程影响的那些实施方式中,腔体425的深度尤为精确。在这样的实施方式中,可蚀刻掉上玻璃包覆层105和/或下玻璃包覆层107,直到在腔体425的底部处暴露出玻璃中心芯体110。因此,腔体425的侧壁由上玻璃包覆层105和/或下玻璃包覆层107限定,并且底板由玻璃中心芯体110限定。这使腔体425具有精确的深度。

图13-14所示的腔体425具有对应于微处理器525的矩形形状。但应理解,腔体425可具有任何合适的形状。例如,腔体425可具有正方形形状、圆形形状或任何其他多边形或非多边形形状。

综合参考图15和16,在一些实施方式中,可将电子部件组装到成形的玻璃制品中。例如,可将微处理器525放置在腔体425中,所述微处理器525可从下方的晶片切下。为了说明将电子部件插入腔体425内,参考了微处理器525,但应理解,也可使用同样的方法来成形腔体425以容纳存储芯片538(图1)、无源元件540(图6)和/或第一有源模拟RF装置532及第二有源模拟RF装置534(图9)中的任一种。另外,虽然图12-16所示的方法显示了将掩模215施加于上玻璃包覆层105并且在上玻璃包覆层105内进行腔体425的蚀刻,但应理解,类似的方法可适用于下玻璃包覆层107以在下玻璃包覆层107内形成腔体425。

腔体425各自具有与微处理器525基本相同的尺寸[宽度(x)、长度(y)和/或深度(z)],以允许将微处理器525精确地装配在每个对应的腔体425中。如上所述,可取的是,使微处理器525与上玻璃包覆层105和/或下玻璃包覆层107的顶表面齐平。然而,可能存在微处理器525的顶部与上玻璃包覆层105和/或下玻璃包覆层107可能不完全齐平的情况。只要得到的重构基材能够被进一步加工而产生最终封装件,这是可以接受的。

微处理器525、存储芯片538(图1)、无源元件540(图6)和/或第一有源模拟RF装置532及第二有源模拟RF装置534(图9)的尺寸一般可变化1-2微米。在一些实施方式中,相对于(a)腔体425的尺寸的目标大小,(b)微处理器525、存储芯片538(图1)、无源元件540(图6)和/或第一有源模拟RF装置532及第二有源模拟RF装置534(图9)的对应尺寸的实际大小和/或(c)微处理器525、存储芯片538(图1)、无源元件540(图6)和/或第一有源模拟RF装置532及第二有源模拟RF装置534(图9)的对应尺寸的目标大小,每个腔体425的宽度(x)、长度(y)和/或深度(z)变化不超过20微米,不超过10微米,不超过5微米或者不超过4微米。例如,每个腔体425的宽度(x)、长度(y)和/或深度(z)比(a)腔体425的尺寸的目标大小,(b)微处理器525、存储芯片538(图1)、无源元件540(图6)和/或第一有源模拟RF装置532及第二有源模拟RF装置534(图9)的对应尺寸的实际大小和/或(c)微处理器525、存储芯片538(图1)、无源元件540(图6)和/或第一有源模拟RF装置532及第二有源模拟RF装置534(图9)的对应尺寸的目标大小大最多20微米,大最多10微米,大最多5微米或者大最多4微米。相比于常规基材,玻璃基材100的层压结构可提供对腔体425的深度的特别精确的控制。

因此,现应理解,通过采用蚀刻速率不同于中心玻璃芯体的包覆层,可在玻璃基材中形成精确的腔体,其接着可用于形成电子封装组件。

术语和解释规范

术语“连接”意为两个构件直接或间接地彼此结合。这种结合本质上可以是静止的或者本质上是可移动的。这种结合可以通过两个构件或两个构件和任何另外的中间构件实现,这些构件可以彼此一体地形成为单个整体,或者两个构件或两个构件与任何另外的中间构件彼此附接。这种结合本质上可以是永久性的,或者本质上可以是可拆卸或可松脱的。

术语“玻璃”和“玻璃组合物”涵盖玻璃材料和玻璃陶瓷材料,如这两类材料通常被理解的那样。同样地,术语“玻璃结构”涵盖包含玻璃的结构。术语“重构晶片和/或面板级封装件”涵盖包括晶片级封装件和面板级封装件的任何尺寸的重构基材封装件。

除非另有说明,否则术语“表面粗糙度”意为如ISO 25178的《产品几何技术规范(GPS)——表面纹理:平面》(Geometric Product Specifications(GPS)–Surfacetexture:areal)所述的以25μm过滤来确定的Ra表面粗糙度。本文中报告的表面粗糙度值使用基恩士(Keyence)共聚焦显微镜来获得。

术语“由……形成”可意为包含、基本上由……组成或由……组成中的一种或多种情况。例如,由特定材料形成的部件可包含该特定材料,基本上由该特定材料组成,或者由该特定材料组成。

空间或方向术语,例如“左”、“右”、“前”、“后”等与附图中所示的主题相关。然而,应理解,所述主题可以假设各种替代性取向,因此,这些术语不应被认为是限制性的。

修饰语,例如“该/所述”、“一个”和“一种”可意味着单数形式或复数形式。并且,当在词语“或”的后面没有“任一”(或指示“或”明确表示为排他性的其他类似语言——例如,x或y中的仅一种等)的情况下使用词语“或”时,其应被解释为包含性的(例如,“x或y”表示x或y中的一种或两种)。

术语“和/或”也应被解释为包含性的(例如“x和/或y”意为x或y中的一种或两种)。在“和/或”或者“或”用作三个或更多个条目的组的连接的情况下,该组应被解释为仅包括一个条目,所有条目在一起,或这些条目的任何组合或数量。另外,说明书和权利要求中使用的术语,例如具有、具备、涵盖和含有应被理解为与术语包含和包括同义。

除非另有说明,否则本说明书(除权利要求外)中所用的表示尺寸、物理特性等的所有数值或措辞应理解为在所有情况下均被术语“约”修饰。至少不是为了将等同原则的应用限制在权利要求,本说明书或权利要求所描述的被术语“约”修饰的每个数值参数应根据所记录的有效数字的位数并运用常用的四舍五入规则进行解释。

所公开的范围应理解为包含任何及所有子范围或各个范围包含的任何和所有的单个值,并且为描述这些子范围或单个值的权利要求提供支持。例如,陈述的1至10的范围应被理解为在最小值1与最大值10之间的任何及所有子范围或者它们之间的单个值(包括和/或不包括端点),并且为描述这些子范围或单个值的权利要求提供支持;也即,以最小值1或更大的数值开始并以最大值10或更小的数值结束的所有子范围(例如5.5至10、2.34至3.56等)或者1至10的任何值(例如3、5.8、9.9994等)。

所有公开的数值应理解是在任一个方向上可变化0-100%,并因此对描述这些数值或者可由这些数值形成的任何及所有范围或子范围的权利要求提供支持。例如,陈述的数值8应被理解成在0至16之间变化(在任一个方向上变化100%),并且为描述该范围自身(例如0至16)、该范围中的任何子范围(例如2至12.5)或该范围中的任何单个数值(例如15.2)的权利要求提供支持。

附图应被解释为例示了按比例绘制的一个或多个实施方式和/或未按比例绘制的一个或多个实施方式。这意味着附图可被解释为,例如,示出的:(a)所有事物均按比例绘制,(b)所有事物均未按比例绘制,或(c)一个或多个特征按比例绘制而一个或多个特征未按比例绘制。因此,附图可单独或彼此组合地为描述任何例示的特征的大小、比例和/或其他尺寸提供支持。此外,所有这些大小、比例和/或其他尺寸应被理解为可在任一个方向上变化0-100%,并因此对描述这些数值或者可由这些数值形成的任何及所有范围或子范围的权利要求提供支持。

权利要求中所述的术语应当通过参考广泛使用的通用词典和/或相关技术词典中的相关条目,本领域技术人员通常理解的含义等来确定它们的普通和惯用含义,并且应理解为,由这些来源中的任何一个或组合所赋予的最广泛的含义(例如,应组合两个或更多个相关词典的条目以提供条目组合的最广泛含义等)仅受以下例外的约束:(a)如果术语的使用方式比其普通和惯用含义更广泛,则该术语应具有其普通和惯用含义加上额外的扩展含义,或(b)如果术语已明确定义为通过在术语后面的短语“本文件中使用的术语应意为”或类似的语言(例如,“该术语意为”、“该术语定义为”、“出于本公开的目的,该术语是指”等等)来描述该术语,则该术语明确定义为具有不同的含义。提到具体实例时使用的“即”、词语“发明”等并不意味着援引例外情况(b)或以其他方式来限制所述的要求保护的术语的范围。除了例外情况(b)所适用的情形外,本文件中的任何内容均不应视为放弃或拒绝权利要求的范围。

权利要求中所述的主题不与本文件中描述或例示的任何实施方式、特征或特征的组合同范围,并且不应被解释为与其同范围。即使在本文件中仅例示和描述了特征或特征组合的一个实施方式也如此。

参考文献的引用

下文列出的每份文件的全部内容通过引用纳入本文件中。如果本文件和一份或多份纳入的文件中使用相同术语,则应将其解释为具有这些来源中任何一个或组合所赋予的最广泛含义,除非该术语在本文件中已明确定义为具有不同含义。如果下列文件与本文件不一致,则以本文件为准。所纳入的主题不应用于限制或缩小明确陈述或描述主题的范围。

-2013年3月13日提交,2016年5月17日授权的题为“Machining of Fusion-DrawnGlass Laminate Structures Containing a Photomachinable Layer”(含有可光加工层的熔合拉制的玻璃层压结构的加工)的第9,340,451号美国专利(申请号13/798,479)(’451专利);

-2015年3月12日提交,2017年3月16日公开的题为“Glass Article and Methodfor Forming the Same”(玻璃制品及其形成方法)的第2017/0073266号美国专利申请公开(申请号15/125,453)(’266申请)。

实施例

通过以下实施例进一步阐述各个实施方式。

根据下表1所列的批料组合物来制备可适合用作结构化制品的玻璃芯体层的多个芯体玻璃组合物。将氧化物成分组分的批料混合、熔化并形成为玻璃板。测量玻璃熔体和得到的结构化制品的性质,并且表2中报告了结果。表2中报告的蚀刻率根据样品在超声浴中接触60℃的50体积%HCl水溶液30分钟后,相对于样品的原始重量的重量损失来表示。

表1:示例性芯体玻璃组合物

表2:示例性芯体玻璃组合物的性质

根据下表3所列的批料组合物来制备可适合用作结构化制品的玻璃包覆层的多个包覆玻璃组合物。将氧化物成分组分的批料混合、熔化并形成为玻璃板。测量玻璃熔体和得到的结构化制品的性质,并且表4中报告了结果。表4中报告的蚀刻率根据样品在超声浴中接触60℃的50体积%HCl水溶液30分钟后,相对于样品的原始重量的重量损失来表示。

表3:示例性包覆玻璃组合物

表4:示例性包覆玻璃组合物的性质

如表2和4中所示,在所选的蚀刻剂(即,50%HCl)中,示例性包覆玻璃组合物比示例性芯体玻璃组合物具有更小的耐久性(即具有更高的蚀刻率)。

如本文所述形成结构化制品并且其包括由示例性芯体玻璃组合物(例如,样品1-1至1-4)形成的玻璃芯体层和由示例性包覆玻璃组合物(例如,样品2-1至2-68)形成的玻璃包覆层。

对本领域的技术人员显而易见的是,可以在不偏离所要求保护的主题的精神或范围的情况下进行各种修改和变动。因此,所要求保护的主题不受所附权利要求书及其等同形式以外的任何内容所限。