监控及复原异质性元件的系统及方法

文献发布时间:2023-06-19 12:22:51

技术领域

本公开主要涉及定制化(custom)集成电路(integrated circuit;IC)的固件复原。更具体地说,本公开的观点涉及例如为一现场可编程门阵列(field programmablegate array;FPGA)的定制化集成电路的固件复原。

背景技术

服务器被大量地运用在高需求的应用中,例如基于网络的系统(network basedsystems)或数据中心。运算应用的云端的出现,已增加对于数据中心的需求,及其他重度的运作需求。数据中心具有为数众多的服务器,该等服务器储存数据并运行被远端连接的电脑装置的使用者所存取的应用。典型的数据中心具有附带供电及通讯连接的物理机箱结构。每个机架可支承多个运算服务器及储存服务器。

由于潜在的专业化应用的种类增加,最近几年服务器设计已移往异质性(heterogeneous)运算架构。使用异质性运算架构允许分担系统中的CPU负载,以及处理特定任务的数据。因此,异质性架构透过负载分担及共享多个专业化功能的命令,改善了服务器效能。这些改善盛行于用在新一代科技例如人工智能(artificial intelligence;AI)、5G、机器学习以及大数据分析应用的服务器上。

定制化集成电路(custom integrated circuit),例如现场可编程门阵列(fieldprogrammable gate array;FPGA),通常被使用在异质性运算架构中,因为FPGA具有弹性设计的好处。FPGA允许使用者为FPGA上的多个逻辑门设计不同的功能。使用FPGA的好处是,使用者能使用软件来“程式化”FPGA IC的逻辑门硬件,以执行特定的任务或其他任务。由于FPGA系硬件,FPGA执行专业化任务,比执行软件程序的同质的(homogeneous)处理器快。因此,FPGA可被“程序化”来以硬件的速度执行多个不同的任务,藉此免除需要专业化硬件来执行这种任务。

由于这种定制化IC系被使用者所设置,在设置软件中可能存在设计缺陷,因而导致在IC执行期间的系统停机(hang-up)或错误。因此,需要有定制化IC的自动复原机制,来改善这种系统的可靠性。然而,在现有的服务器中,并没有定制化IC的自动复原机制。

因此,需要有系统包含自动复原机制,以监控及复原定制化IC的固件。也需要有系统能够在复原定制化IC的固件的同时,监控及复原基板管理控制器(baseboardmanagement controller;BMC)。更进一步需要系统,不需要CPU周期(CPU cycle)时间来处理轮询(polling)程序,以改善系统效能。另外需要、系统,尽管端点错误(side errors)发生,藉由复原固件来改善系统的可靠性。

发明内容

被公开的范例是一种提供监控及复原异质性元件的系统。系统包含以固件运作的集成电路。系统包含被耦接至集成电路的储存装置。储存装置储存集成电路的固件映像档。控制器被耦接至集成电路。控制器可运作来周期性地判断集成电路的运作状态,并从已判断的运作状态来判断集成电路的故障。控制器发送被储存的固件映像档给集成电路,并将固件映像档安装在集成电路上。控制器判断固件映像档的安装是否致使集成电路的复原。

在被公开的范例系统的其他实施中,控制器是基板管理控制器(baseboardmanagement controller;BMC)或场域可程序逻辑阵列(field programmable gate array;FPGA)。在另一实施中,集成电路系FPGA或BMC的其中之一。在另一实施中,控制器可运作来响应于侦测到故障,重设集成电路。在另一实施中,集成电路发送周期性的命令给控制器,且控制器基于周期性的命令判断故障。在另一实施中,系统包含被耦接至集成电路及控制器的非挥发性随机存取存储器(non-volatile random access memory;NVRAM)。集成电路周期性地将状态数据写入NVRAM。控制器基于状态数据判断集成电路的故障。在另一实施中,储存装置系闪存。在另一实施中,控制器与操作系统或基本输入输出系统(basic inputoutput system;BIOS)的其中之一联系。在另一实施中,若固件映像档的安装并没有致使集成电路的复原,则操作系统或BIOS可运作来停用连接至集成电路的硬件端口(hardwareport)。

另一被公开的范例系一种监控及复原以固件运作的异质性集成电路的方法。集成电路的固件映像档被储存在储存装置中。经由控制器,周期性地判断集成电路的运作状态。集成电路的故障被判断。被储存的固件映像档被发送给集成电路。固件映像档被安装在集成电路上。控制器判断固件映像档的安装是否致使集成电路的复原。

在被公开的范例方法的其他实施中,控制器系BMC或FPGA。在另一实施中,集成电路系FPGA或BMC的其中之一。在另一实施中,方法包含响应于侦测到故障,重设集成电路。在另一实施中,故障系基于集成电路发送给控制器的周期性命令所判断。在另一实施中,周期性地判断集成电路的运作状态,包含集成电路将状态数据写入NVRAM,及控制器读取被写入的状态数据。在另一实施中,储存装置系闪存。在另一实施中,控制器被OS或BIOS所指挥。在另一实施中,方法包含若固件映像档的安装并没有致使集成电路的复原,则停用连接至集成电路的硬件端口。

另一被公开的范例是一种包含以固件运作的FPGA集成电路的运算系统。系统包含被耦接至FPGA集成电路、储存FPGA集成电路的固件映像档的储存装置。系统包含被耦接至FPGA集成电路的BMC。BMC可运作来周期性地判断FPGA集成电路的运作状态。BMC从被判断的运作状态来判断FPGA集成电路是否有故障。BMC发送被储存的固件映像档给FPGA集成电路。BMC将固件映像档安装在FPGA集成电路上。BMC判断固件映像档的安装是否致使FPGA集成电路的复原。

在被公开的运算系统的其他实施中,FPGA集成电路可运作来周期性地判断BMC的运作状态;从已判断的运作状态来判断BMC的故障;从储存装置发送被储存的一BMC固件映像档给BMC;将BMC固件映像档安装在BMC上;及判断BMC固件映像档的安装是否致使BMC的复原。

以上发明内容并非意图代表本公开的每个实施例或每个观点。相反地,前述的发明内容仅提供在此列举的某些新颖的观念及特征的范例。以上特征及优点,以及本公开的其他特征及优点,当关联于搭配的图式及附加的请求项,从以下用来实行本发明的代表性实施例及模式的详细叙述中,将会轻易地清晰可见。

附图说明

本公开将可从以下示范的实施例的叙述搭配附带的附图更佳地理解,其中:

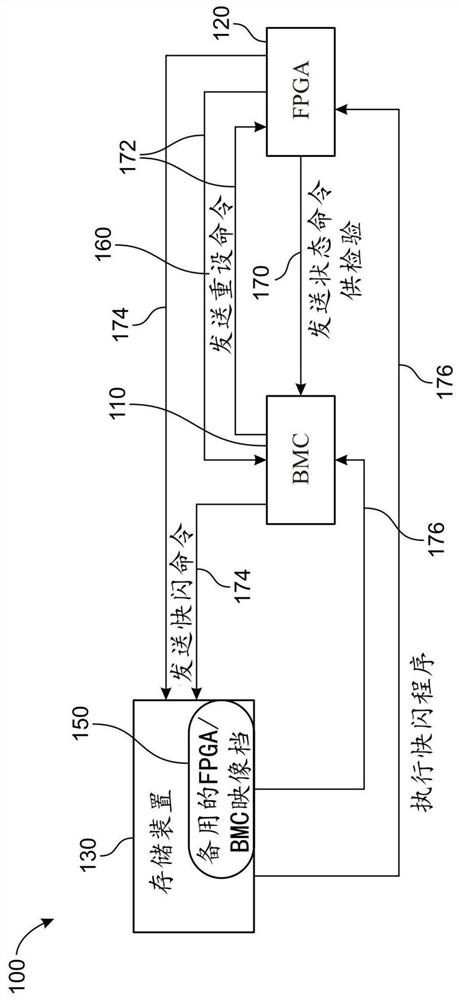

图1是根据本公开的某些观点,一种基于FPGA的范例系统的方块图。

图2是根据本公开的某些观点,图1中的范例FPGA系统的固件复原例行程序的流程图。

图3是根据本公开的某些观点,另一种基于FPGA的系统的方块图。

图4是根据本公开的某些观点,图3中的范例系统的固件复原例行程序的流程图。

本公开容许各式各样的修改及替代的形式。某些代表性的实施例已藉由附图中的范例所显示,并将在此被详细叙述。然而应被理解的是,本发明并非意图受限于被公开的特定形式。相反地,本公开欲涵盖落在如附加的权利要求所定义本发明的精神与范围内的所有修改、均等物及替代选项。

具体实施方式

本发明能以许多不同的形式实施。代表性的实施例被显示在附图中,并将在此被详细叙述。本公开系本发明的原则的范例或图解,且并非意图将本公开的广泛的观点限制于绘式的实施例。在此基础上,例如在摘要、发明内容及实施方式等段落中被公开,但并未明确地在权利要求中列举的元件及限制,不应被单独地、集体地、暗示地、推论地或其他方式地并入至权利要求中。为了本详细叙述的目的,除非被具体地否认,否则单数形包含复数形,反之亦然;且“包含”一词意指“无限制地包含”。此外,表近似的词汇,例如“约”、“几乎”、“大体上”、“大概”及类似的词汇,能在此被用来意指“在”、“近”、“近于”、“3-5%的范围内”或“可接受的制造公差内”,或者其任何的逻辑组合。

本公开涉及提供在储存装置(例如闪存)中,备用的专业化集成电路映像档。集成电路被周期性地检验,且若侦测到故障(failure),映像档可被提供来重设集成电路的运作。

图1显示允许对例如为集成电路的异质性元件监控及复原的系统100。经由被整合的控制器的固件映像档,藉由使用系统100的现有的控制器,复原可被自动地执行。系统100包含基板管理控制器(BMC)110、例如为现场可编程门阵列(FPGA)120的专业化集成电路,以及例如为闪存130的储存装置。在此范例中,FPGA 120是Intel Arria 10FPGA片上系统(System on a Chip;SoC),但其他专业化异质性集成电路,例如复杂可编程逻辑装置(complex programmable logic device;CPLD),可运用在此被叙述的原则。在此范例中,闪存130包含FPGA固件及BMC固件的固件映像档150。BMC 110及FPGA 120被耦接至闪存130。在此范例中,智能型平台管理界面(Intelligent Platform Management Interface;IPMI)总线160将BMC 110与FPGA 120连接起来。

系统100藉由监控及复原,为BMC 110及FPGA 120提供可靠的运作程序。固件映像档150中的固件映像档,系为了复原BMC 110或FPGA 120的运作的可靠的备用固件映像档。这些映像档被储存在闪存130中。看门狗计时器(watch dog timer)为了FPGA120及BMC 100两者而设置。

FPGA120经由IPMI总线160上的命令,周期性地发送信息给BMC 110(170:发送状态命令供检验)。当接收到该命令时,BMC 110回应FPGA 120。该命令包含来自FPGA 120的状态及错误信息。BMC 110对该命令的回应包含BMC状态信息,以供FPGA 120检验。若在给BMC110的命令中有错误信息,或者在看门狗计时器所设定的时间届满前该命令未被接收到,BMC 110将发送检验状态命令给FPGA 120。在此范例中,检验状态命令将被BMC 110发送三次。若没有接收到对于检验状态命令的回应,或者FPGA 120回应错误状态,BMC 110将记录故障状态。同样地,若没有接收到对该命令的回应,或者在来自BMC 110的回应中接收到错误状态,则FPGA 120能发送检验状态命令给BMC 110。若没有接收到对于检验状态命令的回应,或者来自BMC 110的回应指示为故障,则FPGA 120可为BMC 110记录故障状态。

当没有接收到对于检验状态命令的回应,或者接收到错误回应时,FPGA 120或BMC110将尝试重设程序(172:发送重设命令)。若重设程序成功,系统将回到正常的运作。若重设程序不成功,检验状态命令将再次被呼叫。若检验状态命令失败,或者接收到错误回应,FPGA 120或BMC 110将呼叫快闪复原程序(flash recovery procedure),以从闪存130复原FPGA/BMC固件映像档150(174:发送快闪命令)。固件映像档150因此被从闪存130发送给BMC110或FPGA 120(176:执行快闪程序)。若固件安装成功,BMC 110或FPGA 120将BMC 110或FPGA 120已被复原的消息通知系统例行程序(system routine),例如基本输入输出系统(basic input output system;BIOS)或操作系统(operating system;OS)。系统100于是回传至周期性发送信息给BMC 110的FPGA 120。

若对检验状态命令的回应为故障,且快闪固件映像档故障,则系统将例如为BMC110或FPGA 120的硬件已故障的消息通知BIOS及OS。BIOS/OS于是停用连接至BMC 110或FPGA 120的硬件端口(hardware port)。OS停止存取FPGA 120或BMC 110,并发送错误讯息给管理者。

图2是被图1中的系统100的操作系统所执行的复原例行程序(recovery routine)200的流程图。复原例行程序200备份可靠的固件映像档,例如在固件映像档150中的BMC及FPGA固件映像档,以供FPGA/BMC的复原(步骤210)。FPGA/BMC看门狗计时器被设置(步骤212)。FPGA 120根据看门狗计时器,经由IPMI命令周期性地发送状态信息给BMC 110(步骤214)。当接收到IPMI命令,BMC 110将状态信息回应给FPGA 120。若该回应为正常(步骤216,否),则例行程序返回并继续经由IPMI命令发送信息给BMC 110,以及将来自BMC 110的回应发送给FPGA 120(步骤214)。若该回应或命令包含错误信息,或者在看门狗期间并未接收到回应(步骤216,是),则例行程序发送检验状态命令给FPGA 120或BMC 110(步骤218)。对应的FPGA 120或BMC 110判断对于检验状态命令的回应是否为故障,或者没有接收到回应(步骤220)。若检验状态命令指示为故障,或者没有接收到回应,BMC 110或FPGA 120都不会提供故障状态纪录入口(fail state log entry)(步骤222)。

若对于任何检验状态命令有正面的回应(步骤220,否),则例行程序返回至FPGA120发送周期性命令给BMC 110所在的看门狗状态(步骤214)。若接收到指示为故障的回应,或者对于检验状态命令没有回应,则提供故障状态纪录入口(步骤222)。FPGA 120或BMC 110于是呼叫重设程序,以分别复原FPGA 120或BMC 110(步骤224)。重设程序于是被FPGA 120或BMC 110初始化。若FPGA 120或BMC 110传达,因而指示重设系成功的(步骤226,否),则例行程序将BMC 110或FPGA 120已复原的消息通知BIOS或操作系统(OS)(步骤228)。例行程序返回并继续经由IPMI命令发送信息给BMC 110(步骤214)。

若重设程序分别复原FPGA 120或BMC 110失败,则例行程序发送一系列检验状态命令给FPGA 120(步骤230)。例行程序判断是否有对于任何检验状态命令的正面回应(步骤232)。若对于任何检验状态命令有正面回应(步骤232,否),则例行程序返回至FPGA 120发送周期性命令给BMC 110所在的看门狗状态(步骤214)。若对于任何检验状态命令皆无回应,或者接收到故障回应(步骤232,是),则BMC 110及FPGA 120提供故障状态纪录入口(步骤234)。FPGA 120或BMC 110于是呼叫快闪程序,将来自闪存130中所储存的固件映像档150的适当的固件映像档,复原至FPGA120或BMC 110(步骤236)。来自固件映像档150的被储存的固件映像档,被安装在FPGA 120或BMC 110上。例行程序于是判断FPGA120或BMC 110是否借着被安装的固件映像档而正确地运行(步骤238)。若FPGA 120或BMC 110正确地运行,则例行程序将BMC 110或FPGA 120已复原的消息通知BIOS或OS(步骤228)。例行程序返回并继续经由IPMI命令发送信息给BMC 110(步骤214)。

若快闪程序失败(步骤238,是),则例行程序将BMC 110或FPGA 120已故障的消息通知BIOS及OS(步骤240)。BIOS或OS将停用连接至故障的BMC 110或故障的FPGA 120的硬件端口(步骤242)。BIOS或OS将发送错误讯息给管理者(步骤244)。

图3是允许对异质性集成电路监控固件的另一范例系统300的方块图。系统300包含基板管理控制器(BMC)310、例如为现场可编程门阵列(FPGA)320的专业化集成电路,以及一闪存330。在此范例中,闪存330包含固件映像档340,固件映像档340包含FPGA及BMC固件的映像档。BMC 310及FPGA 320被耦接至闪存330。

BIOS 360被耦接至闪存330及BMC 310。非暂时性随机存取存储器(non-volatilerandom access memory;NVRAM)370被连接至BIOS 360、BMC 310及FPGA 320。BIOS 360、BMC310及FPGA 320个别将状态数据写入至NVRAM 370。FPGA 320及BMC 310皆能从NVRAM 370读取状态数据,并且可因此判断其他元件的状态。BIOS状态亦可被FPGA 320或BMC 310所监控。

系统300为FPGA 320提供可靠的运作程序。储存在闪存330中的固件映像档340,系为了复原BMC 310或FPGA 320的运作的可靠的备用固件映像档。看门狗计时器为了FPGA320及BMC 310两者而设置。

BMC 310、FPGA 320及BIOS 360个别以周期性的方式将状态数据写入至NVRAM 370(350:将状态数据写入至NVRAM;以及380:读取/写入状态)。BMC 310读取关于FPGA 320及BIOS 360的被写入的状态数据。FPGA320亦读取来自BMC 310、关于BMC 310的被写入的状态数据(380:读取/写入状态)。若在来自FPGA 320的状态数据中发现错误信息,则BMC 310将发送检验状态命令给FPGA 320。若在来自BMC 310的状态数据中发现错误信息,则FPGA 320将发送检验状态命令给BMC 310。在此范例中,检验状态命令将被BMC 310或FPGA320发送三次。若没有接收到对于检验状态命令的回应,或者接收到的回应指示为故障,BMC 310或FPGA320将记录故障状态。

当没有接收到对于检验状态的回应,或者故障被指示,FPGA320或BMC 310将尝试重设BMC 310或FPGA320(382:发送重设命令)。若重设程序成功,系统将回到正常的运作。若重设程序不成功,检验状态命令将再次被呼叫。若检验状态失败,FPGA 320或BMC 310将呼叫快闪程序,以藉由存取来自被储存在闪存330中的固件映像档340的固件映像档,复原FPGA/BMC的固件(384:发送快闪命令)。固件映像档因此被发送给BMC 310或FPGA 320(386:执行快闪程序)。若固件安装成功,BMC 310或FPGA 320将BMC 310或FPGA 320已被复原的消息通知系统例行程序,例如BIOS 360或操作系统。系统300于是回到正常的运作。

若对检验状态命令的回应为故障,且快闪固件映像档故障,则系统将硬件已故障的消息通知BIOS 360。BIOS/操作系统停用连接至BMC 310或FPGA 320的硬件端口,且操作系统停止存取FPGA 320或BMC 310,并发送错误讯息给管理者。BMC 310亦可从被写进NVRAM370的状态信息中,独立地监控BIOS 360的状态。若状态信息指示为BIOS故障,则BMC 310可尝试发送重设命令,且若发送重设命令失败,可从闪存330复原BIOS固件映像档。

图4是被系统300的操作系统所执行的复原例行程序400的流程图。复原例行程序400备份可靠的固件映像档,例如在固件映像档340(图3中所示)中固件映像档,以供FPGA/BMC的复原(步骤410)。FPGA/BMC看门狗计时器被设置(步骤412)。BMC 310、FPGA 320及BIOS360个别周期性地将对应的状态数据写入至NVRAM 370(步骤414)。FPGA 320及BMC 310检验来自NVRAM 370的被写入的状态数据(步骤416)。若状态数据指示为FPGA 320及BMC 310的正常运作(步骤418,否),则例行程序返回,且BMC 310、FPGA 320及BIOS 360继续将状态数据写入至NVRAM 370(步骤414)。若状态数据包含错误信息,或者在看门狗期间并未接收到回应(步骤418,是),则例行程序发送检验状态命令给FPGA 320(步骤420)。

例行程序判断是否有对于任何检验状态命令的正面回应(步骤422)。若有正面回应(步骤422,否),则例行程序返回至BMC 310、FPGA 320及BIOS 360将状态数据写入至NVRAM 370所在的看门狗状态(步骤414)。若对于任何检验状态命令皆无接收到回应,或者接收到指示为故障的回应(步骤422,是),则BMC 310或FPGA 320提供故障状态纪录入口(步骤424)。FPGA 320或BMC 310于是呼叫重设程序,以分别复原FPGA 320或BMC 310(步骤426)。重设程序于是被BMC 310或FPGA 320所尝试。若FPGA 320或BMC 310传达回应指示重设系成功的(步骤428,否),则例行程序将BMC 310或FPGA 320已复原的消息通知BIOS或操作系统(OS)(步骤430)。例行程序返回,且BMC 310、FPGA 320及BIOS 360继续将状态数据写入至NVRAM 370(步骤414)。

若重设程序分别复原FPGA 320或BMC 310失败(步骤428,是),则例行程序发送一系列检验状态命令给FPGA320或BMC 310(步骤432)。例行程序于是判断是否有对于任何检验状态命令的正面回应(步骤434)。若对于任何检验状态命令有正面回应(步骤434,是),则例行程序返回至BMC 310、FPGA 320及BIOS 360将状态数据写入至NVRAM 370所在的看门狗状态(步骤414)。若对于任何检验状态命令皆无回应,或者接收到故障回应(步骤434,是),则BMC 310或FPGA 320提供故障状态纪录入口(步骤436)。FPGA 320或BMC 310于是呼叫快闪程序,将来自闪存330中所储存的固件映像档340的固件映像档,复原至FPGA 320或BMC310(步骤438)。在固件映像档已分别被安装在FPGA 320或BMC 310上之后,例行程序于是判断FPGA 320或BMC 310是否正确地运行(步骤440)。若FPGA 320或BMC 310正确地运行,则例行程序将BMC 310或FPGA 320已复原的消息通知BIOS或OS(步骤430)。例行程序于是返回,且BMC 310、FPGA 320及BIOS 360继续将状态数据写入至NVRAM 370(步骤414)。

若快闪程序失败(步骤440,是),则例行程序将BMC 310或FPGA 320已故障的消息通知BIOS 360及OS(步骤442)。BIOS 360或OS停用连接至故障的BMC 310或FPGA 320的硬件端口(步骤444)。BIOS 360或OS发送错误讯息给管理者(步骤446)。

本程序的好处是,允许具有第三方客制的集成电路自动地复原故障的集成电路。因此,本程序藉由避免系统在涉入集成电路的运行时间运作(run time operation)上停机,改善系统的可靠性。以上范例例行程序不需要CPU周期时间来处理轮询程序,且不需要额外的硬件来复原,因为已存在于异质性运算架构中的组件被使用于复原例行程序。于是故障的集成电路的自动复原无须仰赖网络管理员来处理错误。因此,具有集成电路的系统可在短时间内被复原。此外,系统允许同时监控BMC,并允许BMC记录及监控更多第三方的集成电路信息。

根据本公开的某些观点,图2及图4是例如那些在图1及图3中,包含专业化集成电路的系统的自动复原例行程序的流程图。图2及图4中的流程图,系专业化集成电路的自动复原程序的范例机器可读指令(machine readable instruction)的代表。在此范例中,机器可读指令包括给(a)处理器;(b)控制器;及/或(c)一个或更多其他合适的处理装置来执行的一演算法。该演算法可在被储存于实体的媒体上的软件所实施,实体的媒体可例如为闪存、光碟唯读存储器(CD-ROM)、磁片(floppy disk)、硬碟、数位影音光盘/数字多功能光盘(digital video disk/digital versatile disk;DVD),或其他存储器装置。然而,本技术领域的普通技术的人将轻易地理解,整个演算法及/或其部分能替代地被处理器之外的装置所执行,且/或以熟知的方式(例如,可被专用集成电路(application specificintegrated circiut;ASIC)、可编程逻辑装置(programmable logic device;PLD)、现场可编程逻辑装置(field programmable logic device;FPLD)、现场可编程逻辑阵列(fieldprogrammable gate array;FPGA)、离散逻辑(discrete logic)等所实施)被实施于固件或专用的硬件中。举例而言,界面的任何或所有的元件能被软件、硬件及/或固件所实施。并且,被流程图所代表的某些或所有的机器可读指令可被手动实施。此外,虽然范例演算法系参考图3-4中所绘示的流程图而叙述,本技术领域的普通技术的人将轻易地理解,实施范例机器可读指令的许多其他方法,可被替代地使用。举例而言,各方块的执行顺序可被改变,且/或某些被叙述的方块可被改变、删减或合并。

如本申请中所使用的“元件”、“模组”、“系统”或类似的词汇,通常系指与电脑相关的实体,可以是硬件(例如电路)、硬件与软件的组合、软件,或者与运作机器相关、具有一种或更多种特定功能的实体。举例而言,元件可以是但不限于在处理器(例如数字信号处理器)上执行的程序、处理器、物件、可执行档、执行线程(thread of execution)、程序,及/或计算机。作为示例,在控制器上执行的应用,以及控制器本身,皆可为元件。一个或更多个元件可常驻于程序及/或执行线程之内,且一个元件可被局限在一台计算机上及/或分散在两台或更多台计算机之间。此外,“装置”可出自于特殊设计的硬件的形式;藉由执行其上使硬件能执行特定功能的软件所特制出的通用硬件;储存在计算机可读取媒体上的软件;或者其组合。

在此所使用的术语仅以叙述特定的实施例为目的,而并非意图限制本发明。如在此所使用的,单数形“一”及“该”意图亦包含复数形,除非文意明显另有所指。此外,倘若“包含”、“具有”一词或者其变形,被使用在详细叙述及/或权利要求中,这类词汇意图被包含在类似于“包括”一词的方式中。

除非另有定义,在此所使用的所有词汇(包含技术性及科学性的词汇),与本技术领域的普通技术的人一般所理解的,具有相同的含意。此外,像是被定义在一般所使用的字典中的词汇,应被解读为具有与它们在相关技术的文意中一致的含意,且除非在此被明确地如此定义,否则该等词汇不会被解读为理想化或过度正式的概念。

虽然本发明的各种实施例已被叙述如上,应被理解的是,该等实施例仅被呈现来作为范例,而非限制。即使本发明已参考一种或更多种实施方式所绘示及叙述,当阅读及理解本说明书及附加的附图时,均等的替换及修改将可被其他熟习此项技术者想到或知晓。此外,虽然本发明的特定的特征可仅被数个实施例的其中之一所公开,这种特征可与其他实施例的一个或更多个其他特征组合,而此其他特征对于任何给定的或特定的应用可能是期望的或有利的。因此,本发明的广度及范围不应受限于任何以上叙述的实施例。反之,本发明的范围应根据以下的权利要求及其均等物所定义。

【符号说明】

100:系统

110:BMC

120:FPGA

130:闪存

150:固件映像档

160:IPMI总线

170:发送状态命令供检验

172:发送重设命令

174:发送快闪命令

176:执行快闪程序

200:复原例行程序

210-244:步骤

300:系统

310:BMC

320:FPGA

330:闪存

340:固件映像档

350:将状态数据写入至NVRAM

360:BIOS

370:NVRAM

380:读取/写入状态

382:发送重设命令

384:发送快闪命令

386:执行快闪程序

400:复原例行程序

410-446:步骤

- 监控及复原异质性元件的系统及方法

- 监控系统及应用该监控系统监控电气元件运行的方法