一种主机板及服务器

文献发布时间:2023-06-19 09:47:53

技术领域

本发明涉及计算机技术领域,尤其涉及一种主机板及服务器。

背景技术

主板又叫主机板(mainboard)、系统板(systemboard)或母板(motherboard)是计算机的重要组成部分,决定了计算机系统的功能和性能特点。

目前市场上的主板通常是按照特定应用系统要求进行设计,一些主板的IO(Input/Output,输入/输出)信号传输速率受IO(Input/Output,输入/输出)接口种类(主要指采用的通信标准类型)的限制,不便于实现高速信号的传输。

发明内容

有鉴于此,本发明实施例提供一种主机板及服务器,便于实现高速信号的传输。

为达到上述发明目的,采用如下技术方案:

第一方面,本发明实施例提供的主机板,包括印制电路板,在所述印制电路板上设有处理器插座、内存插槽及第一速率接口组件,所述处理器插座用于安装处理器,所述第一速率接口组件包括多个PCIE插槽、OCP连接器、SATA连接器及M.2连接器;

所述处理器插座分别与多个内存插槽、PCIE插槽、OCP连接器、SATA连接器及M.2连接器电连接,每个内存插槽支持安装UDIMM、RDIMM和LRDIMM中的任意一种。

可选地,所述处理器插座用于安装处理器,支持8个通道内存插槽,每个通道的内存插槽支持安装两个内存模块。

可选地,所述PCIE插槽包括第一PCIE插槽、第二PCIE插槽、第三PCIE插槽、第四PCIE插槽及第五PCIE插槽,所述第一PCIE插槽连接处理器插座上与处理器第一组信号通路对应的第一输入/输出接口,所述第二PCIE插槽连接处理器插座上与处理器第二组信号通路对应的第二输入/输出接口,所述第三PCIE插槽连接处理器插座上与处理器第三组信号通路对应的第三输入/输出接口,所述第四PCIE插槽连接处理器插座上与处理器第四组信号通路对应的第四输入/输出接口,所述第五PCIE插槽连接处理器插座上与处理器第五组信号通路对应的第五输入/输出接口;

其中,所述第一PCIE插槽至少支持PCIE标准卡x8/x4/x2/x1,第二PCIE插槽、第三PCIE插槽、第四PCIE插槽及第五PCIE插槽分别支持PCIE标准卡x16/x8/x4/x2/x1。

可选地,所述第七组信号通路至少包括6路,所述SATA连接器包括:

MiniSAS HD连接器,所述MiniSAS HD连接器设有4组或6组,每组设有4个SATA接口,其中,至少有两组MiniSAS HD连接器通过所述第一信号切换器连接所述第六输入/输出接口;

7针SATA接口;所述7针SATA接口设有2组,分别与所述第七输入/输出接口连接,用于与第七组信号通路中的2路连接;

及SATA接口的光盘连接器,所述SATA接口的光盘连接器支持连接光盘驱动器或固态硬盘。

可选地,所述处理器插座上具有与处理器第七组信号通路对应的第七输入/输出接口,所述第七组信号通路至少包括5路,所述第七输入/输出接口传输的其中5路通过第二信号切换器与所述M.2连接器连接,其中4路用于配置成PCIE信号,1路用于配置成SATA信号,所述第二信号切换器用于在4路PCIE信号的一路与1路SATA信号之间切换。

可选地,所述印制电路板上还设有基板管理控制器及第二速率接口组件,所述第二速率接口组件的信号传输速率小于所述第一速率接口组件的传输速率,所述基板管理控制器一端与所述处理器安装座通过印制线路电连接,另一端与所述第二速率接口组件电连接,用于使主板支持远程任务管理。

可选地,所述第二速率接口组件包括UART接口、JTAG接口、SPI接口、LPC接口、I2C接口及APML接口。

第二方面,本发明实施例提供一种服务器,包括第一方面任一所述的主机板,所述主机板上的处理器插座中安装有处理器。

本发明实施例提供的主机板及服务器,通过对其结构本身进行改进,在所述印制电路板上设有处理器插座、内存插槽及第一速率接口组件,所述处理器插座用于安装处理器,所述第一速率接口组件包括多个PCIE插槽、OCP连接器、SATA连接器及M.2连接器;所述处理器插座分别与多个内存插槽、PCIE插槽、OCP连接器、SATA连接器及M.2连接器电连接,每个内存插槽支持安装UDIMM、RDIMM和LRDIMM中的任意一种。由于主板采用的第一速率接口组件,例如PCIE插槽、SATA连接器等具有较高带宽,其可以支持高速信号传输。另外,采用的多个(即俗称多通道)内存插槽,例如,UDIMM、RDIMM和LRDIMM中的任意一种,可支持较高频率的内存模块。综上采用的硬件及其拓扑结构组成的主机板,便于实现高速信号的传输。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

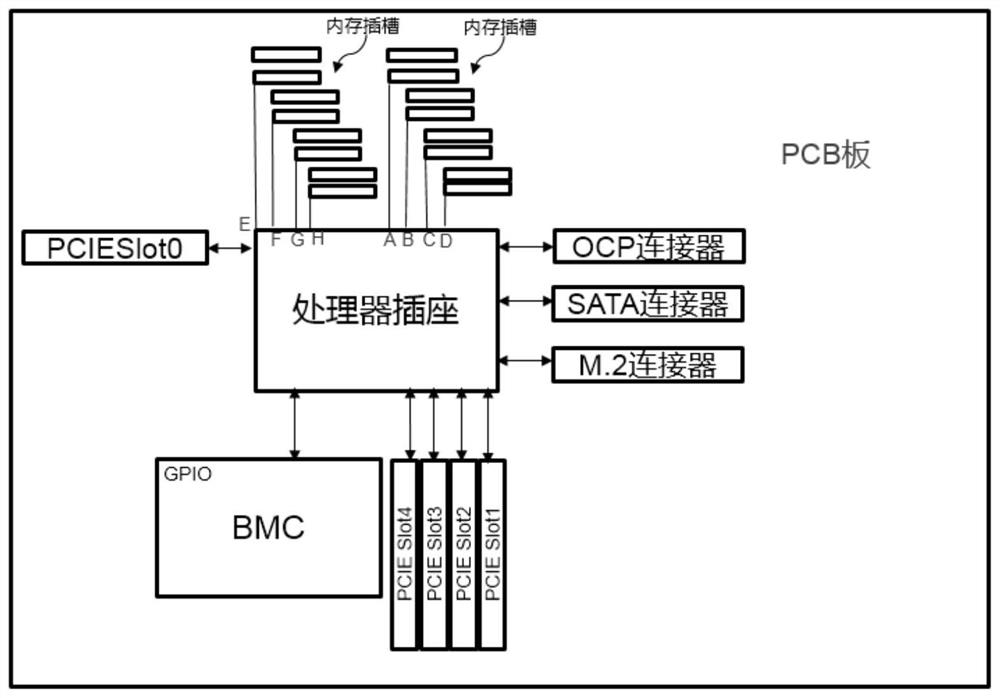

图1为本发明主机板一实施例结构示意框图;

图2为本发明中主机板另一实施例结构示意框图;

图3为本发明主机板支持的CPU一实施例结构示意框图;

图4为本发明中主机板另一实施例结构示意框图;

图5为本发明中主机板另一实施例结构示意框图;

图6至图8分别为本发明中主机板具有JTAG接口功能电路的一实施例结构示意框图;

图9为本发明中主机板具有SPI接口功能电路一实施例结构示意方框图;

图10为本发明主机板具有BMC的功能电路的一实施例结构示意方框图;

图11为通过BMC网口远程实现主机板开、关机及重启电路示意图;

图12为本发明主机板具有温度控制系统交互接口功能电路的一实施例结构示意方框图。

具体实施方式

下面结合附图对本发明实施例进行详细描述。

应当明确,为了更加清楚说明本发明,在以下的具体实施例中描述了众多技术细节,本领域技术人员应当理解,没有其中的某些细节,本发明同样可以实施。另外,为了凸显本发明的发明主旨,涉及的一些本领域技术人员所熟知的方法、手段、零部件及其应用等未作详细描述,但是,这并不影响本发明的实施。本文所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

图1为本发明主机板一实施例结构方框图;参看图1所示,本发明实施例提供的主机板(Mainboard),通常称为主板,又叫系统板(systemboard)或母板(motherboard);适用于个人电脑、工控机、服务器等各种电子设备中。所述主机板包括印制电路板(Printedcircuit boards),俗称PCB板;在所述印制电路板上设有处理器插座,用于安装处理器(CPU:Central Processing Unit/Processor),所述处理器插座也称为处理器插槽,其主要分为Socket和Slot两种。

在一实施例中,所述中央处理器为海光7100或海光7200系列处理器,其隶属于X86CPU,在主机板的印制电路板上设计1颗SP3 4094封装Socket插座,用于安装海光7100/7200CPU;海光7100/7200 CPU芯片是一颗高性能、IO接口丰富的芯片,其中一部分管脚是功能可配置接口。

内存插槽;其中,参看图3所示,海光7100/7200 CPU共支持8个通道内存插槽(英文为:DDR Channel),如图2所示,其通道分别标识为:A、B、C、D、E、F、G和H,每个通道(Channel)内存插槽支持2个双列直插式存储模块(dual In-line memory module,简称DIMM),共支持16条DDR4-2667速率的UDIMM/RDIMM/LRDIMM。

第一速率接口组件;其包括多个PCIE(PCI-Express:peripheral componentinterconnect express,是一种高速串行计算机扩展总线标准)插槽、OCP连接器、SATA连接器及M.2连接器。

所述处理器插座分别与多个内存插槽、PCIE插槽、OCP连接器、SATA连接器及M.2连接器电连接,每个内存插槽支持安装UDIMM、RDIMM和LRDIMM中的任意一种。

OCP连接器支持OCP扣卡,SATA连接器支持标准SATA硬盘,M.2连接器支持M.2SSD。其中,PCIE、OCP、SATA及M.2为通信技术领域术语,可以简单理解为接口的通信传输标准。

本发明实施例提供的主机板,通过对其结构本身进行改进,由于主板采用的第一速率接口组件,例如PCIE插槽、SATA连接器等具有较高带宽,其可以支持高速信号传输。另外,采用的多个(即俗称多通道)内存插槽,例如,UDIMM、RDIMM和LRDIMM中的任意一种,可支持较高频率的内存模块。综上采用的硬件及其拓扑结构组成的主机板,便于实现高速信号的传输。

所述PCIE插槽用于连接PCIE设备;在一些实施例中,所述PCIE插槽包括第一PCIE插槽、第二PCIE插槽、第三PCIE插槽、第四PCIE插槽及第五PCIE插槽,在图1及图2中依次对应5个PCIE x16的Slot0/1/2/3/4。所述第一PCIE插槽连接处理器插座上与处理器第一组信号通路(Lane)G3[15:8]对应的第一输入/输出接口,所述第二PCIE插槽连接处理器插座上与处理器第二组信号通路P2[15:0]对应的第二输入/输出接口,所述第三PCIE插槽连接处理器插座上与处理器第三组信号通路P3[15:0]对应的第三输入/输出接口,所述第四PCIE插槽连接处理器插座上与处理器第四组信号通路G0[15:0]对应的第四输入/输出接口,所述第五PCIE插槽连接处理器插座上与处理器第五组信号通路G1[15:0]对应的第五输入/输出接口。

如图2所示,Slot0:为x8 PCIE连接器,连接CPU的G3[15:8]信号,当然,Slot0也可选择支持x16。Slot1~2:均为x16 PCIE连接器,分别各自连接CPU的P2/P3[15:0]信号;Slot3:支持x16 PCIE信号,连接CPU的G0[15:0]信号;Slot4:支持x16 PCIE信号,连接CPU的G1[15:0]信号。

其中,所述第一PCIE插槽至少支持PCIE标准卡x8/x4/x2/x1,第二PCIE插槽、第三PCIE插槽、第四PCIE插槽及第五PCIE插槽分别支持PCIE标准卡x16/x8/x4/x2/x1。

所述x16、x8、x4、x2和x1分别表示传输通道(即前述的通路,英文为Lane)的数量,例如,x16表示16通道。

本实施例中,所述PCIE插槽为PCIE 3.0插槽,设置五个,其中3个为垂直槽(Vertical Slot),1个为跨槽(Straddle Slot),另1个为直角槽(Right Angle Slot)。

所述PCIE Slot根据实际应用需求,可在PCB板上的不同位置布局选择支持内置插卡或后I/O插卡,也支持设计成横插卡,也可支持设计成竖直插卡等。Slotl~4可支持PCIE标准卡x16/x8/x4/x2/x1,通过插入不同转接板,可支持1个PCIE x16或2个x8 Slot或1个x8+2个x4 PCIE Slot,Slot0可支持PCIE标准卡x8/x4/x2/x1,通过插入不同转接板可支持2个x4 PCIE Slot。

在该实施例中,主板在出厂时预留中央处理器安装位置,具体的安装位置处可以设有所述处理器插座,或者,可以在所述安装位置设有处理器焊接点,以便于OEM、服务器等厂商或用户自行选配。

继续参看图1所示,在一些实施例中,所述OCP连接器(Connector)具有第一接口、第二接口及第三接口,一般具有该三种接口的OCP连接器俗称Connector A+B+C,其中的第一接口对应A接口,第二接口对应B接口,第三接口对应C接口。所述处理器插座上具有与处理器第六组信号通路对应的第六输入/输出接口,所述第六组信号通路包括16路,所述第六输入/输出接口传输的一8路P1[15:8]与第一接口连接,所述第一接口用于配置成PCIE协议,传输的另一8路P1[7:0]与第一信号切换器(图中未示意)连接,所述第一信号切换器输出端分别连接有所述第二接口及M.2连接器,所述第二接口用于配置成SATA协议或用于与第一接口一起配置成16路PCIE协议。

所述处理器插座上具有与处理器第七组信号通路对应的第七输入/输出接口,所述第七组信号通路至少包括4路,所述第七输入/输出接口传输的其中4路P0[7:4]与第三接口连接,所述第三接口用于配置成KR协议。

继续参看图2所示,在另一实施例中,所述SATA连接器包括:MiniSAS HD连接器,所述MiniSAS HD连接器设有4组或6组,每组设有4个SATA接口,共提供16组或24组SATA接口;其中,至少有两组MiniSAS HD连接器通过所述第一信号切换器连接所述第六输入/输出接口;即第一信号切换器根据需要对CPU第六组信号通路中P1[7:0]所连接的连接器进行切换,以使SATA信号选择连接到MiniSAS HD 6~7两组或OCP连接器第二接口。

Mini-SAS HD(High density)连接器是新一代SAS接口,满足6Gb/s至12Gb/s和14Gb/s的通道带宽要求,符合或者超过SAS 2.1规范与SAS 3.0建议执行规范。Mini-SAS HD产品比现有Mini-SAS 2.0产品的端口密度更高。

在MiniSAS HD 6~7与OCP B连接器进行选择连接时,当P1[7:0]连接SATA设备时,即支持24组SATA接口,当P1[7:0]连接OCP连接器第二接口时,支持16组SATA信号。

具体地,MiniSAS HD连接器与OCP连接器之间的信号切换,可以通过信号切换器,例如多路复用器(MUX)进行智能切换;也可以采用P1[7:0]选择在主板上进行零件共用(Co-layout)的方式进行手动选择,这样可以节省成本及PCB板的布线空间。

7针SATA接口;所述7针SATA接口设有2组,分别与所述第七输入/输出接口连接,所述第七组信号通路至少包括6路,其中4路P0[7:4]与前述的OCP连接器的第三接口连接之外,另外2路P0[3]和P0[2]分别与2组连接7针SATA接口分别一一对应连接。

及SATA接口的光盘连接器,所述SATA接口的光盘连接器支持连接光盘驱动器(ODD)或固态硬盘(DOM)。其中,固态硬盘为SATA接口的DOM。

参看图4所示,在一些实施例中,所述处理器插座上具有与处理器第七组信号通路对应的第七输入/输出接口,所述第七组信号通路至少包括5路,所述第七输入/输出接口传输的其中5路通过第二信号切换器与所述M.2连接器连接,其中4路P0[11:8]用于配置成PCIE信号,可支持PCIE M.2盘;1路用于配置成SATA信号,所述第二信号切换器用于在4路PCIE信号中的P0[8]与1路P0[1]SATA信号之间切换。具体为:当SEL引脚为高电平时,第二信号切换器的A脚与C脚连通,信号切换为LaneP0[8];当SEL引脚为低电平时,第二信号切换器的A脚与B脚连通,信号切换为Lane P0[1]。

继续参看图4所示,具体地,所述第二信号切换器为MUX芯片,所述1路P0[1]SATA信号连接M.2连接器的Lane0端口,第二信号切换器的SEL PIN(电平信号脚)设置有上拉电阻,当插入PCIE M.2时,由于M.2上第69pin为NC(表示接线端子悬空,其在数字逻辑电路中表示:引脚不接任何信号,既不与高电平相接,也不与低电平相接),在上拉电阻的作用下,SEL为高电平,PCIE信号通过MUX连接到M.2连接器,当插入SATA M.2时,由于M.2硬盘上的第69pin接地,SEL会被M.2硬盘上的第69pin拉低,SATA信号通过MUX连接到M.2连接器,从而实现了PCIE和SATA M.2的自动识别连接。

除了需要进行高速通信的场合外,主板还需要适应低速率通信的场合,例如在调试场景中,需要主板具备一些低速率通信的接口,以便于进行调试及远程监控管理。因此,参看图4所示,在一些实施例中,所述印制电路板上还设有基板管理控制器及第二速率接口组件,所述第二速率接口组件的信号传输速率小于所述第一速率接口组件的传输速率,所述基板管理控制器一端与所述处理器安装座通过印制线路电连接,另一端与所述第二速率接口组件电连接,用于使主板支持远程任务管理。

其中,远程任务管理包括:BIOS调试、烧录、更新等,以及主板的开机、关机,CPU散热策略调整等任务。

所述第二速率接口组件包括UART(Universal Asynchronous Receiver/Transmitter)接口、JTAG(Joint Test Action Group)接口、SPI(Serial PeripheralInterface)接口、LPC(Low pin count)接口、I2C((Inter-Integrated Circuit)接口及APML(Advanced Platform Management Link)接口。

其中,参看图5所示,展示有UART接口功能电路拓扑,其中,在处理器插座中插入CPU之后,CPU与基板管理控制器(BMC,Baseboard Management Controller;也称为底板管理控制器)通过UART接口连接,主板上设有第一插针连接器(Header)1及第二插针连接器Header 2,CPU与BMC之间的节点通过线缆与所述第一插针连接器Header1连接,所述第二插针连接器Header 2通过RS232接口连接于BMC上。该接口功能电路可实现本地(Local)UART调试方式。

在另一些实施方式中,所述BMC上设有网口,通过该网口与基板管理控制器BMC可实现SOL(Serial over LAN)调试功能,即利用所述网口进行远程连接登录查看调试信息,具体为:CPU的串口信息发送给BMC后,通过BMC固件实现SOL功能,在登陆到BMC web网页,打开SOL界面,就可以看到CPU的串口信息,从而实现了远程调试的功能。

参看图6至图8所示,展示有JTAG接口功能电路拓扑,可实现本地JTAG调试或通过BMC进行远程JTAG调试,JTAG接口一般有10pin的、14pin的和20pin三种。

另外,BMC还可以烧录复杂可编程逻辑器件(Complex Programmable LogicDevice,简称CPLD)程序,为便于描述,下文统称CPLD程序。其中HDT(Hygon Debug Tool)即本地JTAG调试器。参看图6所示,其实现原理是:BMC的TCK(Test Clock Input)/TMS(TestMode Selection Input)信号经过一个带选择开关的切换芯片Switch,可以分成两路,一路连接到CPLD和第三插针连接器Header3;此处的Header3是CPLD的JTAG烧录Header,JTAG烧录header3具有VCC(电源)/TDO(Test Data Output)/TDI(Test Data Input)/TMS(TestMode Selection Input)/GND(电源地)/TCK信号),另一路通过带控制端OE(OutputEnable,一般是输出使能信号)的传输门后连接到CPU,HDT的TCK/TMS通过带控制端的传输门后连接到CPU。HDT和BMC都可以作为调试器对CPU进行调试,因此这两个调试器的使能控制端HDT_OE和BMC_OE是反向的,以保证同时只有一个开启,即要么HDT,要么BMC的TCK/TMS跟CPU相连,其中OE由BMC控制。参看图7所示,HDT和BMC的TRST(Test Reset Input)/DBREQ信号分别通过带控制端OE的传输门后跟CPU互联,两个传输门的控制端HDT_OE和BMC_OE信号间加了一个反向器,保证两个传输门不会同时打开,OE由BMC控制。其中,图8示意出了HDT和BMC的TDI和TDO的切换控制原理,其原理同上述TCK/TMS信号切换原理,可相互参看,就不再赘述。

参看图9所示,展示有SPI接口功能电路拓扑,CPU和BMC的SPI0(DI/DO/HOLD_L/WP_L/CS0)接口通过MUX芯片进行切换,MUX通路默认选择CPU连接,主板上电启动后,CPU从BIOSROM中读取固件信息以初始化主板,当主板CPU不需要启动BIOS的时候,BMC可通过GPIO(general-purpose input/output ports,中文意思是通用i/o端口)控制MUX切换SPI通路到BMC连接,实现远程对BIOS ROM进行烧录。当BMC烧录完成后控制GPIO切换BIOS ROM连接到CPU。主板重启后,CPU从BIOS ROM启动主板,从而实现了BMC远程烧录BIOS的功能。同时CPU的SPI1(DI/DO/HOLD_L/WP_L/CS1)接口连接TCM/TPM模块,从而使主板支持安全模块功能。

参看图10所示,展示有BMC的功能电路拓扑,主板采用ASPEED AST2500 BMC芯片作为管理系统,对主板系统进行开机、关机和重启控制,固件烧录,以及系统错误、告警、温度、电压等进行监控,BMC可通过网络接受外部控制命令。AST2500跟CPU连接,AST2500外围还连接有其它控制电路,其它控制电路包括风扇、内存卡、按键、UART接口、网卡芯片等,如图10所示。

其中,如图11所示,通过BMC网络控制CPU的PWR BTN和RST BTN信号,以对主机板进行开机、关机以及Reset控制。

可以理解的是,CPU工作时会发热,为了实现对CPU温度的监视及控制,在主板上还设有管温度控制系统交互接口。如图12所示,其具体工作原理为:CPU将自身与温度相关的信号,例如,CPU的Thermaltrip(Thermaltrip为CPU的一个管脚,当芯片温度达到设定值的时候,芯片会拉低这个管脚,外部电路监测到这个管脚拉低后,就切断主板上的供电达到保护)和Tdie(内核温度)等温度信号及AMPL接口传送出去的Tmon(Tdie是在芯片内部的一个感温二极管,用来感知芯片内部温度)温度分别连接到第四插针连接器Header4、第五插针连接器Header5及BMC上,测试系统的温度控制模块或BMC对其进行感知,从而控制CPU的散热模块按照不同策略进行调整。

根据上述描述可知,本发明实施例提供的主机板,采用CPLD对电源调整器(VR)进行上电和下电控制,通过逻辑代码可灵活调整电源调整器VR(Voltage Regulator)及输入给CPU的信号的上电和下电时序,且支持远程BMC管理系统以对主板进行远程控制、调试和监测,可以提高主机板整体系统的可管理性。

本发明适用于主机板、计算机、工控机及服务器等电子器件或设备的开发、OEM及芯片测试场景中。

另外,本发明实施例还提供一种服务器,包括机箱,在所述机箱内设有前述任一实施例所述的主机板,所述主机板上的中央处理器插座中安装有处理器,所述处理器与所述信号切换器的输入端电连接。

其中,所述处理器为中央处理器。具体地,所处理器为海光处理器,型号为7100和7200,支持多通道内存。

本实施例的服务器,其主机板由于便于实现高速信号的传输,性能可以在一定程度上得到优化。

需要说明的是,在本文中,术语“上”、“下”等指示的方位或位置关系的用语,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是直接相连,也可以通过中间媒介间接相连。诸如,第一和第二等之类的关系术语仅仅用来将一实体或者操作与另一实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一......”限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。对于本领域的普通技术人员而言,可以通过具体情况理解。

以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以权利要求的保护范围为准。

- 主机板及采用所述主机板的服务器

- 主机板及采用所述主机板的服务器