扫描链控制电路

文献发布时间:2023-06-19 09:51:02

技术领域

本发明涉及一种集成电路芯片测试电路,特别涉及一种集成电路芯片的扫描链测试电路的控制电路。

背景技术

随着大规模集成电路芯片技术的不断发展,芯片集成度越来越高;随之而来,芯片测试难度越来越大。扫描链测试电路的可靠性高、测试准确等优点,在集成电路芯片测试中得到广泛的应用,已经成为现代芯片设计中必不可少的一个组件。但是,扫描链测试电路测试管脚多,现有测试方法测试时需要外接引线,导致测试难度大。尤其是芯片封装在印刷电路板上时,过多的测试管脚不易完全外露或者芯片封装造成测试管脚接触不良等问题,都增大了测试难度。

发明内容

本发明提出一种扫描链控制电路,特别是一种整合扫描链测试电路管脚的扫描链控制电路。在芯片封装后不外露测试管脚的情况下,也能够实现扫描链测试电路的数据输入/输出控制,提高测试灵活性。

在优选的实施例中,本发明提供一种扫描链控制电路,包括:一寄存器控制器;一时钟控制器耦接至上述寄存器控制器,接收一使能时钟信号,并输出一移位时钟信号;一模式控制器耦接至上述寄存器控制器,接收上述使能时钟信号,并输出一模式测试时钟信号及一模式扫描使能时钟信号;一数据选择器耦接至一扫描链测试电路及上述寄存器控制器;当上述数据选择器接收的上述使能时钟信号为第一电平时,上述数据选择器选择一寄存器输入数据输入至上述扫描链测试电路;当上述数据选择器接收的上述使能时钟信号为第二电平时,上述数据选择器选择一管脚输入数据输入至上述扫描链测试电路。

在一些实施例中,上述寄存器控制器输出上述使能时钟信号及上述寄存器输入数据。

在一些实施例中,上述数据选择器的一第一输入端耦接至上述扫描链测试电路,一第二输入端及一第三输入端耦接至上述寄存器控制器。

在一些实施例中,上述数据选择器的第一输入端接收上述扫描链测试电路传送的上述管脚输入数据。

在一些实施例中,上述数据选择器的第二输入端接收上述寄存器控制器传送的上述寄存器输入数据。

在一些实施例中,上述数据选择器的第三输入端接收上述寄存器控制器传送的上述使能时钟信号。

在一些实施例中,上述时钟控制器的一第一数据选择器耦接至上述寄存器控制器及上述扫描链测试电路;当上述第一数据选择器接收的上述使能时钟信号为第一电平时,上述第一数据选择器选择一寄存器移位时钟输出;当上述第一数据选择器接收的上述使能时钟信号为第二电平时,上述第一数据选择器选择一管脚移位时钟输出。

在一些实施例中,上述时钟控制器的一第一数据选择器的一第一输入端耦接至上述扫描链测试电路,一第二输入端及一第三输入端耦接至上述寄存器控制器。

在一些实施例中,上述第一数据选择器的第一输入端接收上述扫描链测试电路管脚传送的上述管脚移位时钟。

在一些实施例中,上述第一数据选择器的第二输入端接收上述寄存器控制器传送的上述寄存器移位时钟。

在一些实施例中,上述第一数据选择器的第三输入端接收上述寄存器控制器传送的上述使能时钟信号。

在一些实施例中,上述时钟控制器还包含一第二数据选择器,当上述第二数据选择器的第三输入端接收来自上述模式控制器的模式扫描使能时钟信号为第一电平时,上述第二数据选择器选择第一输入端来自一时钟振荡器的一功能时钟输出;当上述第二数据选择器的第三输入端接收来自上述模式控制器的模式扫描使能时钟信号为第二电平时,上述第二数据选择器选择第二输入端来自上述第一数据选择器的上述移位时钟输出。

在一些实施例中,上述模式控制器还包含一第三数据选择器及一第四数据选择器。

在一些实施例中,上述扫描链测试电路为包含n+1条扫描链的测试电路,其中n为大于等于0的整数。

在一些实施例中,上述寄存器输入数据及上述管脚输入数据为n+1字节的测试数据,数据位数与扫描链测试电路对应。

附图说明

图1是根据本发明所述的扫描链测试电路的基本示意图。

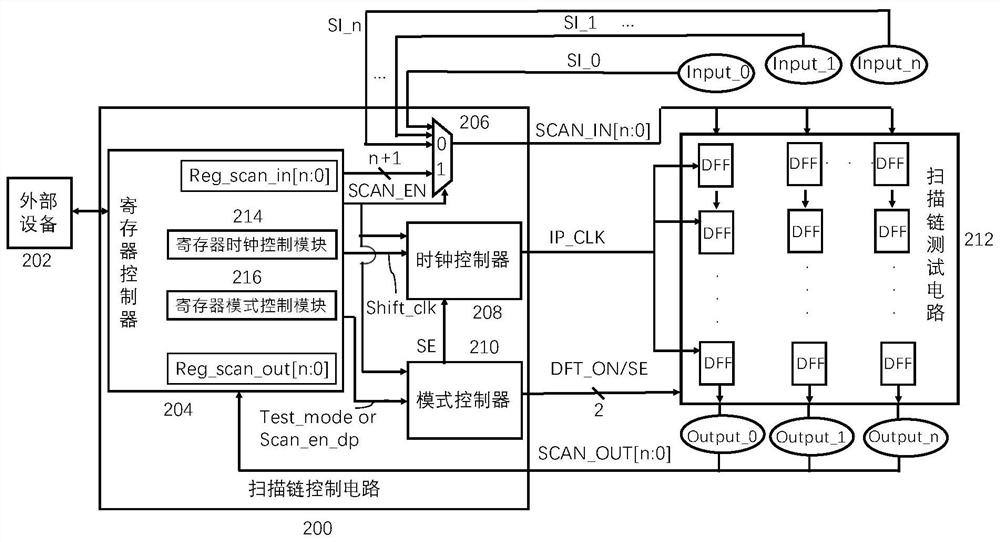

图2是根据本发明一实施例所述的扫描链控制电路的示意图。

图3是根据本发明一实施例所述的数据选择器的示意图。

图4是根据本发明一实施例所述的时钟控制器的示意图。

图5是根据本发明一实施例所述的模式控制器的示意图。

图6是根据本发明一实施例所述的扫描链控制电路时钟信号的示意图。

图7是根据本发明一实施例所述的扫描链控制电路的流程图。

图8是根据本发明一实施例所述的扫描链测试电路封装在PCB板上的示意图。

其中,附图中符号的简单说明如下:

100~扫描链测试电路;200~扫描链控制电路;202~外部设备;204~寄存器控制器;206~数据选择器;208~时钟控制器;210~模式控制器;212、212-1、212-2、212-3、212-4~扫描链测试电路;214~寄存器时钟控制模块;216~寄存器模式控制模块;400、402、406、408、500、502~D触发器;404、410~门控时钟电路;412~时钟振荡器(Phase LockedLoop,PLL);414~第一数据选择器;416~第二数据选择器;504~第三数据选择器;506~第四数据选择器;Reg_scan_in[n:0]~寄存器输入数据;Reg_scan_out[n:0]~寄存器输出数据;SCAN_IN[n:0]~输入数据;SCAN_EN~使能时钟信号;IP_CLK~移位时钟;DFT_ON~模式测试时钟信号;SE~模式扫描使能时钟信号;SCAN_OUT[n:0]~输出数据;IC1、IC2~待测试的集成设计电路;DFF~D型触发器;Input_0、Input_1…Input_n~输入管脚;Output_0、Output_1…Output_n~输出管脚;SI_0、SI_1…SI_n~扫描链测试电路输入数据;TCK~测试时钟信号;Shift_clk~寄存器移位时钟信号;Ext_clk~管脚移位时钟;PLL~时钟振荡器;ICG~门控时钟电路;Func_clk~功能时钟信号;Scan_mode_dp~模式测试备份时钟信号;Scan_en_dp~模式扫描使能备份时钟信号;SE_i~原始控制扫描链测试电路的模式扫描使能时钟信号;DFT_ON_i~原始控制扫描链测试电路的测试模式时钟信号;Test_mode~测试模式信号;T1~第一时段;T2~第二时段;T3~第三时段;T4~第四时段;T5~第五时段;S702、S704、S706、S708、S710~流程步骤。

具体实施方式

为让本发明的目的、特征和优点能更明显易懂,下文特举出本发明的具体实施例,并配合附图,作详细说明如下。

在通篇说明书及权利要求书当中所提及的“包含”及“包括”一词为开放式的用语,故应解释成“包含但不仅限定于”。“耦接”一词在本说明书中包含任何直接及间接的电性连接手段。因此,若文中描述一第一装置耦接至一第二装置,则代表该第一装置可直接电性连接至该第二装置,或经由其它装置或连接手段而间接地电性连接至该第二装置。

在通篇说明书及权利要求书当中使用了某些词汇来指称特定的组件及构件。本领域技术人员应可理解,硬件制造商可能会用不同的名词来称呼同一个组件及构件。本说明书及权利要求书并不以名称的差异来作为区分组件及构件的方式,而是以组件及构件在功能上的差异来作为区分的准则。

图1是根据本发明所述的扫描链测试电路的基本示意图。在芯片设计时,芯片测试电路可包含如图1所示的多条扫描链测试电路(如图1所示,可为输入管脚为SI_0、SI_1、SI_2、SI_3…SI_N和输出管脚为SO_0、SO_1、SO_2、SO_3…SO_N的多条扫描链测试电路),每条扫描链测试电路通过耦接各自的输入/输出管脚(PAD管脚)并在移位时钟(IP_CLK)的作用下汇入待测试数据(SCAN_IN[n:0])或导出测试数据(SCAN_OUT[n:0])供设计人员分析芯片设计。

但是,当芯片被封装在PCB板上时,上述芯片设计的输入/输出管脚(PAD管脚)因为封装的原因,可能会由于封装覆盖导致管脚不外露或者由于封装造成管脚接触不良。最终,将会造成测试不便或测试数据不准确,不能很好的分析芯片设计,增加测试成本和难度。当芯片被封装在PCB板上时,具体来说,会出现以下状况导致测试不准确。首先,会造成SI_1的扫描链测试电路的输入管脚由于封装而不外露(如图1所示,用在PAD管脚上画“X”表示管脚不外露),导致测试人员无法从电路板上外接引线进行后续测试。其次,还有可能导致输出管脚不外露(如图1所示,SI_2的扫描链测试电路的输出管脚不外露),同样也会导致测试人员无法从电路板上外接引线进行后续测试。再次,就算是管脚外露的情况下,也可能会造成管脚接触不良等问题(如图1所示,用在PAD管脚上画“△”表示管脚接触不良),导致测试不准确,也不能很好的分析芯片设计。更有甚者,会同时出现以上三种状况,导致测试数据不准确,增加测试成本和难度。

因此,图2是根据本发明一实施例所述的扫描链控制电路的示意图。扫描链控制电路200可应用于控制集成电路芯片的扫描链测试电路212,实现扫描链测试电路的数据输入/输出控制,提高测试灵活性。如图2所示,上述扫描链控制电路200包括:一寄存器控制器204、一数据选择器206、一时钟控制器208及一模式控制器210;上述寄存器控制器204还包含一寄存器时钟控制模块214及一寄存器模式控制模块216。上述时钟控制器208耦接至上述寄存器控制器204及上述模式控制器210,接收由上述寄存器控制器204输出的一使能时钟信号(SCAN_EN)及一寄存器移位时钟信号(Shift_clk),接收由上述模式控制器210输出的一模式扫描使能时钟信号(SE),并输出一移位时钟信号(IP_CLK);上述模式控制器210耦接至上述寄存器控制器204,接收上述使能时钟信号(SCAN_EN),并输出一模式测试时钟信号(DFT_ON)及上述模式扫描使能时钟信号(SE);一数据选择器206耦接至上述扫描链测试电路212及上述寄存器控制器204;当上述数据选择器206接收的上述使能时钟信号为第一电平时,上述数据选择器206选择一寄存器输入数据(Reg_scan_in[n:0])作为输入数据(SCAN_IN[n:0])输入至上述扫描链测试电路212;当上述数据选择器206接收的上述使能时钟信号为第二电平时,上述数据选择器206选择一管脚输入数据(SI_0、SI_1…SI_n)作为输入数据(SCAN_IN[n:0])输入至上述扫描链测试电路212。此处需要说明的是,上述模式控制器210输出的上述模式测试时钟信号(DFT_ON)及模式扫描使能时钟信号(SE)为控制上述输入数据(SCAN_IN[n:0])经过扫描链测试电路212测试之后的输出数据的输出信号。在一些实施例中,如图6部分所示,上述测试模式时钟信号(DFT_ON)由上述的模式控制器210在接收测试时钟信号TCK信号(由上述外部设备202在测试状态下所产生)3个时钟信号之后拉升为高电平信号,以及模式扫描使能时钟信号(SE)由上述的模式控制器210在接收TCK信号4个时钟信号之后拉升为高电平信号,或者说上述测试模式时钟信号(DFT_ON)及模式扫描使能时钟信号(SE)是由上述的模式控制器210在TCK信号若干时钟周期之后相应拉升为高电平信号且上述测试模式时钟信号(DFT_ON)先于模式扫描使能时钟信号(SE)拉升为高电平信号。此处应说明的是,上述测试模式时钟信号(DFT_ON)先于模式扫描使能时钟信号(SE)1个时钟周期拉升为高电平信号,本领域技术人员可根据实际需要自行配置,本发明并不限制于此。

上述测试模式时钟信号(DFT_ON)及一模式扫描使能时钟信号(SE)拉高为高电平时表示此时经过扫描链测试电路212测试之后输出数据(图2所示的SCAN_OUT[n:0])可输出至图2所示的扫描链控制电路200并最终输出至外部设备供设计人员分析。需要特别说明的是,上述测试模式时钟信号(DFT_ON)及一模式扫描使能时钟信号(SE)用于控制上述测试输出数据(图2所示的SCAN_OUT[n:0])的输出。

在一些实施例中,一原始控制扫描链测试电路的模式扫描使能时钟信号(SE_i)及一模式测试时钟信号(DFT_i)与测试模式时钟信号(DFT_ON)及模式扫描使能时钟信号(SE)的拉升原理类似。上述原始控制扫描链测试电路的模式扫描使能时钟信号(SE_i)及模式测试时钟信号(DFT_i)可以是使用内部电路模块(图5未绘示)在接收TCK信号若干个时钟信号之后拉升为高电平信号且上述模式测试时钟信号(DFT_i)先于原始控制扫描链测试电路的模式扫描使能时钟信号(SE_i)拉升为高电平信号。此处应说明的是,上述模式测试时钟信号(DFT_i)先于原始控制扫描链测试电路的模式扫描使能时钟信号(SE_i)1个时钟周期拉升为高电平信号。本领域技术人员可根据产品需求,自行配置原始的扫描链测试电路的相关模式信号控制模块,本发明并不限制于此。关于此部分内容描述,请参考图5部分所述,在此不再赘述。

如图2所示,上述扫描链测试电路212为一集成电路芯片测试电路,包含n+1(n≥0且为整数)条扫描链,其测试数据经由输入管脚(Input Pad)输入,输出管脚输出。上述单条扫描链测试电路可包含:一输入管脚(例如:Input_0、Input_1、…、Input_n)、多个串联的触发器(例如:可为D类型触发器(D type flip-flop,DFF))、一输出管脚(例如:Output_0、Output_1、…、Output_n)或者可为任何其他类型的集成电路芯片扫描链测试电路,在此并不做任何限制。

需特别说明的是,如图2所示的扫描链测试电路212的输入管脚(例如:Input_0、Input_1、…、Input_n)可分别耦接至上述数据选择器206的多个输入端,并经由数据选择器206控制传送测试数据至扫描链测试电路212(此部分技术细节请参考图3部分所述,在此不再赘述)。因此,当芯片封装至印刷电路板上时,即使扫描链测试电路212的输入管脚(例如:Input_0、Input_1、…、Input_n)由于被覆盖或者焊接等原因造成接触不良时,依然可以经由测试电路板上的布线将相关信号传送至上述扫描链控制电路200,因而可使用上述扫描链控制电路200传输测试数据至扫描链测试电路实现测试需求,避免了测试的不利因素,极大的提高了测试效率。

另外需要说明的是,上述数据选择器206还可接收上述寄存器控制器204传送的寄存器输入数据(Reg_scan_in[n:0]),并在控制信号端的作用下,将寄存器控制器204传送的寄存器输入数据(Reg_scan_in[n:0])输入至扫描链测试电路212(此部分内容请参考图3部分所述,在此不再赘述)。或者说,当芯片封装至印刷电路板上扫描链测试管脚被覆盖或者接触不良时,依然可以使用寄存器输入数据(Reg_scan_in[n:0])将测试数据输入至扫描链测试电路212进行测试。更有甚者,上述n+1bits的寄存器输入数据(Reg_scan_in[n:0])可采用高低电平信号实现寄存器输入数据(Reg_scan_in[n:0])与扫描链测试电路之间的对应(此部分内容请参考图3部分所述,在此不再赘述),使得测试更灵活。

还有一点需要说明的是,如图2所示的扫描链测试电路212的输入管脚(例如:Input_0、Input_1、…、Input_n)也可连接至相应的扫描链测试电路。本领域技术人员也可直接在扫描链测试电路212的输入管脚(例如:Input_0、Input_1、…、Input_n)暴露的情况下,人为的外接引线实现测试的需要。为使绘图更简便,图2未绘示全部连接关系,但本技术相关技术人员可根据实际需要自行配置,本发明并不限制于此。

以上实施例所述的测试数据的输入方式,在满足原有测试需求的基础上,极大的消除了测试的不确定因素,提高了测试的准确性和灵活性,降低了测试人员的测试难度,提高了测试效率,具有一定的技术效果。

上述数据选择器206将测试数据(SCAN_IN[n:0])输入至上述扫描链测试电路212;在上述移位时钟信号(IP_CLK)、模式测试时钟信号(DFT_ON)及模式扫描使能时钟信号(SE)的作用下,上述测试数据(SCAN_IN[n:0])在上述扫描链测试电路中移位进行扫描,并经由输出管脚(Output Pad)输出测试数据(SCAN_OUT[n:0])至上述寄存器控制器204,上述寄存器控制器204记录测试数据并整合(Reg_scan_out[n:0])输出至外部设备202。关于移位时钟信号(IP_CLK)、模式测试时钟信号(DFT_ON)及模式扫描使能时钟信号(SE)的更多细节描述,将于图4、图5部分详细说明,在此不再赘述。

关于输出测试数据(SCAN_OUT[n:0]),需要说明的是:上述移位时钟信号(IP_CLK)控制上述输入测试数据(SCAN_IN[n:0])在上述扫描链测试电路212的多个串联的触发器(例如:可为D类型触发器(D type flip-flop,DFF))中移位进行扫描。上述模式测试时钟信号(DFT_ON)及模式扫描使能时钟信号(SE)控制上述输入测试数据(SCAN_IN[n:0])经过扫描链测试电路212测试之后输出。关于模式测试时钟信号(DFT_ON)及模式扫描使能时钟信号(SE)控制输入测试数据(SCAN_IN[n:0])经过扫描链测试电路212测试之后输出的相关技术细节,请参考图5说明部分,在此不再赘述。

关于输出测试数据(SCAN_OUT[n:0])还有一点需要说明的是:如图2所示,上述扫描链测试电路的输出管脚(例如:Output_0、Output_1、…、Output_n)可直接连接至寄存器控制器204并整合数据输出供设计人员分析。在一些实施例中,设计人员也可直接在输出管脚(例如:Output_0、Output_1、…、Output_n)上外接引线并连接相关测试设备(如:逻辑分析仪等可视化分析设备)输出测试数据,本领域技术人员可根据实际需要自行配置,本发明并不限制于此。

上述外部设备202可为一可视化的测试分析设备,例如:可为一逻辑分析仪、一示波器或其他类型的测试分析设备,在此并不做限制。

上述寄存器控制器204还可包含指令寄存器和/或数据寄存器,本领域技术人员可根据实际使用情况配置多个D触发器和/或多个门电路结构以符合实际测试电路配置需要,但本发明并不限于此。

在一些实施例中,上述第一电平为一高电平;上述第二电平为一低电平。此外,图2中的第一电平与第二电平虽分别以逻辑“1”与逻辑“0”来表示,但它们可以是晶体管的电源电平(例如电平为“VDD”)与接地端电位(例如电平为“0”)或是任何可以让数据选择器106辨识要从第一输入端或第二输入端选择测试数据的电平,本发明对此不进行限制。

在一些实施例中,上述扫描链控制电路可应用于联合测试工作组(Joint TestAction Group,JTAG)调试接口和/或串行线调试(Serial Wire Debug,SWD)接口,本发明对此不进行限制。

图3是根据本发明一实施例所述的数据选择器的示意图。上述数据选择器206可为多个数据选择器组合而成。如图3所示,上述数据选择器206为n+1(n≥0且为整数)个数据选择器组合而成,上述数据选择器206的一第一输入端耦接至上述扫描链测试电路212,并接收来自上述扫描链测试电路212传送的n+1(n≥0且为整数)比特(bit)的上述管脚输入数据(SI_0、SI_1…SI_n);一第二输入端及一第三输入端耦接至上述寄存器控制器204,并接收来自上述寄存器控制器204传送的n+1(n≥0且为整数)比特(bit)的上述寄存器输入数据(Reg_scan_in[n:0])及上述使能时钟信号(SCAN_EN)。上述第三输入端为一控制信号端,本领域技术人员可根据实际配置,任意设定上述控制信号端(上述第三输入端)信号以使数据选择器206辨识要从第一输入端或第二输入端选择测试数据,本发明并不限制于此。

当上述数据选择器206接收的来自上述寄存器控制器204传送的上述使能时钟信号为第一电平时(例如:为高电平“1”),上述数据选择器206选择上述n+1比特的寄存器输入数据(Reg_scan_in[n:0])作为输入数据(SCAN_IN[n:0])输入至上述扫描链测试电路212;当上述数据选择器206接收的来自上述寄存器控制器204传送的上述使能时钟信号为第二电平时(例如:为低电平“0”),上述数据选择器206选择上述n+1比特的管脚输入数据(SI_0、SI_1…SI_n)作为输入数据(SCAN_IN[n:0])输入至上述扫描链测试电路212。

需要说明的是,上述n+1条扫描链测试电路包含n+1个输入管脚及n+1个输出管脚。如图2所示,Input_0为第0条扫描链测试电路的输入管脚,Output_0为第0条扫描链测试电路的输出管脚;Input_1为第1条扫描链测试电路的输入管脚,Output_1为第1条扫描链测试电路的输出管脚…;依此类推,Input_n为第n条扫描链测试电路的输入管脚,Output_n为第n条扫描链测试电路的输出管脚。上述n+1条扫描链测试电路包含的n+1个输入管脚的输入数据可经由上述数据选择器206统一配置,上述n+1条扫描链测试电路包含的n+1个输出管脚的输出数据可经由上述寄存器控制器204统一输出至外部设备202并进行分析;实现扫描链测试电路212的数据输入/输出控制,提高测试灵活性。

需要特别说明的是,上述寄存器输入数据(Reg_scan_in[n:0])、上述管脚输入数据(SI_0、SI_1…SI_n)、上述测试输入数据(SCAN_IN[n:0])、上述测试输出数据(SCAN_OUT[n:0])及上述寄存器输出数据(Reg_scan_out[n:0])为n+1比特(bits)的测试数据,与上述n+1条扫描链测试电路对应。上述数据选择器206为n+1个数据选择器组合而成,与上述n+1条扫描链测试电路对应。

上述n+1比特(bits)的测试数据(SCAN_IN[n:0])可选择n+1条扫描链测试电路的单条扫描链测试电路测试。换句话说,上述n+1比特(bits)的测试数据(SCAN_IN[n:0])可全部测试上述n+1条扫描链测试电路,也可只测试上述n+1条扫描链测试电路中的某一条和/或某几条扫描链测试电路。本领域技术人员可根据实际测试需要自行配置,本发明并不限制于此。

举例来说,假设上述扫描链测试电路212为具有4条扫描链的测试电路(包含第0条、第1条、第2条、第3条),且需测试上述第1条和上述第3条扫描链测试电路。当上述数据选择器206的第三输入端接收上述寄存器控制器204传送的上述使能时钟信号为第一电平时(例如:为高电平“1”),上述数据选择器206选择第二输入端测试数据(例如:寄存器输入数据(Reg_scan_in[0101]))作为测试输入数据(SCAN_IN[0101])输入至上述扫描链测试电路212。当上述数据选择器206的第三输入端接收上述寄存器控制器204传送的上述使能时钟信号为第二电平时(例如:为低电平“0”),上述数据选择器206选择第一输入端测试数据(例如:管脚输入数据(SI_0、SI_1…SI_n))作为测试输入数据(SCAN_IN[0101])输入至上述扫描链测试电路212。更具体的,上述测试输入数据的高电平测试数据“1”输入至第1条和第3条扫描链测试电路,而上述测试输入数据的低电平测试数据“0”输入至第0条和第2条扫描链测试电路。在此实施例中,更能体现当芯片封装至印刷电路板上时,原有输入管脚被覆盖后依然能使用寄存器输入数据(Reg_scan_in[0101]))作为测试输入数据(SCAN_IN[0101])输入至上述扫描链测试电路212的实际效果,极大的避免了测试过程中的一些不利因素,提高测试效率。

当上述数据选择器206的第三输入端接收上述寄存器控制器204传送的上述使能时钟信号为第二电平时(例如:为低电平“0”),上述数据选择器206选择第一输入端测试数据(例如:管脚输入数据(SI_0、SI_1、SI_2和SI_3))作为测试数据(SCAN_IN[0101])输入至上述扫描链测试电路212。更具体的,上述测试输入数据的高电平测试数据“1”输入至第1条和第3条扫描链测试电路,而上述测试输入数据的低电平测试数据“0”输入至第0条和第2条扫描链测试电路。

上述测试数据(SCAN_IN[0101])将需测试的上述第1条和上述第3条扫描链测试电路写入高电平(例如:为高电平“1”),将不需测试的上述第0条和上述第2条扫描链测试电路212写入低电平(例如:为低电平“0”)。

上述数据选择器206将测试数据(SCAN_IN[0101])输入至上述扫描链测试电路212;并在上述移位时钟信号(IP_CLK)、模式测试时钟信号(DFT_ON)及模式扫描使能时钟信号(SE)的作用下,上述测试数据(SCAN_IN[0101])在上述扫描链测试电路中移位进行扫描,并经由输出管脚(Output Pad)输出测试数据(SCAN_OUT[0101])至上述寄存器控制器204,上述寄存器控制器204记录测试数据整合(Reg_scan_out[0101])输出至外部设备202并进行分析。

图4是根据本发明一实施例所述的时钟控制器208的示意图。接下来如图4所示,上述时钟控制器208耦接至上述寄存器控制器204,并接收由寄存器时钟控制模块214所传送的上述使能时钟信号(SCAN_EN)及一寄存器移位时钟信号(Shift_clk),并输出上述移位时钟信号(IP_CLK)至上述扫描链测试电路212的多个串联的D类型触发器。在上述移位时钟信号(IP_CLK)的作用下,经由上述数据选择器206输入至上述扫描链测试电路212的所有寄存器测试数据(SCAN_IN[n:0])将整体向下一级寄存器移动,并将最后一级寄存器的值输出至上述寄存器控制器204并整合(Reg_scan_out[n:0])输出至外部设备202。

上述寄存器控制器204耦接至上述外部设备202,上述外部设备202在测试状态下产生一测试时钟信号(Test Clock,TCK)并传送上述测试时钟信号至上述寄存器控制器204,上述寄存器控制器204接收上述测试时钟信号(Test Clock,TCK)并产生上述使能时钟信号(SCAN_EN)。举例来说,当上述外部设备202的测试人员,接通上述外部设备202与上述寄存器控制器204的连接,并在测试状态下使得上述外部设备202产生一连续标准的高低电平测试时钟信号(Test Clock,TCK),并传送上述测试时钟信号至上述寄存器控制器204;上述寄存器控制器204在接收一个和/或多个时钟周期的上述连续标准的高低电平测试时钟信号(Test Clock,TCK)后产生上述使能时钟信号(SCAN_EN)。如图6所示,上述寄存器控制器204在接收测试时钟信号(Test Clock,TCK)两个时钟周期之后产生上述使能时钟信号(SCAN_EN),本领域技术人员可根据实际需求自行配置,在此不做任何限制。

上述寄存器时钟控制模块214及上述时钟控制器208还可配置多个D触发器和/或多个门电路结构,以符合实际需要。例如:上述寄存器时钟控制模块214还包含多个D触发器400、D触发器402及一门控时钟电路(Input Clock Gating,ICG)404。上述时钟控制器208还包含多个D触发器406、D触发器408、一门控时钟电路(Input Clock Gating,ICG)410、一时钟振荡器(Phase Locked Loop,PLL)412、一第一数据选择器414及一第二数据选择器416。上述第一数据选择器414及一第二数据选择器416可为多个数据选择器组合而成的整合数据选择器,上述时钟振荡器(Phase Locked Loop,PLL)412可置于上述时钟控制器208外部,或单独置于某一模块,本领域技术人员可根据实际需求自行配置,在此不做任何限制。

如图4所示,上述第一数据选择器414的第一输入端耦接至上述扫描链测试电路管脚,接收扫描链测试电路管脚传送的上述管脚移位时钟(Ext_clk);第二输入端及第三输入端耦接至上述寄存器控制器204的寄存器时钟控制模块214,接收寄存器时钟控制模块214传送的上述寄存器移位时钟信号(Shift_clk),及接收由上述寄存器控制器204传送的上述使能时钟信号SCAN_SE。具体的,上述第一数据选择器414根据上述第三输入端(控制端)接收上述使能时钟信号SCAN_SE选择上述二者之一(Shift_clk或Ext_clk)传送至上述第二数据选择器416。当上述第一数据选择器414的第三输入端接收上述使能时钟信号SCAN_SE为高电平时,第一数据选择器414选择输出上述寄存器移位时钟信号至第二数据选择器416;反之,则输出管脚移位时钟至第二数据选择器416。在此需要说明的是,上述使能时钟信号SCAN_SE可直接由上述寄存器控制204传送至上述时钟控制器208。在一些实施例中,也可经由上述寄存器控制204中的寄存器时钟控制模块214传送至上述时钟控制器208,本发明并不限制于此。

上述第二数据选择器416的一第一输入端接收来自一时钟振荡器(Phase LockedLoop,PLL)产生的一连续功能时钟信号(Func_clk),一第二输入端接收上述第一数据选择器414传送的一时钟信号(Shift_clk或Ext_clk)及一第三输入端(信号控制端)耦接至图2所述的模式控制器210,接收模式控制器210传送的一模式扫描时钟信号(SE),并最终输出一移位时钟信号(IP_CLK)至图2的扫描链测试电路212。具体的,当上述第二数据选择器416的第三输入端接收图2的模式控制器210传送的一模式扫描时钟信号(SE)为高电平时,选择上述第一数据选择器414传送的时钟信号(Shift_clk或Ext_clk)作为移位时钟(IP_CLK)输出至扫描链测试电路。当上述第二数据选择器416的第三输入端接收图2的模式控制器传送的一模式扫描时钟信号(SE)为低电平时,选择上述第一输入端接收上述时钟振荡器(PhaseLocked Loop,PLL)产生的一连续功能时钟信号(Func_clk)作为移位时钟(IP_CLK)输出至扫描链测试电路。此处需要说明的是,当上述第二数据选择器416选择连续功能时钟信号(Func_clk)作为移位时钟(IP_CLK)输出至扫描链测试电路时,表示此时扫描链测试电路工作在功能模式(Function mode)状态下。当上述第二数据选择器416选择寄存器移位时钟信号(Shift_clk)作为移位时钟(IP_CLK)输出至扫描链测试电路时,表示此时扫描链测试电路工作在扫描模式(Scan mode)状态下。当上述第二数据选择器416选择管脚移位时钟(Ext_clk)作为移位时钟(IP_CLK)输出至扫描链测试电路时,表示此时扫描链测试电路工作在原始测试模式(Original test mode)状态下。换句话说,当模式扫描时钟信号SE为高电平时,表示目前将启动的是测试模式(例如:扫描模式(Scan mode)或原始测试模式(Original test mode)),因此选择第一数据选择器414所输出的测试时钟(Shift_clk或Ext_clk)作为移位时钟(IP_CLK)输出至扫描链测试电路。当模式扫描时钟信号(SE)为低电平时,表示目前将启动的是功能模式(Function mode),因此选择由第一数据选择器414所输出的Func_clk(亦即由上述时钟振荡器412)产生的一连续功能时钟信号Func_clk)作为移位时钟(IP_CLK)输出至扫描链测试电路。更有甚者,当模式扫描时钟信号SE为高电平时,会依据测试模式信号(test_mode)来决定是启动何种测试模式,关于模式状态部分的详细描述,请参考表1相关部分的描述,在此不再赘述。

在上述移位时钟信号(IP_CLK)的作用下,经由上述数据选择器206输入至上述扫描链测试电路212的所有寄存器测试数据(SCAN_IN[n:0])将整体向下一级寄存器移动,并将最后一级寄存器的值输出至上述寄存器控制器204并整合(Reg_scan_out[n:0])输出至外部设备202。

需要特别解释的是,上述时钟控制器208的D类型触发器406前还包含一反相器(未绘示),用于将TCK做反向保证其中各时钟的时序一致性,提高测试性能,本领域技术人员可自行配置,本发明并不限制于此。当上述寄存器时钟控制模块214传送的使能时钟信号(例如:使能时钟信号为“1”)时,上述时钟控制器208还包含的反相器(未绘示)将上述高电平使能时钟信号进行反向(invert)操作,并传送至上述D类型触发器406,即上述高电平使能时钟信号(例如:使能时钟信号为“1”)转换为低电平使能时钟信号(例如:使能时钟信号为“0”)经由D触发器406与408传送至上述时钟控制器208的门控时钟电路410。当上述使能时钟信号为高电平时,锁住上述连续功能时钟信号(Func_clk);反之,输出稳定连续功能时钟信号(Func_clk)。此处需要特别说明的是,上述锁住连续功能时钟信号(Func_clk),可解读为阻断上述连续功能时钟信号(Func_clk)向下传递,或者可解读为将上述连续功能时钟信号(Func_clk)锁在某一高电平或低电平状态而不发生变化,本领域技术可根据实现的电路功能做相应解读,但本发明对此不做任何限制。

图5是根据本发明一实施例所述的模式控制器210的示意图。如图5所示,上述模式控制器210耦接至寄存器模式控制模块216。上述模式控制器210接收上述寄存器模式控制模块216传送的一使能时钟信号SCAN_SE,并输出一测试模式时钟信号(DFT_ON)及一模式扫描使能时钟信号(SE)至扫描链测试电路212。上述寄存器模式控制模块216还可配置多个D触发器,以符合实际需要。例如:上述寄存器模式控制模块216还包含D触发器500和D触发器502。上述模式控制器210的第四数据选择器506的第一输入端接收来自原始控制扫描链测试电路的模式扫描使能时钟信号(SE_i);第二输入端耦接至上述寄存器模式控制模块216,接收一扫描使能备份信号(Scan_en_dp);第三输入端接收来自原始控制扫描链测试电路的测试模式信号(Test_mode)。上述模式控制器210的第三数据选择器504的第一输入端接收来自原始控制扫描链测试电路的模式测试时钟信号(DFT_i);第二输入端耦接至上述寄存器模式控制模块216,接收一扫描模式备份信号(Scan_mode_dp);第三输入端接收来自原始控制扫描链测试电路的测试模式信号(Test_mode)。关于原始控制扫描链测试电路的模式扫描使能时钟信号(SE_i)、测试模式信号(Test_mode)及模式测试时钟信号(DFT_i)需要说明的是:原始控制扫描链测试电路的模式扫描使能时钟信号(SE_i)及模式测试时钟信号(DFT_i)为扫描链测试电路工作在原始测试模式(Original test mode)状态下的模式控制信号,可由原始的扫描链测试电路的相关模块或由JTAG端口提供(图5未绘示)。上述原始控制扫描链测试电路的模式扫描使能时钟信号(SE_i)及模式测试时钟信号(DFT_i)与测试模式时钟信号(DFT_ON)及模式扫描使能时钟信号(SE)的拉升原理类似。上述原始控制扫描链测试电路的模式扫描使能时钟信号(SE_i)及模式测试时钟信号(DFT_i)在接收TCK信号若干个时钟信号之后拉升为高电平信号且上述模式测试时钟信号(DFT_i)先于原始控制扫描链测试电路的模式扫描使能时钟信号(SE_i)拉升为高电平信号。此处应说明的是,上述模式测试时钟信号(DFT_i)先于原始控制扫描链测试电路的模式扫描使能时钟信号(SE_i)1个时钟周期拉升为高电平信号。本领域技术人员可根据产品需求,自行配置原始的扫描链测试电路的相关模式信号控制模块,本发明并不限制于此。测试模式信号(Test_mode)为控制扫描链测试电路工作在何种模式状态下的控制信号,具体功能细节如表1相关部分所述,在此不再赘述。测试模式信号(Test_mode)可由相关内部模块产生,本发明未绘示产生或提供相关测试模式信号(Test_mode)的功能模块(图5未绘示),本领域相关人员可自行配置。

上述测试模式时钟信号(DFT_ON)及一模式扫描使能时钟信号(SE)为控制图2所述的测试输入数据(SCAN_IN[n:0])在经过扫描链测试电路212测试之后输出数据(图2所示的SCAN_OUT[n:0])的信号。在一些实施例中,如图6部分所示,上述测试模式时钟信号(DFT_ON)由上述的模式控制器210在接收TCK信号3个时钟信号之后拉升为高电平信号,以及模式扫描使能时钟信号(SE)由上述的模式控制器210在接收TCK信号4个时钟信号之后拉升为高电平信号,或者说上述测试模式时钟信号(DFT_ON)及模式扫描使能时钟信号(SE)是由上述的模式控制器210在TCK信号若干时钟周期之后相应拉升为高电平信号且上述测试模式时钟信号(DFT_ON)先于模式扫描使能时钟信号(SE)拉升为高电平信号。此处应说明的是,上述测试模式时钟信号(DFT_ON)先于模式扫描使能时钟信号(SE)1个时钟周期拉升为高电平信号,本领域技术人员可根据实际需要自行配置,本发明并不限制于此。

上述测试模式时钟信号(DFT_ON)及一模式扫描使能时钟信号(SE)拉高为高电平时表示此时经过扫描链测试电路测试之后输出数据(图2所示的SCAN_OUT[n:0])可输出至图2所示的扫描链控制电路200并最终输出至外部设备供设计人员分析。

具体的,当上述测试模式信号(Test_mode)为低电平(例如:Test_mode为“0”)时,经由模式控制器210中的上述第四数据选择器506选择输出上述来自原始控制扫描链测试电路的模式扫描使能时钟信号(SE_i)作为模式扫描使能时钟信号(SE)输出,上述第三数据选择器504选择输出上述来自原始控制扫描链测试电路的模式测试时钟信号(DFT_i)作为模式测试时钟信号(DFT_ON)输出。当上述测试模式信号(Test_mode)为高电平(例如:Test_mode为“1”)时,经由模式控制器210中的上述第四数据选择器506选择输出上述来自寄存器模式控制模块216的模式扫描使能备份时钟信号(Scan_en_dp)作为模式扫描使能时钟信号(SE)输出,上述第三数据选择器504选择输出上述来自寄存器模式控制模块216的模式测试备份时钟信号(Scan_mode_dp)作为模式测试时钟信号(DFT_ON)输出。

图6是根据本发明一实施例所述的扫描链控制电路时钟信号的示意图。接下来将结合图2、图4、图5、图6更加详细的说明。如图6中第一时段T1所示,当图2中的上述外部设备202的测试人员接通外部设备202与上述寄存器控制器204的连接,并在测试状态下使得外部设备202产生一连续标准的高低电平测试时钟信号(Test Clock,TCK),并传送上述测试时钟信号至上述寄存器控制器204;上述寄存器控制器204在接收一个和/或多个时钟周期的上述连续标准的高低电平测试时钟信号(Test Clock,TCK)后产生一高电平的使能时钟信号(例如:SCAN_EN为“1”)。此时,图2中的数据选择器206将测试数据(SCAN_IN[n:0])输入至上述扫描链测试电路212。此处应说明的是,当上述数据选择器206的第三输入端(或称为:信号控制端)接收到高电平的使能时钟信号(例如:SCAN_EN为“1”)时其选择寄存器输入数据(Reg_scan_in[n:0])作为输入数据(SCAN_IN[n:0])输入至上述扫描链测试电路212。如图6所示,更需要说明的是,在T1时段之前输入数据(SCAN_IN[n:0])可以为管脚输入数据SI_0、、、SI_n或者使用其他方式传入的数据(如图6所示为不关注)。

接下来,如图6中第二时段T2所示,当图4中上述寄存器时钟控制模块214传送的为高电平使能时钟信号SCAN_EN(例如:使能时钟信号为“1”)时,图4中的上述时钟控制器208还包含的反相器(未绘示)将上述高电平使能时钟信号进行反向(invert)操作,并传送至上述D类型触发器406,即上述高电平使能时钟信号(例如:使能时钟信号为“1”)转换为低电平使能时钟信号(例如:使能时钟信号为“0”)经由D触发器406与408传送至上述时钟控制器208的门控时钟电路410。当上述使能时钟信号为高电平时,锁住上述连续功能时钟信号(Func_clk)。接下来,如图6中第三时段T3所示,当图5中上述测试模式信号(Test_mode)为高电平(例如:Test_mode为“1”)时,上述模式控制器210中的第三数据选择器504选择输出上述来自寄存器模式控制模块216的模式测试备份时钟信号(Scan_mode_dp)作为模式测试时钟信号(DFT_ON)输出,即输出高电平的模式测试时钟信号。接下来,如图6中第四时段T4所示,当图5中上述测试模式信号(Test_mode)为高电平(例如:Test_mode为“1”)时,上述模式控制器210中的上述第四数据选择器506选择输出上述来自寄存器模式控制模块216的模式扫描使能备份时钟信号(Scan_en_dp)作为模式扫描使能时钟信号(SE)输出,即输出高电平的模式扫描使能时钟信号。最后,如图6中第五时段T5所示,当图4中的时钟控制器208接收来自上述寄存器时钟控制模块214及上述模式控制器210传送的上述使能时钟信号(SCAN_EN)及模式扫描使能时钟信号(SE)为高电平时,上述时钟控制器208输出同上述寄存器移位时钟同频的移位时钟IP_CLK信号至图2所示的上述扫描链测试电路212或者说上述时钟控制器208的移位时钟IP_CLK切换为上述寄存器控制器204输出的寄存器移位时钟并传送上述寄存器移位时钟至图2所示的上述扫描链测试电路212。此时,在上述移位时钟信号(IP_CLK)的作用下,上述第一时段T1输入至扫描链测试电路212的测试数据(SCAN_IN[n:0])在上述扫描链测试电路中移位进行扫描,并在第五时段T5起经由扫描链测试电路的输出管脚(Output Pad)输出测试数据(SCAN_OUT[n:0])至图2中的寄存器控制器204,上述寄存器控制器204记录测试数据并整合(Reg_scan_out[n:0])输出至外部设备202供测试人员分析。需要注意的是,图6还绘出若干个时钟周期之后,即表示测试完成T6时段之后的信号示意图。此部分时段之后的时钟信号图会由于具体电路结构而变化,图6只做简单绘示,并不做具体说明和限制。

需要解释的是,上述结合图6的时钟信号示意图的说明只是扫描链控制电路在使能时钟信号为高电平的工作状态,以下将结合表1所示详细介绍。

如表1所示,扫描链控制电路可工作在三种模式中,即扫描模式(Scan mode)、原始测试模式(Original test mode)及功能模式(Function mode)。当扫描链控制电路接通外部设备202并接收由外部设备202传送的若干个TCK时钟周期之后(如图6所示为两个时钟周期)。当图2所示的扫描链控制电路200中的寄存器控制器204产生一高电平的使能时钟信号(SCAN_EN)。如图4所示的时钟控制器208接收上述高电平的使能时钟信号(SCAN_EN)时,图4中的数据选择器414选择寄存器移位时钟(shift_clk)输出至数据选择器416。如图5所示的寄存器控制器204会相应产生高电平的Scan_mode_dp和Scan_en_dp信号。

再者,当测试模式信号(Test_mode)为高电平时,如图5所示的模式控制器210中的数据选择器506选择高电平的Scan_en_dp信号输出,模式控制器210中的数据选择器504选择高电平的Scan_mode_dp信号输出。此处需要说明的是,表1中数据选择器506和数据选择器504的输出只标注Scan_mode_dp和Scan_en_dp信号而并未标注此信号为高电平或者低电平。应特别解释的是,当上述使能时钟信号(SCAN_EN)和上述测试模式信号(Test_mode)同为高电平时,上述Scan_mode_dp和Scan_en_dp必为高电平而不存在低电平状态,但本领域技术人员可根据自身需求自行设计,所以表1中并未标注Scan_mode_dp和Scan_en_dp信号状态。

接着回到图4所示,当图4中的数据选择器416接收到高电平的SE信号(可为高电平Scan_en_dp信号),图4中的数据选择器416选择shift_clk输出至扫描链测试电路。此时表示,扫描链控制电路工作在Scan mode状态,且输入至扫描链测试电路的测试数据为寄存器输入数据Reg_scan_in[n:0]。

当图2所示的扫描链控制电路200中的寄存器控制器产生一低电平的使能时钟信号(SCAN_EN)。如图4所示的时钟控制器208接收上述低电平的使能时钟信号(SCAN_EN)时,图4中的数据选择器414选择管脚移位时钟(Ext_clk)输出至数据选择器416。此时需要注意的是,如图5所示的寄存器控制器204可以认为不产生Scan_mode_dp和Scan_en_dp信号或认为产生低电平的Scan_mode_dp和Scan_en_dp信号。

再者,当测试模式信号(Test_mode)为低电平时,如图5所示的模式控制器210中的数据选择器506选择高电平的SE_i信号输出,模式控制器210中的数据选择器504选择高电平的DFT_i信号输出。此处需要说明的是,表1中数据选择器506和数据选择器504的输出只标注SE_i和DFT_i信号而并未标注此信号为高电平或者低电平。应特别解释的是,此时SE_i和DFT_i由图5所示的其他电路模块(未绘示)拉升为高电平。

接着回到图4所示,当图4中的数据选择器416接收到高电平的SE信号(可为高电平SE_i信号),图4中的数据选择器414选择管脚移位时钟(Ext_clk)输出至扫描链测试电路。此时表示,扫描链控制电路工作在Original test mode状态,且输入至扫描链测试电路的测试数据为寄存器输入数据SI_0、SI_1…SI_n。

最后需要解释的是,当图2所示的扫描链控制电路200中的寄存器控制器产生一低电平的使能时钟信号(SCAN_EN)。如图4所示的时钟控制器208接收上述低电平的使能时钟信号(SCAN_EN)时,图4中的数据选择器414选择管脚移位时钟(Ext_clk)输出至数据选择器416。再者,当测试模式信号(Test_mode)为低电平时,如图5所示的模式控制器210中的数据选择器506和504接收由图5所示的其他电路模块(未绘示)输出的低电平的SE_i信号和DFT_i信号输出。应特别解释的是,此时低电平的SE_i和DFT_i表示不做测试,执行芯片正常的功能验证工作,即表示进入Function mode,所以测试数据依据芯片测试功能决定而未知。

此处需更详细说明的是,上述三种测试模式状态之间可自由切换,即一种测试模式状态完成之后可切换至另两种测试模式状态中的某一种。如图6所示(表示此时扫描链控制电路200工作在扫描模式(Scan mode)状态),在T5时段若干时钟周期之后,已完成测试数据(Reg_scan_out[n:0])输出至外部设备202。本发明扫描链控制电路200可执行复位(Reset)操作,所有时钟信号(如:SCAN_EN变为低电平、Func_clk与PLL时钟同步(亦称未被锁住或被阻断)、DFT_ON与SE变为低电平、Shift_clk变为低电平、IP_CLK与PLL时钟同步等)恢复至T1时段之前的时钟状态。接下来,扫描链控制电路200可重启工作在原始测试模式状态或工作模式状态,即实现扫描链控制电路200从扫描模式状态向原始测试模式状态的切换或者扫描模式状态向功能模式状态的切换。以上说明,只是简单介绍本发明的扫描链控制电路模式状态之间的切换,但本发明并不限制于此。

表1

图7是根据本发明一实施例所述的扫描链控制电路流程的示意图。其主要步骤包括:在步骤S702中,经图2所示的外部设备202传送一连续稳定的测试时钟信号TCK至寄存器控制器204,扫描链控制电路200的寄存器控制器204产生一高电平使能时钟信号(SCAN_EN=1)或一低电平使能时钟信号(SCAN_EN=0),即启用扫描模式或原始测试模式。

在步骤S704中,扫描链控制电路200根据上述高电平使能时钟信号或低电平使能时钟信号选择输出一测试数据SCAN_IN[n:0]至扫描链测试电路212。如图2所示,当使能时钟信号为高电平(例如:使能信号为“1”)时,数据选择器206选择寄存器控制器204传送至第二输入端的测试数据(Reg_scan_in[n:0])作为测试数据输入至扫描链测试电路212。当使能时钟信号为低电平(例如:使能信号为“0”)时,数据选择器206选择扫描链测试电路212传送至第一输入端的测试数据(SI_0、SI_1…SI_n)作为测试数据输入至扫描链测试电路212。

在步骤S706中,扫描链控制电路200的时钟控制器210触发测试数据在扫描链测试电路212中移动。如图4所示,因为当使能信号为高电平(例如:使能信号为“1”)时,时钟控制器210接收一高电平使能信号。上述时钟控制器210的第一数据选择器414选择上述第二输入端接收的上述寄存器时钟控制模块214传送的寄存器移位时钟信号(Shift_clk)传送至第二数据选择器416。上述时钟控制器210的第二数据选择器416选择上述第二输入端接收的上述第一数据选择器414传送的一寄存器移位时钟信号(Shift_clk)作为移位时钟信号(IP_CLK)输出至扫描链测试电路212。当使能信号为低电平(例如:使能信号为“0”)时,时钟控制器210接收一低电平使能信号。上述时钟控制器210的第一数据选择器414选择上述第一输入端接收的上述扫描链测试电路212传送的管脚移位时钟信号(Ext_clk)传送至第二数据选择器416。上述时钟控制器210的第二数据选择器416选择上述第二输入端接收的上述第一数据选择器414传送的一管脚移位时钟信号(Ext_clk)作为移位时钟信号(IP_CLK)输出至扫描链测试电路212。

在步骤S708中,输出所有扫描链测试电路212的测试数据。因为当使能时钟信号为高电平且测试模式信号为低电平或使能时钟信号为低电平且测试模式信号为高电平时,扫描链测试电路212中的所有寄存器数据在上述寄存器移位时钟(shift_clk)或(Ext_clk)的作用下会整体向下一级寄存器逐级移动,并经扫描链测试电路212的输出管脚输出测试数据(SCAN_OUT[n:0]),并经由寄存器控制器204输出测试数据(Reg_scan_out[n:0])至测试访问端口输出测试数据至芯片外部测试设备202。

在步骤S710中,重复步骤S706、S708至所有数据移位输出至外部设备202。

结合图1至图7所述为该扫描链控制电路的测试原理,以下将详细解释当芯片被封装在PCB板上时,该扫描链控制电路如何实现测试灵活性。图8是根据本发明一实施例所述的扫描链测试电路封装在PCB板上的示意图。如图8所示,仅示出待测试的集成设计电路IC1、IC2及其相应的扫描链测试电路212-1、212-2、212-3、212-4(如图中虚线框中所示,矩形图形示意为一个D型触发器或者其他测试基本单元电路结构,本发明并不限制于此)、PAD管脚与扫描链控制电路200。此处需要说明的是,如图中所示待测试的集成设计电路IC1、IC2仅示出各自的两条扫描链测试电路212-3、212-4和212-1、212-2。但是,待测试的集成设计电路和扫描链测试电路的数量可根据实际测试需要或者根据待测试的集成设计电路的产品功能等相应的测试需求而定,本领域技术人员可根据实际情况自行设计,本发明并不限制扫描链测试电路的数量。此外,当测试电路(亦表示包含扫描链控制电路和扫描链测试电路)被封装在PCB板上时,上述扫描链测试的PAD管脚(如图2所示的输入/输出管脚)会被封装在PCB板上。如图8所示,被封装在PCB板上的管脚表示为如图中阴影矩形的PAD管脚,但是本领域技术人员不应将两者管脚混淆。或者为了将图2所示的PAD管脚与图8所示的PAD管脚作区分与方便理解,上述PCB板上的PAD管脚亦可称为引线接口或引线端,下文在说明PCB板上的管脚时将采用引线端描述。另外,为了方便图示绘示,图8仅示出扫描链控制电路200,关于扫描链控制电路200内部电路结构与扫描链测试电路212-1、212-2、212-3、212-4的具体电路结构,扫描链控制电路200控制扫描链测试电路212-1、212-2、212-3、212-4的具体细节,请参考图2至图5部分的说明,在此不做详细介绍。还有一点需要说明的是,如图8所示扫描链测试电路212-1、212-2、212-3、212-4的输入管脚(应理解为图2中所示的Input_0、Input_1、…、Input_n管脚,图8中未绘示)全部直接连接在各自的扫描链测试电路212-1、212-2、212-3、212-4上,但是在图2所示中,扫描链测试电路212的输入管脚(Input_0、Input_1、…、Input_n)并未直接连接至扫描链测试电路上。此处应解释的是,本领域技术人员即可以按照图2所示连接方式设计电路连接亦可按照图8所示连接方式设计电路连接。为了方便解释本发明的电路原理和图示绘示方便,图2所示为主要解释扫描链控制电路控制扫描链测试电路的电路设计方式,故扫描链测试电路212的输入管脚(Input_0、Input_1、…、Input_n)未直接连接至扫描链测试电路上,本发明并不限制于此。

如图8所示,当测试电路(亦表示包含扫描链控制电路和扫描链测试电路)被封装在PCB板上时,上述待测试的集成设计电路IC1、IC2各自的两条扫描链测试电路212-3、212-4和212-1、212-2在PCB板上的引线端,如阴影的矩形所示。

此时,如需测试集成设计电路IC1和/或集成设计电路IC2,只需从212-3、212-4的引线端和/或212-1、212-2的引线端分别汇入待测试数据或导出测试数据(图示未区分输入端与输出端,但本发明并不限制于此。)供设计人员分析芯片设计。然而,随着集成设计电路的发展,当芯片从晶圆片上的一个个裸片(或称为die)被封装至PCB板上时,芯片测试将会面临诸多问题。一方面,每条扫描链测试电路分别有输入和输出两个管脚,当扫描链测试电路过多时(举例来说,扫描链测试电路为50条时,将会有100个管脚),分别从每条扫描链测试电路的引线端引线进行测试,将大大增加测试的难度,增大开发测试成本。另一发面,当被封装至PCB板上时还会造成引线端连接故障,亦可能会造成测试时短路和/或断路等接触不良故障,导致测试结果准确性下降,不利于分析。

基于上述分析,如图8所示将所有扫描链测试电路的输入/输出管脚统一耦接至扫描链控制电路(如图8中所示虚线框中的扫描链测试电路212-1、212-2、212-3、212-4的输入/输出管脚统一耦接至扫描链控制电路),并经由上述扫描链控制电路控制汇入待测试数据或导出测试数据(图示未区分输入端与输出端,但本发明并不限制于此)。扫描链控制电路通过一测试接口与外部设备连接(如图8中所示为Interface接口)。

在一些实施例中,上述扫描链控制电路可应用于联合测试工作组(Joint TestAction Group,JTAG)调试接口和/或串行线调试(Serial Wire Debug,SWD)接口,本发明对此不进行限制。

在一些实施例中,上述扫描链控制电路封装时可应用于球形触点阵列(ball gridarray,BGA)、倒焊芯片(flip-chip)或触点陈列封装(land grid array,LGA)等封装方式,本发明对此不进行限制。

具体来说,当裸片被封装至PCB板上后,若芯片设计相对来说比较简单,引线端数量比较少,且封装质量完好时,可直接采用从引线端外接引线进行测试。若芯片设计复杂,引线端数量较多或者不确定封装质量是否完好时(造成测试时短路和/或断路等接触不良故障),就可以采用不需要通过引线端测试,而是可以直接通过扫描链控制电路控制测试。换句话说,上述扫描链控制电路直接通过测试电路板上接口进行芯片测试而不需要通过引线端外接引线进行测试。该扫描链控制电路可以使用管脚输入数据(SCAN_IN[n:0])将测试数据输入至扫描链测试电路并在管脚移位时钟(Ext_clk)的作用下进行测试后将测试完成的测试数据(Scan_out[n:0])输出至外部设备供设计人员分析。此时,称之为扫描链控制电路工作在原始测试模式(Original test mode)。更具体的,该扫描链控制电路亦可以使用寄存器输入数据(Reg_scan_in[n:0])并在寄存器移位时钟信号(Shift_clk)的作用下将测试数据输入至扫描链测试电路进行测试后将测试完成的测试数据(Reg_scan_out[n:0])输出至外部设备供设计人员分析。此时,称之为扫描链控制电路工作在扫描模式(Scanmode)。更有甚者,当芯片验证测试完成之后,亦可关闭扫描链控制电路。此时,称之为扫描链控制电路工作在功能模式(Function mode)。此部分内容的描述请参考图2至图7所示部分的说明,在此不再赘述。

上述扫描链控制电路可以使用管脚输入数据(SCAN_IN[n:0])将测试数据输入至扫描链测试电路并在管脚移位时钟(Ext_clk)的作用下进行测试后将测试完成的测试数据(Scan_out[n:0])输出至外部设备。需要说明的是,上述管脚输入数据(SCAN_IN[n:0])是由上述扫描链测试电路的输入管脚(此管脚应理解为图2所示的扫描链测试电路的输入管脚,而不应理解为PAB版上的引线端)传送的测试数据至扫描链控制电路,并经由该扫描链控制电路传送至扫描链测试电路完成测试(关于此部分内容,请参考参考图3部分的说明,在此不再赘述)。最终,测试完成的测试数据(Scan_out[n:0])可直接通过测试电路板上引线端输出至外部设备亦可通过将测试完成的测试数据(Scan_out[n:0])传送至扫描链控制电路并经由Interface接口输出至外部设备。具体的说,测试完成的测试数据(Scan_out[n:0])要输出时,可以有两种选择方式。第一,可直接通过PCB板上的引线端引线输出至外部设备。第二,可以将测试完成的测试数据(Scan_out[n:0])输出至扫描链控制电路,并经由Interface接口输出至外部设备。关于输出测试数据的情况,因为与输入测试数据的情况是类似的原理,本领域相关技术人员可在理解本发明输入测试数据的原理的基础上,可相应的更改输出数据的方式,本发明对输出数据的方式并不做任何限制。

上述扫描链控制电路亦可以使用寄存器输入数据(Reg_scan_in[n:0])并在寄存器移位时钟信号(Shift_clk)的作用下将测试数据输入至扫描链测试电路进行测试后将测试完成的测试数据(Reg_scan_out[n:0])输出至外部设备。需要说明的是,上述寄存器输入数据是由上述扫描链控制电路中的一系列的寄存器产生的测试数据(如图2中的寄存器输入数据(Reg_scan_in[n:0]),但未绘示出具体的寄存器)并经由该扫描链控制电路传送至扫描链测试电路完成测试(关于此部分内容,请参考参考图2和图6部分的说明,在此不再赘述)。最终,测试完成的测试数据(Reg_scan_out[n:0])可直接通过测试电路板上引线端输出至外部设备亦可通过将测试完成的测试数据(Reg_scan_out[n:0])传送至扫描链控制电路并经由Interface接口输出至外部设备。关于寄存器输入数据(Reg_scan_in[n:0])测试完成之后的输出原理,与上述测试完成的测试数据(Scan_out[n:0])的输出原理解释类似,在此不再赘述。

综合以上所述,当芯片被封装在PCB板上时本发明的扫描链控制电路可通过测试电路板上的布线(亦称接口)直接进行芯片测试而不需要通过引线端外接引线进行测试。同时,该扫描链控制电路可选择管脚输入数据(SCAN_IN[n:0])进行测试亦可选择寄存器输入数据(Reg_scan_in[n:0])进行测试。不仅提高了测试的准确性,而且提高了测试选择的灵活性,能极大的提高测试正确性和效率。

以上仅以较佳实施例对本发明进行说明,使本领域技术人员可以从各个方面更佳地了解本发明,但是本领域技术人员可以对本发明进行各种改动和变形而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变形属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变形在内。

- 扫描链控制电路设计方法及扫描链电路

- 扫描链控制电路