一种高密度三态内容寻址存储器及其寻址方法

文献发布时间:2023-06-19 11:05:16

技术领域

本发明涉及嵌入式控制技术领域,尤其是涉及一种高密度三态内容寻址存储器及其实现方法。

背景技术

在大数据和云计算时代,随着各种智能设备的普及,大量的数据随之产生,同时也需要网络进行传输。为了提高数据传输效率和安全性,在路由器中对数据进行筛选变得非常必要。传统基于软件的筛选方法主要依赖CPU(中央处理器)和主存之间进行多次存取和比较操作实现,时间成本和功耗代价都比较大。而TCAM(ternary content addressablememory,三态内容寻址存储器)作为一种硬件层面的解决方案,可以通过并行比较实现快速高效的查找和匹配,较好地解决了传统软件实现方法存在的问题。

TCAM的快速查找和匹配往往是以芯片面积的增长和功耗的增加为代价。传统的TCAM设计以SRAM(静态随机存取存储器)为基础,单个TCAM单元往往需要12-16个晶体管,单元面积过大导致TCAM存储密度很难提升,同时,面积大也导致寄生电容较大,造成动态(active)功耗较大。另外,传统的TCAM继承了SRAM的易失特性,静态(standby)模式不能切断电源,否则所存储的信息丢失,这一特性也导致其静态功耗较大。

针对传统TCAM存在的问题,目前的一个研究热点是如何基于新型高密度存储器来实现高密度TCAM。在国际上,著名的研究机构包括IBM、NEC和Tohoku大学、TSMC和中国台湾清华大学等在集成电路领域的旗舰会议ISSCC(国际固态集成电路会议)和Symposium onVLSI Circuits(VLSIC,大规模集成电路研讨会)从2011年到2016年连续六年报道高密度TCAM的相关成果,相比传统TCAM,现有的高密度TCAM具有单元面积较小、静态功耗低等优点。首先,TCAM单元中晶体管数目减少到2-6个,大大减小了TCAM单元的面积,其次,新型存储器的高密度特性使得TCAM在休眠状态下可以彻底断电而不用担心信息丢失,有利于减小了静态功耗。但是,现有的高密度TCAM方案仍存在一些问题,主要表现在:

“0”和“1”信号之间的存储窗口较小,对于基于MRAM的高密度TCAM,由于MRAM本身Roff/Ron(Ron为低阻,Roff为高阻)较小,且易受波动影响,导致相应的高密度TCAM中的“0”和“1”信号之间的存储窗口小。对于基于RRAM的高密度TCAM,由于其主要依赖RRAM存储电阻与晶体管之间分压获得“0”或“1”,而晶体管和RRAM存储电阻在小尺寸时波动都比较大,且波动规律不一致,导致所得到的“0”和“1”信号之间的存储窗口易受波动影响而变差。

TCAM单元的面积仍然较大,现有的最小高密度TCAM单元面积仍有50F2(F为每个工艺代下的特征尺寸)。由于现有的高密度TCAM单元仍需要晶体管的辅助才能实现TCAM功能,而晶体管需要制作在CMOS前段工艺上,这样一方面撑大TCAM单元的面积,另一方面也限制了TCAM单元三维(3D)集成的可能性,也不利于发挥RRAM的3D可集成能力。

发明内容

为解决现有技术的不足,实现减小存储单元体积,增大存储器存储密度,提高存储器可靠性,使存储器的3D集成成为可能的目的,本发明采用如下的技术方案:

一种高密度三态内容寻址存储器,包括:驱动电路、存储单元、放大器,还包括搜索线、匹配线和互补搜索线,所述驱动电路包括匹配线驱动电路和搜索线驱动电路,所述放大器是匹配线灵敏放大器,所述存储单元包括第一存储电阻和第二存储电阻,所述匹配线驱动电路与所述匹配线相连,所述搜索线驱动电路分别与所述搜索线、所述互补搜索线相连,所述匹配线灵敏放大器与所述匹配线相连,所述第一存储电阻的第一端与所述搜索线相连,所述第一存储电阻的第二端与所述匹配线相连,所述第二存储电阻的第一端与所述互补搜索线相连,所述第二存储电阻的第二端与所述匹配线相连;

所述匹配线驱动电路,用于产生置位电压;

所述搜索线驱动电路,用于产生复位电压;

所述匹配线灵敏放大器,用于将匹配信号放大并输出。

进一步的,所述存储单元还包括第一限流器件和第二限流器件,所述第一存储电阻的第一端与所述第一限流器件串联后,再与所述搜索线相连,所述第二存储电阻的第一端与所述第二限流器件串联后,再与所述互补搜索线相连,增加所述限流器件能够提升存储单元的可靠性。

进一步的,所述存储单元呈阵列式排布,位于同一行上的所述存储单元共用一条匹配线,位于同一列上的所述存储单元共用一条搜索线和互补搜索线。

进一步的,所述匹配线灵敏放大器是比较放大器,对匹配线的输出电压与参考电压进行比较,并将比较结果放大输出。

一种高密度三态内容寻址方法,包括如下步骤:

步骤S1,获取搜索信号,所述搜索信号包括“1”、“0”和“X”;

步骤S2,判断所述搜索信号是否为“1”;

步骤S3,如果所述搜索信号为“1”,则将匹配线和搜索线充电至预充电电压,互补搜索线保持低电平;

步骤S4,如果所述搜索信号不为“1”,则判断所述搜索信号是否为“0”;

步骤S5,如果所述搜索信号为“0”,则将所述匹配线和互补搜索线预充电至高电平,搜索线保持低电平;

步骤S6,如果所述搜索信号不为“0”,则判断所述搜索信号是否为“X”;

步骤S7,如果所述搜索信号为“X”,则将所述搜索线、匹配线和互补搜索线预充电至高电平;

步骤S8,获取所述匹配线输出端的电压;

步骤S9,判断输出电压是否大于参考电压,

所述参考电压的值为高电平VH2与低电平VL2之间的设定值,所述高电平VH2为所述搜索信号与存储单元的存储信息发生匹配时,匹配线在放电阶段放电后的电平值,所述低电平VL2为所述搜索信号与存储单元的存储信息不匹配时,匹配线在放电阶段放电后的电平值;

步骤S10,如果输出电压大于参考电压,则输出“1”,代表存储器单元存储信息与搜索信息相匹配;

步骤S11,如果输出电压小于等于参考电压,则输出“0”,代表存储器单元存储信息与搜索信息不匹配。

进一步的,所述步骤S3之后,存储器进入放电阶段,在搜索“1”时,如果所述存储单元存储的逻辑值为“1”,则所述存储单元对匹配线只有高阻放电通路,在同行其他存储单元也发生匹配的情况下,匹配线只会放电到一个高电平VH1,由于匹配线和搜索线之间的存储电阻为低阻态,搜索线也会随匹配线放电到一个较高电平;如果存储单元存储的逻辑值为“0”,则所述存储单元对匹配线会有低阻放电通路,匹配线会放电到低电平VL1,搜索线和匹配线之间的存储电阻为高阻态,搜索线会放电到一个高电平;

所述步骤S5之后,存储器进入放电比较阶段,在搜索“0”时,如果所述存储单元存储的逻辑值为“0”,则所述存储单元对匹配线只有高阻放电通路,在同行其他存储单元也发生匹配的情况下,匹配线只会放电到一个高电平VH1,由于匹配线和互补搜索线之间是存储电阻为低阻态,互补搜索线也会随匹配线放电到一个高电平;如果存储单元存储的逻辑值为“1”,则该存储单元对匹配线会有低阻放电通路,匹配线会放电到较低电平VL1,互补搜索线和匹配线之间的存储电阻为高阻态,互补搜索线会放电到一个高电平;

步骤S7之后,存储器进入放电比较阶段,不管所述存储单元所存逻辑值是“1”还是“0”,所述存储单元不会对所述匹配线放电。

进一步的,步骤S3中的预充电电压为电源电压。

进一步的,步骤S3中,当存储器中包含限流器件时,所述预充电电压为电源电压与所述限流器件的导通电压之和。

进一步的,存储器的写操作采用施加激励的方式,分为两步,第一步:先写第一存储电阻,第二步:再写第二存储电阻,激励施加方式采用VPP/2或VPP/3算法,VSET为置位电压,VRESET为复位电压,VT为限流器件的导通电压,VSET和VRESET电压由匹配线驱动电路和搜索线驱动电路产生,写操作的VPP/2算法施加激励方式如下:

当写入数据为“0”时,第一步的搜索线为“0”,互补搜索线为VSET/2,匹配线为VSET;第二步的搜索线为VRSET/2,互补搜索线为VRSET,匹配线为“0”;

当写入数据为“1”时,第一步的搜索线为VSET/2,互补搜索线为“0”,匹配线为VSET;第二步的搜索线为VRSET,互补搜索线为VRSET/2,匹配线为“0”;

当写入数据为“0”时,第二步的搜索线为VRSET,互补搜索线为VRSET,匹配线为“0”;

写操作的VPP/3算法施加激励方式如下:

当写入数据为“0”时,第一步的搜索线为“0”,互补搜索线为2/3*VSET,匹配线为VSET;第二步的搜索线为2/3*VSET,互补搜索线为VRSET,匹配线为“0”;

当写入数据为“1”时,第一步的搜索线为2/3*VSET,互补搜索线为“0”,匹配线为VSET;第二步的搜索线为VRSET,互补搜索线为2/3*VSET,匹配线为“0”;

当写入数据为“0”时,第二步的搜索线为VRSET,互补搜索线为VRSET,匹配线为“0”。

进一步的,当存储器中包含限流器件时,写操作的VPP/2算法施加激励方式如下:

当写入数据为“0”时,第一步的搜索线为“0”,互补搜索线为(VSET+VT)/2,匹配线为VSET+VT;第二步的搜索线为(VSET+VT)/2,互补搜索线为VRSET+VT,匹配线为“0”;

当写入数据为“1”时,第一步的搜索线为(VSET+VT)/2,互补搜索线为“0”,匹配线为VSET+VT;第二步的搜索线为VRSET+VT,互补搜索线为(VRSET+VT)/2,匹配线为“0”;

当写入数据为“0”时,第二步的搜索线为VRSET+VT,互补搜索线为VRSET+VT,匹配线为“0”;

写操作的VPP/3算法施加激励方式如下:

当写入数据为“0”时,第一步的搜索线为“0”,互补搜索线为2/3*(VSET+VT),匹配线为VSET+VT;第二步的搜索线为2/3*(VSET+VT),互补搜索线为VRSET+VT,匹配线为“0”;

当写入数据为“1”时,第一步的搜索线为2/3*(VSET+VT),互补搜索线为“0”,匹配线为VSET+VT;第二步的搜索线为VRSET+VT,互补搜索线为2/3*(VRSET+VT),匹配线为“0”;

当写入数据为“0”时,第二步的搜索线为VRSET+VT,互补搜索线为VRSET+VT,匹配线为“0”。

本发明的优势和有益效果在于:

本发明提供的高密度三态内容寻址存储器,采用可以在互补金属氧化物半导体CMOS后段工艺集成的器件来构建存储单元,不包含需要在CMOS前段工艺集成的晶体管,一方面,减小了存储单元的体积,增大了存储器的存储密度,另一方面,使存储器的3D集成成为可能。而且,本发明在搜索信息时,采用匹配线驱动电路将匹配线充电至预充电电压,采用搜索线驱动电路将所述搜索线和所述互补搜索线的电压复位,即“0”和“1”信号的获得并不是通过晶体管的分压得到的,避免了由晶体管的分压带来的“0”和“1”信号之间的存储窗口小的问题,提高了存储器的可靠性。

附图说明

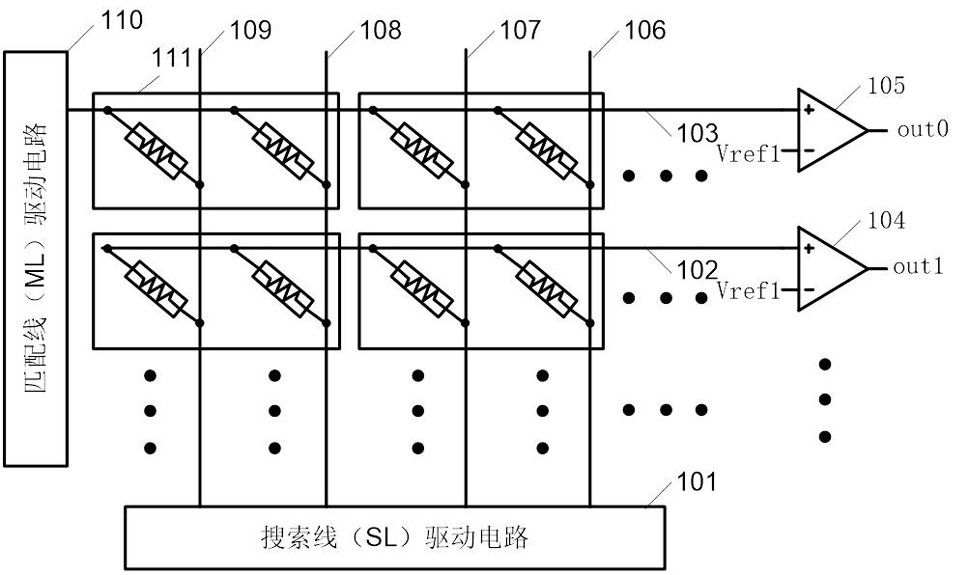

图1为本发明中实施例一的高密度三态内容寻址存储器的结构示意图。

图2为本发明中实施例一的高密度三态内容寻址存储器的存储单元的结构示意图。

图3为本发明中实施例二的高密度三态内容寻址存储器的存储单元的结构示意图。

图4为本发明中实施例二的高密度三态内容寻址存储器的结构示意图。

图5为本发明高密度三态内容寻址存储器的寻址方法流程示意图。

图6为本发明中实施例一的高密度三态内容寻址存储器寻址时的充放电示意图。

具体实施方式

以下结合附图对本发明的具体实施方式进行详细说明。应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明,并不用于限制本发明。

实施例一:

如图1所示,高密度三态内容寻址存储器包括:搜索线107、109,匹配线102、103,互补搜索线106、108,匹配线驱动电路110,搜索线驱动电路101,多个匹配线灵敏放大器104、105和多个存储单元111,所述多个存储单元呈阵列式排布,位于同一行上的所述存储单元共用一条匹配线,不位于同行上的所述存储单元不共用一条匹配线,位于同一列上的所述存储单元共用一条搜索线和互补搜索线,不位于同一列上的所述存储单元不共用同一条搜索线,且不位于同一列上的所述存储单元不共用同一条互补搜索线;匹配线灵敏放大器与匹配线一一对应连接,匹配线的输出端与所述匹配线灵敏放大器的输入端相连接,所述匹配线灵敏放大器用于对匹配线的输出电压与参考电压Vref1进行比较,并将比较结果放大输出;所述匹配线驱动电路110与所述匹配线相连,所述匹配线驱动电路110用于产生置位电压;所述搜索线驱动电路101分别与所述搜索线、所述互补搜索线相连,所述搜索线驱动电路101用于产生复位电压。

如图2所示,所述存储单元包括第一存储电阻201和第二存储电阻202,所述第一存储电阻201的第一端203与所述搜索线107、109相连,所述第一存储电阻201的第二端204与所述匹配线102、103相连,所述第二存储电阻202的第一端205与所述互补搜索线106、108相连,所述第二存储电阻202的第二端206与所述匹配线102、103相连。

实施例二:

如图3所示,高密度三态内容寻址存储器的存储单元中,第一存储电阻201第一端203与第一限流器件301串联后再与所述搜索线107、109相连,所述第二存储电阻202的第一端205与所述第二限流器件302串联后再与所述互补搜索线106、108相连,第一存储电阻201的第二端204与匹配线102、103相连,第二存储电阻202的第二端206与匹配线102、103相连,增加所述限流器件能够提升存储单元的可靠性。

如图4所示,高密度三态内容寻址存储器的存储单元401为具有限流器件的存储单元,其他元件及连接关系与实施例一中的高密度三态内容寻址存储器相同,包括搜索线107、109,匹配线102、103,互补搜索线106、108,匹配线驱动电路110,搜索线驱动电路101,多个匹配线灵敏放大器104、105和多个存储单元401。

本发明提供的高密度三态内容寻址存储器采用阻变式存储器RRAM等可以在后段工艺集成的器件构建而成,并没有使用在互补金属氧化物半导体CMOS工艺的前段制作的晶体管等器件,减小了存储单元的体积,增大了存储器的存储密度,同时,本发明提供的高密度三态内容寻址存储器不再使用传统的晶体管分压的方式获得“1”和“0”的存储窗口,避免了“1”和“0”窗口波动大,不稳定的问题出现,增强了信息存储的可靠性。

如图5所示,高密度三态内容寻址方法,包括如下步骤:

步骤501:获取搜索信号,所述搜索信号包括“1”、“0”和“X”,“1”、“0”和“X”为逻辑值;

步骤502:判断所述搜索信号是否为“1”;

步骤503:如果所述搜索信号为“1”,则匹配线驱动电路将匹配线充电至预充电电压,搜索线驱动电路将搜索线充电至预充电电压,互补搜索线保持低电平,对于实施例一中的不含限流器件的存储单元,所述预充电电压一般为电源电压,对于实施例二中含有限流器件的存储单元,所述预充电电压一般为电源电压与所述限流器件的导通电压之和。之后,存储器进入放电阶段,如图6所示,在搜索“1”,如果所述存储单元存储的逻辑值为“1”,则所述存储单元对匹配线只有高阻放电通路,在同行其他存储单元也发生匹配的情况下,匹配线ML只会放电到一个较高电平VH1,由于匹配线ML和搜索线SL之间是存储电阻为低阻态,搜索线SL也会随匹配线ML放电到一个较高电平,如图6中的实线607所示;如果所述存储单元存储的逻辑值为“0”,所述存储单元对匹配线ML会有低阻放电通路,匹配线ML会放电到较低电平VL1,如图6中的虚线608所示,搜索线SL和匹配线ML之间的存储电阻为高阻态,搜索线SL会放电到一个较高电平;

步骤504:如果所述搜索信号不为“1”,则判断所述搜索信号是否为“0”;

步骤505:如果所述搜索信号为“0”,则将所述匹配线和互补搜索线预充电至高电平,搜索线保持低电平,之后,进入放电比较阶段,如图6所示,在搜索“0”时,如果所述存储单元存储的逻辑值为“0”,则所述存储单元对匹配线ML只有高阻放电通路,在同行其他存储单元也发生匹配的情况下,匹配线ML只会放电到一个较高电平VH1,如图6中的实线604所示,由于匹配线ML和互补搜索线SLB之间是存储电阻为低阻态,互补搜索线SLB也会随匹配线ML放电到一个较高电平;如果存储单元所存逻辑值为“1”,则该存储单元对匹配线ML会有低阻放电通路,匹配线ML会放电到较低电平VL1,如图6中的虚线605所示,互补搜索线SLB和匹配线ML之间的存储电阻为高阻态,互补搜索线SLB会放电到一个较高电平;图6中601为搜索线SL预充电及放电信号的波形,602为互补搜索线SLB预充电及放电信号的波形,603为匹配线ML预充电及搜索匹配时的放电信号的波形。

步骤506:如果所述搜索信号不为“0”,则判断所述搜索信号是否为“X”;

步骤507:如果所述搜索信号为“X”,则将所述搜索线、匹配线和互补搜索线预充电至高电平,之后,进入放电比较阶段,如图6中的609所示,不管所述存储单元所存逻辑值是“1”还是“0”,所述存储单元不会对所述匹配线放电;

步骤508:获取所述匹配线输出端的电压;

步骤509:判断所述输出电压是否大于参考电压,所述参考电压的值为设定值,所述设定值为所述高电平VH2和所述低电平VL2中间的一个电平值,如图6中的虚线610所示;

步骤510:如果所述输出电压大于参考电压,所述参考电压即为图6中610所代表的电压,则与匹配线相连的灵敏放大器输出“1”,代表存储器单元存储信息与搜索信息相匹配,所述灵敏放大器为一个比较放大器;

步骤511:如果所述输出电压小于或等于参考电压,则与匹配线相连的灵敏放大器输出“0”,代表存储器单元存储信息与搜索信息不匹配。

本发明所述的预充电电压在本发明提供的实施例一中一般为电源电压,在实施例二中为电源电压与限流器件的导通电压之和。

其中,对于第一实施例中的存储单元存储的真值表如表一所示,对于第二实施例中的存储单元存储的真值表如表二所示。

表一

表二

对于本发明提供的高密度三态内容寻址存储器的写操作采用施加激励的方式,分为两步,先写左边电阻,然后写右边电阻,激励施加方式与crossbar(交叉阵列)架构的写操作类似,可采用VPP/2或VPP/3算法。VSET为set(置位)电压;VRESET为reset(复位)电压,VT为限流器件的导通电压。VSET和VRESET电压由ML驱动电路110和SL驱动电路101产生,实施例一提供的高密度三态内容寻址存储器的写操作的VPP/2算法施加激励方式如表三所示,VPP/3算法施加激励方式如表四所示,实施例二提供的高密度三态内容寻址存储器的写操作的VPP/2算法施加激励方式如表五所示,VPP/3算法施加激励方式如表六所示。

表三

表四

表五

表六

本发明提供的高密度三态内容寻址存储器在进行写操作以及搜索信息时,采用驱动电路置位、复位和充电,不再使用传统的晶体管分压的方式获得“1”和“0”的存储窗口,避免了“1”和“0”窗口波动大,不稳定的问题出现,增强了信息存储的可靠性。

以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明实施例技术方案的范围。

- 一种高密度三态内容寻址存储器及其寻址方法

- 一种非易失三态内容寻址存储器及其寻址方法