可释放电压应力的电位转换器

文献发布时间:2023-06-19 11:11:32

技术领域

本发明涉及一种可释放电压应力的电位转换器,尤其涉及一种使用遮蔽电路来释放电压应力的电位转换器。

背景技术

负电位转换器可用来将其摆幅介于接地(零伏)到正系统电压(VDDD)之间的正输入逻辑信号转换为其摆幅介于接地到负电压VSN(|VSN|>VDDD)之间的负输出信号。举例来说,图7为公知技术负电位转换器7的功能方块图。在图7中,第一级电路用来将一组输入信号NN及NNB转换为一组第一中继信号,其中该组第一中继信号的摆幅介于系统电压VSSD(例如,零伏)到系统电压VDDD(例如,1.2伏)之间。第二级电路用来将该组第一中继信号转换为一组第二中继信号,其中该组第二中继信号的摆幅介于系统电压VDDDN(例如,VDDDN=VSN/2=-2.75V)到系统电压VSSA(例如,零伏)。第三级电路用来将该组第二中继信号转换为一组输出信号NN_OUT及NN_OUTB,其中输出信号NN_OUT及NN_OUTB的摆幅介于系统电压VSN(例如,-5.5伏)到系统电压VSSA。然而,申请人注意到第二级电路会导致负电位转换器7耗电,然而若将第二级电路从负电位转换器7移除的话,第一级电路与第三级电路之间的电压落差太大的话会导致电压应力风险上升。因此,实有必要在耗电与电压应力风险的困境之间取得解决之道。

进一步地,负电位转换器广泛地应用在不同技术领域,例如在闪存中提供负压给存储单元进行抹去操作,或是在显示驱动芯片中提供负压给薄膜晶体管(TFT)进行导通或关闭操作。然而,当正系统电压须保持在低于1.5伏的情况下,拉升(pull-up)晶体管与拉降(pull-down)晶体管的瞬态切换(transient switching)若无法确实运作,将会导致切换延迟太长、动态电源消耗太大及电路面积太大等问题。

因此,考虑到电源消耗、电压应力风险、节省电路面积、切换速度以及低功率的要求,如何设计负电位转换器以符合上述要求,实乃当今本领域的重要课题。

发明内容

因此,本发明的主要目的在于提供一种可释放电压应力的电位转换器。

本发明揭露一种负电位转换器,包含输入级电路以及推拉级电路。输入级电路用来根据第一输入逻辑信号及第二输入逻辑信号,产生第一中继信号及第二中继信号,其中所述第一中继信号及所述第二中继信号具有第一电压摆幅,且所述第一电压摆幅介于第一系统电压与第二系统电压之间。所述输入级电路包含比较器,用来比较所述第一输入逻辑信号及所述第二输入逻辑信号;电流镜,用来调整所述第一中继信号及所述第二中继信号的大小;第一遮蔽电路,耦接于所述电流镜与所述比较器,用来根据第三系统电压来降低施加到所述比较器的第一电压应力,以及根据第四系统电压来降低施加到所述电流镜的第二电压应力;第二遮蔽电路,耦接于所述第一遮蔽电路,用来根据所述输入级电路的第一操作电压,产生所述第一中继信号;以及切换电路,耦接于所述第二遮蔽电路及所述电流镜,用来根据所述输入级电路的第二操作电压,产生所述第二中继信号。所述推拉级电路耦接于所述第二遮蔽电路及所述切换电路,用来根据所述第一中继信号及所述第二中继信号,产生第一输出信号及第二输出信号,其中所述第一输出信号及所述第二输出信号具有第二电压摆幅,且所述第二电压摆幅介于所述第三系统电压与所述第二系统电压之间;其中所述第二遮蔽电路用来降低施加到所述推拉级电路的第三电压应力;其中所述第一系统电压为正电压,且所述第二系统电压为负电压。

本发明还揭露一种正电位转换器,包含输入级电路以及推拉级电路。所述输入级电路用来根据第一输入逻辑信号及第二输入逻辑信号,产生第一中继信号及第二中继信号,其中所述第一中继信号及所述第二中继信号的电压摆幅介于第一系统电压与第二系统电压之间。所述输入级电路包含比较器,用来比较所述第一输入逻辑信号与所述第二输入逻辑信号;遮蔽电路,耦接于所述比较器,用来降低施加到所述比较器的电压应力,以及产生所述第一中继信号;电流镜,用来调整所述第一中继信号及所述第二中继信号的大小;以及切换电路,耦接于所述电流镜,用来根据所述输入状态电路的第二操作电压,产生所述第二中继信号。所述推拉级电路,耦接于所述切换电路、所述电流镜及所述遮蔽电路,用来根据所述第一中继信号及所述第二中继信号,产生具有所述电压摆幅的第一输出信号及第二输出信号;其中所述第一系统电压为正电压,且所述第二系统电压为接地电压。

附图说明

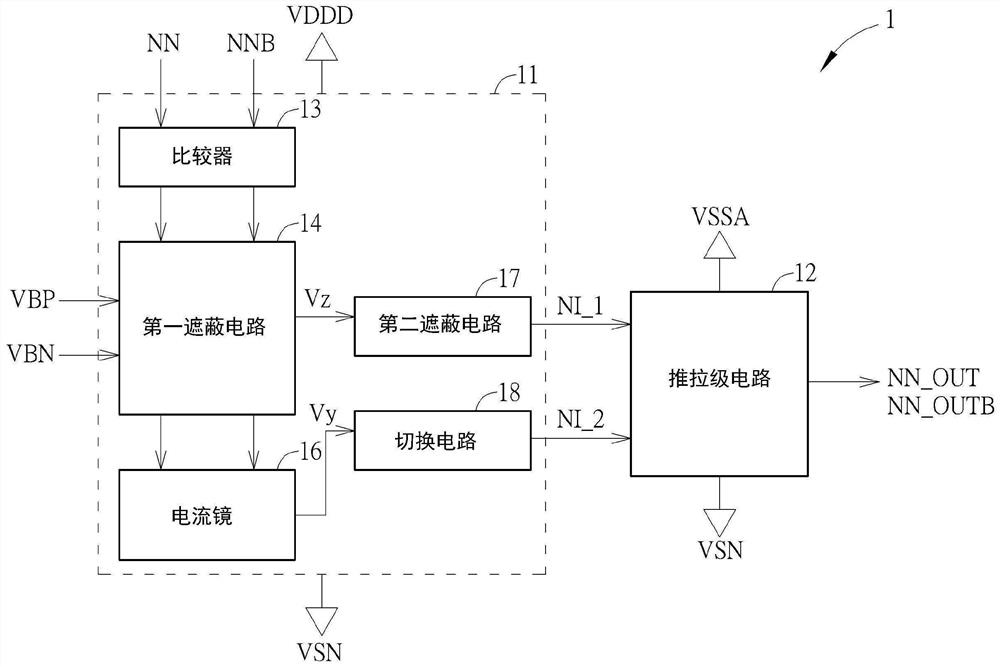

图1A为本发明实施例负电位转换器的功能方块图。

图1B为本发明实施例负电位转换器的示意图。

图2为本发明实施例负电位转换器的示意图。

图3为本发明实施例负电位转换器的示意图。

图4为本发明实施例负电位转换器的示意图。

图5A为本发明实施例正电位转换器的示意图。

图5B为本发明实施例正电位转换器的示意图。

图6为本发明实施例输入级电路的示意图。

图7为公知技术负电位转换器的功能方块图。

具体执行方式

图1A为本发明实施例负电位转换器1的功能方块图。图1B为本发明实施例负电位转换器1的示意图。负电位转换器1包含输入级电路11以及推拉级(push-pull stage)电路12。

在图1A,输入级电路11用来根据第一输入逻辑信号NNB与第二输入逻辑信号NN,产生第一中继信号NI_1与第二中继信号NI_2,其中第一中继信号NI_1与第二中继信号NI_2具有介于第一系统电压VDDD与第二系统电压VSN之间的第一电压摆幅,第二输入逻辑信号NN为第一输入逻辑信号NNB的反相(reverse-phase)信号。第一系统电压VDDD为正电压,第二系统电压VSN为负电压,且系统电压VSN的绝对值大于第一系统电压VDDD的绝对值(意即,|VSN|>VDDD),但不限于此。

输入级电路11包含比较器13、第一遮蔽电路14、电流镜16、第二遮蔽电路17以及切换电路18。

推拉级电路12耦接于输入级电路11,用来根据第一中继信号NI_1以及第二中继信号NI_2,产生第一输出信号NN_OUT及第二输出信号NN_OUTB,其中第一输出信号NN_OUT及第二输出信号NN_OUTB具有第二电压摆幅,且第二电压摆幅介于接地电压VSSA与负系统电压VSN之间。

在图1B,比较器13用来比较第一输入逻辑信号NNB与第二输入逻辑信号NN,比较器13包含第一P型晶体管P1及第二P型晶体管P2。第一遮蔽电路14耦接于比较器13,用来根据第三系统电压VBN来降低施加到比较器13的电压应力(例如,由第一系统电压VDDD与第二系统电压VSN之间的电压差所产生电压应力);第一遮蔽电路14包含第三P型晶体管P3及第四P型晶体管P4。电流镜16用来调整第一中继信号NI_1及第二中继信号NI_2的大小;电流镜16包含第一N型晶体管N1、第二N型晶体管N2、第三N型晶体管N3及第四N型晶体管N4。第一遮蔽电路14还耦接于电流镜16,用来根据第四系统电压VBN来降低施加到电流镜16的电压应力;第一遮蔽电路14包含第五N型晶体管N5及第六N型晶体管N6。第二遮蔽电路17耦接于第一遮蔽电路14,用来根据输入级电路11的第一操作电压Vz来产生第一中继信号NI_1;第二遮蔽电路17包含第五P型晶体管P5及第七N型晶体管N7。切换电路18耦接于电流镜16,用来根据输入级电路11的第二操作电压Vy来产生第二中继信号NI_2;切换电路18包含第六P型晶体管P6及第八N型晶体管N8。

关于比较器13的电路架构,第一P型晶体管P1的源极及基极耦接于第一系统电压VDDD,第一P型晶体管P1的栅极耦接于第一输入逻辑信号NNB,且第一P型晶体管P1的漏极耦接于第三P型晶体管P3的源极。第二P型晶体管P2的源极及基极耦接于第一系统电压VDDD,第二P型晶体管P2的栅极耦接于第二输入逻辑信号NN,且第二P型晶体管P2的漏极耦接于第四P型晶体管P4的源极。第一P型晶体管P1及第二P型晶体管P2用来比较第一输入逻辑信号NNB与第二输入逻辑信号NN,以分别产生第一电流I1及第二电流I2。当输入逻辑信号NNB为逻辑“0”状态且以及反相输入逻辑信号NN为逻辑“1”状态时,第一电流I1比第二电流I2大许多(I1>>I2)。反之,当输入逻辑信号NNB为逻辑“1”状态且反相输入逻辑信号NN为逻辑“0”状态时,第二电流I2比第一电流I1大许多(I2>>I1)。

关于第一遮蔽电路14的电路架构,第三P型晶体管P3的源极耦接于第一P型晶体管P1的漏极,第三P型晶体管P3的基极耦接于第一系统电压VDDD,第三P型晶体管P3的栅极耦接于第三系统电压VBP,且第三P型晶体管P3的漏极耦接于第五N型晶体管N5的漏极。第四P型晶体管P4的源极耦接于第二P型晶体管P2的漏极,第四P型晶体管P4的基极耦接于第一系统电压VDDD,第四P型晶体管P4的栅极耦接于第三系统电压VBP,且第四P型晶体管P4的漏极耦接于第六N型晶体管N6的漏极及第二状态电路12。

请注意,第一P型晶体管P1及第二P型晶体管P2可以是低电压装置,晶体管P1、P2的源极对漏极电压应不大于其可承受的最大耐压。举例来说,晶体管P1、P2的源极对漏极电压应等于或小于第一系统电压VDDD(意即,VSD。P1≤VDDD,VSD。P2≤VDDD,)。除了晶体管P1、P2,负电位转换器1包含的其他晶体管可以是中电压装置。

当晶体管P3、N1、N3、N5被导通时,第三P型晶体管P3用来降低第一P型晶体管P1的源极对漏极电压,其中降低的幅度等于第三系统电压VBP加上第三P型晶体管P3的绝对阈值电压的总和(意即,VS。P1=VBP+|VTH。P3|)。通过控制第三系统电压VBP的电压位准,可确保施加到第一P型晶体管P1的电压应力小于第一系统电压VDDD。相似地,当晶体管P4、N2、N4、N6被导通时,第四P型晶体管P4用来降低第二P型晶体管P2的源极对漏极电压,其中降低的幅度等于第四系统电压VBP加上第四P型晶体管P4的绝对阈值电压的总和(意即,VS。P4=VBN+|VTH。P4|)。通过控制第三系统电压VBP的电压位准,可确保施加到第二P型晶体管P2的电压应力小于第一系统电压VDDD。

第五N型晶体管N5的源极耦接于第三N型晶体管N3的漏极,第五N型晶体管N5的栅极耦接于第四系统电压VBN,第五N型晶体管N5的基极耦接于第二系统电压VSN,且第五N型晶体管N5的漏极耦接于第三P型晶体管P3的漏极。第六N型晶体管N6的源极耦接于第四N型晶体管N4的漏极及栅极,第六N型晶体管N6的栅极耦接于第四系统电压VBN,第六N型晶体管N6的基极耦接于第二系统电压VSN,且第六N型晶体管N6的漏极耦接于第四P型晶体管P4的漏极。当晶体管P1、P3、N1、N3被导通时,第五N型晶体管N5用来降低第三N型晶体管N3的源极对漏极电压或是基极对漏极电压,其中降低的幅度等于第四系统电压VBN减去第五N型晶体管N5的绝对阈值电压的差值(意即,VDN1=VS。N5=VBN-|VTH。N5|)。通过控制第四系统电压VBN的电压位准,可释放第三N型晶体管N3的电压应力。相似地,当晶体管P2、P4、N2、N4被导通时,第六N型晶体管N6用来降低第四N型晶体管N4的源极对漏极电压,其中降低的幅度等于第四系统电压VBN减去第六N型晶体管N6的绝对阈值电压的差值(意即,VS。N6=VBN-|VTH。N6|)。通过控制第四系统电压VBN的电压位准,可释放第四N型晶体管N4的电压应力。

在一实施例中,多个第一遮蔽电路14可串接于比较器13与电流镜16之间。举例来说,图6为本发明实施例第一遮蔽电路140的示意图。第一遮蔽电路140包含多个遮蔽单元141~14n,其中多个遮蔽单元141~14n串接于比较器13(未绘于图6)与电流镜16之间(未绘于图6),以提供电压遮蔽功能以及释放比较器13及电流镜16的晶体管的电压应力。多个遮蔽单元141~14n可由不同的系统电压VDDD、VSN、VBP、VBP来控制。

举例来说,在遮蔽单元141中,P型晶体管P311、P411的基极连接于第一系统电压VDDD1,且P型晶体管P311、P411的栅极连接于第三系统电压VBP1;N型晶体管N511、N611的基极连接于第二系统电压VSN1,且N型晶体管N511、N611的栅极连接于第四系统电压VBP1。

在遮蔽单元142中,P型晶体管P312、P412的基极连接于第一系统电压VDDD2,且P型晶体管P312、P412的栅极连接于第三系统电压VBP2;N型晶体管N512、612的基极连接于第二系统电压VSN2,且N型晶体管N512、612的栅极连接于第四系统电压VBN。

依此类推,在遮蔽单元14n中,P型晶体管P31n、P41n的基极连接于第一系统电压VDDDn,且P型晶体管P31n、P41n的栅极连接于第三系统电压VBPn;N型晶体管N51n、N61n的基极连接于第二系统电压VSNn,且N型晶体管N51n、N61的栅极连接于第四系统电压VBNn。每个系统电压VDDD1~VDDDn皆不同,每个系统电压VBP1~VBPn皆不同,每个系统电压VBN1~VBNn皆不同,且每个系统电压VSN1~VSNn皆不同。

关于电流镜16的电路架构,第一N型晶体管N1的源极及基极耦接于第二系统电压VSN,第一N型晶体管N1的栅极及漏极耦接于第三N型晶体管N3的源极。第二N型晶体管N2的源极及基极耦接于第二系统电压VSN,第二N型晶体管N2的栅极耦接于第一N型晶体管N1的栅极,且第二N型晶体管N2的漏极耦接于第四N型晶体管N4的源极。第三N型晶体管N3包含源极耦接于漏极以及的栅极第一N型晶体管N1以及的栅极第二N型晶体管N2,一栅极耦接于一栅极以及一的漏极第四N型晶体管N4,一基极耦接于第二系统电压VSN,以及一漏极耦接于一的源极第五N型晶体管N5。第四N型晶体管N4包含源极耦接于第二N型晶体管N2的漏极,栅极以及漏极耦接于栅极第三N型晶体管N3的。

关于电流镜16的操作方式,当第二电流I2比第一电流I1大许多(I2>>I1)时,电流镜16的操作相当于传统电流镜;然而当第二电流I2比第一电流小许多(I2<

关于第二遮蔽电路17的电路架构与操作方式,第五P型晶体管P5的源极耦接于第四P型晶体管P4的漏极,第五P型晶体管P5的基极耦接于第一系统电压VDDD,第五P型晶体管P5的栅极及漏极耦接于第七P型晶体管P7的栅极。当第五P型晶体管P5的源极电压大于第一中继信号NI_1加上第五P型晶体管P5的阈值电压的总和(意即,Vz>VNI_1+VTH。P5)且第一中继信号NI_1等于第五P型晶体管P5的源极电压减去第五P型晶体管P5的阈值电压的差值(意即,VNI_1=Vz-VTH。P5)时,第五P型晶体管P5可被导通。当第五P型晶体管P5的源极电压小于第一中继信号NI_1加上第五P型晶体管P5的阈值电压的总和(意即,VS。P5

关于切换电路18的电路架构与操作方式,第六P型晶体管P6的源极耦接于第四N型晶体管N4的源极及第二N型晶体管N2的漏极,第六P型晶体管P6的栅极耦接于第二系统电压VSN,第六P型晶体管P6的基极耦接于第五系统电压VSSA,且第六P型晶体管P6的漏极耦接于第八N型晶体管N8的漏极。第八N型晶体管N8的源极及基极耦接于第二系统电压VSN,第八N型晶体管N8的栅极耦接于节点ND1,且第八N型晶体管N8的漏极耦接于第六P型晶体管P6的漏极。

当第一输入逻辑信号NNB为逻辑“0”状态(VNNB=VSSD,VSSD可以是一接地电压)且第二输入逻辑信号NN为逻辑“1”状态(VNN=VDDD)时,第三操作电压Vx等于第二系统电压VSN加上第一N型晶体管N1的阈值电压的总和(Vx=VSN+VTH。N1)且第二操作电压Vy等于第二系统电压VSN加上第二N型晶体管N2的阈值电压的总和(Vy=VSN+VTH。N2),此时由于第六P型晶体管P6的基极效应(Body effect)使得第六P型晶体管P6的阈值电压高过第二N型晶体管N2的绝对阈值电压(意即,|VTH。P6|>VTH。N2),让第二操作电压Vy过高以致于不能导通第六P型晶体管P6。进一步地,节点ND1的电压大小足够来导通第八N型晶体管N8,使得第二中继信号NI_2的大小被拉到第二系统电压VSN。

当第一输入逻辑信号NNB为逻辑“1”状态(VNNB=VDDD)且第二输入逻辑信号NN为逻辑“0”状态(VNN=VSSD)时,第八N型晶体管N8被关闭,此时因为第六P型晶体管P6的源极对栅极电压大于第六P型晶体管P6的绝对阈值电压(意即,VSG。P6=Vy-VSN>|VTH。P6|),故第六P型晶体管P6被导通。进一步地,第二中继信号NI_2的大小转为第四系统电压VBN减去N型晶体管N6、N5的阈值电压(意即,VNI_2=VBN–VTH。N6–VTH。N4)。在一实施例中,第六P型晶体管P6的源极不限于连接到第二操作电压Vy,本领域具通常知识者可根据电压需求,将第六P型晶体管P6的源极连接到经过第二电流I2的电流路径中的任意节点。

当第三N型晶体管N3的漏极电压弱导通或是弱关闭第八N型晶体管N8时,第八N型晶体管N8用来根据第三N型晶体管N3的漏极电压(其中节点ND1耦接于第三N型晶体管N3的漏极)来形成电流路径给第二中继信号NI_2,让第二中继信号NI_2的电流经过第八N型晶体管N8而回流到第二系统电压VSN,如此可避免第九N型晶体管N9的漏电流。

推拉级电路12包含第七P型晶体管P7、第八P型晶体管P8、第九P型晶体管P9、第九N型晶体管N9、第十N型晶体管N10以及第十一N型晶体管N11。第七P型晶体管P7的源极及基极耦接于第五系统电压VSSA,第七P型晶体管P7的栅极耦接于第五P型晶体管P5的漏极与第七N型晶体管N7的源极,且第七P型晶体管P7的漏极耦接于第八P型晶体管P8的源极。第八P型晶体管P8的源极耦接于第九N型晶体管N9的漏极,第八P型晶体管P8的基极耦接于第五系统电压VSSA,第八P型晶体管P8的栅极耦接于第二系统电压VSN,且第八P型晶体管P8的漏极耦接于第九N型晶体管N9的漏极。第九N型晶体管N9的漏极耦接于第八P型晶体管P8的漏极,用来输出第一输出信号NN_OUT,第九N型晶体管N9的基极耦接于第二系统电压VSN,第九N型晶体管N9的栅极耦接于第六P型晶体管P6的漏极与第八N型晶体管N8的漏极。第九P型晶体管P9的源极及基极耦接于第五系统电压VSSA,第九P型晶体管P9的栅极耦接于第八P型晶体管P8的漏极,且第九P型晶体管P9的漏极耦接于第十N型晶体管N10的漏极。第十N型晶体管N10的漏极耦接于第九P型晶体管P9的漏极,用来输出第二输出信号NN_OUTB,第十N型晶体管N10的基极耦接于第二系统电压VSN,第十N型晶体管N10的栅极耦接于第九P型晶体管P9的栅极,且第十N型晶体管N10的源极耦接于第十一N型晶体管N11的漏极。第十一N型晶体管N11的漏极耦接于第十N型晶体管N10的源极,第十一N型晶体管N11的基极及源极耦接于第二系统电压VSN,且第十一N型晶体管N11的栅极耦接于第九P型晶体管P9的栅极。

在一实施例中,考虑到电路面积最小化的需求,P型晶体管P1、P2、P3、P4、P5可以是N阱(n-well)P型晶体管并共享相同的电源领域,其中晶体管P1、P2、P3、P4、P5的基极连接于相同的第一系统电压VDDD。P型晶体管P6、P7、P8、P9可以是N阱P型晶体管并共享相同的电源领域,其中晶体管P6、P7、P8、P9的基极连接于相同的第五系统电压VSSA。共享相同电源领域的N阱P型晶体管可紧密地配置在邻近区域,以充分利用负电位转换器1的电路面积并提升电源效率。在另一实施例中,考虑到电路设计弹性的需求,P型晶体管P1、P2、P3、P4、P5可使用不同电源领域。举例来说,P型晶体管P3、P4、P5的基极可连接于不同系统电压来控制其基极对栅极电压,以适用于不同应用需求。在一实施例中,系统电压VBP、VBN、VSSA为相同电压。

简言之,在图1A及图1B的负电位转换器1,本发明使用第一电压遮蔽电路14来释放施加到比较器13的晶体管的电压应力以及释放施加到输入级电路11的电流镜16的电压应力。本发明还使用具有电流路径的切换电路18来避免第二中继信号NI_2的漏电流。除此之外,设计负电位转换器1的N阱P型晶体管的电源领域,可充分利用负电位转换器1的电路面积、提升电源效率、增加设计弹性以适用各种应用需求。

图2为本发明实施例负电位转换器2的示意图。负电位转换器1、2的电路结构相似,其中相同组件使用相同标号。负电位转换器2包含输入级电路21及推拉级电路12。输入级电路21包含比较器13、第一遮蔽电路14、电流镜16、第二遮蔽电路27及切换电路18。

第二遮蔽电路27耦接于第一遮蔽电路14,并包含P型晶体管P21。P型晶体管P21的源极耦接于第一遮蔽电路14的第四P型晶体管P4,P型晶体管P21的基极耦接于第一系统电压VDDD,P型晶体管P21的栅极及漏极耦接于第一遮蔽电路14的第六N型晶体管N6的漏极。P型晶体管P21的栅极及漏极用来输出第一中继信号NI_1。P型晶体管P21可以是N阱(N-well)P型晶体管,并与P型晶体管P1、P2、P3、P4共享相同的电源领域(例如,第一系统电压VDDD)。

图3为本发明实施例负电位转换器3的示意图。负电位转换器1、3的电路结构相似,其中相同组件以相同标号表示。负电位转换器3包含输入级电路31及推拉级电路12。输入级电路31包含比较器13、第一遮蔽电路34、电流镜16、第二遮蔽电路27以及切换电路18。

第一遮蔽电路34耦接于比较器13及电流镜16,并包含P型晶体管P3、P4、P32、P33。P型晶体管P32的源极耦接于第三P型晶体管P3的漏极,P型晶体管P32的基极耦接于第一系统电压VDDD,P型晶体管P32的栅极及漏极耦接于P型晶体管P33的源极。P型晶体管P33的源极耦接于P型晶体管P32的栅极及漏极,P型晶体管P33的基极耦接于第一系统电压VDDD,P型晶体管P33的栅极及漏极耦接于第五N型晶体管N5的漏极。当第一输入逻辑信号NNB为逻辑“0”状态(VNNB=VSSD)且第二输入逻辑信号NN为逻辑“1”状态(VNN=VDDD)时,第一电流I1比第二电流I2大许多;此时,第五N型晶体管N5的漏极电压小于第一系统电压VDDD减去晶体管P3、P32、P33的绝对阈值电压与第三系统电压VBP的差值(意即,VD。N5 P型晶体管P21、P32、P33可以是N-阱P型晶体管并与P型晶体管P1、P2、P3、P4共享相同的电源领域(例如,第一系统电压VDDD),但不限于此。 图4为本发明实施例负电位转换器4的示意图。负电位转换器1、4的电路结构相似,其中相同组件使用相同标号。负电位转换器4包含输入级电路41以及推拉级电路12。输入级电路41包含比较器13、第一遮蔽电路34、电流镜16、第二遮蔽电路47以及切换电路18。 第二遮蔽电路47耦接于第一遮蔽电路14,并包含P型晶体管P21、P44。P型晶体管P44的源极耦接于P型晶体管P21的漏极及栅极,P型晶体管P44的基极耦接于第一系统电压VDDD,P型晶体管P44的栅极及漏极耦接于第一遮蔽电路14的第六N型晶体管N6的漏极。第二遮蔽电路47用来降低第六N型晶体管N6的基极对漏极电压。 图5A为本发明实施例正电位转换器5的示意图。正电位转换器5是根据图1A的负电位转换器1的电路架构进行设计。正电位转换器5包含输入级电路51以及推拉级电路52。 输入级电路51用来根据第一输入逻辑信号INB及第二输入逻辑信号IN,产生第一中继信号PI_1及第二中继信号PI_2,其中第一中继信号PI_1及第二中继信号PI_2的第一电压摆幅介于第一系统电压VDDA与第二电压VSSA之间,且第二输入逻辑信号IN是第一输入逻辑信号INB的反相(reverse-phase)信号。输入级电路51包含比较器53、遮蔽电路54、电流镜56以及切换电路58。 比较器53包含第一N型晶体管N51以及第二N型晶体管N52。遮蔽电路54耦接于比较器53,用来产生第一中继信号PI_1,其中遮蔽电路54包含第三P型晶体管P53以及第四P型晶体管P54。电流镜56耦接于遮蔽电路54,并包含第一P型晶体管P51、第二P型晶体管P52、第三P型晶体管P53以及第四P型晶体管P54。切换电路58耦接于电流镜56,用来根据第二操作电压Vm,产生第二中继信号PI_2,其中切换电路58包含第五P型晶体管P55以及第五N型晶体管N55。 关于比较器53的电路架构,第一N型晶体管N51的源极及基极耦接于第二系统电压VSSA,第一N型晶体管N51的栅极耦接于第二输入逻辑信号IN,且第一N型晶体管N51的漏极耦接于第三N型晶体管N53的源极。第二N型晶体管N52的源极及基极耦接于第二系统电压VSSA,第二N型晶体管N52的栅极耦接于第一输入逻辑信号INB,且第二N型晶体管N52的漏极耦接于第四P型晶体管P54的源极。第一N型晶体管N51及第二N型晶体管N52用来比较第一输入逻辑信号INB与第二输入逻辑信号IN,以分别产生第一电流I51及第二电流I52。当输入逻辑信号IN为逻辑“0”状态且反相输入逻辑信号INB为逻辑“1”状态时,第二电流I52比第一电流I51大许多(I52>>I51)。反之,当输入逻辑信号IN为逻辑“1”状态且反相输入逻辑信号INB为逻辑“0”状态时,第一电流I51比第一电流大许多I52(I51>>I52)。 关于遮蔽电路54的电路架构,第三N型晶体管N53的源极耦接于第一N型晶体管N51的漏极,第三N型晶体管N53的基极耦接于第二系统电压VSSA,第三N型晶体管N53的栅极耦接于第三系统电压VBIAS,且第三N型晶体管N53的漏极耦接于第三P型晶体管P53的漏极及栅极与第四P型晶体管P54的栅极。第四N型晶体管N54的源极耦接于第二N型晶体管N52的漏极,第四N型晶体管N54的基极耦接于第二系统电压VSSA,第四N型晶体管N54的栅极耦接于第三系统电压VBIAS,且第四N型晶体管N54的漏极耦接于第四P型晶体管P54的漏极。当晶体管N51、P51、P53被导通时,第一N型晶体管N51的漏极电压(VD。N51)等于第三系统电压VBIAS减去第三N型晶体管N53的绝对阈值电压的差值(意即,VBIAS-|VTH。N53|)。通过控制第三系统电压VBIAS的电压位准,可确保第一N型晶体管N51的总体(overall)电压小于其可承受的最大耐压。相似地,当晶体管N52、P52、P54被导通时,第二N型晶体管N52的漏极电压(VD。N52)等于第三系统电压VBIAS减去第四N型晶体管N54的绝对阈值电压的差值(意即,VBIAS-|VTH。N54|)。通过控制第三系统电压VBIAS的电压位准,可确保第二N型晶体管N52的总体电压小于其可承受的最大耐压。 请注意,第一N型晶体管N51及第二N型晶体管N52可以是低电压装置,晶体管N51、N52的源极对漏极(或是基极对漏极)电压应不大于其可承受的最大耐压。举例来说,晶体管N51、N52的源极对漏极电压应小于或等于第一系统电压VDDD(VSD。N51= 关于电流镜56的电路架构,第一P型晶体管P51的源极及基极耦接于第一系统电压VDDA,第一P型晶体管P51的栅极耦接于第二P型晶体管P52的栅极及漏极。第二P型晶体管P52的源极及基极耦接于第一系统电压VDDA,第二P型晶体管P52的栅极及漏极耦接于第一P型晶体管P51的栅极。第三P型晶体管P53的源极耦接于第一P型晶体管P51的漏极,第三P型晶体管P53的栅极及漏极耦接于第三N型晶体管N53的漏极与第四P型晶体管P54的栅极,第三N型晶体管N53的基极耦接于第一系统电压VDDA。第四P型晶体管P54的源极耦接于第二P型晶体管P52的漏极及栅极与第一P型晶体管P51的栅极,第四P型晶体管P54的栅极耦接于第三P型晶体管P53的栅极及漏极与第三N型晶体管N53的漏极,第四P型晶体管P54的基极耦接于第一系统电压VDDA,且第四P型晶体管P54的漏极耦接于第四N型晶体管N54的漏极。电流镜56可具有威尔森(Wilson)电流镜结构。 关于切换电路58的电路架构,第五N型晶体管N55的源极耦接于第三P型晶体管P53的源极与第一P型晶体管P51的漏极,第五N型晶体管N55的栅极耦接于第一系统电压VDDA,第五N型晶体管N55的基极耦接于第二系统电压VSSA,且第五N型晶体管N55的漏极耦接于第五P型晶体管P55的漏极。当第一P型晶体管P51的漏极电压小于第一系统电压VDDA减去第一P型晶体管P55的阈值电压的差值(意即,VD。P51 当第一输入逻辑信号INB为逻辑“0”状态(VINB=VSSD)且第二输入逻辑信号IN为逻辑“1”状态(VIN=VDDD)时,第一电流I51比第二电流I52大许多(I51>>I52),以将第一中继信号PI_1及第二中继信号PI_2拉低到第二系统电压VSSA,此时节点ND5的电压近似于第一系统电压VDDA。第二中继信号PI_2(PI_2=Vm)导通第六P型晶体管P56,且节点ND5的电压关闭第五P型晶体管P55。在此情况下,第一输出信号OUT等于第一系统电压VDDA(OUT=VDDA),且第二输出信号OUTB等于第二系统电压VSSA(OUTB=VSSA)。 当第一输入逻辑信号INB为逻辑“1”状态(VINB=VDDD)且第二输入逻辑信号IN为逻辑“1”状态(VIN=VSSD)时,第二电流I52比第一电流I51大许多(I52>>I51),以将第一中继信号PI_1及第二中继信号PI_2拉升到第一系统电压VDDA,此时节点ND5的电压近似于第二系统电压VSSA。节点ND5的电压关闭第五P型晶体管P55以将第二中继信号PI_2拉升到第一系统电压VDDA,且第二中继信号PI_2关闭第六P型晶体管P56。第一中继信号PI_1耦接于第一反向器521,在此情况下,第一输出信号OUT等于第二系统电压VSSA(OUT=VSSA),且第二输出信号OUTB等于第一系统电压VSSA(OUTB=VDDA)。 当第四P型晶体管P54的源极电压弱导通或是弱关闭第五P型晶体管P55时,第五P型晶体管P55用来根据第四P型晶体管P54的源极电压(其中节点ND5耦接于第四P型晶体管P54的源极)来形成电流路径给第二中继信号PI_2,让第二中继信号PI_2电流可经过第五P型晶体管P55来回流到第一系统电压VDDA,如此可避免第六P型晶体管P56的漏电流。 推拉级电路52耦接于输入级电路51,用来根据第一中继信号PI_1及第二中继信号PI_2,产生第一输出信号OUT及第二输出信号OUTB,其中第一输出信号OUT及第二输出信号OUTB的第一电压摆幅介于第一系统电压VDDA与第二系统电压VSSA之间。 推拉级电路52包含第六P型晶体管P56、第一反向器521以及第二反向器522。图5B为本发明实施例正电位转换器5的示意图。在图5B中,第一反向器521包含第六N型晶体管N56以及第七N型晶体管;且第二反向器522包含第七P型晶体管P57、第八N型晶体管N58以及第九N型晶体管N59。第一反向器521用来根据第六N型晶体管N56控制的偏压电流,将第一中继信号PI_1转换为第一输出信号OUT。第二反向器522用来将第一输出信号OUT转换为第二输出信号OUTB。 第六P型晶体管P56可视为可变电阻,第六P型晶体管P56的源极及基极耦接于第一系统电压VDDA,第六P型晶体管P56的栅极耦接于晶体管P55、N55的漏极,且第六P型晶体管P56的漏极耦接于第七N型晶体管N57的漏极与晶体管P57、N58、N59的栅极。第六N型晶体管N56的源极及基极耦接于第二系统电压VSSA,第六N型晶体管N56的栅极耦接于遮蔽电路54的第三N型晶体管N53的漏极,且第六N型晶体管N56的漏极耦接于第七N型晶体管N57的源极。第七N型晶体管N57的源极耦接于第六N型晶体管N56的漏极,第七N型晶体管N57的基极耦接于第二系统电压VSSA,第七N型晶体管N57的栅极耦接于遮蔽电路54的第三N型晶体管N53的漏极,且第七N型晶体管N57的漏极耦接于第六P型晶体管P56的漏极。第六P型晶体管P56以及第七N型晶体管N57可视为一反向器,用来产生第一输出信号OUT。第六N型晶体管N56以及第七N型晶体管N57用来降低在晶体管的切换操作中产生的浪涌电流(inrushcurrent)的大小。 第七P型晶体管P57的源极及基极耦接于第一系统电压VDDA,第七P型晶体管P57的栅极耦接于晶体管P56、N57的漏极,且第七P型晶体管P57的漏极耦接于第九N型晶体管N59的漏极。第八N型晶体管N58的源极及基极耦接于第二系统电压VSSA,第八N型晶体管N58的栅极耦接于第七P型晶体管P57的栅极,且第八N型晶体管N58的漏极耦接于第九N型晶体管N59。第九N型晶体管N59的源极耦接于第八N型晶体管N58的漏极,第九N型晶体管N59的基极耦接于第二系统电压VSSA,第九N型晶体管N59的栅极耦接于晶体管P57、N58的栅极,且第九N型晶体管N59的漏极耦接于第七P型晶体管P57的漏极。请注意,晶体管P56、N57的漏极用来输出第一输出信号OUT,且晶体管P57、N59的漏极用来输出第二输出信号OUTB。第七P型晶体管P57、第八N型晶体管N58以及第九N型晶体管N59可视为反向器,用来反相第一输出信号OUT来产生第二输出信号OUTB。第八N型晶体管N58及第九N型晶体管N59用来降低在晶体管的切换操作中产生的浪涌电流的大小。 简言之,在图5A及图5B的正电位转换器5中,本发明使用电压遮蔽电路54来释放施加到输入级电路53的晶体管的电压应力。本发明还使用具有电流路径的切换电路58来避免第六P型晶体管P56的漏电流。 综上所述,本发明提供了适用于正电压及负电压转换的电位转换器架构,其中电位转换器的遮蔽电路用来释放施加到输入级电路的晶体管的电压应力,且电位转换器的切换电路用来避免漏电流。除此之外,本发明通过设计电位转换器的N阱P型晶体管的电源领域,可充分利用电位转换器的电路面积、提升电源效率、增加设计弹性以适用各种应用需求。 以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,皆应属本发明的涵盖范围。

- 可释放电压应力的电位转换器

- 直接引出顶阶电位而计算次级输入电压的多级并行式模数转换器