一种基于P型氮化物隔离的P-GaN晶体管及其制备方法

文献发布时间:2024-04-18 19:44:28

技术领域

本申请实施例涉及半导体器件技术领域,特别涉及一种基于P型氮化物隔离的P-GaN晶体管及其制备方法。

背景技术

氮化镓(GaN)作为第三代半导体材料的代表,相比硅或砷化镓,具有更宽的禁带宽度,更高的临界击穿场强,在高频、大功率的领域展现出独特的优势。GaN基高电子迁移率晶体管(High Electron Mobility Transistor,HEMT)可由异质结构产生高浓度和迁移率的二维电子气(2DEG),可实现高耐压大电流的功率器件,并在抗单粒子效应中展示出出色的能力。

制作高质量的器件需要减小器件之间的漏电,杜绝器件之间的相互影响,因此需要实现器件之间良好的电隔离。目前基于各种衬底的外延片制备GaN分立器件主要有两种隔离方式,一种是利用刻蚀工艺形成台面,另一种利用离子注入工艺形成高阻区域,将器件有源区外二维电子气阻断,AlGaN/GaN HEMT器件制作在未注入离子的隔离岛上,隔离岛之间彼此电隔离,使器件之间独立工作。

然而,现有的隔离方式存在如下问题:如图1所示,台面刻蚀是通过在器件之间刻蚀出深度远远大于沟道的沟槽,实现器件间导电通道的阻断,来形成隔离区。但是,台面刻蚀的侧壁可能导致漏电流增加、击穿电压降低;台阶过深会导致金属容易断裂等。如图2所示,离子注入隔离是通过离子注入来补偿半导体中的自由电子和空穴,形成半绝缘的高阻层,作为器件的隔离。但是,离子注入会引入晶格损伤,增大泄漏电流。

发明内容

本申请实施例提供一种基于P型氮化物隔离的P-GaN晶体管及其制备方法,采用隔离层与沟道层形成pn结,耗尽沟道层中的二维电子气,阻断器件间的相互作用形成隔离。也可注入小剂量的Mg或其它离子,从而增加空穴浓度,增加pn型耗尽区深度,加强隔离效果。同时,本申请取消了常规P-GaN器件的台面刻蚀工艺,不仅减小了刻蚀损伤,还降低了成本;有望降低泄漏电流,提高器件的击穿电压。

为解决上述技术问题,本申请实施例提供一种基于P型氮化物隔离的P-GaN晶体管,包括:衬底以及依次堆叠在衬底上的成核层、缓冲层、沟道层和势垒层;位于势垒层上的源极和漏极,且源极和漏极分别与势垒层形成欧姆接触;位于势垒层上的隔离层、氮化物层以及钝化层,钝化层位于源极和氮化物层之间、氮化物层与漏极之间;隔离层与沟道层形成pn结,用于耗尽沟道层中的二维电子气,形成器件之间的隔离;位于氮化物层上的栅极,栅极的底部与氮化物层形成欧姆接触或肖特基接触。

在一些示例性实施例中,隔离层的材料与氮化物层的材料相同。

在一些示例性实施例中,隔离层的材料包括掺杂的P型氮化物。

在一些示例性实施例中,掺杂的P型氮化物包括掺杂的P型氮化镓、P型氮化铝、P型铝镓氮中的一种或几种。

在一些示例性实施例中,氮化物层的材料包括掺杂的P型氮化镓、P型氮化铝、P型铝镓氮中的一种或几种。

在一些示例性实施例中,隔离层的掺杂浓度与所述氮化物层的掺杂浓度相同。

在一些示例性实施例中,沿势垒层指向氮化物层的方向,隔离层的高度与氮化物层的高度相同。

在一些示例性实施例中,上述基于P型氮化物隔离的P-GaN晶体管还包括:用于提高载流子迁移率的插入层,插入层位于势垒层与沟道层之间。

另一方面,本申请实施例还提供了一种基于P型氮化物隔离的P-GaN晶体管的制备方法的制备方法,包括以下步骤:首先,提供衬底,在衬底上形成依次堆叠的成核层、缓冲层、沟道层和势垒层;然后,在势垒层远离沟道层的一侧形成氮化物材料层,得到外延片;接下来,刻蚀氮化物材料层,形成氮化物层和隔离层,并露出势垒层;隔离层与沟道层形成pn结,用于耗尽沟道层中的二维电子气,形成器件之间的隔离;在势垒层上制作掩膜,形成欧姆窗口,以形成源极、漏极;在势垒层和氮化物层上制作掩膜,形成栅极窗口,以形成栅极;在势垒层、源极、漏极、栅极以及隔离层的上方形成钝化材料层;最后,在源极、漏极、栅极上方的钝化材料层上开孔,引出电极,得到晶体管。

一些示例性实施例中,氮化物层和隔离层同时制作,且隔离层的材料与氮化物层的材料相同。

本申请实施例提供的技术方案至少具有以下优点:

本申请实施例采用一种新型GaN器件隔离方法,提供一种基于P型氮化物隔离的P-GaN晶体管及其制备方法,该晶体管包括:衬底、成核层、缓冲层、沟道层、势垒层、位于势垒层上的源极和漏极、位于势垒层上的隔离层、氮化物层以及钝化层以及位于氮化物层上的栅极;源极和漏极分别与势垒层形成欧姆接触,钝化层位于源极和氮化物层之间、氮化物层与漏极之间;隔离层与沟道层形成pn结,用于耗尽沟道层中的二维电子气,形成器件之间的隔离;栅极的底部与氮化物层形成欧姆接触或肖特基接触。

本申请提供一种基于P型氮化物隔离的P-GaN晶体管及其制备方法,其目的在于提出一种新型GaN器件隔离方法,采用P型GaN或其他氮化物材料形成隔离层,使隔离层与沟道层形成pn结,可耗尽沟道层中由极化效应产生的二维电子气,阻断器件间的相互干扰作用,以形成器件之间的有效隔离,也可注入小剂量的Mg或其它离子,加强隔离效果。本申请取消了常规P-GaN器件的台面刻蚀工艺,不仅减小了刻蚀损伤,还降低了成本。与此同时,本申请制得的P-GaN栅HEMT不仅可以保持增强型的特性,还可以减小刻蚀与注入损伤,从而降低泄漏电流,提高器件的击穿电压。

附图说明

一个或多个实施例通过与之对应的附图中的图片进行示例性说明,这些示例性说明并不构成对实施例的限定,除非有特别申明,附图中的图不构成比例限制。

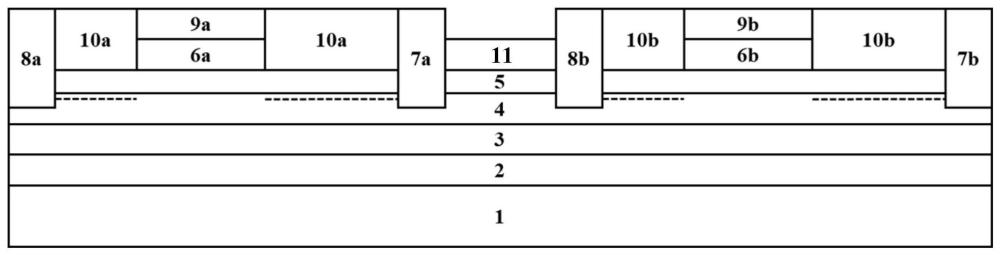

图1为现有技术中一种台面刻蚀隔离的P-GaN栅高电子迁移率晶体管的结构示意图;

图2为现有技术中一种离子注入隔离的P-GaN栅高电子迁移率晶体管的结构示意图;

图3为本申请一实施例提供的一种基于P型氮化物隔离的P-GaN晶体管的结构示意图;

图4为本申请一实施例提供的一种基于P型氮化物隔离的P-GaN晶体管的俯视图;

图5为本申请一实施例提供的一种基于P型氮化物隔离的P-GaN晶体管的制备方法的流程示意图;

图6为本申请一实施例提供的基于P型氮化物隔离的P-GaN晶体管的仿真图;

图7为本申请一实施例提供的基于P型氮化物隔离的P-GaN晶体管的放大图。

具体实施方式

由背景技术可知,现有的器件隔离方式包括台面刻蚀隔离和离子注入隔离,两种隔离方式均存在着一些问题,比如台面刻蚀的侧壁可能导致漏电流增加、击穿电压降低;台阶过深会导致金属容易断裂等;而离子注入隔离时,离子注入会引入晶格损伤,增大泄漏电流。

图1示出了一种台面刻蚀隔离的P-GaN栅高电子迁移率晶体管的结构示意图。该器件为常规结构的基于AlGaN/GaN异质结构的P型氮化物栅HEMT,参考图1,常规结构的高电子迁移率晶体管包括衬底1、成核层2、缓冲层3、沟道层4、势垒层5、源极7、漏极8和氮化物层6,氮化物层6位于源极7和漏极8之间,氮化物层6两侧均设有钝化层10,氮化物层6的上方设有栅极9,钝化层10填充在源极7和氮化物层6之间的区域,以及钝化层10还填充在氮化物层6和漏极8之间的区域。其中,两个器件的沟道层4分别用4a、4b表示,两个器件的势垒层5分别用5a、5b表示,两个器件的氮化物层6分别用6a、6b表示,两个器件的源极7、漏极8分别用7a和7b、8a和8b表示;两个器件的栅极9、钝化层10分别用9a和9b、10a和10b表示。从图1可以看出,在两个器件之间通过刻蚀沟槽实现器件之间的隔离;其中,刻蚀沟槽的深度远远大于器件的沟道深度,来实现器件间导电通道的阻断,来形成隔离区。但是,台面刻蚀的侧壁存在着可能导致漏电流增加、击穿电压降低的问题,以及存在着台阶过深会导致金属容易断裂的问题。

图2示出了一种离子注入隔离的P-GaN栅高电子迁移率晶体管的结构示意图;与图1中隔离方式不同的是,图2是在两个器件之间通过在离子注入区内进行离子注入,通过离子注入来补偿半导体中的自由电子和空穴,形成半绝缘的高阻层,作为器件的隔离。但是,该隔离方式存在着会引入晶格损伤,增大泄漏电流的技术问题。

为解决上述技术问题,本申请实施例提供一种基于P型氮化物隔离的P-GaN晶体管及其制备方法,该晶体管包括:衬底以及依次堆叠在衬底上的成核层、缓冲层、沟道层和势垒层;位于势垒层上的源极和漏极,且源极和漏极分别与势垒层形成欧姆接触;位于势垒层上的隔离层、氮化物层以及钝化层,钝化层位于源极和氮化物层之间、氮化物层与漏极之间;隔离层与沟道层形成pn结,用于耗尽沟道层中的二维电子气,形成器件之间的隔离;位于氮化物层上的栅极,栅极的底部与氮化物层形成欧姆接触或肖特基接触。本申请实施例提供一种基于P型氮化物隔离的P-GaN晶体管及其制备方法,采用隔离层与沟道层形成pn结,耗尽沟道层中的二维电子气,阻断器件间的相互作用形成隔离。也可注入小剂量的Mg或其它离子,从而增加空穴浓度,增加pn型耗尽区深度,加强隔离效果。同时,本申请取消了常规P-GaN器件的台面刻蚀工艺,不仅减小了刻蚀损伤,还降低了成本;有望降低泄漏电流,提高器件的击穿电压。

下面将结合附图对本申请的各实施例进行详细的阐述。然而,本领域的普通技术人员可以理解,在本申请各实施例中,为了使读者更好地理解本申请而提出了许多技术细节。但是,即使没有这些技术细节和基于以下各实施例的种种变化和修改,也可以实现本申请所要求保护的技术方案。

参考图3,本申请实施例提供一种基于P型氮化物隔离的P-GaN晶体管及其制备方法,包括:衬底1以及依次堆叠在衬底1上的成核层2、缓冲层3、沟道层4和势垒层5,以及位于势垒层5上的源极7和漏极8、位于势垒层5上的隔离层11、氮化物层8以及钝化层10以及位于氮化物层6上的栅极9。其中,源极7和漏极8分别与势垒层5形成欧姆接触;氮化物层6位于源极7和漏极8之间,钝化层10位于源极7和氮化物层6之间、氮化物层6和漏极8之间;隔离层11与沟道层4形成pn结,用于耗尽沟道层4中的二维电子气,形成器件之间的隔离;栅极9的底部与氮化物层6形成欧姆接触或肖特基接触。

需要说明的是,两个器件的沟道层4、势垒层5、氮化物层6、源极7、漏极8、栅极9、钝化层10分别用4a和4b、5a和5b、6a和6b、7a和7b、8a和8b、9a和9b、10a和10b表示。

本申请实施例提供的基于P型GaN(氮化镓)栅HEMT(高电子迁移率晶体管)器件可用于电力电子系统的功率开关、功率转换电路中GaN器件的隔离。本申请针对现有的器件隔离方式存在的技术问题,提供一种基于P型氮化物隔离的P-GaN晶体管及其制备方法。本申请利用隔离层(P-GaN)隔离的P-GaN栅HEMT是在器件有源区设计并制作常规器件,但在器件之间的P-GaN进行保留,不采用刻蚀和离子注入工艺进行隔离,而是利用P-GaN耗尽沟道层的二维电子气,形成pn结而起到隔离作用。总体俯视图如图4所示,各器件之间由P-GaN进行隔离。

本申请提供一种新型的隔离方式,采用隔离层11与沟道层4形成pn结,耗尽沟道层4中的二维电子气,阻断器件间的相互作用形成隔离。同时,本申请取消了常规P-GaN器件的台面刻蚀工艺,不仅减小了刻蚀损伤,还降低了成本;有望降低泄漏电流,提高器件的击穿电压。

在一些实施例中,隔离层11的材料与氮化物层6的材料相同。

需要说明的是,为了节省工艺以及提高工艺上的便利性,隔离层11可以与氮化物层6同时制作的,因此隔离层11的材料可以与氮化物层6的材料相同。

在一些实施例中,氮化物层6的材料包括掺杂的P型氮化物、P型氧化物中的一种或几种。在隔离层11的材料与氮化物层6的材料相同时,隔离层11的材料包括掺杂的P型氮化物中的一种或几种。

在一些实施例中,氮化物层6的材料包括P型氮化镓(P-GaN)、P型氮化铝(P-AlN)、P型铝镓氮(P-AlGaN)中的一种或几种。优选的,氮化物层6的材料为P型GaN,通常,氮化物层6的材料采用掺Mg的P型GaN材料。

在一些实施例中,隔离层11的材料包括P型氮化镓(P-GaN)、P型氮化铝(P-AlN)、P型铝镓氮(P-AlGaN)中的一种或几种。优选的,隔离层11的材料与氮化物层6的材料相同,且隔离层11的离子掺杂浓度与氮化物层6的离子掺杂浓度相同,隔离层11的材料为P型GaN,通常,隔离层11的材料采用掺Mg的P型GaN材料。

当然,可以理解的是,隔离层11也可以为与氮化物层6材料不同的氮化物,也可以单独设计其他材料制作隔离层11,以使隔离层11与沟道层4形成pn结,使其能够耗尽沟道层4中的二维电子气,形成器件之间的隔离。

在一些实施例中,隔离层11的掺杂浓度与氮化物层6的掺杂浓度相同。

在一些实施例中,沿势垒层5指向氮化物层6的方向,隔离层11的高度与氮化物层6的高度相同。

需要说明的是,由于隔离层11可以与氮化物层6同时制作,因此隔离层11的材料、掺杂浓度、高度(厚度)可以与氮化物层6的材料、掺杂浓度、高度(厚度)相同。当然,可以理解的是,隔离层11的材料、掺杂浓度、高度(厚度)也可以与氮化物层6的材料、掺杂浓度、高度(厚度)不同。

在一些实施例中,沿源极7指向漏极8的方向,隔离层11的长度等于相邻器件之间的间距。示例的,隔离层11的长度为100nm~500μm。隔离层11的高度可以氮化物层6的高度相等,也可以不相等。需要说明的是,隔离层11的长度以及高度均可以实际设计需要进行适应性调整。

在一些实施例中,上述基于P型氮化物隔离的P-GaN晶体管及其制备方法,还包括:插入层,插入层位于的沟道层4与势垒层5之间。插入层用于提高载流子迁移率,插入层的材料包括但不限于AlN、InAlN、AlGaN。

在一些实施例中,衬底1的材料包括蓝宝石、碳化硅(SiC)、硅(Si)、氮化镓中的一种。令衬底1下表面指向衬底1上表面的方向为厚度方向,衬底1的厚度为100nm~1000μm。需要说明的是,本申请以下实施例中所述的厚度均是指在该厚度方向上,各个膜层的厚度。

在一些实施例中,成核层2的材料包括氮化镓、氮化铝、铝镓氮(AlGaN)中的一种。优选的,成核层2的材料为氮化铝。成核层2的厚度分别为300nm~500nm。

在一些实施例中,缓冲层3的材料包括氮化镓、氮化铝、铝镓氮中的一种或几种。缓冲层3的厚度为0.5μm~5μm。

在一些实施例中,沟道层4的材料包括氮化镓、铝镓氮中的一种。优选的,缓冲层3和沟道层4的材料均为氮化镓。沟道层4的厚度为50nm~500nm。

在一些实施例中,势垒层5的材料为纤锌矿结构的AlGaN,具体的,势垒层5的材料为Al

在一些实施例中,源极7和漏极8可以采用Ti/Al/Ni/Au或者Ti/Al/Pt/Au的金属组合,以使源极7和漏极8分别与势垒层5形成欧姆接触。

在一些实施例中,钝化层10可以包括第一钝化层和第二钝化层;第一钝化层位于源极7和氮化物层6之间;第二钝化层位于氮化物层6和漏极8之间。需要说明的是,第二钝化层的高度可以与第一钝化层的高度相等,也可以不相等。通常情况下,由于第一钝化层和第二钝化层同时制作,第二钝化层的高度与第一钝化层的高度相等。

一些示例性实施例中,第一钝化层的材料包括氧化硅(SiO

具体的,由于第一钝化层和第二钝化层可以同时制作,因此,优选的,第一钝化层和第二钝化层的材料相同,且高度相同。沿栅极9指向氮化物层6的方向,第一钝化层和第二钝化层的高度为20nm~500nm。

参看图5,本申请实施例还提供了一种基于P型氮化物隔离的P-GaN晶体管的制备方法,包括以下步骤:

步骤S1、提供衬底,在衬底上形成依次堆叠的成核层、缓冲层、沟道层和势垒层。

步骤S2、在势垒层远离沟道层的一侧形成氮化物材料层,得到外延片。

步骤S3、刻蚀氮化物材料层,形成氮化物层和隔离层,并露出势垒层;隔离层与沟道层形成pn结,也可注入小剂量的Mg或其它离子,用于耗尽沟道层中的二维电子气,形成器件之间的隔离。

步骤S4、在势垒层上制作掩膜,形成欧姆窗口,以形成源极、漏极。

步骤S5、在势垒层和氮化物层上制作掩膜,形成栅极窗口,以形成栅极。

步骤S6、在势垒层、源极、漏极、栅极以及隔离层的上方形成钝化材料层。

步骤S7、在源极、漏极、栅极上方的钝化材料层上开孔,引出电极,得到晶体管。

具体的,在制备高电子迁移率晶体管时,首先提供衬底1,在衬底1上形成依次堆叠的成核层2、缓冲层3、沟道层4和势垒层5。在衬底1上形成堆叠的各个膜层前,首先对衬底1进行预处理和热处理,将衬底1放入氢氟酸(HF)溶液中浸泡1min,再依次放入丙酮溶液、无水乙醇溶液和去离子水中各超声清洗10min以消除衬底1表面悬挂键,将清洗吹干后的衬底1在氢气H

在成核层2上,继续采用MOCVD工艺依次淀积缓冲层3;在淀积缓冲层3的过程中,MOCVD工艺中的反应室压力为10Torr~100Torr,Ga源流量为50μmol/min~100μmol/min,氨气流量为3000sccm~6000sccm,氢气流量为1000sccm~2000sccm,温度为900℃。优选的,淀积成核层2的MOCVD工艺的反应室压力为10Torr、温度为900℃,向反应室同时通入流量为50μmol/min的Ga源、流量为1000sccm的氢气和流量为3000sccm的氨气,形成缓冲层3。缓冲层3的材料为GaN、AlN、AlGaN中的一种或几种。缓冲层3的厚度为0.5μm~5μm。

接下来,在缓冲层3上,采用MOCVD工艺依次淀积50nm的沟道层4,MOCVD工艺参数为:反应室压力为10Torr、温度为900℃,向反应室同时通入流量为50μmol/min的Ga源、流量为1000sccm的氢气和流量为3000sccm的氨气;沟道层4为GaN、AlN、AlGaN中的一种。优选的,沟道层4的材料为GaN;沟道层4的厚度分别为50nm~500nm。

在沟道层4上,继续采用MOCVD工艺淀积势垒层5;势垒层5的材料为AlGaN或AlN。优选的,势垒层5的材料为Al

在势垒层5上,采用MOCVD工艺在P-GaN窗口上淀积厚度为70nm的氮化物材料层,得到外延片;MOCVD工艺参数为:反应室压力为10Torr、温度为900℃,向反应室同时通入流量为50μmol/min的Ga源、流量为1000sccm的氢气和流量为3000sccm的氨气。

刻蚀器件之间的隔离区域以外的氮化物材料层,露出势垒层5,分别形成氮化物层6和隔离层11。具体的,通过对氮化物材料层进行图案化处理,刻蚀氮化物材料层,露出势垒层5,形成氮化物层6以及隔离层11。氮化物层6和隔离层11均为P型氮化物层,二者同时制作时,氮化物层6和隔离层11的材料相同。P型氮化物层为掺杂的P型GaN、AlN、AlGaN中的一种或几种。此处,需要说明的是,如若隔离层11采用与氮化物层6不同的材料时,可单独制作掩膜,以分别制作氮化物层6和隔离层11。

在势垒层5上制作掩膜,形成欧姆窗口,放入E-Beam电子束蒸发设备,采用电子束蒸发工艺淀积源极7和漏极8,Ti/Al/Ni/Au金属作为源极7和漏极8,电子束蒸发工艺的速率为0.1nm/s,并在850℃下进行退火30s。

源极7和漏极8采用Ti/Al/Ni/Au或者Ti/Al/Pt/Au的金属组合,以形成欧姆接触。优选的,源极7和漏极8的材料采用Ti/Al/Ni/Au组合的金属,其中金属Ti的厚度为20nm~100nm,金属Al的厚度为100nm~300nm,金属Ni的厚度为20nm~200nm,金属Au的厚度为20nm~200nm。在本申请实施例中,金属Ti的厚度为20nm,金属Al的厚度为100nm,金属Ni的厚度为20nm,金属Au的厚度为20nm。

在氮化物层6和势垒层5上制作掩膜,分别形成栅极窗口和肖特基岛窗口,将形成窗口的样品放置在电子束蒸发反应室中,利用纯度均为99.999%的镍和金靶材,在栅极窗口中采用电子束蒸发工艺淀积金属Ni/Au作为栅极9,其中Ni的厚度为20nm,Au的厚度为50nm。栅极9采用可与P型氮化物层6形成肖特基接触的金属,通常采用金属Ni/Au。。

将进行完上述步骤的样片放入等离子体化学气相淀积PECVD反应室内,PECVD工艺在势垒层5、源极7、漏极8、栅极9和隔离层11的上部淀积钝化材料层。具体的,采用等离子体增强化学气相沉积(Plasma Enhanced chemical VaPour DePosition,PECVD)工艺在势垒层5、源极7、漏极8、栅极9和隔离层11的上部淀积厚度为50nm~400nm的钝化材料层。在淀积钝化材料层的PECVD工艺中,反应室压力为0.5Pa~30Pa,反应室温度为200℃~350℃,反应室中同时通入20sccm的甲硅烷(SiH

最后,在源极7、漏极8、栅极9上方的钝化层10上开孔,引出电极,即得到晶体管。

需要说明的是,为了节省工艺,氮化物层6和隔离层11可以同时制作,在二者同时制作时,二者的材料相同,即二者的材料可以均为掺杂的P型氮化物。掺杂的P型氮化物通常选用掺杂的P型GaN、AlN、AlGaN中的一种或几种。

相比于现有的常规P型氮化物栅高电子迁移率晶体管,本申请的优势在于:本申请利用P-GaN隔离的P-GaN栅HEMT是在器件有源区设计并制作常规器件,但在器件之间的P-GaN进行保留,不采用刻蚀和离子注入工艺进行隔离,而是利用P-GaN耗尽沟道层的二维电子气,形成pn结而起到隔离作用。

通过仿真结果对本申请制得的基于P型氮化物隔离的P-GaN晶体管进行效果验证,如图6和图7所示;其中,图6为本申请制得的基于P型氮化物隔离的P-GaN晶体管的仿真图,图7为本申请制得的基于P型氮化物隔离的P-GaN晶体管的放大图。从图6和图7中可以看出,仿真击穿时的电流,可见漏电分布在单个器件内,不会影响另一个器件。由此可见,本申请提供的基于P型氮化物隔离的P-GaN晶体管及其制备方法,通过隔离层11能够有效阻断器件间的相互干扰作用,形成器件之间的有效隔离。

由以上技术方案,本申请实施例采用一种新型GaN器件隔离方法,提供一种基于P型氮化物隔离的P-GaN晶体管及其制备方法,该晶体管包括:衬底、成核层、缓冲层、沟道层、势垒层、位于势垒层上的源极和漏极、位于势垒层上的隔离层、氮化物层以及钝化层以及位于氮化物层上的栅极;源极和漏极分别与势垒层形成欧姆接触,钝化层位于源极和氮化物层之间、氮化物层与漏极之间;隔离层与沟道层形成pn结,用于耗尽沟道层中的二维电子气,形成器件之间的隔离;栅极的底部与氮化物层形成欧姆接触或肖特基接触。

本申请提供一种基于P型氮化物隔离的P-GaN晶体管及其制备方法,其目的在于提出一种新型GaN器件隔离方法,采用P型GaN或其他氮化物,氧化物等材料形成隔离层,使隔离层与沟道层形成pn结,可耗尽沟道层中由极化效应产生的二维电子气,阻断器件间的相互干扰作用,以形成器件之间的有效隔离。也可注入小剂量的Mg或其它离子,从而增加空穴浓度,增加pn型耗尽区深度,加强隔离效果。本申请取消了常规P-GaN器件的台面刻蚀工艺,不仅减小了刻蚀损伤,还降低了成本。与此同时,本申请制得的P-GaN栅HEMT不仅可以保持增强型的特性,还可以减小刻蚀与注入损伤,从而降低泄漏电流,提高器件的击穿电压。

本领域的普通技术人员可以理解,上述各实施方式是实现本申请的具体实施例,而在实际应用中,可以在形式上和细节上对其作各种改变,而不偏离本申请的精神和范围。任何本领域技术人员,在不脱离本申请的精神和范围内,均可作各自更动与修改,因此本申请的保护范围应当以权利要求限定的范围为准。

- 一种氧化槽交替隔离型绝缘栅双极晶体管及其制备方法

- 一种电荷存储型绝缘栅双极型晶体管及其制备方法

- 一种基于钴基氮化物纳米阵列的杀虫脒传感器的制备方法及应用

- 一种体掺杂金刚石基常关型场效应晶体管及其制备方法

- 一种绝缘栅双极型晶体管及其制备方法

- 一种基于p-GaN结构的三维增强型高电子迁移率晶体管及其制造方法

- 一种基于p-GaN结构的三维增强型高电子迁移率晶体管及其制造方法