连接线及连接线的使用方法

文献发布时间:2023-06-19 13:46:35

【技术领域】

本发明涉及一种连接线及连接线的使用方法,尤指一种能快速打开高速传输通道的连接 线及连接线的使用方法。

【背景技术】

现有一种连接线,其一端具有一第一连接器,所述第一连接器用以与一第一设备对接。所 述第一连接器具有一第一芯片模块及一第一驱动器,且所述第一芯片模块及所述第一驱动器 通过一第一线路相连接。所述连接线的另一端具有一第二连接器,所述第二连接器用以与一 第二设备对接。所述第二连接器具有一第二芯片模块及一第二驱动器,且所述第二芯片模块 及所述第二驱动器通过一第二线路相连接。所述连接线还设有一侦测线路,所述侦测线路一 端连接所述第一连接器,另一端连接所述第二连接器,所述侦测线路还延伸具有一第三线路 及一第四线路。所述第三线路用以连接所述第一芯片模块,所述第四线路用以连接所述第二 芯片模块。

当所述连接线使用时,所述第一连接器与所述第一设备相对接,所述第二连接器与所述 第二设备相对接。所述第一设备通过所述侦测线路的所述第三线路连接所述第一芯片模块, 且告知所述第一芯片模块所述第一设备即将开启高速信号传输的讯息及高速信号传输的方 向。在此之后所述第一设备再通过所述侦测线路的所述第四线路告知所述第二芯片模块所述 第一设备即将开启高速信号传输的讯息及高速信号传输的方向。在所述侦测线路将所述第一 设备即将开启高速信号传输的讯息及高速传输的方向分别告知所述第一芯片模块及所述第二 芯片模块之后,所述第一芯片模块会通过所述第一线路将所述第一设备即将开启高速信号传 输的讯息及高速信号传输的方向告诉所述第一驱动器且所述第一芯片模块会与所述第一驱动 器进行沟通,使得所述第一驱动器开启其内部的传输通道。所述第二芯片模块会通过所述第 二线路将所述第一设备即将开启高速信号传输的讯息及高速信号传输的方告诉所述第二驱动 器且所述第二芯片模块会与所述第二驱动器进行沟通,使得所述第二驱动器开启其内部的传 输通道。当所述第一驱动器及所述第二驱动器都打开其内部的传输通道之后,所述第一设备 及所述第二设备就可以通过所述连接线传输高速信号。

但是,由于所述第一设备告知所述第一芯片模块及所述第二芯片模块所述第一设备即将 开启高速信号传输的讯息及高速信号传输的方向之后,所述第一设备就会马上开始传输高速 信号,但是此时所述第一芯片模块还在与所述第一驱动器进行沟通,所述第二芯片模块还在 与所述第二驱动器进行沟通。因此,所述第一驱动器和所述第二驱动器此时都没有打开其内 部的传输通道,故导致所述第一设备与所述第二设备无法通过所述连接线传输高速信号。

因此,有必要设计一种改良的连接线,以克服上述问题。

【发明内容】

本发明的目的在于提供一种通过一第一侦测线路从而快速打开一第一驱动器及一第二 驱动器内部的信号传输通道,使得第一设备及第二设备能够通过所述高速传输线路传递信号 的连接线及连接线的使用方法。

为实现上述目的,本发明采用以下技术手段:

一种连接线,用以连接一第一设备及一第二设备,其特征在于,包括:一第一连接器, 用以与所述第一设备相连接,所述第一连接器设有一第一芯片模块及一第一驱动器;一第二 连接器,用以与所述第二设备相连接,所述第二连接器设有一第二芯片模块及一第二驱动器; 一第一侦测线路一端用以连接所述第一驱动器,另一端用以连接所述第二驱动器,所述第一 驱动器或所述第二驱动器二者中侦测到信号的一者打开其内部信号传输通道,且通过所述第 一侦测线路告知未侦测到信号的一者打开其内部信号传输通道;一第二侦测线路一端经由所 述第一连接器连接所述第一设备,另一端经由所述第二连接器连接所述第二设备,且所述第 二侦测线路具有一第一导通路径与所述第一芯片模块相连接,所述第一芯片模块用于控制所 述第一驱动器中的信号的传输方向,所述第二侦测线路具有一第二导通路径与所述第二芯片 模块相连接,所述第二芯片模块用于控制所述第二驱动器中的信号的传输方向;至少一高速 传输线路一端经由所述第一连接器连接所述第一设备,另一端经由所述第二连接器连接所述 第二设备,且所述高速传输线路分别连接所述第一驱动器或所述第二驱动器。

进一步,一供电线路一端经由所述第一连接器连接所述第一设备,另一端经由所述第二连 接器连接所述第二设备,连接电源的所述第一连接器或所述第二连接器通过所述供电线路将 电源传输至未连接电源的所述第二连接器或所述第一连接器。

进一步,所述供电线路通过一第一连接线路连接一第一逻辑电源,所述第一逻辑电源用于 调整所述供电线路传输至所述第一逻辑电源内的电源的电压,且所述第一逻辑电源将调整后 的电源分别传输至所述第一芯片模块及所述第一驱动器。

进一步,所述供电线路通过一第二连接线路连接一第二逻辑电源,所述第二逻辑电源用于 调整所述供电线路传输至所述第二逻辑电源内的电源的电压,且所述第二逻辑电源将调整后 的电源分别传输至所述第二芯片模块及所述第二驱动器。

进一步,所述第一设备及所述第二设备均设有至少一对接收信号及至少一对发送信号,所 述第一驱动器具有一第一侦测件及一第一驱动模块,所述第一侦测件用于侦测所述第二设备 的所述接收信号,当所述第一侦测件侦测到所述第二设备的所述接收信号,且通过一第一告 知线路告知所述第一驱动模块,所述第一驱动模块将打开其内部的信号传输通道。

进一步,所述第一设备及所述第二设备均设有至少一对接收信号及至少一对发送信号,所 述第二驱动器具有一第二侦测件及一第二驱动模块,所述第二侦测件用于侦测所述第一设备 的所述接收信号,当所述第二侦测件侦测到所述第一设备的所述接收信号,且通过一第二告 知线路告知所述第二驱动模块,所述第二驱动模块将打开其内部的信号传输通道。

进一步,所述第一驱动器或所述第二驱动器二者中已打开其内部信号传输通道的一者通 过所述第一侦测线路告知未打开其内部信号传输通道的一者打开其内部信号传输通道。

进一步,一第三导通路径一端连接所述第一芯片模块,另一端连接所述第一驱动器,所述 第一芯片模块通过所述第三导通路径控制所述第一驱动器中的信号的传输方向,一第四导通 路径一端连接所述第二芯片模块另一端连接所述第二驱动器,所述第二芯片模块通过所述第 四导通路径控制所述第二驱动器中的信号的传输方向。

进一步,所述第一芯片模块通过所述第三导通路径将信号传输至所述第一驱动器,且告知 所述第一驱动器将所述第一芯片模块传输至所述第一驱动器的信号放大,所述第二芯片模块 通过所述第四导通路径将信号传输至所述第二驱动器,且告知所述第二驱动器将所述第二芯 片模块传输至所述第二驱动器的信号放大。

进一步,一信号传输线路经由所述第一连接器连接所述第一设备,另一端经由所述第二连 接器连接所述第二设备,所述信号传输线路供所述第一设备及所述第二设备进行信息的交换, 且使所述第一设备或所述第二设备通过一电源线将电源传输至所述第二设备或所述第一设 备。

另外,本发明还提供一种连接线的使用方法,所述使用方法适用于一种连接线,所述连 接线用以与一第一设备及一第二设备相连接,所述连接线包括:一第一连接器、一第二连接 器、一第一侦测线路、一第二侦测线路及一高速传输线路,且所述第一连接器设有一第一芯 片模块及一第一驱动器,所述第二连接器设有一第二芯片模块及一第二驱动器,其特征在于, 所述使用方法包括:步骤1,将所述第一设备与所述第一连接器相连接,所述第二设备与所 述第二连接器相连接;步骤2,当所述第一驱动器先侦测到信号的时候,所述第一驱动器会 打开其内部的信号传输通道,在此之后所述第一驱动器会通过所述第一侦测线路告知所述第 二驱动器,使得所述第二驱动器打开其内部的传输通道,或者当所述第二驱动器先侦测到信 号的时候,所述第二驱动器会打开其内部的信号传输通道,在此之后所述第二驱动器会通过 所述第二侦测线路告知所述第一驱动器,使得所述第一驱动器打开其内部的传输通道;步骤 3,所述第一设备先通过所述第二侦测线路的一第一导通路径告知所述第一芯片模块所述第一 设备中信号的传输方向,在此之后,所述第一设备再通过所述第二侦测线路的一第二导通路 径告知所述第二芯片模块所述第一设备中信号的传输方向,或者所述第二设备先通过所述第 二侦测线路的所述第二导通路径告知所述第二芯片模块所述第二设备中信号的传输方向,在 此之后,所述第二设备再通过所述第二侦测线路的所述第一导通路径告知所述第一芯片模块 所述第二设备中信号的传输方向;步骤4,所述第一芯片模块与所述第一驱动器进行信号传 输,从而控制所述第一驱动器中信号的传输方向,所述第二芯片模块与所述第二驱动器进行 信号传输,从而控制所述第二驱动器中信号的传输方向;步骤5,所述第一设备依次通过所 述第一驱动器、所述高速传输线路及所述第二驱动器将所述第一设备中的信号传输给所述第 二设备;或者所述第二设备依次通过所述第二驱动器、所述高速传输线路及所述第一驱动器 将所述第二设备中的信号传输给所述第一设备。

进一步,在步骤1之后步骤2之前,所述第一设备先通过所述连接线的一第一连接线路 将电源传输至所述第一连接器的一第一逻辑电源,在此之后所述第一连接器再通过所述连接 线的一供电线路及一第二连接线路将电源传输至所述第二连接器;或者所述第二设备先通过 所述第二连接线路将电源传输至所述第二连接器,在此之后所述第二连接器再通过所述供电 线路及所述第一连接线路将电源传输至所述第一连接器。

进一步,在步骤1之后步骤2之前,所述第一逻辑电源先将所述电源进行升压或降压处 理后,所述第一逻辑电源再将处理后的所述电源传输至所述第一芯片模块及所述第一驱动器; 所述第二逻辑电源先将所述电源升压或降压处理后,所述第二逻辑电源再将处理后的所述电 源传输至所述第二芯片模块及所述第二驱动器。

进一步,在步骤2中,所述第一驱动器设置有一第一侦测件及一第一驱动模块,所述第 二驱动器设置有一第二侦测件及一第二驱动模块;当所述第一侦测件侦测到所述第二设备的 接收信号时,所述第一侦测件将通过一第一告知线路告知所述第一驱动模块,使得所述第一 驱动模块打开其内部的信号传输通道;或者当所述第二侦测件侦测到所述第一设备的接收信 号时,所述第二侦测件将通过一第二告知线路告知所述第二驱动模块,使得所述第二驱动模 块打开其内部的信号传输通道。

进一步,在步骤4中,所述第一芯片模块通过一第三导通路径将信号传输至所述第一驱 动器,且告知所述第一驱动器将所述第一芯片模块传输至所述第一驱动器的信号放大,所述 第二芯片模块通过一第四导通路径将信号传输至所述第二驱动器,且告知所述第二驱动器将 所述第二芯片模块传输至所述第二驱动器的信号放大。

与现有技术相比,本发明具有以下有益效果:

本发明所述连接线及连接线的使用方法的所述第一侦测线路一端用以连接所述第一驱动 器,另一端用以连接所述第二驱动器,所述第一驱动器或所述第二驱动器二者中侦测到信号 的一者打开其内部信号传输通道,且通过第一侦测线路告知未侦测到信号的一者打开其内部 信号传输通道。如此,所述第一驱动器不需要与所述第一芯片模块沟通后再打开所述其内部 的信号传输通道,所述第二驱动器不需要与所述第二芯片模块沟通后再打开所述其内部的信 号传输通道。这样省去了所述第一芯片模块与所述第一驱动器沟通时间,也省去了所述第二 芯片模块与所述第二驱动器沟通时间。

而且由于所述第一芯片模块通过所述第一导通路径控制所述第一驱动器中的信号的传输 方向,所述第二芯片模块通过所述第二导通路径控制所述第二驱动器中的信号的传输方向。 如此,虽然所述第一芯片模块通过所述第一导通路径控制所述第一驱动器中的信号传输方向, 所述第二芯片模块通过所述第二导通路径控制所述第二驱动器中的信号传输方向会花费相应 的时间,但是与背景技术的所述第一芯片模块通过所述第一线路将所述第一设备即将开启高 速信号传输的讯息及高速信号传输的方向告诉所述第一驱动模块,所述第二芯片模块会通过 所述第二线路将所述第二设备即将开启高速信号传输的讯息及高速信号传输的方向告诉所述 第二驱动模块相比还是节约了时间。故即使所述第一设备或者所述第二设备分别告知所述第 一芯片模块及所述第二芯片模块所述第一设备或者所述第二设备即将开启高速传输的讯息及 高速信号的方向后,就马上开始传输高速信号。此时,由于所述第一驱动器及所述第二驱动 器均打开了其内部的传输通道,故所述第一设备与所述第二设备之间的高速传输信号能通过 所述连接线进行传递。

【附图说明】

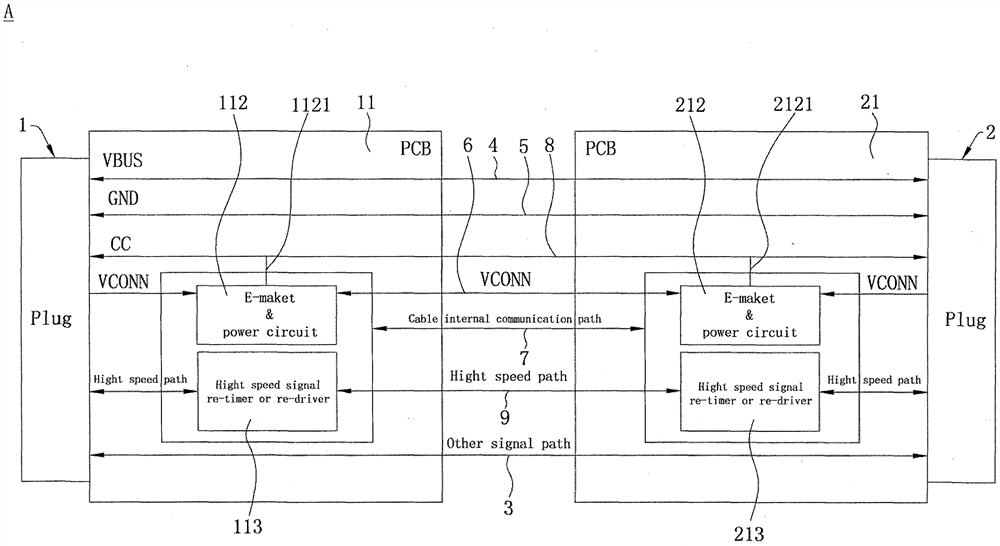

图1为本发明连接线的示意图;

图2为本发明连接线的局部详细示意图;

图3为本发明连接线的局部剖视图;

具体实施方式的附图标号说明:

【具体实施方式】

为便于更好的理解本发明的目的、结构、特征以及功效等,现结合附图和具体实施方式 对本发明作进一步说明。

如图1至图3所示,本发明涉及一种连接线A,所述连接线A包括一第一连接器1及一第 二连接器2。所述第一连接器1设于所述连接线A的一端用以与一第一设备1’相对接,所述 第二连接器2设于所述连接线A的另一端用以与一第二设备2’相对接。所述第一设备1’设 有一第一控制器11’、一对第一发送信号12’及一对第一接收信号13’。所述第二设备2’对 应于所述第一设备1’设有一第二控制器21’、一对第二发送信号22’及一对第二接收信号 23’。

如图1至图3所示,所述连接线A具有一信号传输线3,所述信号传输线3的一端通过所 述第一连接器1连接所述第一设备1’,另一端通过所述第二连接器2连接所述第二设备2’。 所述第一设备1’及所述第二设备2’通过所述信号传输线3进行信息的交换。所述第一设备 1’及所述第二设备2’主要通过所述信号传输线3进行电源的沟通及讯号种类的沟通。所述 第一设备1’和所述第二设备2’通过所述信号传输线3进行电源的沟通后,确定由所述第一 设备1’将电源传输给所述第二设备2’(在其它实施例中也可以是,由所述第二设备2’将 电源传输给所述第一设备1’)。所述第一设备1’和所述第二设备2’通过所述信号传输线3 进行讯号种类的沟通主要是根据所述第一设备1’和所述第二设备2’的类型,而确定所述第 一设备1’与所述第二设备2’之间的传递的讯号种类。例如,假设所述第一设备1’及所述第二设备2’均为USB的装置,那么所述第一设备1’与所述第二设备2’之间是通过USB讯 号进行沟通的。

如图1至图3所示,所述连接线A还包括一电源线4及一接地线5,所述电源线4一端通 过所述第一连接器1连接所述第一设备1’,另一端通过所述第二连接器2连接所述第二设备 2’。当所述第一设备1’及所述第二设备2’通过所述信号传输线3进行信息的交换后,所述 第一设备1’就可以通过所述电源线4将电源传输至所述第二设备2’(在其它实施例中也可 以是所述第二设备2’通过所述电源线4将电源传输至所述第一设备1’),使得所述第一设备 1’及所第二设备2’都连通有电源。所述接地线5一端连接所述第一连接器1,另一端连接 所述第二连接器2,如此使得所述第一连接器1的地线及所述第二连接器2的地线连通,从 而使得所述第一连接器1及所述第二连接器2具有良好的接地性能。

如图1至图3所示,所述连接线A还设有一供电线路6、一第一侦测线路7、一第二侦测 线路8及四个高速传输线路9。所述供电线路6一端通过所述第一连接器1连接所述第一控 制器11’,另一端通过所述第二连接器2连接所述第二控制器21’。所述第一控制器11’通过所述供电线路6将电源传输给所述第一连接器1和所述第二连接器2(在其它实施例中也可以是,所述第二控制器21’通过所述供电线路6将电源传输给所述第二连接器2和所述第一连接器1)。所述第二侦测线路8一端通过所述第一连接器1连接所述第一控制器11’,另一端通过所述第二连接器2连接所述第二控制器21’。当所述第一控制器11’通过所述供电线路6将电源传输给所述第一连接器1和所述第二连接器2后,所述第一控制器11’及所述第二控制器21’则会通过所述第二侦测线路8进行相关信息的交换,从而互相确认所述第一设备1’及所述第二设备2’的连线类型,并且所述第一设备1’会通过所述第二侦测线路8 先后告知所述第一连接器1及所述第二连接器2所述第一设备1’即将通过所述高速传输线 路9将所述第一发送信号12’传输至所述第二设备2’。所述第一侦测线路7一端用以连接所 述第一连接器1,另一端用以连接所述第二连接器2。故,当所述第一设备1’及所述第二设 备2’通过所述第二侦测线路8进行沟通且相互确认类型,且所述第一设备1’通过所述第二 侦测线路8先后告知所述第一连接器1及所述第二连接器2所述第一设备1’即将通过所述 高速传输线路9将所述第一发送信号12’传输至所述第二设备2’之后,所述第一连接器1 则会打开其内部的信号传输通道且通过所述第一侦测线路7快速告知所述第二连接器2,使 得所述第二连接器2能够快速打开其内部的信号传输通道。所述高速传输线路9一端通过所述第一连接器1连接所述第一设备1’,另一端通过所述第二连接器2连接所述第二设备2’。当所述第一设备1’通过所述第二侦测线路8先后告知所述第一连接器1及所述第二连接器2所述第一设备1’即将通过所述高速传输线路9将所述第一发送信号12’传输至所述第二设备2’之后,所述高速传输线路9则会将所述第一发送信号12’传输至所述第二设备2’,及 将所述第二发送信号22’传输至所述第一设备1’。而且由于此时所述第一连接器1及所述第二连接器2均已开启其内部的传输通道。故所述第一发送信号12’及所述第二发送信号22’能在所述高速传输线路9上进行传输。

如图1至图3所示,所述第一连接器1设有一第一电路板11,所述第一电路板11上设有 一第一逻辑电源111、一第一芯片模块112及一第一驱动器113。所述第一逻辑电源111通过 一第一连接线路1111连接所述供电线路6,使得所述供电线路6上的电源能够通过所述第一 连接线A传输至所述第一逻辑电源111内。而且所述第一逻辑电源111会将所述供电线路6 传输至所述第一逻辑电源111内的电源的电压进行调整,使得调整后的电源电压与所述第一 芯片模块112及所述第一驱动器113所需要的电源电压相一致。在此之后,所述第一逻辑电 源111再将调整后的电源通过一第一线路1112传递给所述第一芯片模块112,并且所述第一 逻辑电源111将调整后的电源通过一第二线路1113传递给所述第一驱动器113,使得所述第 一芯片模块112及所述第一驱动器113都连接有电源。

如图1至图3所示,所述第一芯片模块112通过一第一导通路径1121连接所述第二侦测 线路8,使得所述第二侦测线路8能够通过所述第一导通路径1121将所述第一控制器11’传 输的信号(信号包括USB信号、BTB信号及PD转向信号)传递给所述第一芯片模块112。所 述第一芯片模块112连接有一第三导通路径1122(所述第二导通路径2121又称为低频传输 线,简称I2C),所述第三导通路径1122一端用以连接所述第一芯片模块112,另一端用以连 接所述第一驱动器113。所述第一芯片模块112通过所述第三导通路径1122将所述第一芯片 模块112的信号传输给所述第一驱动器113,从而控制所述第一驱动器113中的所述第一发 送信号12’的传输方向。与此同时,所述第一芯片模块112还通过所述第三导通路径1122 告知所述第一驱动器113将所述第一芯片模块112传输至所述第一驱动器113的部分信号(该 部分信号包括USB信号及BTB信号)进行放大处理,从而使得被放大的部分信号的得以增强, 有利于所述连接线A的信号的传输。

如图1至图3所示,所述第一驱动器113内设有一第一侦测件1131(RX detect)及一第 一驱动模块1132,所述第一驱动模块1132又包括一第一正向驱动模块11321及一第一逆向 驱动模块11322。所述第一侦测件1131用以侦测所述第二设备2’内的所述第二接收信号23’。 当所述第一侦测件1131侦测到所述第二接收信号23’时,所述第一侦测件1131会通过一第 一告知线路11311告知所述第一驱动模块1132。当所述第一驱动模块1132接收到所述第一 侦测件1131通过所述第一告知线路11311的告知信号之后,所述第一正向驱动模块11321会 开启其内部的信号传输通道,在此之后所述第一设备1’会通过所述高速传输线将所述第一 发送信号12’经过所述第一驱动器113传输至所述第二设备2’。

如图1至图3所示,所述第二连接器2设有一第二电路板21,所述第二电路板21上设有 一第二逻辑电源211、一第二芯片模块212及一第二驱动器213。所述第二逻辑电源211通过 一第二连接线路2111连接所述供电线路6,使得所述供电线路6上的电源能够通过所述第二 连接线A传输至所述第二逻辑电源211内。而且所述第二逻辑电源211会将所述供电线路6 传输至所述第二逻辑电源211内的电源的电压进行调整,使得调整后的电源电压与所述第二 芯片模块212及所述第二驱动器213所需要的电源电压相一致。在此之后,所述第二逻辑电 源211再将调整后的电源通过一第三线路2112传递给所述第二芯片模块212,并且所述第二 逻辑电源211将调整后的电源通过一第四线路2113传递给所述第二驱动器213,使得所述第 二芯片模块212及所述第二驱动器213都连接有电源。

如图1至图3所示,所述第二芯片模块212通过一第二导通路径2121连接所述第二侦测 线路8,使得所述第二侦测线路8能够通过所述第二导通路径2121将所述第一控制器21’传 输的信号(相关信号包括USB信号、BTB信号及PD转向信号)传递给所述第二芯片模块212。 所述第二芯片模块212连接有一第四导通路径2122(所述第四导通路径2122又称为低频传 输线,简称I2C),所述第四导通路径2122一端用以连接所述第二芯片模块212,另一端用以 连接所述第二驱动器213。所述第二芯片模块212通过所述第四导通路径2122将所述第二芯 片模块212的信号传输给所述第二驱动器213,从而控制所述第二驱动器213中的所述第二 发送信号22’的传输方向。与此同时,所述第二芯片模块212还通过所述第四导通路径2122 告知所述第二驱动器213将所述第二芯片模块212传输至所述第二驱动器213的部分信号(该 部分信号包括USB信号及BTB信号)进行放大处理,从而使得被放大的部分信号的得以增强, 有利于所述连接线A的信号的传输。

如图1至图3所示,所述第二驱动器213内设有一第二侦测件2131(RX detect)及一第 二驱动模块2132,所述第二驱动模块2132又包括一第二正向驱动模块21321及一第二逆向 驱动模块21322。所述第二侦测件2131用以侦测所述第一设备1’内的所述第一接收信号13’。 当所述第二侦测件2131侦测到所述第一接收信号13’时,所述第二侦测件2131会通过一第 二告知线路21311告知所述第二驱动模块2132。当所述第二驱动模块2132接收到所述第二 侦测通过所述第二告知线路21311的告知的信号之后,所述第二正向驱动模块21321会开启 其内部的信号传输通道,在此之后所述第二设备2’会通过所述高速传输线将所述第二发送 信号22’经过所述第二驱动器213传输至所述第一设备1’。

如图1至图3所示,以下所述连接线的使用方法的第一实施例(为方便,图1、图2和图3中省去了一些步骤):

步骤1,当所述连接线A使用时,所述第一连接器1与所述第一设备1’相对接,所述第 二连接器2与所述第二设备2’相对接。所述第一设备1’及所述第二设备2’先通过所述信号传输路径进行电源及信号种类的沟通,从而确定电源由所述第一设备1’传输给所述第二设备2’,以及确定所述第一设备1’及所述第二设备2’之间传输信号的类型。在此之后, 所述第一设备1’通过所述电源线4将电源传输至所述第二设备2’,使得所述第二设备2’ 通电。而且此时,所述第一连接器1及所述第二连接器2通过所述接地线5连接接地,使得 所述第一连接器1及所述第二连接器2均具有良好的接地性能。

在此之后,所述第一设备1’通过所述供电线路6检测所述第一芯片模块112的内部电阻, 所述第二设备2’通过所述供电线路6检测所述第二芯片模块212的内部电阻,从而确定由 所述第一设备1’通过所述供电线路6先对所述第一芯片模块112提供电源,之后所述第一 设备1’再通过所述供电线路6对所述第二芯片模块212提供电源。具体提供电源的路径为: 所述第一设备1’的所述第一控制器11’先通过所述供电线路6及所述第一连接线路1111将 电源传输给所述第一逻辑电源111,然后所述第一逻辑电源111将输入进的电源电压进行调 整,最后所述第一逻辑电源111再将调整后的电源分别通过所述第一线路1112及所述第二线 路1113输给所述第一芯片模块112及所述第一驱动模块1132。在此之后所述第一设备1’再 通过所述供电线路6及所述第二连接线路2111将电源传输给所述第二逻辑电源211,然后所 述第二逻辑电源211将输入进的电源电压进行调整,最后所述第二逻辑电源211再将调整后 的电源分别通过所述第三线路2112及所述第四线路2113输给所述第二芯片模块212及所述 第二驱动模块2132。如此,使得所述第一芯片模块112、所述第一驱动器113、所述第二芯 片模块212及所述第二驱动器213都连通有电源。

步骤2,所述第一设备1’及所述第二设备2’通过所述第二侦测线路8进行沟通,从而 互相确认所述第一设备1’及所述第二设备2’的连线类型,并且所述第一设备1’会通过所 述第二侦测线路8及所述第一导通路径1121先告知所述第一芯片模块112所述第一设备1’ 即将通过所述高速传输线路9将所述第一发送信号12’传输至所述第二设备2’,之后所述第 一设备1’再通过所述第二侦测线路8及所述第二导通路径2121告知所述第二芯片模块212 所述第一设备1’即将通过所述高速传输线路9将所述第一发送信号12’传输至所述第二设 备2’。在所述第一芯片模块112获知所述第一设备1’即将通过所述高速传输线路9将所述 第一发送信号12’传输至所述第二设备2’的讯息之后,所述第一芯片模块112会通过所述 第三导通路径1122与所述第一驱动器113进行沟通,从而使得所述第一驱动器113的所述第 一正向驱动模块11321打开其内部的信号传输通道。与此同时,所述第一侦测件1131也会一 直侦测所述第二设备2’上的所述第二接收信号23’,一旦所述第一侦测件1131侦测到所述 第二接收信号23’,所述第一侦测件1131就会直接通过所述第一告知线路11311告知所述第 一驱动模块1132,从而使得所述第一正向驱动模块11321打开其内部的传输通道。当所述第 一正向驱动模块11321打开其内部的传输通过之后,所述第一驱动器113会马上通过所述第 一侦测线路7告知所述第二驱动器213,使得所述第二驱动器213中的所述第二正向驱动模 块21321不需要通过所述第二芯片模块212或者所述第二侦测件2131的告知就直接打开其内 部的传输通道。

步骤3,在所述第一正向驱动模块11321及所述第二正向驱动模块21321均打开其内部的 传输通道之后,所述第一设备1’的所述第一控制器11’会通过所述第二侦测线路8及所述 第一导通路径1121将所述第一设备的所述第一控制器11’传输的信号(信号包括USB信号、 BTB信号及PD转向信号)传递给所述第一芯片模块112。在此之后,所述第一设备1’的所 述第一控制器11’再通过所述第二侦测线路8及所述第二导通路径2121将所述第一控制器 11’传输的信号(信号包括USB信号、BTB信号及PD转向信号)传递给所述第二芯片模块。

步骤4,所述第一芯片模块112通过所述第三导通路径1122将所述第一芯片模块112的 信号传输给所述第一驱动器113,从而控制所述第一驱动器113中的所述第一发送信号12’ 的传输方向。与此同时,所述第一芯片模块112还会通过所述第三导通路径1122告知所述第 一驱动器113将所述第一芯片模块112传输至所述第一驱动器113的部分信号(该部分信号 包括USB信号及BTB信号)进行放大处理。所述第二芯片模块212通过所述第四导通路径2122 将所述第二芯片模块212的信号传输给所述第二驱动器213,从而控制所述第二驱动器213 中的所述第二发送信号22’的传输方向。与此同时,所述第二芯片模块212还通过所述第四 导通路径告知所述第二驱动器213将所述第二芯片模块212传输至所述第二驱动器213的部 分信号(该部分信号包括USB信号及BTB信号)进行放大处理。

步骤5,所述第一设备1’的所述第一发送信号12’通过所述高速传输线路9和所述第一 驱动器113传输至所述第二设备2’,所述第二设备2’的所述第二发送信号22’通过所述高 速传输线路9和所述第二驱动器213传输至所述第一设备1’。从而实现所述第一设备1’与 所述第二设备2’之间的高速信号的传输。

所述连接线A在使用时第二实施例,其与第一实施例的所述连接线A在使用时的不同之 处在于,所述第二实施例的所述连接线A的结构与所述第一实施例的所述连接线A的结构相 同,故不再赘述:所述第一设备1’及所述第二设备2’通过所述信号传输路径进行电源及信 号种类的沟通,从而确定电源由所述第二设备2’传输给所述第一设备1’,之后所述第二设 备2’通过所述电源线4将电源传输至所述第一设备1’,使得所述第一设备1’通电。在此 之后,确定由所述第二设备2’通过所述供电线路6先后对所述第二芯片模块212及所述第 一芯片模块112提供电源。具体提供电源的路径为:所述第二设备2’的所述第二控制器21’ 先通过所述供电线路6及所述第二连接线路2111将电源传输给所述第二逻辑电源211,然后 所述第二逻辑电源211将输入进的电源电压进行调整,最后所述第二逻辑电源211再将调整 后的电源分别通过所述第三线路2112及所述第四线路2113输给所述第二芯片模块212及所 述第二驱动模块2132。在此之后所述第二设备2’再通过所述供电线路6及所述第一连接线 路1111将电源传输给所述第一逻辑电源111,然后所述第一逻辑电源111将输入进的电源电 压进行调整,最后所述第一逻辑电源111再将调整后的电源分别通过所述第一线路1112及所 述第二线路1113输给所述第一芯片模块112及所述第一驱动模块1132。如此,使得所述第 二芯片模块212、所述第二驱动器213、所述第一芯片模块112及所述第一驱动器113都连通 有电源。

在此之后,所述第二设备2’会通过所述第二侦测线路8及所述第二导通路径2121先告 知所述第二芯片模块212所述第二设备2’即将通过所述高速传输线路9将所述第二发送信 号22’传输至所述第一设备1’,之后所述第二设备2’再通过所述第二侦测线路8及所述第 一导通路径1121告知所述第一芯片模块112所述第二设备2’即将通过所述高速传输线路9 将所述第二发送信号22’传输至所述第一设备1’。在所述第二芯片模块212获知所述第二设 备2’即将通过所述高速传输线路9将所述第二发送信号22’传输至所述第一设备1’的讯 息之后,所述第二芯片模块212会通过所述第四导通路径2122与所述第二驱动器213进行沟 通,从而使得所述第二驱动器213的所述第二正向驱动模块21321打开其内部的信号传输通 道。与此同时,所述第二侦测件2131也会一直侦测所述第一设备1’上的所述第一接收信号 13’,一旦所述第二侦测件2131侦测到所述第一接收信号13’,所述第二侦测件2131就会直 接通过所述第二告知线路21311告知所述第二驱动模块2132,从而使得所述第二正向驱动模 块21321打开其内部的传输通道。当所述第二正向驱动模块21321打开其内部的传输通过之 后,所述第二驱动器213会马上通过所述第一侦测线路7告知所述第一驱动器113,使得所 述第一驱动器113中的所述第一正向驱动模块11321不需要通过所述第一芯片模块112或者 所述第一侦测件1131的告知就直接打开其内部的传输通道。从而使得所述第二设备2’的所 述第二发送信号22’通过所述高速传输线路9经和所述第二驱动器213传输至所述第一设备 1’,所述第一设备1’的所述第一发送信号12’通过所述高速传输线路9和所述第一驱动器 113传输至所述第二设备2’。从而实现所述第二设备2’与所述第一设备1’之间的高速信号 的传输。

所述连接线A在使用时第三实施例,其与第一实施例的所述连接线A在使用时的不同之 处在于,所述第三实施例的所述连接线A的结构与所述第一实施例的所述连接线A的结构相 同,故不再赘述:所述第一连接器1连接的所述第一设备1’仅设有两对所述第一发送信号 12’,而未设置有所述第一接收信号13’。所述第二连接器2连接的所述第二设备2’仅设有 两对所述第二接收信号23’,而未设置有所述第二发送信号22’。此时,当所述第一正向驱动 模块11321打开其内部的传输通过之后,所述第一驱动器113会马上通过所述第一侦测线路 7告知所述第二驱动器213,使得所述第二驱动器213中的所述第二逆向驱动模块21322不需 要通过所述第二芯片模块212或者所述第二侦测件2131的告知就直接打开其内部的传输通 道。从而使得所述第一设备1’的所述第一发送信号12’通过所述高速传输线路9传输至所 述第一驱动器113内,然后所述第一发送信号12’再通过所述高速传输线路9传输至所述第 二驱动器213内,最后所述第一发送信号12’再通过所述高速传输线路9传输至所述第二设 备2’。

所述连接线A在使用时第四实施例,其与第一实施例的所述连接线A在使用时的不同之 处在于,所述第四实施例的所述连接线A的结构与所述第一实施例的所述连接线A的结构相 同,故不再赘述:所述第一连接器1连接的所述第一设备1’仅设有两对所述第一接收信号 13’,而未设置有所述第一发送信号12’。所述第二连接器2连接的所述第二设备2’仅设有 两对所述第二发送信号22’,而未设置有所述第二接收信号23’。此时,当所述第二正向驱动 模块21321打开其内部的传输通过之后,所述第二驱动器213会马上通过所述第二侦测线路 8告知所述第一驱动器113,使得所述第一驱动器113中的所述第一逆向驱动模块11322不需 要通过所述第一芯片模块112或者所述第一侦测件1131的告知就直接打开其内部的传输通 道。从而使得所述第二设备2’的所述第二发送信号22’通过所述高速传输线路9传输至所 述第二驱动器213内,然后所述第二发送信号22’再通过所述高速传输线路9传输至所述第 一驱动器113内,最后所述第二发送信号22’再通过所述高速传输线路9传输至所述第一设 备1’。

综上所述,本发明连接线A及连接线A的使用方法有下列有益效果:

(1)本发明所述连接线A及连接线A的使用方法的所述第一侦测线路7一端用以连接所 述第一驱动器113,另一端用以连接所述第二驱动器213,所述第一驱动器113或所述第二驱 动器213二者中侦测到信号的一者打开其内部信号传输通道,且通过第一侦测线路7告知未 侦测到信号的一者打开其内部信号传输通道。如此,所述第一驱动器113不需要与所述第一 芯片模块112沟通后再打开所述其内部的信号传输通道,所述第二驱动器213不需要与所述 第二芯片模块212沟通后再打开所述其内部的信号传输通道。这样省去了所述第一芯片模块 112与所述第一驱动器113沟通时间,也省去了所述第二芯片模块212与所述第二驱动器213 沟通时间。

而且由于所述第一芯片模块112通过所述第一导通路径1121控制所述第一驱动器113中 的信号的传输方向,所述第二芯片模块212通过所述第二导通路径2121控制所述第二驱动器 213中的信号的传输方向。如此,虽然所述第一芯片模块112通过所述第一导通路径1121控 制所述第一驱动器113中的信号传输方向,所述第二芯片模块212通过所述第二导通路径2121 控制所述第二驱动器213中的信号传输方向会花费相应的时间,但是与背景技术的所述第一 芯片模块112通过所述第一线路1112将所述第一设备1’即将开启高速信号传输的讯息及高 速信号传输的方向告诉所述第一驱动模块1132,所述第二芯片模块212会通过所述第二线路 1113将所述第二设备2’即将开启高速信号传输的讯息及高速信号传输的方向告诉所述第二 驱动模块2132相比还是节约了时间。故即使所述第一设备1’或者所述第二设备2’分别告 知所述第一芯片模块112及所述第二芯片模块212所述第一设备1’或者所述第二设备2’即 将开启高速传输的讯息及高速信号的方向后,就马上开始传输高速信号。此时,由于所述第 一驱动器113及所述第二驱动器213均打开了其内部的传输通道,故所述第一设备1’与所 述第二设备2’之间的高速传输信号能通过所述连接线A进行传递。

(2)所述第一逻辑电源111用于调整所述供电线路6传输至所述第一逻辑电源111内的 电源的电压,且所述第一逻辑电源111将调整后的电源分别传输至所述第一芯片模块112及 所述第一驱动模块1132;所述第二逻辑电源211用于调整所述供电线路6传输至所述第二逻 辑电源211内的电源的电压,且所述第二逻辑电源211将调整后的电源分别传输至所述第二 芯片模块212及所述第二驱动模块2132。如此,即使所述供电线路6在传输电源的时候会有 电源的损耗而导致电源电压小于所述第一芯片模块112、所述第一驱动模块1132、所述第二 芯片模块212、所述第二驱动模块2132所需要的电源电压,或者所述供电线路6的电源电压 大于所述第一芯片模块112、所述第一驱动模块1132、所述二芯片模块、所述第二驱动模块 2132所需要的电源电压。经过所述第一逻辑电源111及所述第二逻辑电源211的调整之后, 使得所述供电线路6供给第一芯片模块112、所述第一驱动模块1132、所述第二芯片模块212、 所述第二驱动模块2132的电源电压与其所需的电源电压大小一致所述,从而避免了所述第一 芯片模块112、所述第一驱动模块1132、所述第二芯片模块212、所述第二驱动模块2132接 收到的电源电压与其所需要的电源电压大小不一致,而影响所述连接线A的信号传输的问题 发生。

(3)所述第一芯片模块112通过所述第三导通路径1122告知所述第一驱动器113将所 述第一芯片模块112传输至所述第一驱动器113的信号放大,所述第二芯片模块212通过所 述第四导通路径2122告知所述第二驱动器213将所述第二芯片模块212传输至所述第二驱动 器213的信号放大。如此,使得增大所述第一驱动器113及所述第二驱动器213内信号的强 度,有利于高频信号的传输。

以上详细说明仅为本发明之较佳实施例的说明,非因此局限本发明的专利范围,所以, 凡运用本创作说明书及图示内容所为的等效技术变化,均包含于本发明的专利范围内。