显示装置

文献发布时间:2023-06-19 19:23:34

技术领域

本发明涉及一种显示装置。

背景技术

随着多媒体的发展,显示装置的重要性正在增加。响应于此,诸如有机发光显示装置(Organic Light Emitting Display)、液晶显示装置(LCD:Liquid Crystal Display)等多种种类的显示装置正在被投入使用。

作为将显示装置的图像显示的装置,存在包括发光元件的自发光显示装置。自发光显示装置作为发光元件,有使用有机物作为发光物质的有机发光显示装置或者使用无机物作为发光物质的无极发光显示装置等。

发明内容

本发明所要解决的技术问题在于,提供一种包括具有沿彼此不同方向延伸的形状的电极且防止电短路的显示装置。

本发明的技术问题并不局限于以上所提及的技术问题,未提及的其他技术问题可以通过以下记载被本领域技术人员明确地理解。

用于解决上述技术问题的根据一实施例的显示装置包括:第一电极,布置在基板上,并沿第一方向延伸;多个第二电极,隔着所述第一电极而与所述第一电极沿第二方隔开;多个发光元件,布置在所述第一电极和所述第二电极上;堤层,沿所述第一方向和所述第二方向延伸,并围绕布置有所述发光元件的发光区域、布置在所述发光区域的所述第一方向的一侧的第一子区域以及布置在所述发光区域的所述第一方向的另一侧的第二子区域;以及多个连接电极,布置在所述第一电极和所述第二电极中的至少一个上,并与所述发光元件电连接,其中,所述第二电极与所述堤层重叠,并包括沿所述第一方向延伸的电极杆部以及从所述电极杆部分支而一部分布置在所述发光区域内的多个电极分支部,所述连接电极包括:第一连接电极,布置在所述第一电极上,与所述堤层中布置在所述发光区域的上侧的上侧堤部重叠,并且一部分布置在所述第一子区域;第二连接电极,布置在所述多个第二电极中的一个的第一电极分支部上,与所述堤层中布置在所述发光区域的下侧的下侧堤部重叠,并且一部分布置在所述第二子区域;以及第三连接电极,横跨所述多个第二电极中的另一第二电极的第二电极分支部和所述第一电极上而布置,并围绕所述第一连接电极的一部分。

所述第一连接电极可以与所述堤层的所述下侧堤部沿所述第一方向隔开,所述第二电极与所述堤层的所述上侧堤部沿所述第一方向隔开。

所述第三电极可以包括:布置在所述第二电极的所述第二电极分支部上的第一延伸部;布置在所述第一电极上并与所述第一连接电极隔开的第二延伸部;以及连接所述第一延伸部和所述第二延伸部的第一连接部,其中,所述第一连接部布置在所述堤层的所述下侧堤部上。

所述第一延伸部和所述第二延伸部可以分别与所述堤层的所述上侧堤部沿所述第一方向隔开。

还可以包括布置在所述第一电极和所述第二电极上的第一绝缘层、布置在所述发光元件上的第二绝缘层以及布置在所述第二绝缘层上的第三绝缘层,其中,所述发光元件布置在所述第一绝缘层与第二绝缘层之间,所述第一连接电极和所述第二连接电极布置在所述第三绝缘层上,所述第三连接电极布置在所述第二绝缘层与所述第三绝缘层之间。

所述第一连接电极和所述第二连接电极可以布置在所述第二绝缘层与所述第三绝缘层之间,所述第三连接电极布置在所述第三绝缘层上。

所述第一连接电极可以布置在所述第一子区域,并通过贯通所述第一绝缘层、所述第二绝缘层以及所述第三绝缘层而暴露所述第一电极的一部分的第一接触部来接触于所述第一电极,并且所述第二连接电极可以布置在所述第二子区域,并通过贯通所述第一绝缘层、所述第二绝缘层以及所述第三绝缘层而暴露所述第二电极的一部分的第二接触部来接触于所述第二电极。

所述第一电极可以从所述第一子区域横跨所述发光区域和所述第二子区域而布置,并且布置于在与所述堤层的所述上侧堤部重叠的部分中形成的第一电极接触孔上,所述第二电极布置于在所述堤层中的沿所述第一方向延伸的部分中形成的第二电极接触孔上。

显示装置还可以包括:布置在所述基板与所述第一电极之间的第一堤图案以及分别布置在所述基板与所述多个第二电极之间的多个第二堤图案,其中,所述第一堤图案与所述堤层的沿所述第一方向延伸的部分不重叠,所述多个第二堤图案分别与所述堤层的沿所述第一方向延伸的部分重叠。

所述发光元件可以包括:第一发光元件,布置在所述第一堤图案和所述多个第二堤图案中一个之间,包括布置在所述第一电极和所述第二电极的所述第二电极分支部上;以及第二发光元件,布置在所述第一堤图案和所述多个第二堤图案中的另一个之间,并布置在所述第一电极和所述第二电极的所述第一电极分支部上,其中,所述第一连接电极与所述第一发光元件的第一端部接触,所述第二连接电极与所述第二发光元件的第二端部接触,所述第三连接电极与所述第一发光元件的第二端部和所述第二发光元件的第一端部分别接触。

其他实施例的具体事项包括在详细的说明书及附图中。

在根据实施例的显示装置中,布置在一个子像素的彼此不同的连接电极可以沿彼此不同方向延伸并越过堤层而布置。据此,彼此不同的连接电极可以防止因残留在堤层侧表面的残渣而导致的电短路,显示装置可以防止子像素的发光不良。

根据实施例的效果并不局限于以上举例示出的内容,更加多样的效果包括在本说明书内。

附图说明

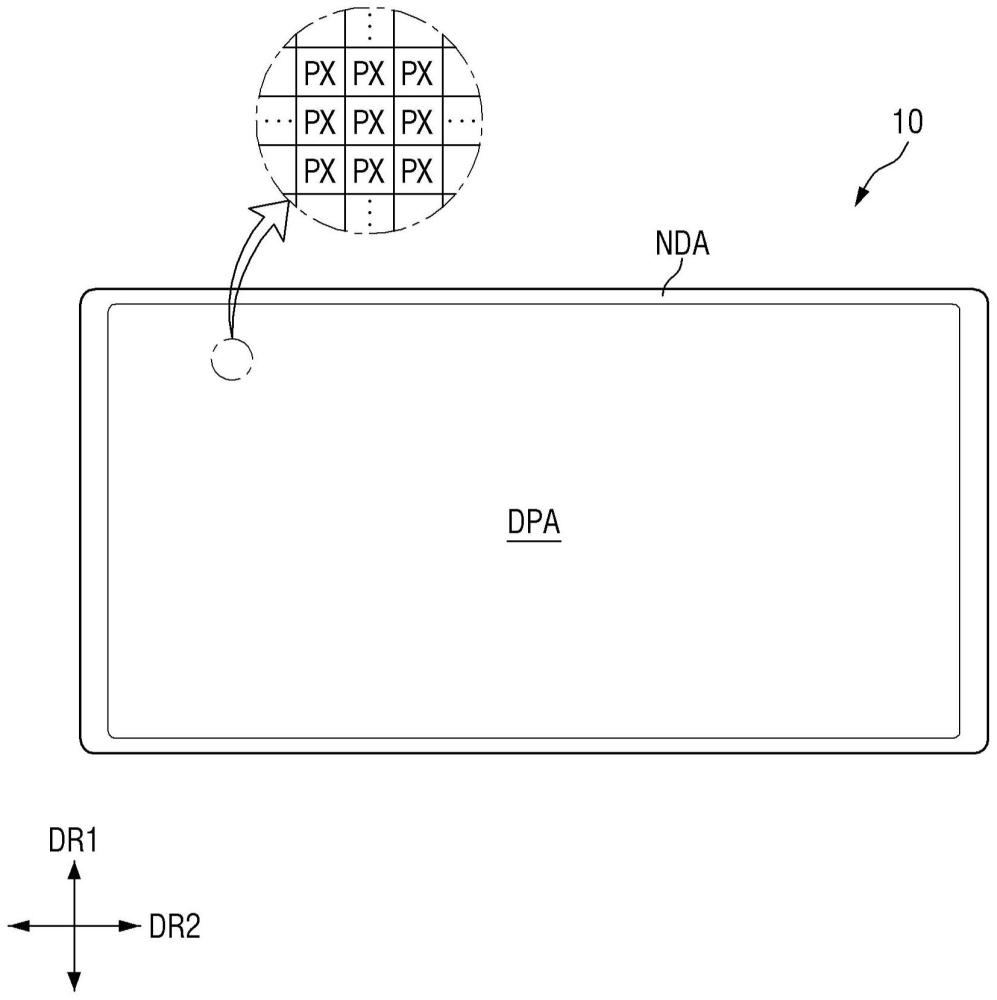

图1是根据一实施例的显示装置的示意性的平面图。

图2是示出包括于根据一实施例的显示装置的多条布线的布置的平面图。

图3是根据一实施例的显示装置的一子像素的等效电路图。

图4是示出根据一实施例的显示装置的一像素的平面图。

图5是示出包括于图4的一像素的电极的布置的平面图。

图6是示出包括于图4的一像素的连接电极的布置的平面图。

图7是示出图4的一子像素的平面图。

图8是沿图7的E1-E1'线截取的剖视图。

图9是沿图7的E2-E2'线截取的剖视图。

图10是沿图7的E3-E3'线截取的剖视图。

图11是图6的A部分的放大图。

图12是根据一实施例的发光元件的示意图。

图13是示出根据另一实施例的显示装置的一子像素的平面图。

图14是沿图13的E4-E4'线截取的剖视图。

图15是沿图13的E5-E5'线和E6-E6'线截取的剖视图。

图16是示出根据另一实施例的显示装置的一子像素的平面图。

图17是沿图16的E8-E8'线截取的剖视图。

图18是沿图16的E9-E9'线和E10-E10'线截取的剖视图。

附图标记说明

10:显示装置

SUB:基板

RME:电极

VIA:过孔层

PAS1、PAS2、PAS3:第一绝缘层至第三绝缘层

BP1、BP2:堤图案

BNL:堤层

ED:发光元件

CNE:连接电极

具体实施方式

参照与附图一起详细后述的实施例,可以明确本发明的优点和特征以及达成这些的方法。然而本发明可以实现为互不相同的多种形态,并不局限于以下公开的实施例,本实施例仅用于使本发明的公开完整并且向本发明所属技术领域中具有普通知识的人完整地告知发明范围而被提供,本发明仅由权利要求的范围而被定义。

提及元件(elements)或者层在其他元件或者层“上(on)”的情形包括在其他元件的紧邻的上方的情形或者在中间夹设有其他层或者其他元件的情形。与此相同,被称为“下(Below)”、“左(Left)”以及“右(Right)”的情况包括与其他元件直接相邻地夹设的情况或者在中间夹设其他层或其他材料的情况。贯穿整个说明书,相同的附图标记指相同的构成要素。

虽然第一、第二等用于叙述多种构成要素,但这些构成要素显然不受限于这些术语。这些术语仅用于将一个构成要素与另一构成要素进行区分。因此,以下提及的第一构成要素在本发明的技术思想内,显然也可以是第二构成要素。

以下,参照附图对具体实施例进行说明。

图1是根据一实施例的显示装置的示意性的平面图。

参照图1,显示装置10显示视频或静止图像。显示装置10可以指提供显示画面的所有电子装置。例如,显示装置10可以包括提供显示画面的电视、笔记本计算机、监视器、广告牌、物联网装置、移动电话、智能电话、平板个人计算机(PC:Personal Computer)、电子手表、智能手表、手表电话、头戴式显示器、移动通信终端、电子记事本、电子书、便携式多媒体播放器(PMP:Portable Multimedia Player)、导航仪、游戏机、数码相机、摄像机等。

显示装置10包括提供显示画面的显示面板。显示面板的示例可以包括无机发光二极管显示面板、有机发光显示面板、量子点发光显示面板、等离子体显示面板、场发射显示面板等。以下,作为显示面板的一例,例示了应用无机发光二极管显示面板的情形,但并不限定于此,只要能够应用相同的技术思想,则也可以应用其他显示面板。

显示装置10的形状可以多样地变形。例如,显示装置10可以具有横向长度长的矩形,纵向长度长的矩形、正方形、角部(顶角)圆滑的四边形、其他多边形、圆形等形状。显示装置10的显示区域DPA的形状也可以与显示装置10的整体形状类似。在图1中,例示了在第二方向DR2上的长度长的矩形形状的显示装置10。

显示装置10可以包括显示区域DPA和非显示区域NDA。显示区域DPA是能够显示画面的区域,非显示区域NDA是不显示画面的区域。显示区域DPA也可以被称为有效区域,非显示区域NDA也可以被称为非有效区域。显示区域DPA可以大致占据显示装置10的中央。

显示区域DPA可以包括多个像素PX。多个像素PX可以沿行列方向排列。各个像素PX的形状在平面上可以为矩形或正方形,但并不限定于此,也可以是各个边相对于一方向倾斜的菱形形状。各个像素PX可以排列为条纹型或岛型。并且,像素PX中的每一个可以包括一个以上的发出特定波长带的光的发光元件而显示特定颜色。

显示区域DPA的周边可以布置有非显示区域NDA。非显示区域NDA可以将显示区域DPA全部或者局部地围绕。显示区域DPA可以是矩形形状,非显示区域NDA可以布置为与显示区域DPA的四个边相邻。非显示区域NDA可以构成显示装置10的边框。在各个非显示区域NDA中,可以布置有包括在显示装置10中的布线或电路驱动部,或者贴装有外部装置。

图2是示出包括于根据一实施例的显示装置的多条布线的布置的平面图。

参照图2,显示装置10可以包括多条布线。显示装置10可以包括多条扫描线SL(SL1、SL2、SL3)、多条数据线DTL(DTL1、DTL2、DTL3)、初始化电压布线VIL以及多条电压布线VL(VL1、VL2、VL3、VL4)等。虽未在附图中示出,但显示装置10中还可布置有其他布线。

第一扫描线SL1和第二扫描线SL2可以沿第一方向DR1延伸而布置。第一扫描线SL1和第二扫描线SL2可以布置为彼此相邻的状态,并且与其他第一扫描线SL1和第二扫描线SL2沿第二方向DR2隔开布置。第一扫描线SL1和第二扫描线SL2可以与连接于扫描驱动部(未图示)的扫描布线垫WPD_SC相连接。第一扫描线SL1和第二扫描线SL2可以从布置在非显示区域NDA的垫区域PDA延伸至显示区域DPA而布置。

第三扫描线SL3可以沿第二方向DR2延伸而布置,并且与其他第三扫描线SL3沿第一方向隔开布置。一条第三扫描线SL3可以与一条以上的第一扫描线SL1或者一条以上的第二扫描线SL2连接。在一实施例中,第一扫描线SL1和第二扫描线SL2可以利用布置在与第三扫描线SL3不同层的导电层构成。多条扫描线SL可以在显示区域DPA的整个表面具有网络(Mesh)结构,但并不限定于此。

另外,在本说明书中,“连接”的含义不仅可以表示一个部件与另一部件通过相互物理接触而连接,而且也可以表示通过其他部件而连接。此外,可以理解为,作为一体化的一个部件,一部分和另一部分由于一体化的部件而相互连接。进一步地,一个部件与另一部件的连接可以被解释为,除了直接接触的连接以外还包括通过另一部件的电连接的含义。

数据线DTL可以沿第一方向DR1延伸而布置。数据线DTL包括第一数据线DTL1、第二数据线DTL2以及第三数据线DTL3,第一数据线至第三数据线DTL1、DTL2、DTL3的各一条形成一个组而彼此邻近地布置。各条数据线DTL1、DTL2、DTL3可以布置为从布置在非显示区域NDA的垫区域PDA延伸至显示区域DPA。但并不限定于此,数据线DTL可以在后述的第一电压布线VL1与第二电压布线VL2之间以等间隔隔开而布置。

初始化电压布线VIL可以沿第一方向DR1延伸而布置。初始化电压布线VIL可以布置在数据线DTL与第一扫描线SL1和第二扫描线SL2之间。初始化电压布线VIL可以布置为从布置在非显示区域NDA的垫区域PDA延伸至显示区域DPA。

第一电压布线VL1和第二电压布线VL2沿第一方向DR1延伸而布置,第三电压布线VL3和第四电压布线VL4沿第二方向DR2延伸而布置。第一电压布线VL1和第二电压布线VL2可以沿第二方向DR2交替布置,并且第三电压布线VL3和第四电压布线VL4沿第一方向DR1交替布置。第一电压布线VL1和第二电压布线VL2可以沿第一方向DR1延伸并横穿显示区域DPA而布置,并且第三电压布线VL3和第四电压布线VL4各自的一部分布线布置在显示区域DPA,其他布线可以布置在位于显示区域DPA的第一方向DR1两侧的非显示区域NDA。第一电压布线VL1和第二电压布线VL2可以利用布置在与第三电压布线VL3和第四电压布线VL4不同层的导电层构成。第一电压布线VL1可以与至少一条第三电压布线VL3连接,第二电压布线VL2可以与至少一条第四电压布线VL4连接,从而电压布线VL可以在显示区域DPA整个表面上具有网络(Mesh)结构。然而,本发明不限于此。

第一扫描线SL1、第二扫描线SL2、数据线DTL、初始化电压布线VIL、第一电压布线VL1和第二电压布线VL2可以与至少一条布线垫WPD电连接。各条布线垫WPD可以布置于非显示区域NDA。根据一实施例,各条布线垫WPD可以布置于位于作为显示区域DPA的第一方向DR1的另一侧的下侧的垫区域PDA。第一扫描线SL1和第二扫描线SL2连接于布置在垫区域PDA的扫描布线垫WPD_SC,数据线DTL中的每一个连接于彼此不同的数据布线垫WPD_DT。初始化电压布线VIL连接于初始化布线垫WPD_Vint,第一电压布线VL1连接于第一电压布线垫WPD_VL1,而且第二电压布线VL2连接于第二电压布线垫WPD_VL2。外部装置可以贴装于布线垫WPD上。外部装置可以通过各向异性导电膜、超声波接合等而被贴装在布线垫WPD上。在附图中,例示了各条布线垫WPD布置在布置于显示区域DPA的下侧的垫区域PDA的情形,但并不限定于此。多条布线垫WPD中的一部分也可以布置在显示区域DPA的上侧或者左右侧中的任一区域。

显示装置10的各个像素PX或者子像素SPXn(n是1至3的整数)包括像素驱动电路。上述的布线可以在穿过各个像素PX或其周围的同时向各个像素驱动电路施加驱动信号。像素驱动电路可以包括晶体管和电容器。各个像素驱动电路的晶体管和电容器的数量可以多样地变形。根据一实施例,显示装置10的各个子像素SPXn可以为像素驱动电路包括三个晶体管和一个电容器的3T1C结构。以下将3T1C结构作为示例而对像素驱动电路进行说明,但并不限定于此,也可以应用2T1C结构、7T1C结构、6T1C结构等其他多样的变形结构。

图3是根据一实施例的显示装置的一子像素的等效电路图。

参照图3,除了发光二极管EL之外,根据一实施例的显示装置10的各个子像素SPXn还可以包括三个晶体管T1、T2、T3和一个存储电容器Cst。

发光二极管EL根据通过第一晶体管T1供应的电流而发光。发光二极管EL可以包括第一电极、第二电极以及布置于它们之间的至少一个发光元件。所述发光元件可以借由从第一电极和第二电极传输的电信号而发出特定波长带的光。

发光二极管EL的一端可以连接于第一晶体管T1的源电极,另一端可以连接于供应比第一电压布线VL1的高电位电压(以下,称为第一电源电压)低的低电位电压(以下,称为第二电源电压)的第二电压布线VL2。

第一晶体管T1根据栅电极与源电极的电压差来调节从供应第一电源电压的第一电压布线VL1流向发光二极管EL的电流。作为一例,第一晶体管T1可以是用于驱动发光二极管EL的驱动晶体管。第一晶体管T1的栅电极可以连接于第二晶体管T2的源电极,源电极连接于发光二极管EL的第一电极,并且漏电极连接于施加第一电源电压的第一电压布线VL1。

第二晶体管T2被第一扫描线SL1的扫描信号导通而将数据线DTL连接至第一晶体管T1的栅电极。第二晶体管T2的栅电极可以连接于第一扫描线SL1,源电极连接于第一晶体管T1的栅电极,并且漏电极连接于数据线DTL。

第三晶体管T3被第二扫描线SL2的扫描信号导通而将初始化电压布线VIL连接于发光二极管EL的一端。第三晶体管T3的栅电极可以连接于第二扫描线SL2,漏电极连接于初始化电压布线VIL,并且源电极连接于发光二极管EL的一端或者第一晶体管T1的源电极。

虽然在附图中示出了第二晶体管T2和第三晶体管T3的栅电极中的每一个与彼此不同的扫描线SL1、SL2电连接的情形,但并不限定于此。在若干实施例中,第二晶体管T2和第三晶体管T3的栅电极可以分别与彼此相同的扫描线电连接。

在一实施例中,各个晶体管T1、T2、T3的源电极和漏电极不限于上述的情况,也可以是与此相反的情况。此外,晶体管T1、T2、T3中的每一个可以利用薄膜晶体管(thin filmtransistor)形成。此外,在图3中,以各个晶体管T1、T2、T3利用n型金属氧化物半导体场效应晶体管(MOSFET:Metal Oxide Semiconductor Field Effect Transistor)形成的情况为中心进行了说明,但并不限定于此。即,各个晶体管T1、T2、T3可以利用p型MOSFET形成,或者也可以为一部分由N型MOSFET形成,另一部分利用p型MOSFET形成。

存储电容器Cst形成于第一晶体管T1的栅电极与源电极之间。存储电容器Cst存储第一晶体管T1的栅电极电压与源电极电压的电压差。

以下,进一步参照其他附图对根据一实施例的显示装置10的一像素PX的结构进行详细说明。

图4是示出根据一实施例的显示装置的一像素的平面图。图4示出了布置在显示装置10的一像素PX的电极RME(RME1、RME2)、堤图案BP和堤层BNL、多个发光元件ED(ED1、ED2)以及连接电极CNE(CNE1、CNE2、CNE3)的平面布置。

参照图4,显示装置10的多个像素PX中的每一个可以包括多个子像素SPXn。例如,一个像素PX可以包括第一子像素SPX1、第二子像素SPX2以及第三子像素SPX3。第一子像素SPX1可以发出第一颜色的光,第二子像素SPX2可以发出第二颜色的光,第三子像素SPX3可以发出第三颜色的光。作为一例,第一颜色可以是蓝色,第二颜色可以是绿色,第三颜色可以是红色。然而,并不限定于此,各个子像素SPXn也可以发出相同颜色的光。作为一实施例,各个子像素SPXn可以发出蓝色的光。在附图中,例示了一个像素PX包括三个子像素SPXn的情形,但并不限定于此,像素PX可以包括更多数量的子像素SPXn。

显示装置10的各个子像素SPXn可以包括发光区域EMA及非发光区域。发光区域EMA可以是布置有发光元件ED而射出特定波长带的光的区域。非发光区域可以是未布置发光元件ED且从发光元件ED发出的光未到达而不射出光的区域。

发光区域EMA可以包括布置有发光元件ED的区域以及作为与发光元件ED邻近的区域的从发光元件ED发出的光射出的区域。发光区域EMA还可以包括从发光元件ED发出的光被另一部件反射或折射而射出的区域。多个发光元件ED可以布置在各个子像素SPXn,并且可以形成包括布置有它们的区域和与其邻近的区域的发光区域。

在附图中例示了各个子像素SPXn的发光区域EMA具有彼此相同的面积的情形,但并不限定于此。在若干实施例中,各个子像素SPXn的各个发光区域EMA还可以根据从布置于对应子像素的发光元件ED发出的光的颜色或波长带而具有彼此不同的面积。

各个子像素SPXn还可以包括布置在非发光区域的子区域SA1、SA2。相应的子像素SPXn的第一子区域SA1可以布置在作为发光区域EMA的第一方向DR1上的一侧的上侧,第二子区域SA2可以布置在作为发光区域EMA的第一方向DR1上的另一侧的下侧。发光区域EMA和子区域SA1、SA2可以沿第一方向DR1交替排列,在以第一方向DR1隔开的彼此不同的子像素SPXn的发光区域EMA之间可以布置有第一子区域SA1或者第二子区域SA2。例如,发光区域EMA和子区域SA1、SA2彼此可以在第一方向DR1上交替排列,发光区域EMA和子区域SA1、SA2中的每一个可以在第二方向DR2上反复排列。然而,并不限定于此,在多个像素PX中,发光区域EMA和子区域SA还可以具有与图4不同的排列。

子区域SA1、SA2未布置有发光元件ED,从而不会射出光,但可以布置有布置在各个子像素SPXn的电极RME的一部分。布置在彼此不同的子像素SPXn的电极RME可以通过子区域SA1、SA2的分离部ROP1、ROP2彼此分离而布置。

布置在各个像素PX并与发光二极管EL接触的电路层的布线和电路元件可以分别与第一子像素至第三子像素SPX1、SPX2、SPX3连接。然而,所述布线与电路元件可以不与各个子像素SPXn或者发光区域EMA的所占的区域相对应地布置,而是在一个像素PX内与发光区域EMA的位置无关地布置。

堤层BNL可以布置为围绕多个子像素SPXn以及发光区域EMA和子区域SA1、SA2。堤层BNL可以布置在沿第一方向DR1和第二方向DR2相邻的子像素SPXn的边界,还可以布置在发光区域EMA和子区域SA1、SA2的边界。显示装置10的子像素SPXn、发光区域EMA以及子区域SA1、SA2可以是借由堤层BNL的布置而得以区分的区域。多个子像素SPXn和发光区域EMA以及子区域SA1、SA2之间的间隔可以根据堤层BNL的宽度而不同。

堤层BNL可以包括在平面上沿第一方向DR1以及第二方向DR2延伸的部分,从而在显示区域DPA的整个表面布置为格子形图案。堤层BNL可以跨过各个子像素SPXn的边界而布置,从而区分相邻的子像素SPXn。此外,堤层BNL可以布置为围绕布置在各个子像素SPXn的发光区域EMA和子区域SA,从而区分它们。

图5是示出包括于图4的一像素的电极的布置的平面图。图6是示出包括于图4的一像素的连接电极的布置的平面图。图7是示出图4的一子像素的平面图。图8是沿图7的E1-E1'线截取的剖视图。图9是沿图7的E2-E2'线截取的剖视图。图10是沿图7的E3-E3'线截取的剖视图。

图5和图6分别是示出布置在一像素PX的电极RME以及连接电极CNE的相对布置的平面图。图8示出了将布置在一子像素SPXn的发光元件ED1、ED2的两端部横穿的剖面。图9和图10分别示出了将布置在一子像素SPXn的电极接触孔CTD、CTS、CTA以及接触部CT1、CT2横穿的剖面。

结合图4而参照图5和图6,显示装置10可以包括布置在第一基板SUB和其之上的半导体层、多个导电层以及多个绝缘层。此外,显示装置10可以包括多个电极RME(RME1、RME2)、发光元件ED(ED1、ED2)以及连接电极CNE(CNE1、CNE2、CNE3)。所述半导体层、导电层以及绝缘层分别可以构成显示装置10的电路层。

第一基板SUB可以是绝缘基板。第一基板SUB可以利用玻璃、石英或高分子树脂等的绝缘物质构成。此外,第一基板SUB可以是刚性(Rigid)基板,但也可以是能够实现弯曲(Bending)、折叠(Folding)、卷曲(Rolling)等的柔性(Flexible)基板。第一基板SUB可以包括显示区域DPA和围绕显示区域DPA的非显示区域NDA,显示区域DPA可以包括作为发光区域EMA和非发光区域中的一部分的子区域SA。

第一导电层可以布置于第一基板SUB上。第一导电层包括下部金属层BML,下部金属层BML被布置为与第一晶体管T1的第一有源层ACT1重叠。下部金属层BML可以防止光入射到第一晶体管T1的第一有源层ACT1,或者与第一有源层ACT1电连接,以执行使第一晶体管T1的电特性稳定化的功能。然而,可以省略下部金属层BML。

缓冲层BL可以布置在下部金属层BML和第一基板SUB上。缓冲层BL形成于第一基板SUB上,以保护像素PX的晶体管免受通过易于渗透湿气的第一基板SUB渗透的水分的影响,并且可以执行表面平坦化功能。

半导体层布置在缓冲层BL上。半导体层可以包括第一晶体管T1的第一有源层ACT1以及第二晶体管T2的第二有源层ACT2。第一有源层ACT1和第二有源层ACT2可以布置为与后述的第二导电层的第一栅电极G1和第二栅电极G2局部地重叠。

半导体层可以包括多晶硅、单晶硅、氧化物半导体等。在另一实施例中,半导体层也可以仅包括多晶硅。所述氧化物半导体可以是含铟(In)的氧化物半导体。例如,所述氧化物半导体可以是铟锡氧化物(ITO:Indium Tin Oxide)、铟锌氧化物(IZO:Indium ZincOxide)、铟镓氧化物(IGO:Indium Gallium Oxide)、铟锌锡氧化物(IZTO:Indium Zinc TinOxide)、铟镓锡氧化物(IGTO:Indium Gallium Tin Oxide)、铟镓锌氧化物(IGZO:IndiumGallium Zinc Oxide)、铟镓锌锡氧化物(IGZTO:Indium Gallium Zinc Tin Oxide)中的至少一个。

在附图中,例示了在显示装置10的子像素SPXn布置有一个第一晶体管T1的情形,但并不限定于此,显示装置10可以包括更多数量的晶体管。

第一栅极绝缘层GI可以在显示区域DPA中布置于半导体层上。第一栅极绝缘层GI可以不布置在垫区域PDA。可以起到各个晶体管T1、T2的栅极绝缘膜的作用。在附图中,例示了第一栅极绝缘层GI与后述的第二导电层的栅电极G1、G2一起图案化,从而在第二导电层与半导体层的有源层ACT1、ACT2之间局部地布置的情形,但并不限定于此。在若干实施例中,第一栅极绝缘层GI也可以布置在缓冲层BL的整个面上。

第二导电层可以布置在栅极绝缘层GI上。第二导电层可以包括第一晶体管T1的第一栅电极G1和第二晶体管T2的第二栅电极G2。第一栅电极G1可以布置为在作为厚度方向的第三方向DR3上与第一有源层ACT1的沟道区域重叠,第二栅电极G2可以布置为在作为厚度方向的第三方向DR3上与第二有源层ACT2的沟道区域重叠。虽未在附图中示出,第二导电层还可以包括存储电容器的一个电极。

第一层间绝缘层IL1可以布置在第二导电层上。第一层间绝缘层IL1可以在第二导电层与布置于其上的其他层之间执行绝缘膜的功能,并保护第二导电层。

第三导电层可以布置在第一层间绝缘层IL上。第三导电层可以包括布置在显示区域DPA的第一电压布线VL1和第二电压布线VL2以及第一导电图案CDP1和各个晶体管T1、T2的源电极S1、S2以及漏电极D1、D2。虽未在附图中示出,第三导电层还可以包括存储电容器的另一个电极。

第一电压布线VL1可以被施加传输至第一电极RME1的高电位电压(或者第一电源电压),并且第二电压布线VL2可以被施加传输至第二电极RME2的低电位电压(或者第二电源电压)。第一电压布线VL1的一部分可以通过贯通第一层间绝缘层IL1和第一栅极绝缘层GI的接触孔而与第一晶体管T1的第一有源层ACT1接触。第一电压布线VL1可以起到第一晶体管T1的第一漏电极D1的作用。第二电压布线VL2可以直接连接于后述的第二电极RME2。

第一导电图案CDP1可以通过贯通第一层间绝缘层IL1和第一栅极绝缘层GI的接触孔而与第一晶体管T1的第一有源层ACT1接触。第一导电图案CDP1可以通过另一接触孔而与下部金属层BML接触。第一导电图案CDP1可以起到第一晶体管T1的第一源电极S1的作用。此外,第一导电图案CDP1可以电连接后述的第一电极RME1或者第一连接电极CNE1。第一晶体管T1可以将从第一电压布线VL1施加的第一电源电压传输至第一电极RME1或者第一连接电极CNE1。

第二源电极S2和第二漏电极D2分别可以通过贯通第一层间绝缘层IL1和第一栅极绝缘层GI的接触孔与第二晶体管T2的第二有源层ACT2接触。第二晶体管T2可以是上文中参照图3而描述的开关晶体管中的一个。第二晶体管T2可以将从图3的数据线DTL施加的信号传输至第一晶体管T1,或者将从图3的初始化电压布线VIL施加的信号传输至存储电容器的另一电极。

第一保护层PV1布置在第三导电层上。第一保护层PV1在第三导电层与其他的层之间执行绝缘膜的功能,并保护第三导电层。

上述的缓冲层BL、第一栅极绝缘层GI、第一层间绝缘层IL1以及第一保护层PV1可以利用交替层叠的多个无机层构成。例如,缓冲层BL、第一栅极绝缘层GI、第一层间绝缘层IL1以及第一保护层PV1可以形成为包含硅氧化物(SiO

过孔层VIA在显示区域DPA中布置在第三导电层上。过孔层VIA包括有机绝缘物质(例如,聚酰亚胺(PI)之类的有机绝缘物质),以补偿由于下部导电层而形成的台阶,并且可以平坦地形成上表面。然而,在若干实施例中,可以省略过孔层VIA。

显示装置10作为布置在过孔层VIA上的显示元件层,可以包括堤图案BP1、BP2、多个电极RME(RME1、RME2)和堤层BNL、多个发光元件ED(ED1、ED2)和多个连接电极CNE(CNE1、CNE2、CNE3)。此外,显示装置10可以包括布置在过孔层VIA上的第一绝缘层PAS1、第二绝缘层PAS2以及第三PAS3。

多个堤图案BP1、BP2可以布置在各个子像素SPXn的发光区域EMA。堤图案BP1、BP2可以具有沿第二方向DR2具有预定宽度并沿第一方向DR1延伸的形状。多个堤图案BP1、BP2可以具有沿第一方向DR1延伸的形状,且在第二方向DR2上测量的宽度可以彼此不同,一个堤图案BP1、BP2可以横跨沿第二方向DR2相邻的子像素SPXn而布置。

例如,堤图案BP1、BP2可以包括布置在各个子像素SPXn的发光区域EMA内的第一堤图案BP1以及横跨彼此不同的子像素SPXn的发光区域EMA而布置的第二堤图案BP2。

第一堤图案BP1布置在发光区域EMA的中心部,第二堤图案BP2隔着第一堤图案BP1而布置且与第一堤图案BP1相隔开。第一堤图案BP1和第二堤图案BP2可以沿第二方向DR2彼此交替地布置。发光元件ED可以布置在隔开的第一堤图案BP1与第二堤图案BP2之间。

第一堤图案BP1和第二堤图案BP2在第一方向DR1上的长度可以彼此相同,但沿第二方向DR2测量的宽度可以彼此不同。堤层BNL中的沿第一方向DR1延伸的部分可以在厚度方向上与第二堤图案BP2重叠。第一堤图案BP1可以布置为与第一电极RME1重叠,第二堤图案BP2可以布置为与第二电极RME2的电极分支部RM_B1、RM_B2以及堤层BNL重叠。堤图案BP1、BP2可以在显示区域DPA整个面布置成岛型的图案。

在附图中,例示了布置于各个子像素SPXn的堤图案BP1、BP2具有不同宽度布置的情形,但并不限定于此。堤图案BP1、BP2的数量和形状可以根据电极RME的数量或布置结构而不同。

第一堤图案BP1和第二堤图案BP2在第一方向DR1上的长度可以彼此相同,可以大于堤层BNL所围绕的发光区域EMA在第一方向上的长度。第一堤图案BP1和第二堤图案BP2的一部分可以与堤层BNL中的沿第二方向DR2延伸的部分重叠。然而,并不限定于此,堤图案BP1、BP2可以与堤层BNL一体化,或者与沿堤层BNL的第二方向DR2延伸的部分相隔开。在这种情况下,堤图案BP1、BP2在第一方向DR1上的长度可以等于或小于堤层BNL所围绕的发光区域EMA在第一方向DR1上的长度。

多个堤图案BP1、BP2可以布置在过孔层VIA上。例如,堤图案BP1、BP2可以直接布置在过孔层VIA上,并且可以具有至少一部分以过孔层VIA的上表面为基准而突出的结构。堤图案BP1、BP2的突出的部分可以具有倾斜的或者具有预定曲率而弯曲的侧表面,并且从发光元件ED发出的光可以被布置于堤图案BP1、BP2上的电极RME反射而朝向过孔层VIA的上部方向射出。与附图中示出的情形不同地,堤图案BP1、BP2可以具有在剖面图上的外表面具有预定曲率而弯曲的形状,例如,可以具有半圆或者半椭圆的形状。堤图案BP1、BP2可以包括聚酰亚胺(PI)之类的有机绝缘物质,但并不限定于此。

多个电极RME(RME1、RME2)可以以沿一方向延伸的形状布置于每个子像素SPXn。多个电极RME1、RME2可以沿第一方向DR1延伸而布置于子像素SPXn的发光区域EMA和子区域SA1、SA2,并且它们可以在第二方向DR2上彼此隔开布置。多个电极RME可以电连接于后述的发光元件ED,但并不限定于此,也可以不与发光元件ED电连接。

多个电极RME包括布置在各个子像素SPXn的中心部的第一电极RME1以及横跨彼此不同的子像素SPXn而布置的第二电极RME2。第一电极RME1和第二电极RME2大体上可以具有沿第一方向DR1延伸的形状,并且布置在发光区域EMA的部分的形状可以彼此不同。

第一电极RME1可以布置在子像素SPXn的中心,布置在发光区域EMA的部分可以布置在第一堤图案BP1上。第一电极RME1从第一子区域SA1沿第一方向DR1延伸,并且可以延伸至第二子区域SA2。第一电极RME1可以具有在第二方向DR2上测量的宽度根据位置而变得不同的形状,至少在发光区域EMA中与第一堤图案BP1重叠的部分可以具有比第一堤图案BP1大的宽度。

第二电极RME2可以包括沿第一方向DR1延伸的部分和在发光区域EMA附近分支的部分。在一实施例中,第二电极RME2可以包括沿第一方向DR1延伸的电极杆部RM_S和从电极杆部RM_S分支而沿第二方向DR2弯折,再沿第一方向DR1延伸的多个电极分支部RM_B1、RM_B2。电极杆部RM_S可以布置为与堤层BNL的沿第一方向DR1延伸的部分重叠,可以布置在子区域SA的第二方向DR2上的一侧。电极分支部RM_B1、RM_B2可以在布置于堤层BNL的沿第一方向DR1延伸的部分的电极杆部RM_S中被分支,可以彼此沿第二方向DR2的两侧弯折。电极杆部RM_S可以在堤层BNL的沿第一方向DR1延伸的部分和沿第二方向DR2延伸的部分交叉的部分中由电极分支部RM_B1、RM_B2分离。电极分支部RM_B1、RM_B2可以沿第一方向DR1横穿发光区域EMA而布置,然后再次弯折而连接于电极杆部RM_S。例如,第二电极RME2的电极分支部RM_B1、RM_B2以一个子像素SPXn的发光区域EMA为基准,可以在其上侧分支,然后在其下侧再次彼此连接。

第二电极RME2可以包括布置在第一电极RME1左侧的第一电极分支部RM_B1和布置在第一电极RME1右侧的第二电极分支部RM_B2。包含在一个第二电极RME2的电极分支部RM_B1、RM_B2可以分别布置在沿第二方向DR2相邻的子像素SPXn的发光区域EMA,在一个子像素SPXn中可以布置有彼此不同的第二电极RME2的电极分支部RM_B1、RM_B2。以第一电极RME1为基准,其左侧可以布置有第二电极RME2的第一电极分支部RM_B1,在第一电极RME1的右侧可以布置有另一个第二电极RME2的第二电极分支部RM_B2。

第二电极RME2的各个电极分支部RM_B1、RM_B2可以与第二堤图案BP2的一侧重叠。第一电极分支部RM_B1可以与布置在第一堤图案BP1的左侧的第二堤图案BP2部分重叠,第二电极分支部RM_B2可以与布置在第一堤图案BP1的右侧的第二堤图案BP2部分重叠。第一电极RME1可以与双侧相互不同的第二电极RME2的彼此不同的电极分支部RM_B1、RM_B2隔开并对向,第一电极RME1与各个电极分支部RM_B1、RM_B2之间的间隔可以小于彼此不同的堤图案BP1、BP2之间的间隔。

第一电极RME1的在第二方向DR2上测量的宽度可以大于第二电极RME2的电极杆部RM_S以及电极分支部RM_B1、RM_B2的宽度。第一电极RME1的宽度大于第一堤图案BP1的宽度并且与其两侧重叠,相反第二电极RME2的宽度相对较小,从而电极分支部RM_B1、RM_B2仅可以与第二堤图案BP2的一侧重叠。

布置在堤图案BP1、BP2之间的发光元件ED朝向两端部方向发出光,发出的所述光可以朝向布置在堤图案BP1、BP2上的电极RME。各个电极RME可以具有布置在堤图案BP1、BP2上的部分反射从发光元件ED发出的光的结构。第一电极RME1和第二电极RME2可以布置为至少覆盖堤图案BP1、BP2的一侧表面,从而反射从发光元件ED发出的光。

第一电极RME1和第二电极RME2中的第一电极RME1可以延伸至第一子区域SA1的第一分离部ROP1以及第二子区域SA2的第二分离部ROP2而布置,相反,第二电极RME2可以不与子区域SA1、SA2分离。一个第二电极RME2可以包括多个电极杆部RM_S和电极分支部RM_B1、RM_B2而沿第一方向DR1延伸,并且具有在各个子像素SPXn的发光区域EMA附近分支的形状。第一电极RME1可以布置在布置于各个子像素SPXn的彼此不同的子区域SA1、SA2的分离部ROP1、ROP2之间,并可以横穿发光区域EMA而布置。

根据一实施例,显示装置10可以包括布线连接电极EP,布线连接电极EP布置在各个子像素SPXn的多个子区域SA1、SA2中的第一子区域SA1,且布置在彼此不同的子像素SPXn的第一电极RME1之间。在子像素SPXn的第二子区域SA2可以不布置布线连接电极EP,并且沿第一方向DR1相邻的不同子像素SPXn的第一电极REM1彼此隔开。多个子像素SPXn中,在图7中示出的子像素SPXn中,布置有布线连接电极EP的第一子区域SA1可以布置在发光区域EMA的上侧,第二子区域SA2可以布置在发光区域EMA的下侧。相反,与图7的子像素SPXn沿第一方向DR1相邻的子像素SPXn中,布置有布线连接电极EP的第一子区域SA1可以布置在发光区域EMA的下侧,并且第二子区域SA2可以布置在发光区域EMA的上侧。

第一电极REM1可以在第一子区域SA1中隔着第一分离部ROP1而与布线连接电极EP相隔开。一个第一区域SA1中可以布置有两个第一分离部ROP1,布线连接电极EP可以隔着下侧的第一分离部ROP1而与布置在相应的子像素SPXn的第一电极REM1隔开,并且可以隔着上侧的第一分离部ROP1而与布置在另一子像素SPXn的第一电极REM1相隔开。在第二子区域SA2中可以布置有一个第二分离部ROP2,且彼此不同的第一电极REM1沿第一方向DR1隔开。

根据一实施例,第一电极REM1可以在与堤层BNL的沿第二方向DR2延伸的部分重叠的部分中通过第一电极接触孔CTD与第三导电层的第一导电图案CDP1接触。第一电极REM1可以布置在贯通过孔层VIA以及第一保护层PV1的第一电极接触孔CTD上,并且通过第一电极接触孔CTD与第一导电图案CDP1接触。第二电极REM2可以在电极杆部RM_S中通过第二电极接触孔CTS与第三导电层的第二电压布线VL2接触。第二电极REM2可以布置在贯通过孔层VIA以及第一保护层PV1的第二电极接触孔CTS上,并通过第二电极接触孔CTS与第二电压布线VL2接触。第一电极REM1可以通过第一导电图案CDP1与第一晶体管T1电连接,从而施加第一电源电压,第二电极REM2可以与第二电压布线VL2电连接,从而施加第二电源电压。然而,并不限定于此。根据另一实施例,各个电极RME1、RME2也可以不与第三导电层的电压布线VL1、VL2电连接,而后述的连接电极CNE可以与第三导电层直接连接。

布线连接电极EP可以通过贯通过孔层VIA的第三电极接触孔CTA与第三导电层的第一电压布线VL1连接。布线连接电极EP可以布置在贯通过孔层VIA以及第一保护层PV1的第三电极接触孔CTA上,并通过第三电极接触孔CTA与第一导电图案CDP1接触。第一电极REM1以与布线连接电极EP相连接的状态形成,为布置发光元件ED而施加的电信号从第一电压布线VL1通过布线连接电极EP被施加到第一电极RME1。在布置发光元件ED的工艺中,可以向第一电压布线VL1和第二电压布线VL2施加信号,并且它们可以分别传输到各自的第一电极RME1和第二电极RME2。

另一方面,第一电极接触孔CTD和第二电极接触孔CTS的相对布置可以与第三电极接触孔CTA不同。第一电极接触孔CTD可以布置在第一子区域SA1和第二子区域SA2中,并且第二电极接触孔CTS可以形成为与位于每个子区域SA1、SA2的第二方向DR2的一侧的堤层BNL重叠。相反,第三电极接触孔CTA可以仅布置在第一子区域SA1中。这可以是由于第二电极接触孔CTS和第三电极接触孔CTA分别露出互不相同的电压布线VL1、VL2的上表面,从而与此对应地确定各电极接触孔的位置。即使在分离电极RME的分离部ROP1、ROP2的情况,第一分离部ROP1也可以布置在第一子区域SA1中,并且可以分别在布线连接电极EP的上侧和下侧形成。相反,第二分离部ROP2可以布置在第二子区域SA2中,并且可以布置在第一电极RME1之间。在第一子区域SA1中,可以形成有两个第一分离部ROP1,并且在第二子区域SA2中可以形成有一个第二分离部ROP2。

多个电极RME可以包括反射率高的导电性物质。例如,电极RME可以包括诸如银(Ag)、铜(Cu)、铝(Al)等的金属,或者具有包括铝(Al)、镍(Ni)、镧(La)等的合金,或者钛(Ti)、钼(Mo)以及铌(Nb)等的金属层和所述合金层叠的结构。在若干实施例中,电极RME可以构成为双层或多层,所述双层或多层由包含铝(Al)的合金和钛(Ti)、钼(Mo)及铌(Nb)构成的一层以上的金属层层叠而成。

但并不限定于此,各个电极RME还可以包括透明性导电性物质。例如,各个电极RME可以包括诸如ITO、IZO、ITZO等的材料。在若干实施例中,各个电极RME可以形成透明性导电性物质和反射率高的金属层分别层叠一层以上的结构,或者可以形成为包括它们的一层。例如,各电极RME可以具有ITO/Ag/ITO、ITO/Ag/IZO或者ITO/Ag/ITZO/IZO等的层叠结构。电极RME可以与发光元件ED电连接,并将从发光元件ED发出的光中的一部分向第一基板SUB的上部方向进行反射。

第一绝缘层PAS1可以布置在显示区域DPA的整个面,并且可以布置在过孔层VIA和多个电极RME上。第一绝缘层PAS1可以包括绝缘物质来保护多个电极RME,同时使不同的电极RME彼此绝缘。第一绝缘层PAS1在形成堤层BNL前布置为覆盖电极RME,从而能够在堤层BNL的形成工艺中防止电极RME受损。此外,第一绝缘层PAS1可以防止布置在其上的发光元件ED与其他构件直接接触而被损伤。

作为示例性实施例,第一绝缘层PAS1可以在沿第二方向DR2隔开的电极RME之间以上表面的一部分凹入的方式形成台阶。在形成第一绝缘层PAS1的台阶的上表面上布置有发光元件ED,在发光元件ED与第一绝缘层PAS1之间还可以形成空间。

堤层BNL可以布置在第一绝缘层PAS1上。堤层BNL可以包括沿第一方向DR1和第二方向DR2延伸的部分,并可以围绕各个子像素SPXn。堤层BNL可以围绕各个子像素SPXn的发光区域EMA和子区域SA1、SA2来区分它们,并且可以围绕显示区域DPA的最外侧来区分显示区域DPA和非显示区域NDA。堤层BNL布置在显示区域DPA的整个面而形成格子状图案,在显示区域DPA中堤层BNL所开口的区域可以是发光区域EMA和子区域SA1、SA2。

堤层BNL可以具有与堤图案BP1、BP2类似的预定高度。在若干实施例中,堤层BNL的上表面的高度可以大于堤图案BP1、BP2,其厚度可以等于或大于堤图案BP1、BP2。堤层BNL可以防止在显示装置10的制备工艺中的喷墨印刷工序中墨溢出到相邻的子像素SPXn。堤层BNL可以包括与堤图案BP1、BP2相同的诸如聚酰亚胺的有机绝缘物质。

多个发光元件ED可以布置在发光区域EMA中。发光元件ED布置于彼此不同的堤图案BP1、BP2之间,并且可以彼此沿第一方向DR1隔开而排列。在一实施例中,多个发光元件ED可以具有沿一方向延伸的形状,并且两端部分别布置在彼此不同的电极RME上。发光元件ED的长度可以比沿第二方向DR2隔开的电极RME之间的间隔长。发光元件ED大致可以排列成延伸的方向与电极RME延伸的第一方向DR1垂直。然而,并不限定于此,发光元件ED的延伸方向可以向着第二方向DR2或者与其倾斜的方向而布置。

多个发光元件ED可以在彼此不同的堤图案BP1、BP2之间布置在彼此不同的电极RME上。发光元件ED可以包括第一发光元件ED1和第二发光元件ED2,第一发光元件ED1的两端布置在第一电极RME1和第二电极RME2的第二电极分支部RM_B2上,第二发光元件ED2的两端布置在第一电极RME1和另一个第二电极RME2的第一电极分支部RM_B1上。第一发光元件ED1可以以第一电极RME1为基准布置在右侧,第二发光元件ED2可以以第一电极RME1为基准布置在左侧。第一发光元件ED1可以布置在第一电极RME1和第二电极RME2上,并且第二发光元件ED2可以布置在第一电极RME1和第二电极RME2上。

多个发光元件ED可以布置在第一绝缘层PAS1上。发光元件ED可以具有沿一方向延伸的形状,并且可以布置为延伸的一方向与第一基板SUB的上表面平行。如下所述,发光元件ED可以包括沿着所述延伸的一方向布置的多个半导体层,所述多个半导体层可以沿着与第一基板SUB的上表面平行的方向依次布置。然而,并不限定于此,当发光元件ED具有其他结构的情况下,多个半导体层可以沿着垂直于第一基板SUB的方向布置。

布置在各个子像素SPXn的发光元件ED可以根据上述的半导体层所构成的材料发出彼此不同波长带的光。然而,并不限定于此,布置在各个子像素SPXn的发光元件ED可以包括相同材料的半导体层而发出相同颜色的光。

发光元件ED可以与连接电极CNE(CNE1、CNE2)接触而与电极RME及过孔层VIA下部的导电层电连接,并且施加电信号而发出特定波长带的光。

第二绝缘层PAS2可以布置在多个发光元件ED、第一绝缘层PAS1以及堤层BNL上。第二绝缘层PAS2包括在堤图案BP1、BP2之间沿第一方向DR1延伸而布置在多个发光元件ED上的图案部。所述图案部配置为局部围绕发光元件ED的外面,可以不覆盖发光元件ED的两侧或两端部。所述图案部可以在平面图上的各个子像素SPXn内形成线型或岛型的图案。第二绝缘层PAS2的所述图案部可以在保护发光元件ED的同时在显示装置10的制备工艺中固定发光元件ED。此外,第二绝缘层PAS2可以被布置为填充发光元件ED与其下部的第一绝缘层PAS1之间的空间。此外,第二绝缘层PAS2的一部分可以布置在堤层BNL的上部以及子区域SA。

多个连接电极CNE(CNE1、CNE2、CNE3)可以布置在多个电极RME以及堤图案BP1、BP2上。多个连接电极CNE可以分别具有沿一方向延伸的形状,并且可以彼此隔开布置。各个连接电极CNE可以与发光元件ED接触,并可以电连接到第三导电层。

多个连接电极CNE(CNE1、CNE2、CNE3)可以包括第一连接电极CNE1、第二连接电极CNE2以及第三连接电极CNE3。

第一连接电极CNE1可以具有沿第一方向DR1延伸的形状,并且可以布置在第一电极RME1上。第一连接电极CNE1中布置在第一堤图案BP1上的部分可以与第一电极RME1重叠,并且从第一电极RME1沿第一方向DR1延伸且越过堤层BNL而布置至位于发光区域EMA的上侧的第一子区域SA1。第一连接电极CNE1可以在第一子区域SA1中通过第一接触部CT1与第一电极RME1接触。

第二连接电极CNE2可以具有沿第一方向DR1延伸的形状,并且可以布置在第二电极RME2上。第二连接电极CNE2中布置在第二堤图案BP2上的部分可以与第二电极RME2重叠,并且从第二电极RME2沿第一方向DR1延伸且越过堤层BNL而布置至位于发光区域EMA的上侧的第一子区域SA1。第二连接电极CNE2可以在第二子区域SA2中通过第二接触部CT2与第二电极RME2接触。

第三连接电极CNE3可以包括沿第一方向DR1延伸的延伸部CN_E1、CN_E2以及连接延伸部CN_E1、CN_E2的第一连接部CN_B1。第一延伸部CN_E1在发光区域EMA内与第一连接电极CNE1对向,且布置在第二电极RME2的第二电极分支部RM_B2上,并且第二延伸部CN_E2在发光区域EMA内与第二连接电极CNE2对向,且布置在第一电极RME1上。第一连接部CN_B1可以在布置于发光区域EMA的下侧的堤层BNL上沿第二方向DR2延伸而连接第一延伸部CN_E1和第二延伸部CN_E2。第三连接电极CNE3可以布置在发光区域EMA和堤层BNL上,可以不直接连接于电极RME。布置在第一延伸部CN_E1下部的第二电极分支部RM_B2可以与第二电压布线VL2电连接,施加到第二电极分支部RM_B2的第二电源电压可以不被传输到第三连接电极CNE3。

根据一实施例,在显示装置10中,连接电极CNE中的一部分可以通过布置在子区域SA1、SA2的接触部CT1、CT2与电极RME接触。第一连接电极CNE1在布置于相应子像素SPXn的发光区域EMA上侧的第一子区域SA1中,可以通过贯通第一绝缘层PAS1、第二绝缘层PAS2以及第三绝缘层PAS3的第一接触部CT1而与第一电极RME1接触。第二连接电极CNE2在布置于相应子像素SPXn的发光区域EMA下侧的第二子区域SA2中,可以通过贯通第一绝缘层PAS1、第二绝缘层PAS2以及第三绝缘层PAS3的第二接触部CT2而与第二电极RME2接触。第一连接电极CNE1和第二连接电极CNE2可以分别通过电极RME与第三导电层电连接。第一电极RME1可以布置成使得布置在子区域SA1、SA2的部分与第一接触部CT1重叠,并且第二电极RME2包括从电极杆部RM_S沿第二方向DR2突出而布置在子区域SA1、SA2的部分,且可以在突出的所述部分与第二接触部CT2重叠。

第一连接电极CNE1可以电连接到第一晶体管T1而被施加第一电源电压,并且第二连接电极CNE2可以电连接到第二电压布线VL2而被施加第二电源电压。各个连接电极CNE可以在发光区域EMA中与发光元件ED接触,并将电源电压传输到发光元件ED。

第三连接电极CNE3与第一连接电极CNE1和第二连接电极CNE2不同,可以不与电极RME接触。第一连接电极CNE1和第二连接电极CNE2可以是与电极RME接触的第一类型连接电极,且第三连接电极CNE3可以是不与电极RME接触的第二类型连接电极。第三连接电极CNE3可以通过发光元件ED与第一连接电极CNE1和第二连接电极CNE2电连接。

多个连接电极CNE(CNE1、CNE2、CNE3)分别与发光元件ED接触,并且可以与电极RME或其下部的导电层电连接。例如,第一连接电极CNE1和第二连接电极CNE2可以分别布置在第三绝缘层PAS3上,并且与发光元件ED接触。第三连接电极CNE3可以布置在第二绝缘层PAS2上,并且与发光元件ED接触。第一连接电极CNE1可以与第一电极RME1局部地重叠,并且与发光元件ED的一端部接触。第二连接电极CNE2可以与第二电极RME2局部地重叠,并且与发光元件ED的另一端部接触。第三连接电极CNE3可以横跨第一电极RME1和第二电极RME2而布置,并且与发光元件ED接触。连接电极CNE可以在布置于发光区域EMA的部分与发光元件ED接触,并且在布置于子区域SA的部分与第三导电层电连接。

对应于连接电极CNE的布置结构,多个发光元件ED可以根据两个端部接触的连接电极CNE而被划分为彼此不同的发光元件ED。第一发光元件ED1和第二发光元件ED2可以与第一类型连接电极和第二类型连接电极接触。第一发光元件ED1的第一端部可以与第一连接电极CNE1接触,第二发光元件ED2的第二端部可以与第二连接电极CNE2接触。第一发光元件ED1的第二端部可以与第三连接电极CNE3接触,第二发光元件ED2的第一端部可以与第三连接电极CNE3接触。多个发光元件ED1、ED2可以通过多个连接电极CNE彼此串联连接。根据本实施例的显示装置10可以在每个子像素SPXn中包括更多数量的发光元件ED并构成它们的串联连接,从而可以增加每单位面积的发光量。

然而,并不限定于此。在若干实施例中,多个连接电极CNE可以与第三导电层直接接触,也可以通过不是电极RME的其他图案与第三导电层电连接。

连接电极CNE可以包括导电性物质。例如,可以包括ITO、IZO、ITZO、铝(Al)等。作为一例,连接电极CNE可以包括透明性导电性物质,从发光元件ED发出的光可以透过连接电极CNE而射出。

第三绝缘层PAS3布置在第三连接电极CNE3和第二绝缘层PAS2上。第三绝缘层PAS3可以布置在第二绝缘层PAS2的整个面以覆盖第三连接电极CNE3,并且第一连接电极CNE1和第二连接电极CNE2可以布置在第三绝缘层PAS3上。第三绝缘层PAS3可以布置在除了布置有第一连接电极CNE1和第二连接电极CNE2的区域之外的过孔层VIA整个面上。第三绝缘层PAS3可以使第一连接电极CNE1和第二连接电极CNE2相互绝缘,使得第一连接电极CNE1和第二连接电极CNE2不会与第三连接电极CNE3直接接触。

显示装置10在发光区域EMA内可以包括布置在第二电极RME2的第二电极分支部RM_B2与堤层BNL之间的开口部OP。开口部OP可以贯通第二绝缘层PAS2和第三绝缘层PAS3,并且形成为在第二电极分支部RM_B2和堤层BNL之间沿第一方向DR1延伸。开口部OP可以提供从发光元件ED发出的光中的在连接电极CNE或者第一绝缘层PAS1内全反射的光所射出的路径。然而,并不限定于此,开口部OP不限于此,也可以省略开口部OP。

虽未在附图中示出,但在第三绝缘层PAS3、第一连接电极CNE1以及第二连接电极CNE2上还可以布置有其他绝缘层。所述绝缘层可以发挥保护布置在第一基板SUB上的构件不受外部环境影响的作用。

上述的第一绝缘层PAS1、第二绝缘层PAS2以及第三绝缘层PAS3中的每一个可以包括无机物绝缘性物质或者有机物绝缘性物质。作为一例,第一绝缘层PAS1、第二绝缘层PAS2以及第三绝缘层PAS3中的每一个可以包括无机物绝缘性物质,或者第一绝缘层PAS1和第三绝缘层PAS3可以包括无机物绝缘性物质,而第二绝缘层PAS2包括有机物绝缘性物质。第一绝缘层PAS1、第二绝缘层PAS2以及第三绝缘层PAS3中的每一个或至少一个层可以形成为多个绝缘层交替或重复地层叠的结构。在示例性实施例中,第一绝缘层PAS1、第二绝缘层PAS2以及第三绝缘层PAS3可以分别是氧化硅(SiO

在根据一实施例的显示装置10中,第一接触部CT1和第二接触部CT2可以分别布置在被堤层BNL围绕的区域中的子区域SA1、SA2。第一接触部CT1和第二接触部CT2可以贯通第一绝缘层PAS1、第二绝缘层PAS2以及第三绝缘层PAS3,并且可以不布置在布置有发光元件ED的发光区域EMA中。据此,可以防止从发光元件ED发出的光在接触部CT1、CT2反射或折射而无法射出。

根据接触部CT1、CT2和发光元件ED的布置,连接电极CNE中的一部分可以横跨发光区域EMA和子区域SA1、SA2而配置。第一连接电极CNE1可以布置为从发光区域EMA延伸到布置在发光区域EMA上侧的第一子区域SA1。第二连接电极CNE2可以布置为从发光区域EMA延伸到布置在发光区域EMA下侧的第二子区域SA2。第一连接电极CNE1和第二连接电极CNE2作为布置在第三绝缘层PAS3上的连接电极,可以布置于彼此相同的层。它们可以在将构成连接电极的材料沉积在相同的层之后,通过利用光敏抗蚀剂的图案化工艺来形成。

第一连接电极CNE1和第二连接电极CNE2可以沿着堤层BNL的台阶而横跨发光区域EMA和子区域SA1、SA2而布置。堤层BNL可以具有比连接电极CNE的厚度大的厚度,在连接电极CNE的图案化工艺中,在堤层BNL的倾斜的侧表面可能残留有连接电极CNE的残渣。当布置在同一层上的第一连接电极CNE1和第二连接电极CNE2彼此相邻地布置时,也有可能由于材料的残渣而电连接。随着第一连接电极CNE1和第二连接电极CNE2以发光区域EMA为基准横跨彼此不同的子区域SA1、SA2而布置,根据一实施例的显示装置10可以布置为彼此不相邻。例如,第一连接电极CNE1和第二连接电极CNE2可以分别越过堤层BNL而布置在子区域SA1、SA2,并且可以越过堤层BNL的彼此不同部分而布置在彼此不同的子区域SA1、SA2。据此,可以防止第一连接电极CNE1和第二连接电极CNE2由于残留在堤层BNL的侧表面上的残渣而彼此电连接。

图11是图6的A部分的放大图。

参照图6和图11,根据一实施例的显示装置10的第一连接电极CNE1可以布置为在第一方向DR1上从发光区域EMA延伸到第一子区域SA1。在堤层BNL的沿第二方向DR2延伸的部分中,第一连接电极CNE1可以越过布置在发光区域EMA上侧的上侧堤部而布置。与此相反地,第二连接电极CNE2可以在第一方向DR1上从发光区域EMA延伸而布置至第二子区域SA2。在堤层BNL的沿第二方向DR2延伸的部分中,第二连接电极CNE2可以越过布置在发光区域EMA的下侧的下侧堤部而布置。

堤层BNL可以包括面向发光区域EMA的内侧侧表面IBS1、IBS2。例如,堤层BNL可以包括沿第二方向DR2延伸的部分的第一内侧侧表面IBS1和沿第一方向DR1延伸的部分的第二内侧侧表面IBS2。第一连接电极CNE1可以越过堤层BNL的上侧堤部的第一内侧侧表面IBS1而布置至第一子区域SA1,并且与下侧堤部的第一内侧侧表面IBS1隔开。或者,第一连接电极CNE1可以与堤层BNL的下侧堤部隔开,并且与上侧堤部重叠。第二连接电极CNE2可以越过堤层BNL的下侧堤部的第一内侧侧表面IBS1而布置至第二子区域SA2,并且与上侧堤部的第一内侧侧表面IBS1隔开。或者,第二连接电极CNE2可以与堤层BNL的上侧堤部隔开,并且与下侧堤部重叠。在第三连接电极CNE3中,第一延伸部CN_E1和第二延伸部CN_E2可以分别在第一方向DR1上与堤层BNL的上侧堤部隔开,并且第一连接部CN_B1可以布置在堤层BNL的下侧堤部上。

在形成布置在同一层的第一连接电极CNE1和第二连接电极CNE2的工艺中,构成连接电极的材料的残渣可以形成在堤层BNL的第一内侧侧表面IBS1和第二内侧侧表面IBS2上。虽然未在附图中示出,但在堤层BNL的内侧侧表面中,面向子区域SA1、SA2的内侧侧表面上也有可能形成所述残渣。由于第一连接电极CNE1与上侧堤部重叠并与下侧堤部隔开且第二连接电极CNE2与下侧堤部重叠并与上侧堤部隔开,因此即使堤层BNL的内侧侧表面IBS1、IBS2上残留残渣,第一连接电极CNE1和第二连接电极CNE2直接连接的可能性也可以较低。例如,第二连接电极CNE2可以布置为在第一方向DR1上与堤层BNL的上侧堤部隔开,并且第一连接电极CNE1可以布置为在第一方向DR1上与堤层BNL的下侧堤部隔开。因此,为了使第一连接电极CNE1与第二连接电极CNE2直接连接,需要形成沿着第一内侧侧表面IBS1和第二内侧侧表面IBS2连接的残渣。由于残留在堤层BNL的内侧侧表面IBS1、IBS2的残渣会在工艺中被基本全部去除,仅残留一部分,因此残留有沿着第一内侧侧表面IBS1和第二内侧侧表面IBS2连接的残渣的概率可以较低。

根据一实施例的显示装置10,由于第一连接电极CNE1和第二连接电极CNE2从发光区域EMA沿彼此不同方向延伸并越过堤层BNL,因此,因残留在内侧侧表面IBS1、IBS2的残渣而彼此直接连接的概率会减少,并且可以防止相应子像素SPXn的发光不良。

图12是根据一实施例的发光元件的示意图。

参照图12,发光元件ED可以是发光二极管(Light Emitting diode),具体地,发光元件ED可以是具有纳米(Nano-meter)至微米(Micro-meter)单位大小且利用无机物构成的无机发光二极管。若在彼此对向的两个电极之间沿着特定方向形成电场,则发光元件ED可整齐排列于形成极性的上述两个电极之间。

根据一实施例的发光元件ED可以具有沿一方向延伸的形状。发光元件ED可以具有圆柱体、杆(Rod)、线(Wire)、管(Tube)等形状。但是,发光元件ED的形态并不局限于此,发光元件ED可以具有正方体、长方体、六角柱形等多角棱柱形状,或者具有向一方向延伸且外表面部分倾斜的形状等多种形态。

发光元件ED可以包括掺杂有任意导电型(例如,p型或n型)掺杂剂的半导体层。半导体层可以通过传输从外部电源施加的电信号来发出特定波长带的光。发光元件ED可以包括第一半导体层31、第二半导体层32、发光层36、电极层37以及绝缘膜38。

第一半导体层31可以是n型半导体。第一半导体层31可以包括具有化学式Al

第二半导体层32隔着发光层36布置在第一半导体层31上。第二半导体层32可以是p型半导体,并且第二半导体层32可以包括具有化学式Al

另一方面,虽然在附图中示出了第一半导体层31和第二半导体层32构成为一个层的情形,但并不限定于此。根据发光层36的物质,第一半导体层31和第二半导体层32还可包括更多数量的层,例如,覆盖层(Clad layer)或拉伸应变势垒减小(TSBR:Tensile strainbarrier reducing)层。例如,发光元件ED还可以包括布置在第一半导体层31与发光层36之间或者第二半导体层32与发光层36之间的其他半导体层。布置在第一半导体层31和发光层36之间的半导体层可以是掺杂有n型掺杂剂的AlGaInN、GaN、AlGaN、InGaN、AlN及InN中的一种以上,并且布置在第二半导体层32与发光层36之间的半导体层可以是掺杂有p型掺杂剂的AlGaInN、GaN、AlGaN、InGaN、AlN以及InN中的一种以上。

发光层36布置在第一半导体层31与第二半导体层32之间。发光层36可以包括单量子阱结构或多量子阱结构的物质。在发光层36包括多量子阱结构的物质的情况下,也可以是量子层(Quantum layer)和阱层(Well layer)相互交替层叠多个的结构。发光层36可根据通过第一半导体层31和第二半导体层32施加的电信号而通过电子-空穴对的结合来发出光。发光层36可以包括AlGaN、AlGaInN、InGaN等物质。尤其,在发光层36为多量子阱结构,并且为量子层和阱层交替层叠的结构的情况下,量子层可以包含AlGaN或AlGaInN,阱层可以包含GaN或AlInN等物质。

发光层36可以是能带隙(Band gap)大的种类的半导体物质和能带隙小的半导体物质彼此交替层叠的结构,根据发出的光的波长带可以包括不同的III族至V族半导体物质。发光层36发出的光不局限在蓝色波长带的光,根据情况也可以出发红色、绿色波长带的光。

电极层37可以是欧姆(Ohmic)连接电极。但是,并不限定于此,也可以是肖特基(Schottky)连接电极。发光元件ED可以包括至少一个电极层37。发光元件ED可以包括一个以上的电极层37,但并不限定于此,也可以省略电极层37。

当在显示装置10中发光元件ED与电极或者连接电极电连接时,在电极层37可以降低发光元件ED与电极或者连接电极之间的电阻。电极层37可以包括具有导电性的金属。例如,电极层37可以包括铝(Al)、钛(Ti)、铟(In)、金(Au)、银(Ag)、ITO、IZO以及ITZO中的至少一种。

绝缘膜38以围绕上述多个半导体层和电极层的外表面而布置。例如,绝缘膜38可以布置成至少围绕发光层36的外表面,并且可以形成为暴露发光元件ED的长度方向上的两个端部。此外,绝缘膜38在与发光元件ED的至少一端部相邻的区域,也可以形成为剖面上的圆上表面。

绝缘膜38可以包括具有绝缘特性的物质,例如,硅氧化物(SiO

绝缘膜38可以发挥保护发光元件ED的半导体层和电极层的功能。当绝缘膜38与向发光元件ED传输电信号的电极直接接触的情况下,可以防止可能在发光层发生的电短路。此外,绝缘膜38可以防止发光元件ED的发光效率的降低。

此外,可以对绝缘膜38的外表面进行表面处理。发光元件ED可以以分散在预定的墨中的状态喷射到电极上而被整齐排列。其中,为了使发光元件ED在油墨内不与相邻的其他发光元件ED凝聚而维持分散的状态,绝缘膜38的表面可以进行疏水性或者亲水性处理。

以下,参照其他附图,对显示装置10的其他实施例进行说明。

图13是示出根据另一实施例的显示装置的一子像素的平面图。图14是沿图13的E4-E4'线截取的剖视图。图15是沿图13的E5-E5'线和E6-E6'线截取的剖视图。

参照图13至图15,在根据一实施例的显示装置10_1中,包括第一连接电极CNE1和第二连接电极CNE2的第一连接电极层可以布置在第二绝缘层PAS2与第三绝缘层PAS3之间,包括第三连接电极CNE3的第二连接电极层可以布置在第三绝缘层PAS3上。本实施例与图4至图11的实施例的不同之处在于,第一连接电极CNE1、第二连接电极CNE2和第三连接电极CNE3所布置的层不同。

例如,第一连接电极CNE1和第二连接电极CNE2可以分别布置在第二绝缘层PAS2上,并且可以与发光元件ED接触。第三连接电极CNE3可以布置在第三绝缘层PAS3上,可以与发光元件ED接触。第一连接电极CNE1可以通过在相应子像素SPXn的发光区域EMA上侧布置的第一子区域SA1中贯通第一绝缘层PAS1和第二绝缘层PAS2的第一接触部CT1而与第一电极RME1接触。第二连接电极CNE2可以通过在相应子像素SPXn的发光区域EMA下侧布置的第二子区域SA2中贯通第一绝缘层PAS1和第二绝缘层PAS2的第二接触部CT2而与第二电极RME2接触。

图16是示出根据另一实施例的显示装置的一子像素的平面图。图17是沿图16的E8-E8'线截取的剖视图。图18是沿图16的E9-E9'线和E10-E10'线截取的剖视图。

参照图16至图18,根据一实施例的显示装置10_2中,各个子像素SPXn的电极RME、连接电极CNE以及发光元件ED的布置可以不同。例如,根据一实施例的显示装置10_2可以在每个子像素SPXn中包括两个电极RME(RME1、RME2)以及两个连接电极CNE(CNE1、CNE2)。以下,省略对重复内容的说明,以区别点为中心进行说明。

显示装置10_2可以包括布置在各个子像素SPXn的第一堤图案BP1和第二堤图案BP2。第一堤图案BP1和第二堤图案BP2可以在每个子像素SPXn的发光区域EMA内沿第二方向DR2彼此隔开。第一堤图案BP1可以布置在作为发光区域EMA的相对于中心的第二方向DR2上的一侧的左侧,并且第二堤图案BP2可以与第一堤图案BP1隔开,并布置在作为发光区域EMA的相对于中心的第二方向DR2上的另一侧的右侧。第一堤图案BP1和第二堤图案BP2可以沿着第二方向DR2彼此交替地布置,并且可以在显示区域DPA中以岛状图案布置。在第一堤图案BP1与第二堤图案BP2之间可以布置有多个发光元件ED。

第一堤图案BP1和第二堤图案BP2在第一方向DR1上的长度可以彼此相同,并且可以小于堤层BNL所围绕的发光区域EMA的第一方向DR1上的长度。第一堤图案BP1和第二堤图案BP2可以与堤层BNL的沿第二方向DR2延伸的部分相隔开。第一堤图案BP1和第二堤图案BP2的第二方向DR2上的宽度可以彼此相同。

多个堤图案BP1、BP2可以布置在过孔层VIA上。例如,堤图案BP1、BP2可以直接布置于过孔层VIA上,并且可以具有以过孔层VIA的上表面为基准至少一部分突出的结构。堤图案BP1、BP2的突出的部分可以具有倾斜的或者具有预定曲率而弯曲的侧表面,从发光元件ED发出的光可以在布置于堤图案BP1、BP2上的电极RME反射而向过孔层VIA的上部方向射出。

多个电极RME(RME1、RME2)以沿一方向延伸的形状布置在各个子像素SPXn。多个电极RME1、RME2可以沿第一方向DR1延伸而布置于子像素SPXn的发光区域EMA和子区域SA,这些电极可以沿第二方向DR2彼此隔开而布置。

显示装置10_2可以包括布置在各个子像素SPXn的第一电极RME1和第二电极RME2。第一电极RME1布置在发光区域EMA的中心的左侧,第二电极RME2在第二方向DR2上与第一电极RME1相隔开,并布置在发光区域EMA的中心的右侧。第一电极RME1可以布置在第一堤图案BP1上,第二电极RME2可以布置在第二堤图案BP2上。第一电极RME1和第二电极RME2可以越过堤层BNL而局部地布置在相应子像素SPXn和子区域SA。彼此不同的子像素SPXn的第一电极RME1和第二电极RME2可以以位于一个子像素SPXn的子区域SA内的分离部ROP为基准彼此隔开。

第一电极RME1和第二电极RME2可以至少布置在堤图案BP1、BP2的倾斜的侧表面上。在一实施例中,在第二方向DR2上测量的多个电极RME的宽度可以小于在第二方向DR2上测量的堤图案BP1、BP2的宽度,第一电极RME1和第二电极RME2在第二方向DR2上隔开的间隔可以小于堤图案BP1、BP2之间的间隔。第一电极RME1和第二电极RME2的至少一部分区域可以直接布置在过孔层VIA上,从而它们可以布置在相同平面上。

各电极RME可以在发光区域EMA与子区域SA之间的重叠于堤层BNL的部分通过电极接触孔CTD、CTS与第三导电层直接接触。第一电极接触孔CTD可以形成在堤层BNL与第一电极RME1重叠的区域,第二电极接触孔CTS可以形成在堤层BNL与第二电极RME2重叠的区域。第一电极RME1可以通过贯通过孔层VIA和第一保护层PV1的第一电极接触孔CTD与第一导电图案CDP1接触。第二电极RME2可以通过贯穿过孔层VIA和第一保护层PV1的第二电极接触孔CTS与第二电压布线VL2接触。第一电极RME1可以通过第一导电图案CDP1与第一晶体管T1电连接,并被施加第一电源电压,第二电极RME2可以与第二电压布线VL2电连接,并被施加第二电源电压。

多个发光元件ED可以布置在发光区域EMA。发光元件ED布置在堤图案BP1、BP2之间,并且可以在第一方向DR1上彼此隔开而排列。发光元件ED可以与连接电极CNE(CNE1、CNE2)接触而与电极RME和过孔层VIA下部的导电层电连接,并且可以被施加电信号而发出特定波长带的光。

第二绝缘层PAS2可以布置在多个发光元件ED、第一绝缘层PAS1以及堤层BNL上。第二绝缘层PAS2包括在堤图案BP1、BP2之间沿第一方向DR1延伸而布置在多个发光元件ED上的图案部。所述图案部布置为局部地围绕发光元件ED的外表面,并且可以不覆盖发光元件ED的两侧或者两端部。所述图案部可以在平面图上的各个子像素SPXn内形成线型或岛型的图案。第二绝缘层PAS2的所述图案部可以在保护发光元件ED的同时在显示装置10的制备工艺中固定发光元件ED。此外,第一绝缘层PAS1可以布置成填充发光元件ED与其下部的第二绝缘层PAS2之间的空间。此外,第二绝缘层PAS2中的一部分可以布置于堤层BNL的上部和子区域SA。

多个连接电极CNE(CNE1、CNE2)可以布置在多个电极RME以及堤图案BP1、BP2上。多个连接电极CNE可以分别具有沿一方向延伸的形状,并且可以彼此隔开而布置。各个连接电极CNE可以与发光元件ED接触,并且可以与第三导电层电连接。

多个连接电极CNE可以包括布置于各个子像素SPXn的第一连接电极CNE1和第二连接电极CNE2。第一连接电极CNE1可以具有沿第一方向DR1延伸的形状,并且可以布置在第一电极RME1或第一堤图案BP1上。第一连接电极CNE1可以与第一电极RME1局部地重叠,并且可以从发光区域EMA越过堤层BNL而布置至子区域SA。第一连接电极CNE1可以布置至布置于发光区域EMA的下侧的子区域SA,并且可以以越过堤层BNL的下侧堤部的方式布置。

第二连接电极CNE2可以具有沿第一方向DR1延伸的形状,并且可以布置在第二电极RME2或第二堤图案BP2上。第二连接电极CNE2可以与第二电极RME2局部地重叠,并且可以从发光区域EMA越过堤层BNL而布置至子区域SA。第二连接电极CNE2可以布置至布置于发光区域EMA的上侧的子区域SA,并且可以以越过堤层BNL的上侧堤部的方式布置。

第一连接电极CNE1和第二连接电极CNE2可以分别与发光元件ED接触,并与电极RME或者其下部的导电层电连接。例如,第一连接电极CNE1和第二连接电极CNE2可以分别布置在第二绝缘层PAS2的侧表面上,并与发光元件ED接触。第一连接电极CNE1可以与第一电极RME1局部地重叠,并与发光元件ED的一端接触。第二连接电极CNE2可以与第二电极RME2局部地重叠,以与发光元件ED的另一端接触。多个连接电极CNE横跨发光区域EMA和子区域SA而布置。连接电极CNE可以在布置于发光区域EMA的部分与发光元件ED接触,并且在布置于子区域SA的部分与第三导电层电连接。

根据一实施例,在显示装置10中,各个连接电极CNE可以通过布置在子区域SA的接触部CT1、CT2而与电极RME接触。第一连接电极CNE1可以在布置于相应子像素SPXn的发光区域EMA下侧的下侧子区域SA中通过第一接触部CT1而与第一电极RME1接触。第二连接电极CNE2可以在布置在相应子像素SPXn的发光区域EMA上侧的上侧子区域SA中通过第二接触部CT2与第二电极RME2接触。

在显示装置10_2中,可以省略第三绝缘层PAS3且第一连接电极CNE1和第二连接电极CNE2布置在相同层上。第二绝缘层PAS2可以包括有机物绝缘性物质,第一连接电极CNE1和第二连接电极CNE2可以局部地布置在第二绝缘层PAS2上。例如,第一连接电极CNE1和第二连接电极CNE2在发光区域EMA中可以与布置在发光元件ED上的第二绝缘层PAS2直接接触。第一连接电极CNE1和第二连接电极CNE2可以与布置在发光元件ED上的第二绝缘层PAS2的侧表面接触。

在每一个子像素SPXn包括两个电极RME和两个连接电极CNE且省略第三绝缘层PAS3的实施例中,第一连接电极CNE1和第二连接电极CNE2可以布置在彼此相同的层。如上所述,第一连接电极CNE1和第二连接电极CNE2以越过堤层BNL的方式布置,并且以越过彼此不同的部分(例如,上侧堤部和下侧堤部)的方式布置,因此不会因残留在堤层BNL的内侧侧表面的残渣而直接连接。显示装置10_2在每一个子像素SPXn中包括少量的电极RME和连接电极CNE,从而可以在每单位面积包括大量的子像素SPXn。进而,即使通过连接电极CNE的布置设计而在较窄的区域中布置有隔开的连接电极CNE1、CNE2,也能够防止它们直接连接而在相应子像素SPXn中发生发光不良。

以上,参照附图说明了本发明的实施例,但在本发明所属技术领域中具有普通知识的人员可以理解的是,可以在不改变本发明的其技术思想或者必要特征的情况下以其他具体形态实施。因此,以上记载的实施例应当理解为在所有方面均为示例性的,而不是限定性的。