自动化FPGA验证系统

文献发布时间:2023-06-19 10:16:30

技术领域

本申请涉及芯片技术领域,具体涉及一种自动化FPGA验证系统。

背景技术

芯片设计过程中,为了保证逻辑设计的准确性,需要使用FPGA验证平台对逻辑设计进行验证。

传统FPGA验证平台由FGPA芯片及其外围电路组成,FGPA芯片通过固定的 IO(输入/输出)口与外围电路连接。

在传统FPGA验证平台上,当需要验证逻辑设计的IO MUX(输入/输出口复用) 功能时,每验证一种IO MUX功能,都需要进行逻辑代码修改,以保证逻辑设计的IO能与FPGA验证平台的外围电路的IO对应上。如此操作,会存在以下问题:

1.验证过程中,对逻辑代码的修改,破坏了逻辑代码的原始性,有可能遗漏或者带来新的BUG;

2.每验证一种IO MUX功能都需要修改一次逻辑代码,工作量大、验证耗时长;

由此,本发明人凭借多年从事相关行业的经验与实践,提出一种自动化FPGA验证系统,以克服现有技术的缺陷。

发明内容

针对现有技术中的问题,本申请提供一种自动化FPGA验证系统,能够快速、准确和便捷的实现FPGA的自动化验证。

为解决上述技术问题,本申请提供以下技术方案:

第一方面,本申请提供一种自动化FPGA验证系统,包括:用于装载逻辑设计代码的第一FPGA芯片组、用于IO MUX功能切换的第二FPGA芯片组以及多个外围电路,所述第二FPGA芯片组与所述外围电路连接;

所述第一FPGA芯片组和所述第二FPGA芯片组通过通信接口和芯片IO口连接,所述芯片IO口用于对所述外围电路的功能信号进行功能复用,所述通信接口用于在所述芯片IO口进行功能复用时,实现所述第一FPGA芯片组和所述第二FPGA芯片组的同步配合。

进一步地,在验证所述IO口的复用功能时,所述第一FPGA芯片组将IO口设置为外围电路的第一功能信号,同时通过所述通信接口通知所述第二FPGA芯片组同步将所述IO口切换到第一功能信号,把所述第一FPGA芯片组的IO口与所述外围电路相连接,以此实现使用所述外围电路验证逻辑设计的IO口复用功能。

由上述技术方案可知,本申请提供一种自动化FPGA验证系统,通过用于装载逻辑设计代码的第一FPGA芯片组、用于IO MUX功能切换的第二FPGA芯片组以及多个外围电路,所述第二FPGA芯片组与所述外围电路连接;所述第一FPGA芯片组和所述第二FPGA芯片组通过通信接口和芯片IO口连接,所述芯片IO口用于对所述外围电路的功能信号进行功能复用,所述通信接口用于在所述芯片IO口进行功能复用时,实现所述第一FPGA芯片组和所述第二FPGA芯片组的同步配合。本申请能够快速、准确和便捷的实现FPGA的自动化验证。

附图说明

为了更清楚地说明本申请实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

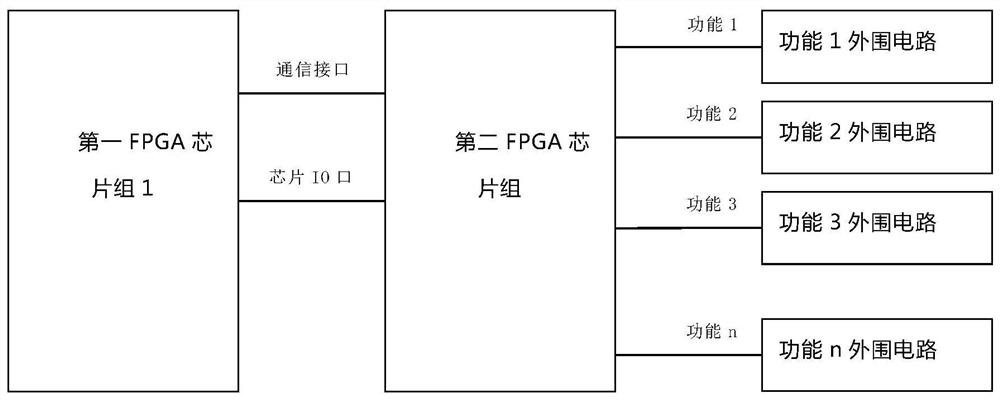

图1为本申请所述自动化FPGA验证系统的结构示意图。

具体实施方式

为了使本技术领域的人员更好地理解本申请方案,下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本申请一部分的实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本申请保护的范围。

需要说明的是,本申请的说明书和权利要求书及上述附图中的术语“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的本申请的实施例。此外,术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

在本申请中,术语“上”、“下”、“左”、“右”、“前”、“后”、“顶”、“底”、“内”、“外”、“中”、“竖直”、“水平”、“横向”、“纵向”等指示的方位或位置关系为基于附图所示的方位或位置关系。这些术语主要是为了更好地描述本申请及其实施例,并非用于限定所指示的装置、元件或组成部分必须具有特定方位,或以特定方位进行构造和操作。

并且,上述部分术语除了可以用于表示方位或位置关系以外,还可能用于表示其他含义,例如术语“上”在某些情况下也可能用于表示某种依附关系或连接关系。对于本领域普通技术人员而言,可以根据具体情况理解这些术语在本申请中的具体含义。

此外,术语“安装”、“设置”、“设有”、“连接”、“相连”、“套接”应做广义理解。例如,可以是固定连接,可拆卸连接,或整体式构造;可以是机械连接,或电连接;可以是直接相连,或者是通过中间媒介间接相连,又或者是两个装置、元件或组成部分之间内部的连通。对于本领域普通技术人员而言,可以根据具体情况理解上述术语在本申请中的具体含义。

需要说明的是,在不冲突的情况下,本申请中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本申请。

考虑到在传统FPGA验证平台上,当需要验证逻辑设计的IO MUX(输入/输出口复用)功能时,每验证一种IO MUX功能,都需要进行逻辑代码修改,以保证逻辑设计的IO能与FPGA验证平台的外围电路的IO对应上。如此操作,会存在以下问题:

1.验证过程中,对逻辑代码的修改,破坏了逻辑代码的原始性,有可能遗漏或者带来新的BUG;

2.每验证一种IO MUX功能都需要修改一次逻辑代码,工作量大、验证耗时长。

本申请提供一种自动化FPGA验证系统的实施例,参见图1,本实施例中,所述自动化FPGA验证系统具体包含用于装载逻辑设计代码的第一FPGA芯片组、用于IO MUX功能切换的第二FPGA芯片组以及多个外围电路,所述第二FPGA芯片组与所述外围电路连接;

所述第一FPGA芯片组和所述第二FPGA芯片组通过通信接口和芯片IO口连接,所述芯片IO口用于对所述外围电路的功能信号进行功能复用,所述通信接口用于在所述芯片IO口进行功能复用时,实现所述第一FPGA芯片组和所述第二 FPGA芯片组的同步配合。

从上述描述可知,根据本申请实施例提供的自动化FPGA验证系统,通过用于装载逻辑设计代码的第一FPGA芯片组、用于IO MUX功能切换的第二FPGA芯片组以及多个外围电路,所述第二FPGA芯片组与所述外围电路连接;所述第一 FPGA芯片组和所述第二FPGA芯片组通过通信接口和芯片IO口连接,所述芯片 IO口用于对所述外围电路的功能信号进行功能复用,所述通信接口用于在所述芯片IO口进行功能复用时,实现所述第一FPGA芯片组和所述第二FPGA芯片组的同步配合。本申请能够快速、准确和便捷的实现FPGA的自动化验证。

参见图1,在第一FPGA芯片组与第二FPGA芯片组的连接包含了一组通信接口及芯片的IO口,其中IO口包含了功能1信号、功能2信号、功能3信号、功能n信号的功能复用,(即通过软件设置,可以将IO设置成功能1、2、3、n信号)。

作为一种优选地实施方式,在验证所述IO口的复用功能时,所述第一FPGA 芯片组将IO口设置为外围电路的第一功能信号,同时通过所述通信接口通知所述第二FPGA芯片组同步将所述IO口切换到第一功能信号,把所述第一FPGA芯片组的IO口与所述外围电路相连接,以此实现使用所述外围电路验证逻辑设计的IO口复用功能。

同理,通过同步配合,也可实现逻辑设计的IO口复用功能2、3、n的自动切换验证。

如此验证方式,不需要修改第一FPGA芯片组中的逻辑设计代码,也不需要人工干预,特别是在回归测试的时候,可以实现完全的自动化测试验证,极大减少验证工作量、以及缩短验证时长。

以上所述仅为本发明示意性的具体实施方式,并非用以限定本发明的范围。任何本领域的技术人员,在不脱离本发明的构思和原则的前提下所作出的等同变化与修改,均应属于本发明保护的范围。