一种基于忆阻器的神经网络容错方法

文献发布时间:2023-06-19 09:29:07

技术领域

本发明涉及硬件神经网络技术领域,特别是涉及一种基于忆阻器的神经网络容错方法。

背景技术

人工神经网络是20世纪80年代以来人工智能领域兴起的研究热点。随着技术的进步,人工智能的应用在现实的生活中也越来越普遍。然而传统的冯·诺依曼架构计算机是一种精确计算和严格执行算法指令的架构,并不适合做学习、模糊处理方面的任务。人脑可以处理复杂的感知任务,而且功耗非常低。如识别物体,对视频和音频数据的理解,语音对话等。受人类大脑工作原理的启发,人们希望以人脑为蓝本,应用生物神经网络的概念来建立仿人脑的神经网络系统,实现新一代的计算机体系结构,并针对特定的应用来降低功耗和提高性能。

忆阻器以其高密度、高速度以及高可靠性得到半导体领域的广泛关注。国内外关于忆阻器神经计算的研究重点主要集中在解决或者规避忆阻器的器件缺陷。

在硬件上,忆阻器神经计算解决方法的基本思路主要是通过冗余电路来纠正相变存储器中的故障,采用冗余行匹配算法,使用忆阻器的冗余行替换出故障的忆阻器器件。使用传统CMOS工艺中常用的AD/DA技术将模拟运算转化为数字运算,提高了忆阻器上的运算的正确率。另外,也有的硬件方法会通过不断用电流烧写忆阻器阻值的方式,来使得其阻值到合理误差范围之内。

往往神经网络技术需要消耗大量的运算资源,造成的大量的能耗。为了保证神经网络算法在运算中的实时性和灵活性,硬件上的实现需要同时具备高运算能力和低功耗的特性。而现在CMOS工艺面临着规模的限制和“内存墙”的瓶颈。忆阻器的crossbar结构是能够被用于解决神经网络运算中主要的矩阵乘法运算,相比于CMOS工艺,该设备有相当大的能效比,同等运算级别的crossbar结构拥有更小的芯片面积。但是忆阻器本身有器件上的缺陷,自身的阻值会受到温度、时间、刷写次数等因素的影响从而漂移,降低了在其上运行的神经网络算法的稳定性和准确率。通过软件方法规避忆阻器的器件缺陷,从而使神经网络以高可靠性在其上运行,成为一个亟待解决的重要问题。

纯硬件解决方法往往会消耗大量的冗余硬件资源,扩大了芯片面积,提升了功耗,这与忆阻器本身的理念并不符合。反复烧写的方式虽然没有消耗额外的硬件资源,但需要反复对芯片进行测试,这需要大量的能耗。

发明内容

本发明所要解决的技术问题是提供一种基于忆阻器的神经网络容错方法,提高在其上运行神经网络算法的稳定性和准确率。

本发明解决其技术问题所采用的技术方案是:提供一种基于忆阻器的神经网络容错方法,包括以下步骤:

(1)在进行神经网络权值矩阵的存储时,以某个电阻状态为目标,读出忆阻器器件电阻以获得存储阵列中的忆阻器电阻的分布;

(2)在进行权重更新时,将神经网络权重矩阵映射至存储阵列,根据权重矩阵进行存储单元映射,通过自适应算法将大的权值映射到缺陷小的忆阻器器件上,完成权重更新,实现神经网络的学习与训练。

所述步骤(1)中读出器件电阻时,将其他的忆阻器保持在高阻态。

所述步骤(2)中通过自适应算法将大的权值映射到缺陷小的忆阻器器件上具体为:将权值大的权重映射到器件缺陷小的忆阻器器件上,并根据权值调整的幅度,将调整幅度大的权重映射到器件缺陷小的忆阻器器件上。

所述器件缺陷包括但不限于阻值漂移、阻值不变和阻值波动。

所述忆阻器为具有存储记忆功能的非易失性存储器器件,包括但不限于相变存储器或阻抗式随机存储器。

所述忆阻器为crossbar阵列结构,所述crossbar阵列结构的一端连接信号输入端,另一端连接信号输出端;所述crossbar阵列结构包括n*m个突触电路,其中,n为所述crossbar阵列结构的行数,m为所述crossbar阵列结构的列数。

有益效果

由于采用了上述的技术方案,本发明与现有技术相比,具有以下的优点和积极效果:本发明采用软件方式进行神经网络的容错,通过减少硬件的使用,大大简化了电路的复杂度,减少了芯片的面积,整个系统功耗较小,便于存储阵列之后的大规模集成。结合忆阻器交叉阵列的器件特性,实现了在其上运行的神经网络算法的稳定性和准确率,保证了神经网络的高运算能力、高灵活性以及高实时性的特性。

附图说明

图1为忆阻器crossbar结构图;

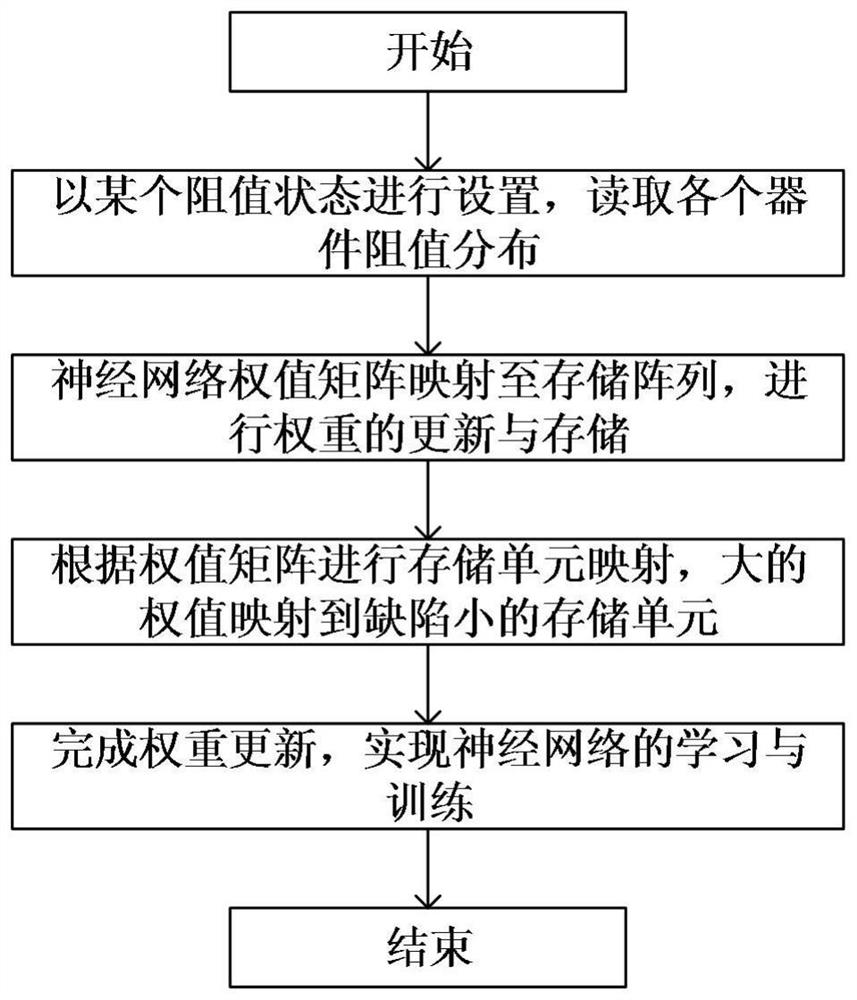

图2为本发明实施方式的基于忆阻器的神经网络容错方法的流程图;

图3为相变存储器理想阻值分布图;

图4为相变存储器实际阻值分布图;

图5为相变存储器阻值存储变化示意图。

具体实施方式

下面结合具体实施例,进一步阐述本发明。应理解,这些实施例仅用于说明本发明而不用于限制本发明的范围。此外应理解,在阅读了本发明讲授的内容之后,本领域技术人员可以对本发明作各种改动或修改,这些等价形式同样落于本申请所附权利要求书所限定的范围。

本发明的实施方式涉及一种基于忆阻器的神经网络容错方法,该方法是基于忆阻器crossbar阵列结构,如图1所示。

忆阻器是包括相变存储器等在内的一系列有存储记忆功能的存储器。神经网络本身有一定的容错能力,但由于忆阻器器件本身存在缺陷,通过算法减少误差能够提升神经网络的泛化能力。

通过权值矩阵到存储阵列的映射,模拟神经网络中权值的重量,采用映射的方式进行权值的存储与更新,减少忆阻器器件自身的缺陷,具有高运算能力和低功耗,提高了神经网络的稳定性和准确率。

本实施方式的一种基于相变存储器的神经网络容错方法,主要流程如图2所示。在进行神经网络权值矩阵的存储时,以某个电阻状态为目标,读出器件电阻以获得存储阵列中的忆阻器电阻的分布。对每个忆阻器器件进行读取,并将所有其他的忆阻器保持在高阻态。

在进行权重更新的时候,通过一种自适应的权值矩阵映射算法,将大的权值映射到缺陷小的忆阻器器件上。通过规避忆阻器器件本身的缺陷带来的可靠性问题,实现神经网络权值存储的高准确率。如此反复,完成神经网络的学习与训练过程。

本实施方式的基于相变存储器的神经网络容错方法旨在神经网络训练前将影响神经网络准确率的因素可能性降到最小,本实施方式省去了在训练前对已损坏的忆阻单元进行的查询搜索,尽可能地在神经网络学习训练时规避由于忆阻单元缺陷可能造成权值影响这一因素。本实施方式在开始进行权值映射时直接将大的权值映射到缺陷小的忆阻器器件上,从源头上尽量避免了由于忆阻器器件的缺陷所带来的神经网络学习训练的错误,减少了电路的能耗,提高了神经网络的稳定性和准确率。

下面以相变存储器crossbar阵列为例进行具体阐述:

相变存储器是基于Ovshinsky效应的元件,通过相变材料在晶态和非晶态之间进行相互转化,带来电阻差异的变化,实现信息的多值存储,如图3所示(从左到右阻值依次增大)。但是相变存储器由于其自身特性,相变存储单元阻值会随着时间的变化产生阻值漂移,阻值漂移情况随着相变材料的阻值变大而越来越严重,甚至于其他相邻阻态发生交叠,导致数据错误,如图4所示,在利用其多值存储特性应用于神经网络时会出现准确率较低的问题。

本实施方式的一种基于忆阻器的神经网络算法主要流程如下:

在进行神经网络的学习时,权值矩阵映射到相变存储器crossbar中每个相变存储器的电导进行表示,即每个相变存储器单元的阻值是确定的。在进行神经网络的训练时,由于权值矩阵的调节反映在存储单元矩阵中即是各个存储器的阻值的变化。

由于相变存储器自身存在阻值漂移,在进行权值调整前,读出各个相变单元的阻值,根据需要变化的权重进行调节。通过将权值大的映射到漂移小的器件上,尽可能多的减少阻值的漂移,进行权值的存储与更新,完成神经网络的高精度学习与训练。具体如下:

在进行神经网络权值矩阵的存储时,以某个电阻状态为目标编程,读出器件电阻以获得存储阵列中的忆阻器电阻的分布。对每个忆阻器器件进行读取,并将所有其他的忆阻器保持在高阻态。通过预先读取的方法,调整了神经网络的算法。

在进行权重更新的时候,通过自适应的方法,将权值矩阵与存储阵列进行映射,通过算法将权值大的权重映射到漂移小的器件上,根据权值调整的幅度,将调整幅度大的权重映射到阻值漂移小的器件上,权值矩阵映射到存储阵列中进行存储与更新,完成神经网络的学习与训练。

如图5所示,若此时相变存储器单元阻值处在箭头所示位置时,由于受到器件自身缺陷影响,阻值增大会导致漂移情况更加严重,故此单元存储时可以存储小于或等于其此时阻值的阻态,整个交叉阵列权值的存储按照上述规则进行,从而尽可能地减少阻值漂移产生的错误对整个神经网络的影响。

不难发现,本发明通过软件方式进行神经网络容错,算法简单,便于网络应用;通过权值矩阵与忆阻器交叉阵列的自适应调整,实现神经网络中权值的存储与更新,减少相变存储器的漂移带来的可靠性问题,实现了在其上运行的神经网络算法的稳定性和准确率,保证了神经网络的高运算能力、高灵活性以及高实时性的特性,为未来构建大规模忆阻器神经形态网络提供一种有效的网络容错算法。

- 一种基于忆阻器的神经网络容错方法

- 一种针对忆阻器误差的忆阻器存储器神经网络训练方法