WLAN中增强的高吞吐量同步和受约束的多链路传输

文献发布时间:2023-06-19 09:32:16

相关引用

本发明主张递交于2019年7月12日,号码为62/873,364以及递交于2019年8/16日,号码为62/888,015的美国临时专利申请案的优先权,上述列出的申请案内容以引用方式并入本文。

技术领域

本发明总体上涉及无线通信,并且更具体地,涉及无线局域网(wireless localarea network,简称WLAN)中的增强的高吞吐量(enhanced high-throughput,简称EHT)同步且受约束的多链路传输。

背景技术

除非本文另外指出,否则本节中描述的方法不是下面列出的权利要求的现有技术,并且不被包括在本节中而被承认为现有技术。

WLAN中的站点(station,简称STA)可利用其自己的EDCA参数(例如最小竞争窗口(minimum contention window,简称CWmin),最大竞争窗口(maximum contention window,简称CWmax),仲裁帧间间隔(arbitration inter-frame space,简称AIFS),竞争窗口(contention window,简称CW)和重试计数器(retry counter),在每个链路上执行独立的增强的分布式信道存取机制(Enhanced Distributed Channel Access,简称EDCA)。在获得发送机会(transmit opportunity,简称TXOP)之后,STA可发起帧交换序列的传输。每个媒体存取控制(Media Access Control,简称MAC)协议数据单元(Media Access ControlProtocol Data Unit,简称MPDU)可被独立地编码为多个频率段之一。

当STA同时发送和接收帧时,可能存在装置内共存(in-device coexistence,简称IDC)干扰。当在2.4GHz频段和5GHz频段之间同时进行发送和接收(transmit&receive,简称Tx&Rx)操作时,所产生的IDC干扰往往可以忽略不计。但是,当在5GHz频段和6GHz频段之间同时进行Tx和Rx操作时,根据操作信道的频率间隔,产生的IDC干扰可能会发生变化并对吞吐量产生负面影响。因此,需要一种用于WLAN中的EHT同步和受约束的多链路传输的解决方案。

发明内容

以下发明内容仅是说明性的,而无意于以任何方式进行限制。即,提供以下概述以介绍本文描述的新颖的和非显而易见的技术的概念、重点、益处和优点。选择的实现在下面的详细描述中进一步描述。因此,以下概述并非旨在标识所要求保护的主题的必要特征,也不旨在用于确定所要求保护的主题的范围。

本发明的目的是提供与WLAN中的EHT同步和受约束的多链路传输有关的方案、概念、设计、技术、方法和装置。在根据本发明的各种提出的方案下,前述IDC干扰问题可被避免或减轻。

在一方面,一种方法可包括:通过第一频带中的第一链路和不同于第一频带的第二频带中的第二链路,第一装置的处理器利用执行操作与第二装置通信。例如,该方法可包括处理器在第一链路和第二链路中的每一个上执行独立的EDCA。该方法还可包括处理器获得TXOP。该方法还可以包括处理器将第一链路和第二链路上的发送和接收的开始时间和结束时间之一或两者同步,以避免由于发送和接收同时发生而引起IDC干扰。

在另一方面,一种方法可以包括:通过第一频带中的第一链路和不同于第一频带的第二频带中的第二链路,第一装置的处理器利用执行操作与第二装置通信。例如,该方法可包括处理器在第一链路和第二链路中的每一个上执行独立的EDCA。该方法还可包括处理器获得TXOP。该方法可进一步包括处理器避免在第一链路和第二链路上同时发送和接收以避免引起IDC干扰。

值得注意的是,尽管本文提供的描述可能是在特定无线存取技术,网络和网络拓扑(例如Wi-Fi),所提出的概念、方案以及任一(多种)变体/衍生物的上下文中可在其他类型的无线电接入技术、网络和网络拓扑中,并通过其他类型的无线电接入技术、网络和网络拓扑来实现,例如但不限于蓝牙,ZigBee,第五代(5th Generation,简称5G/新无线电(NewRadio,简称NR),长期演进(Long-Term Evolution,简称LTE),高级LTE,高级LTE Pro,物联网(Internet-of-Things,简称IoT),工业物联网(Industrial IoT,简称IIoT)和窄带物联网(narrowband IoT,简称NB-IoT)。因此,本发明的范围不限于本文描述的示例。

附图说明

下列图示用以提供本发明的进一步理解,并被纳入且构成本发明的一部分。这些图示说明了本发明的实施方式,并与说明书一起用以解释本发明的原理。为了清楚地说明本发明的概念,与实际实施方式中的尺寸相比一些元素可以不按照比例被示出,这些图示无需按照比例绘制。

图1示出其中可实现根据本发明的各种解决方案和方案的示例网络环境的图。

图2示出示例方案图。

图3示出根据本发明的示例场景的图。

图4示出根据本发明的示例场景的图。

图5示出根据本发明的示例场景的图。

图6示出根据本发明的示例场景的图。

图7示出根据本发明的示例场景的图。

图8示出根据本发明的示例场景的图。

图9示出根据本发明的示例场景的图。

图10示出根据本发明的示例场景的图。

图11示出根据本发明的示例场景的图。

图12示出根据本发明的示例场景的图。

图13示出根据本发明的示例场景的图。

图14示出根据本发明的示例场景的图。

图15示出根据本发明的示例场景的图。

图16示出根据本发明的实施方式的示例通信系统的框图。

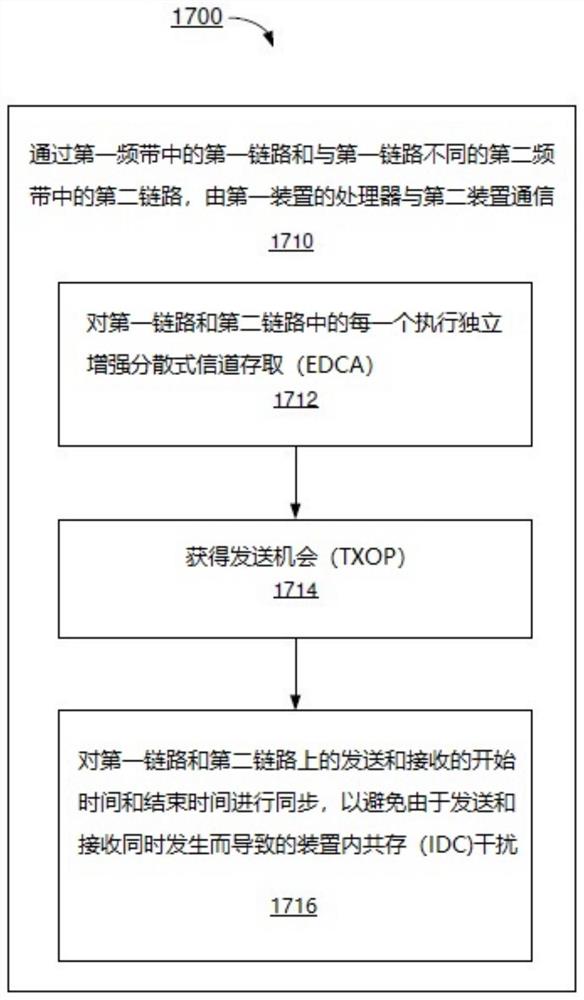

图17是根据本发明的实施方式的示例过程的流程图。

图18是根据本发明的实施方式的示例过程的流程图。

具体实施方式

下文描述了本发明所要求保护的主题的详细实施例和实施方式。然而,应该理解的是,所公开的实施例和实施方式仅仅是对要求保护的主题的说明,其可以以各种形式体现。然而,本发明可以以许多不同形式实施,并且不应该被解释为限于本发明阐述的示例性实施例和实施方式。而是,这些示例性实施例和实施方式的提供,使得本发明的描述是彻底和完整的,并且将向本领域技术人员充分传达本发明的范围。在以下描述中,可以省略公知特征和技术的细节以避免不必要地模糊所呈现的实施例和实施方式。

概述

根据本发明的实施方式涉及与WLAN中的EHT同步和受约束的多链路传输有关的各种技术、方法、方案和/或解决方案。根据本发明,多种可能的解决方案可单独地或联合地实现。即,尽管该些可能的解决方案可以在下面分别描述,但是该些可能的解决方案中的两个或更多个可以以一种或另一种组合实现。

图1示出了其中可实现根据本发明的各种解决方案和方案的示例网络环境100。图2-图15示出了根据本发明的在网络环境100中的各种提出的方案的实现的示例。参考图1-图15,以下提供对各种提议方案的描述。

如图1所示,网络环境100可包括根据一个或多个电气和电子工程师协会(Institute of Electrical and Electronics Engineers,IEEE)802.11标准在WLAN中无线通信的通信实体110和通信实体120。例如,通信实体110可以是STA(例如,发送STA)或接入点(access point,简称AP),并且通信实体120可以是对等STA,请求STA或AP。在根据本发明的各种提出的方案下,通信实体110和通信实体120可被配置为根据在此描述的各种提出的方案来执行EHT同步和受约束的多链路传输。

图2标出了异步多链路传输的示例场景200。参考图2,在场景200中,作为STA的通信实体110可利用其自己的EDCA参数(例如,CWmin,CWmax,AIFS,CW和重试计数器)在每个链路上执行独立的EDCA信道存取。在获得TXOP之后,通信实体110可发起帧交换序列的传输。每个MPDU可被独立地编码到多个频率段之一。

图3示出了根据本发明的同步和受约束的多链路传输的示例场景300。参考图3,在根据本发明的关于同步多链路传输的建议方案下,在获得TXOP之后,通信实体110可同步开始时间和/或结束时间(在本文中可互换地称为“开始时间和结束时间中的一个或两个”),以避免IDC干扰。还参考图3,在根据本发明的关于受约束的多链路传输的另一建议方案下,在获得TXOP之后,通信实体110不在多链路通信上同时发送或接收帧以避免IDC干扰。

在提出的方案下,如果其他主信道的物理载波监听(physical carrier sense,CS)和虚拟CS均处于空闲状态,则对于无法获取TXOP用于EDCA的其他主信道的早期存取被允许。物理CS可在点协调功能(point coordination function,简称PCF)优先帧间空间(priority inter-frame space,简称PIFS)期间被检查。多个MPDU中的每个MPDU可被独立地编码为多个频率段之一,或者,多个MPDU可被联合地编码为一个以上的频率段。关于受约束的多链路传输,作为STA的通信实体110可对多个频率段执行独立的编码和/或解码时使用独立的离散傅立叶逆变换(independent inverse discrete Fourier transform,简称IDFT)或离散傅立叶变换(discrete Fourier transform,简称DFT)。

同步多链路传输

图4示出了根据本发明的同步多链路传输中的第一物理层一致性过程(PhysicalLayer Conformance Procedure,简称PLCP)物理层服务数据单元(PHY Service DataUnit,简称PSDU)同步的示例场景400。参考图4,在根据本发明的提议方案下,在同步多链路传输中可存在各种PPDU同步机制。在提出的方案下,通信实体110可以以相同的PPDU格式,相同的保护间隔(guard interval,简称GI)和相同的长训练字段(long training field,简称LTF)类型在多链路上发送帧。此外,通信实体110可以在相同的PPDU格式,相同的GI和相同的LTF类型的多链路传输上请求响应帧。例如,当通信实体110在链路上发送高效率(high-efficiency,简称HE)单个用户(single-user,简称SU)PPDU时,通信实体110可在其他链路上仅发送HE SU PPDU(例如,非高吞吐量(non-high throughput,简称non-HT)PPDU,HT PPDU,超高吞吐量(very high throughput,简称VHT)PPDU,HE多用户(multi-user,简称MU)PPDU,HE扩展范围(extended-range,简称ER)SU PPDU,基于HE触发(trigger-based,简称TB)的PPDU不能在其他链路上传输)。

在提出的方案下,为了同步多链路传输上的发送和接收的开始时间和/或结束时间,预HE调制字段的持续时间在多链路传输上可以是相同的,HE调制字段的持续时间在多链路传输上也可以相同。值得注意的是,在HE PPDU中,传统短训练字段(legacy shorttraining field,简称L-STF),传统长训练字段(legacy long training field,简称L-LTF),传统信号字段(legacy signal field,简称L-SIG),重复传统信号字段(repeatedlegacy signal field,简称RL-SIG),高效率信号A字段(high-efficiency signal Afield,HE-SIG-A)和高效率信号B字段(high-efficiency signal B field,简称HE-SIG-B)可被称为预HE调制字段,而高效率短训练字段(HE-STF),高效率长训练字段(HE-LTF)和数据字段可被称为HE调制字段。此外,预HE调制字段和HE调制字段具有不同的符号持续时间。

图5示出了根据本发明的同步多链路传输中的PPDU同步的示例场景500。参考图5,在提出的方案下,第一PPDU同步机制可涉及在多链路传输上的HE(ER)SU PPDU的传输。具体地,在第一PPDU同步机制中,对于HE(ER)SU PPDU的预HE调制字段,不需要附加规则,因为HE(ER)SU PPDU的预HE调制字段不变。然而,对于HE(ER)SU PPDU的HE调制字段,通信实体110可在聚合MPDU(aggregate MPDU,简称A-MPDU)中包括帧结束(end of frame,简称EOF)填充子帧,以满足在多链路传输上HE调制字段的相同持续时间要求。例如,通信实体110可在获得用于EDCA的TXOP的主链路上发送的PPDU的A-MPDU中不包括EOF填充子帧。

图6示出了根据本发明的同步多链路传输中的PPDU同步的示例场景600。参考图6,在提出的方案下,第二PPDU同步机制可涉及在多链路传输上的HE MU PPDU的传输。具体地,在第二PPDU同步机制中,在多链路传输上,预HE调制字段中的HE-SIG-B字段的符号数目可以不同。通信实体110可在用户专用字段中包括一个或多个填充用户字段,以满足多链路传输上的预HE调制字段的相同持续时间要求。例如,填充用户字段的站点标识(stationidentifier,简称STA-ID)子字段可被设置为预定值(例如2046)。对于HE MU PPDU的HE调制字段,通信实体110可以在A-MPDU中包括EOF填充子帧,以满足在多链路传输上HE调制字段的相同持续时间要求。当作为STA的通信实体110将HE MU PPDU发送到单个接收者(例如,作为AP的通信实体120)时,通信实体110可在获得TXOP用于EDCA的主链路上发送的PPDU的A-MPDU中不包括EOF填充子帧。

在根据本发明的在同步多链路传输中的PPDU同步的建议方案下,在多链路传输上发送的响应帧的发送时间可以不同。这是因为在多链路传输上发送的响应帧的调制和编解碼方案(modulation and coding scheme,简称MCS)或帧大小(例如,确认(acknowledgement,简称Ack)帧或块确认(block acknowledgement,简称BlockAck)帧)可能不同。为了使多链路传输上的响应帧的发送和接收的开始时间和/或结束时间同步,可能需要MAC层物理(physical,简称PHY)层填充。例如,除非在请求的STA(例如,通信实体120)不请求特定的PPDU格式(例如,触发帧的HE TB PPDU)时,发送请求帧的STA(例如,通信实体110)可使用HE SU PPDU。

在根据本发明的在同步多链路传输中的PPDU同步的建议方案下,在收到请求帧之后,多链路传输上的响应帧的传输的开始时间可在短帧间间隔(short inter-framespace,简称SIFS)上同步。此外,如下所述,响应帧在多链路传输上的传输的结束时间可被确定为三个选项之一。

图7示出了根据本发明的在多链路传输上响应帧的传输的结束时间的第一选项的示例场景700。参考图7,在第一选项中,在多链路传输上被请求的PPDU(例如,BlockAck)的发送时间被确定为根据每条链路的请求PPDU的传输向量(transmit vector,简称TXVECTOR)参数计算出的响应帧的最小发送时间的最长值。例如,最初,STA(例如,通信实体110)可基于5GHz链路上的请求PPDU的TXVECTOR参数来计算响应帧的第一最小发送时间(TXTIME1)。此外,STA可基于6GHz链路上的请求PPDU的TXVECTOR参数来计算响应帧的第二最小发送时间(TXTIME2)。然后,TXTIME1和TXTIME2之间的最大值(例如,MAX(TXTIME1,TXTIME2))被确定为回应帧在5GHz链路和6GHz链路上的发送时间。接下来,MAC或PHY填充可在多链路传输上被应用,以在5GHz链路和6GHz链路上满足相同的发送时间。

图8示出了根据本发明的在多链路传输上响应帧的传输的结束时间的第二选项的示例场景800。参考图8,在第二选项中,携带响应帧的被请求的HE PPDU的L-SIG长度字段的值可在请求帧的A-控制字段中提供。例如,请求STA(例如,通信实体120)可确定响应帧的发送时间,如在请求帧中携带的L-SIG长度A-控制字段中所指定的。在必要的情况下,MAC或PHY填充可被应用于多链路传输,以满足5GHz链路和6GHz链路上相同的发送时间。

图9示出了根据本发明的在多链路传输上响应帧的传输的结束时间的第三选项的示例场景900。参考图9,在第三选项中,其中EDCA获取TXOP的主链路可在请求帧的A-控制字段中被指定。响应的STA(例如,通信实体110)可基于与主链路的基本服务集合(basicservice set,简称BSS)相关的候选MCS集合(Candidate MCS Set)来确定响应帧的发送时间。因此,从与由主链路A-控制字段的值所指示的链路的BSS相关的Candidate MCS Set,发送时间(TXTIME)可被确定。

在根据本发明的在同步多链路传输中的PPDU同步的建议方案下,一些控制帧可能有必要携带于非HT(重复)PPDU中。例如,发送请求(request to sent,简称RTS)帧和清除发送(clear to send,简称CTS)帧可携带于非HT(重复的)PPDU中,以保护传统STA的网络分配向量(network allocation vector,简称NAV)。关于多链路传输上的非HT(例如,重复的)PPDU中的RTS和CTS帧的交换,在每个链路上发送的RTS帧的特定信息可以是特定链路的值,并且该些信息在多链路传输中可以是不同的或相同的。该些信息可包括例如但不限于非HT(带宽信令)中的信道带宽,接收器地址,发射器地址和信道带宽。但是,STA(例如,通信实体110)可以在多链路传输上使用相同的MCS和相同的持续时间信息。

图10示出了根据本发明的在多链路传输上的非HT PPDU中的RTS和CTS帧交换的示例场景1000。参考图10,为了满足相同的发送时间,在5GHz链路和6GHz链路上发送的RTS帧可使用相同的MCSm,并且在5GHz链路和6GHz链路上发送的CTS帧可使用相同的MCSn。

在提出的方案下,为了允许发送方STA计算持续时间/ID字段的内容,响应多链路传输上接收到的RTS帧的STA可在多链路传输上以链路主速率或者以如下所述多链路可选速率发送其CTS帧。

关于多链路主速率,多链路主速率可被定义为与多链路传输相关联的BSS的BSS基本速率集合(BSS Basic Rate Set)参数中的公共速率(common rate)的最高速率,该多链路主速率小于或等于先前RTS帧的速率(或非HT参考速率)。如果BSSBasicRateSet参数中的速率没有满足这些条件,则多链路主速率可被定义为与多链路传输相关联的PHY的强制性公共速率的最高速率,该速率小于或等于先前RTS帧的速率(或非HT参考速率)。

关于多链路可选速率,具有多链路可选速率的帧的持续时间可与以多链路主速率的帧的持续时间相同。多链路可选速率可以是与多链路传输相关的BSS的BSSBasicRateSet参数中的公共速率,或者可以是与多链路传输相关的PHY的强制性公共速率。以多链路可选速率的帧的调制等级可以与由IEEE规范选择的用于选择速率或MCS的多链路主速率的调制等级相同(例如,第10.6.6.5.2节)。如果存在非HT PPDU CTS帧,则STA可以以多链路主要速率或多链路可选速率发送非HT PPDU CTS帧。

然而,在响应的STA没有从所有链路接收到CTS帧的情况下,回应的STA计算出的多链路主要速率可能与响应的STA所期望的不同。当与多链路传输相关的BSS的BSSBasicRateSet参数不相同时,或者当与多链路传输关联的PHY的强制速率不同时,该种情况可能会出现。为了避免该问题,RTS帧可具有用于指定是否在获得TXOP用于EDCA的主链路上发送它的指示。回应的STA可标识在主链路上发送的RTS帧。即,响应的STA可在多链路传输上以主要速率或与主链路的BSS相关的可选速率来发送其CTS帧。

在根据本发明的提出的方案下,在控制帧中,接收器地址(receiver address,简称RA)和/或发送器地址(transmitter address,简称TA)字段可被用于指示主链路。例如,在非主链路上发送的控制帧的RA字段可具有预定值(例如,发送对应的控制帧的STA的MAC地址,即发送器地址)。在非主链路上发送的控制帧的TA字段可具有预定值(例如,所发送的控制帧的接收STA的MAC地址,即接收器地址)。在提出的方案下,RA和/或TA字段的交换机制被应用于以下三个模型之一,即:仅RA字段交换,仅TA字段交换以及RA和TA字段双交换。除主链路的信号外,交换机制还可用于指示其他信息。另外,当交换机制被使用时,加扰序列的前7位可被重新定义。

在当前的IEEE规范下,该些位用于指示诸如CH_BANDWIDTH_IN_NON_HT和DYN_BANDWIDTH_IN_NON_HT的参数。

在提出的方案下,当对等STA在多个链路上接收到RTS帧时,STA可执行特定操作。首先,在RTS帧的RA被设置为自身并且RTS帧的TA被设置为第三方STA的MAC地址的情况下,STA可确定主链路。其次,在RTS帧的RA被设置为在主链路上接收到的RTS帧的TA和/或主链路上收到的RTS帧的TA被设置为RTS的RA的情况下,STA可确定非主链路。值得注意的是,在对等STA仅在非主链路上接收到RTS帧的情况下,STA可能不会以CTS帧作为响应。

受约束的多链路传输

当STA(例如,通信实体110)在具有不同TXVECTOR参数(例如,PPDU格式,GI或LTF类型)的多链路传输上发送帧时,可能难以准确地同步多链路上的传输的开始时间和结束时间。在根据本发明的提出的方案下,可能存在关于受约束的多链路传输的定时精度要求。在提出的方案下,多链路上的传输的开始时间和结束时间可在表示为aSIFSTime+aSignalExtension的持续时间内同步。为了满足该要求,STA可应用MAC填充,PHY填充和/或分组扩展(packet extension,简称PE)。此处,参数aSIFSTime在2.4GHz频段运行时可能为10μs,而在5GHz频段运行时可能为16μs。此外,参数aSignalExtension在5GHz频段工作时可能为0μs,而在2.4GHz频段工作时可能为6μs。因此,aSIFSTime+aSignalExtension的持续时间可能为16μs。

在提出的方案下,当相同的帧间间隔(例如,SIFS,PIFS或AIFS)在多链路传输上使用时,如果多链路上的传输的结束时间在aSIFSTime+aSignalExtension内同步,后续传输的开始时间也可在aSIFSTime+aSignalExtension内同步。因此,除非帧是TXOP的初始帧,否则仅多链路上的传输的结束时间被关注。即,不需要同步初始帧的开始时间。假设由正交频分复用(orthogonal frequency-division multiplexing,简称OFDM)符号未对准引起的定时误差限制在16μs以内,以满足定时精度要求(例如,多条链路上传输的结束时间可在持续时间aSIFSTime+aSignalExtension内同步),仅MAC填充(例如,EOF填充子帧或填充子字段)可能是必需的。PHY上可能没有任何更改。

图11示出了根据本发明的受约束的多链路传输的定时精度要求的示例场景1100。参考图11所示,多链路上的传输的结束时间之间的差可小于SIFS(例如,aSIFSTime+aSignalExtension)。在方案1100中,发送(transmission,简称TX)和接收(receiving,简称RX)不重叠。图12示出了根据本发明的受约束的多链路传输的定时精度要求的示例场景1200。参考图12,在场景1200中,在具有多链路能力的装置内的STA(例如,通信实体110和通信实体120)的SIFS定时精度是不同的。例如,基于对HE TB PPDU的IEEE 802.11ax要求,SIFS定时精度可能在±0.4μs内不同。在该种情况下,TX和RX可能会重叠。

在根据本发明的提出的方案下,为了解决SIFS定时精度误差的问题,多种选择中的一种可被采取。根据第一选项(选项1),当对等STA在多链路上发送帧到STA时,STA(例如,通信实体110)可请求其对等STA(例如,通信实体120)包括不需要解码的最小填充信息。例如,该最小填充信息可包括EOF填充子帧,填充子字段或PE(例如4μs,8μs,12μs或16μs)。最小填充信息的时间要求可独立地发送给对等STA。因此,TX和RX可在填充信息被发送的时间内重叠。

根据第二选项(选项2),STA可增加定时精度要求。例如,多链路上传输的结束时间可在aSIFSTime+aSignalExtension–TimingErrorMargin的持续时间内同步。当STA从对等STA接收到定时误差余量(TimingErrorMargin)信息时,TimingErrorMargin可指示对等STA可在从请求帧的末尾开始的aSIFSTime+aSignalExtension±TimingErrorMargin的持续时间内对STA做出回应。

值得注意的是,由于在STA接收PE时,接收STA不会对PE进行解码(例如4μs,8μs,12μs或16μs),因此STA可同时在其他链路上发送帧。在PE内的TX和RX重叠被允许的情况下,由于STA可在不等待PE的接收的情况下更早发送帧,因此性能可稍微改善。在可选方法中,除了多条链路上的PE之外的传输的结束时间在aSIFSTime+aSignalExtension的持续时间内同步。因此,MAC填充(例如,EOF填充子帧和填充子字段)可被应用。

图13示出了根据本发明的受约束的多链路传输的定时精度要求的示例场景1300。参考图13,在场景1300中,除了PE之外的传输的结束时间之间的差可小于SIFS。因此,TX和RX可在PE内重叠。为了解决SIFS定时精度误差的问题,上述选项1和/或选项2可被应用。

在根据本发明的提出的方案下,对于HE TB PPDU传输,多链路上的传输的开始时间可被对准。在此种情况下,STA(例如,通信实体110)可在4μs、8μs、12μs或16μs中选择PE,使得传输的结束时间之间的差不大于aSlotTime。在提出的方案下,PE字段的持续时间可由数据字段的最后一个或多个OFDM符号中的前-前向纠错(forward error correction,简称FEC)填充因子值以及TXVECTOR参数NORMAL_PACKET_PADDING确定。因此,STA可设置前-FEC填充因子值和TXVECTOR参数NORMAL_PACKET_PADDING以满足以上条件。

图14示出了根据本发明的受约束的多链路传输的定时精度要求的示例场景1400。参考图14,在场景1400中,6GHz和5GHz的STA可同时发送回应帧。但是,6GHz的帧间空间可能比SIFS长,而SIFS可能短于PIFS。图15示出了根据本发明的受约束的多链路传输的定时精度要求的示例场景1500。

在根据本发明的提出的方案下,当AP多链路装置(multi-link device,MLD)将对准携带一帧的下行链路(downlink,简称DL)PPDU的结束时间,该帧请求一实时响应,并且该DL PPDU在多链路上被同时发送到相同的非实时发送-以及-接收(non-simultaneous-transmit-and-receive,简称non-STR)非-AP MLD,AP MLD可确保发送DL PPDU的结束时间之间的差小于特定持续时间(例如,小于SIFS)。

在根据本发明的提议的方案下,关于PHY层管理实体(PHY layer managemententity,简称PLME)服务接入点(service access point,简称SAP)接口,PLMN-TXTIME.confirm原语(primitive)可被用来指示发送在相应的PLME-TXTIME.request原语中描述的PPDU所需的时间。该原语可被表示为PLME-TXTIME.confirm(TXTIME,PSDU_LENGH[])。TXTIME表示发送在相应的PLME-TXTIME.request原语中描述的PPDU所需的时间(例如,以微秒为单位)。如果计算的时间包括分数微秒,并且对应的PLME-TXTIME中的TXVECTOR参数FORMAT.request原语不是HE_SU、HE_MU、HE_TB或HE_ER_SU,则非定向多千兆位(non-directional multi-gigabit,简称non-DMG)STA可将TXTIME值舍入到下一个更高的整数。如果对应的PLME-TXTIME.request原语中的TXVECTOR参数FORMAT是HE_SU、HE_MU、HE_TB或HE_ER_SU,则非DMG STA可能不会将TXTIME值向上或向下取整。DMG STA可能无法向上或向下舍入TXTIME值。PLCP服务数据单元(Service Data Unit,简称PSDU)(PSDU_LENGH[])参数的长度可以是大小为TXVECTOR参数NUM_USERS的数组。数组中的每个值可指示为该数组索引所代表的用户填充PPDU所需的八字节(octet)的数目。仅当TXVECTOR FORMAT参数非常高的吞吐量(very high-throughput,简称VHT)时,该参数才可能存在。

PLME-TXTIME.request原语可以是对PHY的请求,以计算将PPDU发送到无线介质上所需的时间,PPDU包含指定长度的PSDU并使用指定格式,数据速率和信令。该原语可表示为PLME-TXTIME.request(TXVECTOR,REMAINING_TXTIME[])。TXVECTOR代表MAC子层提供给本地PY实体以发送PSDU的参数列表。IEEE规范第8.3.4.4节列出了所需的最低PHY参数。REMAINING_TXTIME[]参数是同时链路计数大小的数组。数组中的每个值指示在由该数组索引表示的链路上传输进行中的PPDU所需的剩余时间(例如,以微秒为单位)。仅当TXVECTOR FORMAT参数为EHT并且至少一个PPDU在多条链路之一上传输时,该参数才存在。当MAC子层需要确定传输特定PSDU所需的时间时,此原语可由MAC子层发布给PHY实体。PHY实体接收该原语的效果是生成一个PHY-TXTIME.confirm原语,该原语传达了所需的发送时间。当存在REMAINING_TXTIME[]参数时,所需的发送时间可能在aSIFSTime+aSignalExtension的差值之内,并且所有时间都在REMAINING_TXTIME[]参数中指示。因此,当STA(例如,通信实体110)从其对等STA(例如,通信实体120)接收到定时误差余量(TimingErrorMargin)的信息时,aSIFSTime+aSignalExtension的差值可以是aSIFSTime+aSignalExtension-TimingErrorMargin。

说明性实施

图16示出了根据本发明的实施方式的至少具有示例装置1610和示例装置1620的示例系统1600。装置1610和装置1620中的每一个可以执行各种功能以实现本文中描述的与WLAN中的EHT同步和受约束的多链路传输有关的方案,技术,过程和方法,包括以上关于各种提议的设计,概念,上述方案,系统和方法以及以下过程。例如,装置1610可以是通信实体110的示例实现,并且装置1620可以是通信实体120的示例实现。

装置1610和装置1620中的每一个可以是电子装置的一部分,该电子装置可以是STA或AP,诸如便携式或移动装置,可穿戴装置,无线通信装置或计算装置。例如,装置1610和装置1620中的每一个可被实现在智能电话,智能手表,个人数字助理,数字照相机或诸如平板计算机,膝上型计算机或笔记本计算机的计算装置中。装置1610和装置1620中的每一个也可以是机器类型装置的一部分,该机器类型装置可以是诸如非移动式装置,固定装置,家用装置,有线通信装置或计算装置的物联网(Internet of Things,简称IoT)装置。例如,装置1610和装置1620中的每一个都可以在智能恒温器,智能冰箱,智能门锁,无线扬声器或家庭控制中心中实现。当装置1610在网络装置中实现或作为网络装置实现时,装置1610和/或装置1620可以在诸如WLAN中的AP的网络节点中实现。

在一些实施方式中,装置1610和装置1620中的每一个可以以一个或多个集成电路(integrated-circuit,简称IC)芯片的形式实现,例如但不限于,一个或多个单核处理器,一个或多个更多的多核处理器,一个或多个精简指令集计算(reduced-instruction setcomputing,简称RISC)处理器,或一个或多个复杂指令集计算(complex-instruction-set-computing,简称CISC)处理器。在上述各种方案中,装置1610和装置1620中的每一个可在STA或AP中实现或被实现为STA或AP。装置1610和装置1620中的每一个可包括图16中所示的例如分别具有处理器1612和处理器1622的该些组件中的至少部分。装置1610和装置1620中的每一个可以进一步包括与本发明的所提出的方案不相关的一个或多个其他组件(例如,内部电源,显示设备和/或用户周边装置),并且因此,装置1610和装置1620的该组件在图16中未示出,为了简化和简洁起见,也未在以下描述。

在一方面,处理器1612和处理器1622中的每一个可以以一个或多个单核处理器,一个或多个多核处理器,一个或多个RISC处理器或一个或多个CISC处理器的形式实现。也就是说,即使在本文中使用单数术语“处理器”来指代处理器1612和处理器1622,根据本发明,处理器1612和处理器1622中的每一个在一些实施方式中可包括多个处理器,而在其他实施方式中可包括单个处理器。在另一方面,处理器1612和处理器1622中的每一个可以以具有电子部件的硬件(以及可选地,固件)的形式实现,该电子部件包括例如但不限于一个或多个晶体管,一个或多个二极管,一个或多个电容器,一个或多个电阻器,一个或多个电感器,一个或多个忆阻器和/或一个或多个变容二极管,其被配置和布置为实现根据本发明的特定目的。换句话说,在至少一些实施方式中,处理器1612和处理器1622中的每一个均是专门设计,布置和配置为执行特定任务的专用机器,所述特定任务包括与根据本发明的各种实施方式的WLAN中的EHT同步和受约束的多链路传输有关的该些任务。

在一些实施方式中,装置1610还可包括耦合至处理器1612的收发器1616。收发器1616可无线地发送和接收数据。在一些实施方式中,装置1620还可包括耦合至处理器1622的收发器1626。收发器1626可包括能够无线传输和接收数据的收发器。

在一些实施方式中,装置1610可进一步包括内存1614,该内存1614耦合至处理器1612并且能够被处理器1612存取并且在其中存储数据。在一些实施方式中,装置1620可进一步包括内存1624,该内存1624耦合至处理器1622并且能够被处理器1622存取并且在其中存储数据。内存1614和内存1624中的每一个可包括一种随机存取内存(random-accessmemory,简称RAM),诸如动态RAM(dynamic RAM,简称DRAM),静态RAM(static RAM,简称SRAM),晶闸管RAM(thyristor RAM,简称T-RAM)和/或零电容器RAM(zero-capacitor RAM,简称Z-RAM。可选地或额外地,内存1614和内存1624中的每一个可包括一种只读存储器(read-only memory,简称ROM),诸如掩模(mask)ROM,可程序设计ROM(programmable ROM,简称PROM),可擦除可程序设计ROM(erasable programmable,简称EPROM)和/或电可擦除可程序设计ROM(electrically erasable programmable ROM,简称EEPROM)。可选地或额外地,内存1614和内存1624中的每一个可包括一种非易失性随机存取内存(non-volatilerandom-access memory,简称NVRAM),诸如闪存,固态内存,铁电RAM(ferroelectric RAM,简称FeRAM),磁阻RAM(magnetoresistive RAM,简称MRAM)和/或相变内存。

装置1610和装置1620中的每一个可以是能够使用根据本发明的各种提出的方案彼此通信的通信实体。出于说明性目的而非限制,以下提供了对作为通信实体110的装置1610和作为通信实体120的装置1620的能力的描述。值得注意的是,尽管在WLAN的上下文中提供了下面描述的示例实施方式,但是可以在其他类型的网络中实施相同的实施方式。因此,尽管以下示例实施方式的描述涉及装置1610用作发送装置并且装置1620用作接收装置的场景,但是适用于其中装置1610用作接收装置和1620用作发送装置的另一场景。

在根据本发明的关于同步多链路传输的建议方案下,经由第一频带中的第一链路和经由不同于第一频带的第二频带中的第二链路,装置1610的处理器1612通过特定操作来与装置1620通信。例如,处理器1612可在第一链路和第二链路中的每一个上执行独立的EDCA。另外,处理器1612可获得TXOP。此外,处理器1612可使第一链路和第二链路上的发送和接收的开始时间和/或结束时间同步,以避免由于发送和接收同时发生而引起IDC干扰。

在一些实施方式中,在同步第一链路和第二链路上的发送和接收的开始时间和/或结束时间时,处理器1612可执行特定操作。例如,处理器1612可识别在请求帧中携带的L-SIG长度A-控制字段中的值。另外,处理器1612可基于所识别的值来确定回应于请求帧而将被发送的响应帧的发送时间。此外,处理器1612可在第一链路和第二链路上的发送时间发送回应帧。

在一些实施方式中,在同步第一链路和第二链路上的发送和接收的开始时间和/或结束时间时,处理器1612可在确定发送时间时在第一链路和第二链路上应用MAC层填充,PHY层填充或MAC层填充和PHY层填充两者。

在一些实施方式中,在同步第一链路和第二链路上的发送和接收的开始时间和/或结束时间时,处理器1612可执行特定操作。例如,处理器1612可基于第一链路上的请求PPDU的TXVECTOR参数来计算响应帧的第一最小发送时间。另外,处理器1612可基于第二链路上的另一请求PPDU的另一TXVECTOR参数来计算响应帧的第二最小发送时间。此外,处理器1612可将第一最小发送时间或第二最小发送时间中的较高者确定为响应帧的发送时间。此外,处理器1612可在确定发送时间时在第一链路和第二链路上应用MAC层填充,PHY层填充或MAC层填充和PHY层填充两者。另外,处理器1612可在第一链路和第二链路上的发送时间发送回应帧。

在一些实施方式中,在同步第一链路和第二链路上的发送和接收的开始时间和/或结束时间时,处理器1612可在接收到一个或多个请求帧之后,在SIFS上同步第一链路和第二链路上一个或多个响应帧的发送的开始时间。

在一些实施方式中,在与装置1620进行通信时,在另一主信道的物理CS和虚拟CS都是空闲状态的情况下,处理器1612可执行对没有获得TXOP用于相应的EDCA的该另一主信道的早期存取。在该种情况下,物理CS可以在PIFS期间检查。

在一些实施方式中,在与装置1620通信时,处理器1612可执行以下之一:(a)将多个MPDU中的每个MPDU独立地编码为多个频率段;或者(b)将多个MPDU联合编码为多个频率段。

在一些实施方式中,在同步中,处理器1612可以相同的PPDU格式,相同的GI和相同的LTF类型在第一链路和第二链路上发送一个或多个帧。

在一些实施方式中,在同步中,处理器1612可以相同的PPDU格式,相同的GI和相同的LTF类型在第一链路和第二链路上接收一个或多个回应帧。

在一些实施方式中,在同步第一链路和第二链路上的发送和接收的开始时间和/或结束时间时,处理器1612可执行特定操作。例如,处理器1612可对第一链路和第二链路上的一个或多个预HE调制字段维持相同的持续时间。另外,处理器1612可对第一链路和第二链路上的一个或多个HE调制字段维持相同的持续时间。

在一些实施方式中,一个或多个预HE调制字段可包括以下一个或多个:L-STF,L-LTF,L-SIG字段,RL-SIG字段,HE-SIG-A字段和HE-SIG-B字段。在一些实施方式中,一个或多个HE调制字段可包括以下一个或多个:HE-STF,HE-LTF和数据字段。

在一些实施方式中,在对第一链路和第二链路上的一个或多个HE调制的字段维持相同的持续时间时,处理器1612可在第一链路和第二链路上发送的HESU PPDU或在第一链路和第二链路上发送的HE MU PPDU的一个或多个HE调制字段的A-MPDU中发送一个或多个EOF填充子帧。

在一些实施方式中,在对第一链路和第二链路上的一个或多个预HE调制字段维持相同的持续时间时,处理器1612可在HE-SIG-B字段的用户专用字段中添加一个或多个填充用户字段。

在根据本发明的关于受约束的多链路传输的另一建议方案下,通过第一频带中的第一链路和不同于第一频带的第二频带中的第二链路,装置1610的处理器1612可执行特定操作与装置1620通信。例如,处理器1612可在第一链路和第二链路中的每一个上执行独立的EDCA。另外,处理器1612可获得TXOP。此外,处理器1612可避免同时在第一链路和第二链路上进行发送和接收,以避免引起IDC干扰。

在一些实施方式中,在避免同时在第一链路和第二链路上进行发送和接收时,通过应用MAC层填充、PHY层填充或PE,处理器1612可在预定义的持续时间(例如,aSIFSTime+aSignalExtension)内使第一链路和第二链路上的传输的开始时间和/或结束时间同步。

在一些实施方式中,在同步第一链路和第二链路上的传输的开始时间和/或结束时间时,处理器1612可使第一链路上的第一传输的第一结束时间和第二链路上的第二传输的第二结束时间在缩短的持续时间内同步,缩短的持续时间是通过从预定义的持续时间中减去定时误差余量来确定的。

在一些实施方式中,在进一步同步第一链路和第二链路上的传输的开始时间和/或结束时间时,处理器1612可从装置1620接收与定时误差余量有关的信息,该信息指示装置1620能够从请求帧末尾在预定义的持续时间加上或减去的定时误差余量内做出回应。

在一些实施方式中,在第一链路上的第一传输的第一结束时间与在第二链路上的第二传输的第二结束时间之间的差可以小于SIFS。在此种情况下,第一装置的发送和接收之间可能没有重叠。可选地,当存在SIFS定时精度误差时,第一装置的发送和接收之间的重叠可以是允许的。

在一些实施方式中,装置1610可充当AP MLD,并且装置1620可充当非STR非APMLD。在这样的情况下,在同步第一链路和第二链路上的发送和接收的开始时间和/或结束时间时,处理器1612可对准携带一帧的DL PPDU的结束时间,该帧请求响应,并且该DL PPDU在第一链路和第二链路上被同时发送到装置1620,第一链路上的第一传输的第一结束时间与第二链路上的第二传输的第二结束时间之间的差小于某个持续时间(例如,SIFS)。

在一些实施方式中,在通信时,在另一主信道的物理CS和虚拟CS都是空闲状态的情况下,处理器1612也可执行对没有获得TXOP用于相应的EDCA的该另一主信道的早期存取。在该种情况下,物理CS可在PIFS期间被检查。

在一些实施方式中,在通信时,处理器1612可执行以下之一:(a)将多个MPDU中的每个MPDU独立地编码为多个频率段;或者(b)将多个MPDU联合编码为多个频率段。在该种情况下,在独立地编码多个MPDU中的每个MPDU时,处理器1612可在独立地编码多个MPDU中的每个MPDU时使用独立的DFT或独立的IDFT。

说明性过程

图17示出了根据本发明的实施方式的示例过程1700。过程1700可表示实现上述各种提议的设计,概念,方案,系统和方法的一方面。更具体地,过程1700可代表与根据本发明的WLAN中的EHT同步和受约束的多链路传输有关的所提出的概念和方案的一方面。过程1700可包括块1710和子块1712、1714和1716中的一个或多个所示出的一个或多个操作、动作或功能。尽管被示为离散的块,但是过程1700的各个块可根据所需的实施方式被划分为额外的块,组合成更少的块或删除。此外,过程1700的块/子块可以按照图17所示的循序(或其他顺序)执行。此外,过程1700的一个或多个块/子块可被重复地或迭代地执行。过程1700可由装置1610和装置1620或其任何变型实现或在其中实现。仅出于说明性目的且不限制范围,过程1700在下面一种或多种IEEE 802.11标准的无线网络(例如WLAN)中,在装置1610作为通信实体110(例如,STA或AP)以及装置1620作为通信实体120(例如,对等STA或AP)的上下文中描述。过程1700可从块1710开始。

在1710,过程1700可涉及通过第一频带中的第一链路和不同于第一频带的第二频带中的第二链路,装置1610的处理器1612执行由1712、1714和1716表示的操作与装置1620通信。

在1712,过程1700可包括处理器1612在第一链路和第二链路中的每一个上执行独立的EDCA。过程1700可从1712进行到1714。

在1714,过程1700可涉及处理器1612获得TXOP。过程1700可从1714进行到1716。

在1716,过程1700可包括处理器1612同步第一链路和第二链路上的发送和接收的开始时间和/或结束时间,以避免由于同时发生发送和接收而引起IDC干扰。

在一些实施方式中,在同步第一链路和第二链路上的发送和接收的开始时间和/或结束时间时,过程1700可涉及处理器1612执行特定操作。举例来说,过程1700可涉及处理器1612识别请求帧中携带的L-SIG长度A-控制字段中的值。另外,过程1700可涉及处理器1612基于所识别的值来确定回应请求帧而将要发送的响应帧的发送时间。此外,过程1700可涉及处理器1612在第一链路和第二链路上的发送时间发送回应帧。

在一些实施方式中,在同步第一链路和第二链路上的发送和接收的开始时间和/或结束时间时,过程1700还可包括处理器1612在确定发送时间时在第一链路和第二链路上应用MAC层填充,PHY层填充,或MAC层填充和MAC层填充两者。

在一些实施方式中,在同步第一链路和第二链路上的发送和接收的开始时间和/或结束时间时,过程1700可涉及处理器1612执行特定操作。例如,过程1700可涉及处理器1612基于第一链路上的请求PPDU的TXVECTOR参数来计算响应帧的第一最小发送时间。另外,过程1700可涉及处理器1612基于第二链路上的另一请求PPDU的另一TXVECTOR参数来计算响应帧的第二最小发送时间。此外,过程1700可涉及处理器1612将第一最小发送时间或第二最小发送时间中的较高者确定为响应帧的发送时间。此外,过程1700可涉及处理器1612在确定传输时间时在第一链路和第二链路上应用MAC层填充,PHY层填充,或MAC层填充和PHY层填充两者。另外,过程1700可涉及处理器1612在第一链路和第二链路上的发送时间发送回应帧。

在一些实施方式中,在同步第一链路和第二链路上的发送和接收的开始时间和/或结束时间时,过程1700可涉及处理器1612在接收一个或多个请求帧后,在SIFS上将第一链路和第二链路上的一个或多个响应帧的发送的开始时间同步。

在一些实施方式中,在与装置1620进行通信时,过程1700涉及,在另一主信道的物理CS和虚拟CS都是空闲状态的情况下,处理器1612可执行对没有获得TXOP用于相应的EDCA的该另一主信道的早期存取。在该种情况下,物理CS可在PIFS期间被检查。

在一些实施方式中,在与装置1620通信时,过程1700还可包括处理器1612执行以下之一:(a)将多个MPDU中的每个MPDU独立地编码为多个频率段;或者(b)将多个MPDU联合编码为多个频率段。

在一些实施方式中,在同步中,过程1700可包括处理器1612以相同的PPDU格式、相同的GI和相同的LTF类型在第一链路和第二链路上发送一个或多个帧。

在一些实施方式中,在同步中,过程1700可包括处理器1612以相同的PPDU格式、相同的GI和相同的LTF类型在第一链路和第二链路上接收一个或多个回应帧。

在一些实施方式中,在同步第一链路和第二链路上的发送和接收的开始时间和/或结束时间时,过程1700可涉及处理器1612执行特定操作。例如,过程1700可涉及处理器1612对第一链路和第二链路上的一个或多个预HE调制字段维持相同的持续时间。另外,过程1700可涉及处理器1612对第一链路和第二链路上的一个或多个HE调制字段维持相同的持续时间。

在一些实施方式中,一个或多个预HE调制字段可包括以下一个或多个:L-STF,L-LTF,L-SIG字段,RL-SIG字段,HE-SIG-A字段和HE-SIG-B字段。在一些实施方式中,一个或多个HE调制字段可包括以下一个或多个:HE-STF,HE-LTF和数据字段。

在一些实施方式中,在对第一链路和第二链路上的一个或多个HE调制的字段维持相同的持续时间时,过程1700可涉及处理器1612在第一链路和第二链路上发送的HE SUPPDU或在第一链路和第二链路上发送的HE MU PPDU的一个或多个HE调制字段的A-MPDU中发送一个或多个EOF填充子帧。

在一些实施方式中,在对第一链路和第二链路上的一个或多个预HE调制的字段维持相同的持续时间时,过程1700可涉及处理器1612将一个或多个填充用户字段(PaddingUser field)添加到HE-SIG-B字段的用户专用字段(UserSpecific field)中。

图18示出了根据本发明的实施方式的示例过程1800。过程1800可代表实现上述各种提议的设计,概念,方案,系统和方法的一方面。更具体地,过程1800可代表与根据本发明的WLAN中的EHT同步和受约束的多链路传输有关的所提出的概念和方案的一方面。过程1800可包括一个或多个操作,动作或功能,如块1810和子块1812、1814和1816中的一个或多个所示。尽管被示为离散的块,但是过程1800的各个块可根据所需的实施方式被划分为其他块,组合成更少的块或删除。此外,过程1800的块/子块可以以图18中所示的顺序执行,或以其他顺序执行。此外,过程1800的一个或多个块/子块可以重复地或迭代地执行。过程1800可由装置1610和装置1620或其任何变型实施或在其中实现。仅出于说明性目的且不限制范围,过程1800在下面一种或多种IEEE 802.11标准的无线网络(例如WLAN)中,在装置1610作为通信实体110(例如,STA或AP)以及装置1620作为通信实体120(例如,对等STA或AP)的上下文中描述。过程1800可从块1810处开始。

在1810,过程1800可涉及,通过第一频带中的第一链路和不同于第一频带的第二频带中的第二链路,装置1610的处理器1612执行由1812、1814和1816表示的操作与装置1620通信。

在1812,过程1800可包括处理器1612在第一链路和第二链路中的每一个上执行独立的EDCA。处理1800可从1812进行到1814。

在1814,过程1800可包括处理器1612获得TXOP。处理1800可从1814进行到1816。

在1816,过程1800可包括处理器1612避免同时在第一链路和第二链路上进行发送和接收,以避免引起IDC干扰。

在一些实施方式中,在避免同时在第一链路和第二链路上进行发送和接收时,过程1800可涉及,通过应用MAC层填充,PHY层填充或PE,处理器1612将第一链路和第二链路上的发送的开始时间和/或结束时间同步于预定义的持续时间(例如aSIFSTime+aSignalExtension)。

在一些实施方式中,在同步第一链路和第二链路上的发送的开始时间和/或结束时间时,过程1800可涉及,处理器1612将第一链路上的第一传输的第一结束时间和第二链路上的第二传输的第二结束时间同步于缩短的持续时间内,该缩短的持续时间是通过从预定义的持续时间中减去定时误差余量来确定的。

在一些实施方式中,在进一步同步第一链路和第二链路上的传输的开始时间和/或结束时间时,过程1800还可包括处理器1612从装置1620接收与定时误差余量有关的信息,该信息指示该装置1620能够从请求帧的末尾在预定义的持续时间加上或减去定时误差余量内做出回应。

在一些实施方式中,在第一链路上的第一传输的第一结束时间与在第二链路上的第二传输的第二结束时间之间的差可小于SIFS。在该种情况下,第一装置的发送和接收之间可能没有重叠。可选地,当存在SIFS定时精度误差时,第一装置的发送和接收之间的重叠可以是允许的。

在一些实施方式中,装置1610可充当AP MLD,并且装置1620可充当非STR非APMLD。在该种情况下,在同步第一链路和第二链路上的发送和接收的开始时间和/或结束时间时,过程1800可涉及,处理器1612可对准携带一帧的DL PPDU的结束时间,该帧请求响应,并且该DL PPDU在第一链路和第二链路上被同时发送到装置1620,第一链路上的第一传输的第一结束时间与第二链路上的第二传输的第二结束时间之间的差小于特定持续时间(例如,SIFS)。

在一些实施方式中,在通信中,过程1800可进一步涉及,在另一主信道的物理CS和虚拟CS都是空闲状态的情况下,处理器1612可执行对没有获得TXOP用于相应的EDCA的该另一主信道的早期存取。在该种情况下,物理CS可在PIFS期间被检查。

在一些实施方式中,在通信中,过程1800还可涉及,处理器1612执行以下之一:(a)将多个MPDU中的每个MPDU独立地编码为多个频率段;或者(b)将多个MPDU联合编码为多个频率段。在该种情况下,在独立地编码多个MPDU中的每个MPDU时,过程1800可涉及,处理器1612在独立地编码多个MPDU中的每个MPDU时使用独立的DFT或独立的IDFT。

附加的说明

本文所描述的主题有时表示不同的组件,其包含在或者连接到其他不同的组件。可以理解的是,所描述的结构仅是示例,实际上可以由许多其他结构来实施,以实现相同的功能,从概念上讲,任何实现相同功能的组件的排列实际上是“相关联的”,以便实现所需功能。因此,不论结构或中间部件,为实现特定的功能而组合的任何两个组件被视为“相互关联”,以实现所需的功能。同样,任何两个相关联的组件被看作是相互“可操作连接”或“可操作耦接”,以实现特定功能。能相互关联的任何两个组件也被视为相互“可操作地耦接”,以实现特定功能。能相互关联的任何两个组件也被视为相互“可操作地耦合”以实现特定功能。可操作连接的具体例子包括但不限于物理可配对和/或物理上相互作用的组件,和/或无线可交互和/或无线上相互作用的组件,和/或逻辑上相互作用和/或逻辑上可交互的组件。

此外,关于基本上任何复数和/或单数术语的使用,本领域的技术人员可以根据上下文和/或应用从复数转换为单数和/或从单数到复数。为清楚起见,本发明明确阐述了不同的单数/复数排列。

此外,本领域的技术人员可以理解,通常,本发明所使用的术语特别是权利要求中的,如权利要求的主题,通常用作“开放”术语,例如,“包括”应解释为“包括但不限于”,“有”应理解为“至少有”“包括”应解释为“包括但不限于”等。本领域的技术人员可以进一步理解,若计划介绍特定数量的权利要求内容,将在权利要求内明确表示,并且,在没有这类内容时将不显示。例如,为帮助理解,下面权利要求可包含短语“至少一个”和“一个或复数个”,以介绍权利要求的内容。然而,这些短语的使用不应理解为暗示使用“一”或“一个”介绍权利要求内容,而限制了任何特定神专利范围。甚至当相同的权利要求包括介绍性短语“一个或复数个”或“至少有一个”,不定冠词,例如“一”或“一个”,则应被解释为表示至少一个或者更多,对于用于介绍权利要求的明确描述的使用而言,同样成立。此外,即使明确引用特定数量的介绍性内容,本领域的技术人员可以认识到,这样的内容应被解释为表示所引用的数量,例如,没有其他修改的“两个引用”,意味着至少两个引用,或两个或两个以上的引用。此外,在使用类似于“A、B和C中的至少一个”的表述的情况下,通常如此表述是为了本领域的技术人员可以理解该表述,例如,“系统包括A、B和C中的至少一个”将包括但不限于单独具有A的系统,单独具有B的系统,单独具有C的系统,具有A和B的系统,具有A和C的系统,具有B和C的系统,和/或具有A、B和C的系统,等。本领域的技术人员进一步可理解,无论在说明书中,权利要求中或者附图中,由两个或两个以上的替代术语所表现的任何分隔的单词和/或短语应理解为,包括这些术语中的一个,其中一个,或者这两个术语的可能性。例如,“A或B”应理解为,“A”,或者“B”,或者“A和B”的可能性。

从前述可知,出于说明目的,本发明已描述了各种实施方案,并且在不偏离本发明的范围和精神的情况下,可以进行各种变形。因此,此处所公开的各种实施方式不用于限制,真实的范围和申请由权利要求表示。

- WLAN中增强的高吞吐量同步和受约束的多链路传输

- 用于高吞吐量MIMO WLAN系统的天线阵列配置