高电子迁移率晶体管及其制作方法

文献发布时间:2023-06-19 09:57:26

技术领域

本发明涉及一种高电子迁移率晶体管的结构及其制作方法,特别是涉及一种源极电极和漏极电极形状不同的高电子迁移率晶体管的结构及其制作方法。

背景技术

III-V族半导体化合物由于其半导体特性而可应用于形成许多种类的集成电路装置,例如高功率场效晶体管、高频晶体管或高电子迁移率晶体管(high electron mobilitytransistor,HEMT)。在高电子迁移率晶体管中,两种不同能带隙(band-gap)的半导体材料结合而于结(junction)形成异质结(heterojunction)而为载流子提供通道。近年来,氮化镓系列的材料由于拥有较宽能隙与饱和速率高的特点而适合应用于高功率与高频率产品。氮化镓系列的高电子迁移率晶体管由材料本身的压电效应产生二维电子气(two-dimensional electron gas,2DEG),相较于传统晶体管,高电子迁移率晶体管的电子速度及密度均较高,故可用以增加切换速度。

然而随着电子产品升级,因此需增加高电子迁移率晶体管的操作效能。

发明内容

有鉴于此,本发明提供一种高电子迁移率晶体管,通过降低导通电阻(on-resistance)来提升高电子迁移率晶体管的操作效能。

根据本发明的一优选实施例,一种高电子迁移率晶体管包含一第一III-V族化合物层,一第二III-V族化合物层设置于第一III-V族化合物层上,第二III-V族化合物层的组成与第一III-V族化合物层不同,其中第二III-V族化合物层包含一浅凹槽、一第一深凹槽和一第二深凹槽,第一深凹槽和第二深凹槽分别位于浅凹槽的两侧,一源极电极填入第一深凹槽并且接触第一III-V族化合物层的一上表面,一漏极电极填入第二深凹槽并且接触第一III-V族化合物层的上表面,其中源极电极和漏极电极的形状相异,一栅极电极设置浅凹槽的正上方。

根据本发明的另一优选实施例,一种高电子迁移率晶体管的制作方法包含提供一第一III-V族化合物层,然后形成一第二III-V族化合物层于第一III-V族化合物层上,第二III-V族化合物层的组成与第一III-V族化合物层不同,之后形成一浅凹槽、一第一深凹槽和一第二深凹槽于第二III-V族化合物层内,第一深凹槽和第二深凹槽分别位于浅凹槽的两侧,接续形成一源极主体和一漏极电极,其中源极主体位于第一深凹槽中,漏极电极位于第二深凹槽中,然后形成一导电层覆盖源极主体、浅凹槽、第二III-V族化合物层和漏极电极,再移除覆盖浅凹槽、漏极电极以及浅凹槽和该漏极电极之间的第二III-V族化合物层的导电层,保留覆盖源极主体以及浅凹槽和源极主体之间的导电层以作为一源极延伸层,其中源极主体和源极延伸层组成一源极电极,最后形成一栅极电极位于浅凹槽的正上方。

为让本发明的上述目的、特征及优点能更明显易懂,下文特举优选实施方式,并配合所附的附图,作详细说明如下。然而如下的优选实施方式与附图仅供参考与说明用,并非用来对本发明加以限制者。

附图说明

图1至图7为本发明的第一优选实施例所绘示的一种高电子迁移率晶体管的制作方法的示意图;

图8为本发明的第二优选实施例所绘示的一种高电子迁移率晶体管的制作方法的示意图;

图9为本发明的另一优选实施例所绘示的高电子迁移率晶体管的变化型的示意图;

图10为本发明的另一优选实施例所绘示的高电子迁移率晶体管的变化型的示意图。

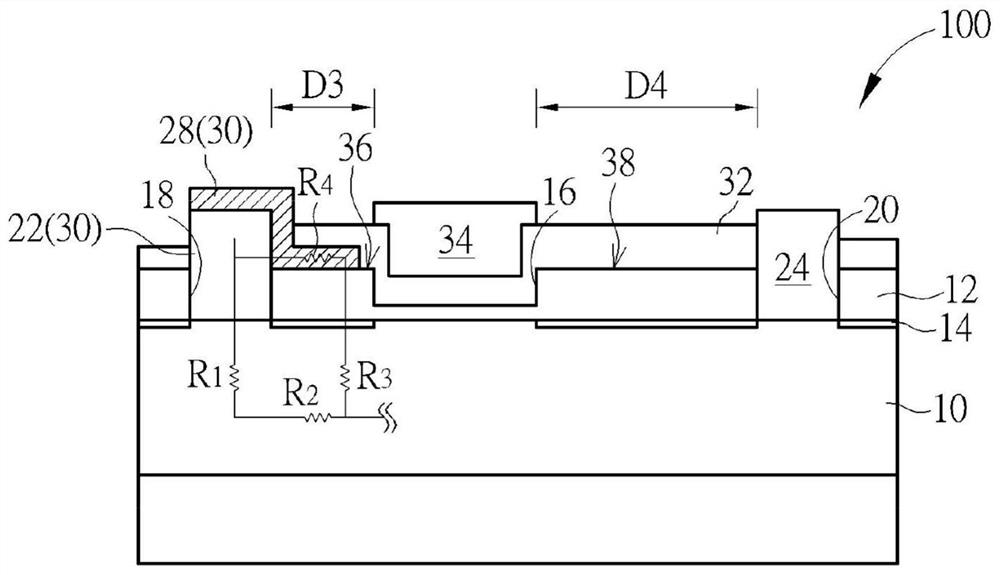

主要元件符号说明

10 第一III-V族化合物层 12 第二III-V族化合物层

14 二维电子气 16 浅凹槽

18 第一深凹槽 20 第二深凹槽

22 源极主体 24 漏极电极

26 导电层 28 源极延伸层

30 源极电极 32 保护层

34 栅极电极 36 第一上表面

38 第二上表面 100 高电子迁移率晶体管

128 源极延伸层 200 高电子迁移率晶体管

300 高电子迁移率晶体管 D1 距离

D2 距离 D3 距离

D4 距离 R1 等效电阻

R2 等效电阻 R3 等效电阻

R4 等效电阻

具体实施方式

图1至图7为根据本发明的第一优选实施例所绘示的一种高电子迁移率晶体管的制作方法。

如图1所示,首先提供一基底,一第一III-V族化合物层10形成于基底上,然后形成一第二III-V族化合物层12覆盖并接触第一III-V族化合物层10,第二III-V族化合物层12的组成与第一III-V族化合物层10不同。第一III-V族化合物层10可以为氮化镓(galliumnitride,GaN)、氮化铟镓(indium gallium nitride,In

如图2所示,先形成一浅凹槽16于第二III-V族化合物层12中,之后再形成一第一深凹槽18和一第二深凹槽20分别位于浅凹槽16的两侧,形成浅凹槽16、第一深凹槽18和第二深凹槽20的方式可以采用光刻蚀刻制作工艺。浅凹槽16不贯穿第二III-V族化合物层12,第一深凹槽18和第二深凹槽20都贯穿第二III-V族化合物层12,也就是说,浅凹槽16的深度比第一深凹槽18和第二深凹槽20的深度小,此外在第一深凹槽18和第二深凹槽20形成之后,第二III-V族化合物层12会从第一深凹槽18和第二深凹槽20曝露出来。在形成浅凹槽16、第一深凹槽18和第二深凹槽20之后,在浅凹槽16、第一深凹槽18和第二深凹槽20正下方的二维电子气14会消失。另外,根据本发明的优选实施例,第一深凹槽18和浅凹槽16之间的距离D1小于第二深凹槽20和浅凹槽16之间的距离D2。

如图3所示,形成一源极主体22和一漏极电极24,源极主体22位于第一深凹槽18中,漏极电极24位于第二深凹槽20中,源极主体22和漏极电极24的形成方式包含形成一掩模层(图未示)覆盖第二III-V族化合物层12,然后在掩模层上定义出漏极电极24和源极主体22的位置以露出第一深凹槽18和第二深凹槽20,之后溅镀金属材料在第一深凹槽18和第二深凹槽20中作为漏极电极24和源极主体22。源极主体22和漏极电极24可以各自包含钛、铝、镍、金或是其它的导电材料。在源极主体22和漏极电极24完成之后,接续形成一导电层26顺应的覆盖源极主体22、浅凹槽16、第二III-V族化合物层12和漏极电极24。导电层26包含氮化钛、金、铂、钛、氧化铟锡(Indium Tin Oxide,ITO)、掺铝氧化锌(Aluminum-dopedZinc Oxide,AZO)或是其它的导电材料。

如图4所示,移除覆盖浅凹槽16、漏极电极24以及浅凹槽16和漏极电极24之间的第二III-V族化合物层12等位置的导电层26,只保留覆盖源极主体22上表面、源极主体22部分的一侧表面、以及覆盖浅凹槽16和源极主体22之间的导电层26以作为一源极延伸层28,其中源极主体22和源极延伸层28组成一源极电极30。值得注意的是:源极电极30的形状和漏极电极24的形状相异。根据本发明的优选实施例,源极主体22的材料和源极延伸层28的材料不同。根据本发明的其它优选实施例,源极主体22的材料和源极延伸层28的可以相同。

图8为根据本发明的第二优选实施例所绘示的一种高电子迁移率晶体管的制作方法,其中相同功能的元件将使用和第一优选实施例相同的标号。根据本发明的第二优选实施例,如图8所示,在移除导电层26时,导电层26也可以只保留在浅凹槽16和源极主体22之间的导电层26作为一源极延伸层128,其在源极主体22和栅极电极34之间的第二III-V族化合物层12上(栅极电极34的位置请参阅图7),其它位置的导电层26都被移除。

根据本发明的另一优选实施例,源极延伸层可以和源极主体一体成型,也就是说图3步骤中在掩模层上定义源极主体22时,可以同时定义源极延伸层28的位置,之后在溅镀金属材料时一同形成源极延伸层28。如此就可以省略形成导电层的步骤。后续制作工艺将以图4中的源极延伸层的形状为例接续说明。

如图5所示,选择性地形成一保护层32顺应地覆盖并接触第二III-V族化合物层12、源极延伸层28、漏极电极24并且填入浅凹槽16,保护层32可以为氮化硅或氮化铝,或其他可为保护层的材料。如图6所示,移除部分的保护层32,只保留在第一深凹槽18和第二深凹槽20之间的保护层32,也就是说剩余的保护层32只接触部分的源极延伸层28、填入浅凹槽16并且接触位于浅凹槽16和第二深凹槽20之间的第二III-V族化合物层12。如图7所示,形成一栅极电极34位于浅凹槽16的正上方。此时本发明的高电子迁移率晶体管100已经完成,高电子迁移率晶体管100为一常闭型(normally-off)晶体管。

图7为根据本发明的一优选实施例所绘示的高电子迁移率晶体管。如图7所示,一种高电子迁移率晶体管100,包含一第一III-V族化合物层10,一第二III-V族化合物层12设置于第一III-V族化合物层10上,第二III-V族化合物层12的组成与该第一III-V族化合物层10不同,第一III-V族化合物层10可以为氮化镓或/及氮化铟镓等材料来形成,第二III-V族化合物层12可利用氮化铝镓、氮化铝铟、氮化铝铟镓或/及氮化铝等材料来形成,但并不以此为限。根据本发明的优选实施例,第一III-V族化合物层10为氮化镓,第二III-V族化合物层12为氮化铝镓。

一浅凹槽16、一第一深凹槽18和一第二深凹槽20设置于第二III-V族化合物层12中,第一深凹槽18和第二深凹槽20分别位于浅凹槽16的两侧,请同时参阅图2,第一深凹槽18和浅凹槽16之间的距离D1小于第二深凹槽18和浅凹槽16之间的距离D2,一源极电极30填入第一深凹槽18并且接触第一III-V族化合物层10的上表面,一漏极电极24填入第二深凹槽20并且接触第一III-V族化合物层10的上表面,其中源极电极30和漏极电极24的形状相异,一栅极电极34设置在浅凹槽16的正上方。另外一保护层32可选择性地覆盖并接触第二III-V族化合物层12和部分的源极电极30并且填入浅凹槽16,也就是说保护层32会分隔栅极电极34和源极电极30并且分隔栅极电极和34漏极电极24。保护层32包含氮化硅或氮化铝。

此外,在浅凹槽16和第一深凹槽18之间的第二III-V族化合物层12具有一第一上表面36,在浅凹槽16和第二深凹槽20之间的第二III-V族化合物层12具有一第二上表面38,值得注意的是:源极电极30接触第一上表面36,漏极电极24不接触第二上表面38,此外源极电极30包含一源极主体22和一源极延伸层28,源极主体22填入第一深凹槽18、接触第一III-V族化合物层10的上表面、并且不接触第二III-V族化合物层12的第一上表面36,而源极延伸层28覆盖并接触源极主体22的上表面、源极主体22的一侧壁以及第二III-V族化合物层12的第一上表面36。

此外,根据本发明的优选实施例,源极主体22和源极延伸层28的材料不同。源极延伸层28包含氮化钛、金、铂、钛、氧化铟锡或掺铝氧化锌,源极主体22和漏极电极24各自包含钛、铝、镍、铂或金。

本发明在源极电极30具有一源极延伸层28覆盖在栅极电极34和源极主体22之间的第二III-V族化合物层12,如此可以降低高电子迁移率晶体管100的导通电阻,如图7所示,当高电子迁移率晶体管100的电流导通后,源极电极30和第一III-V族化合物层10产生了一个等效电阻R1,第一III-V族化合物层10往漏极电极24的方向产生了一个等效电阻R2,源极延伸层28、第一III-V族化合物层10和第二III-V族化合物层12产生了一个等效电阻R3,源极延伸层28产生了一个等效电阻R4。等效电阻R4使得等效电阻R1、等效电阻R2和等效电阻R3从原本的三者串连变成串连的等效电阻R1和等效电阻R2和串连的等效电阻R3和等效电阻R4并联,因此总电阻会比原本的等效电阻R1、等效电阻R2和等效电阻R3三者串连小。如此就可以降低高电子迁移率晶体管100的导通电阻。

此外若是漏极电极24延伸至第二上表面38就会造成高电子迁移率晶体管100的击穿电压(break down voltage)下降,因此本发明中的漏极电极24不会延伸至第二上表面38。由于高电子迁移率晶体管100通常需要承受高电压,所以在本实施例中特意将栅极电极34和漏极电极24的距离D4设置得比栅极电极34和源极主体22的距离D3大,为了达成此目的,请参阅图2,第一深凹槽18和浅凹槽16之间的距离D1需小于第二深凹槽18和浅凹槽16之间的距离D2。

图9所绘示的是高电子迁移率晶体管的变化型,其中相同功能的元件将使用和第一优选实施例相同的标号,根据不同的制作工艺,可以先制作源极延伸层28,再形成源极主体22和漏极电极24,如此一来就会如图9所示的高电子迁移率晶体管200,其源极延伸层28接触第一III-V族化合物层10,并且源极主体22形成在源极延伸层28之上。

图10所绘示的是高电子迁移率晶体管的变化型,其中相同功能的元件将使用和第一优选实施例相同的标号,图10中的高电子迁移率晶体管300和图7的高电子迁移率晶体管100的差别在于:高电子迁移率晶体管300在图3步骤移除部分金属层之后,利用湿蚀刻将源极主体22未接触第一深凹槽18的二个转角圆弧化(rounded),同时漏极电极24未接触第二深凹槽20的二个转角也被圆弧化,之后再形成源极延伸层28顺应地覆盖源极主体22,由于源极主体22的转角被圆弧化,所以源极延伸层28对应转角的位置也会呈现圆弧化的轮廓。

本发明的高电子迁移率晶体管具有不同形状的源极电极和漏极电极,因为本发明特别将源极电极向栅极电极的方向延伸,使得源极电极会覆盖源极电极和栅极电极之间的III-V族化合物层。如此可以降低高电子迁移率晶体管的电通电阻。

以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

- ScAlN/GaN高电子迁移率晶体管及其制作方法

- 高电子迁移率晶体管及其制作方法