数据处理系统、中央运算处理装置和数据处理方法

文献发布时间:2023-06-19 10:36:57

技术领域

本发明涉及数据处理系统、中央运算处理装置和数据处理方法。

本申请针对在2018年10月19日向日本申请的日本特愿2018-197945号要求优先权,将其内容援引于此。

背景技术

近年,在网络的领域中,虚拟化受到注目。通过虚拟化,能够在逻辑上利用构成网络的装置而不管实际的物理硬件结构如何。讨论了为虚拟化而通过通用硬件来构成以往在光接入系统中通过专用的硬件所制作的OLT(Optical Line Terminal,光线路终端)等装置并用软件来安装功能的结构。通过用软件实现功能,装置的功能变得可替换,另外,谋求装置的共同化或资源共享化。因此,能够期待CAPEX(Capital expenditure,资本支出)的削减。此外,考虑通过软件来使功能的更新或设定变更变得容易由此导致CAPEX削减。

在此,作为用于使接入系统的软件区域扩大到包括纠错功能的物理层处理的讨论,示出了利用接入系统具有的GPU(Graphics Processing Unit,图形处理单元)的安装技术。物理层处理的运算量很大,因此,以往,安装于专用芯片的ASIC(Application SpecificIntegrated Circuit,专用集成电路)。一般,通用硬件难以高速处理。因此,在物理层处理中仅利用CPU(central processing unit,中央处理单元)的情况下,吞吐量的性能达成是困难的。此外,作为通用处理器的动向,CPU的性能也达到了顶点。于是,通过与具有多核、可实现以高水平的并行化的GPU、FPGA(field-programmable gate array,现场可编程门阵列)等加速器进行组合,从而进行了性能提高。像这样,通过使用GPU等加速器来谋求性能达成的实现。

10G-EPON(10Gigabit Ethernet(注册商标) Passive Optical Network,无源光网络)(例如,参照非专利文献2)系统中的站侧装置即OLT(Optical Line Terminal)通过图4所示的功能来实现编码处理。也就是说,物理层由PMA(physical medium attachment;物理介质连接部)、PMD(physical medium dependent;物理介质依赖部)、PCS(physicalcoding sublayer;物理编码子层)、RS(reconciliation sublayer;调和子层)构成。进行编码的功能相当于PCS。PCS内的功能包括加扰处理、报头添加、0添加/去除、FEC(forwarderror correction:前向纠错)编码等。

在此,讨论了使PCS的功能软件化。关于PCS中的编码,可并行处理的功能与不可并行处理的功能混在一起。GPU能够针对可并行处理的功能实现大幅高速化。可是,针对不可并行处理的功能,对于串行处理有效的CPU处理比利用GPU的处理更加能够高速化。因此,需要可实现CPU和GPU的协调处理的架构。进而,在通信处理中利用CPU和GPU时,需要连续地将信号转送到CPU或GPU的技术。

从上述两点出发,需要能够通过CPU和GPU协调地处理的且能够连续地流送信号的架构、以及这样的架构的控制方法。另外,需要将信号连续地转送到外部且经由CPU、GPU的方法。

在图像处理等的高速化中提出了利用CPU和GPU的协调处理系统。在这样的协调处理系统中,采取重复从CPU向GPU的存储器的转送和对转送到GPU的数据的处理的结构。

图5示出了在OLT内将通过CPU进行了计算的信号直接转送到外部的方法(例如,参照非专利文献1)。该图所示的OLT例如使用通用服务器来实现。在该图所示的方法中,在CPU中确保了多个发送用缓冲器。每当转送时,CPU依次变更对发送到IF板的主信号进行存储的缓冲器的地址来进行主信号的转送。仅CPU进行对主信号的运算。

图6示出在OLT内将外部信号连续地直接转送到GPU的方法(例如,参照非专利文献2)。该图所示的OLT例如使用通用服务器来实现。在该图所示的方法中,在GPU中确保了多个接收用缓冲器。每当转送时,OLT依次变更对GPU接收的信号进行存储的缓冲器的地址来进行转送。仅由GPU进行对主信号的运算。

现有技术文献

非专利文献

非专利文献1:Takahiro Suzuki, Sang-Yuep Kim, Jun-ichi Kani, Ken-IchiSuzuki, Akihiro Otaka, "Real-time Demonstration of PHY Processing on CPU forProgrammable Optical Access Systems", 2016 IEEE Global CommunicationsConference (GLOBECOM 2016), 2016年;

非专利文献2:Takahiro Suzuki, Sang-Yuep Kim, Jun-ichi Kani, ToshihiroHanawa, Ken-Ichi Suzuki, Akihiro Otaka, "Demonstration of 10-Gbps Real-TimeReed-Solomon Decoding Using GPU Direct Transfer and Kernel Scheduling forFlexible Access Systems", Journal of Lightwave Technology, 2018年5月, Vol.36,No.10, p.1875-1881。

发明内容

发明要解决的课题

然而,在上述的图5所示的技术中,仅CPU进行对主信号的运算,在图6所示的技术中,仅GPU进行对主信号的运算。像这样,这些并不是加速器与中央运算处理装置(CPU)协作地进行对主信号的运算的技术。

鉴于上述情况,本发明的目的在于,提供能够使加速器与中央运算处理装置协调地进行数据处理的数据处理系统、中央运算处理装置和数据处理方法。

用于解决课题的方案

本发明的一个方式是一种数据处理系统,其中,具备:接口电路,与外部装置通信;加速器,进行第一数据处理;以及中央运算处理装置,控制所述加速器和所述接口电路,所述中央运算处理装置具备:数据处理执行部,进行第二数据处理;外部转送控制部,进行控制为使得从所述接口电路向所述加速器或该中央运算处理装置转送从所述外部装置接收的数据的处理、以及控制为使得从所述加速器或该中央运算处理装置向所述接口电路转送向所述外部装置发送的数据的处理中的至少任一个;数据处理控制部,控制为使得针对从所述外部装置接收的所述数据或向所述外部装置发送的所述数据来执行利用所述加速器的所述第一数据处理和利用所述数据处理执行部的所述第二数据处理;以及处理结果复制部,进行向所述中央运算处理装置输出所述第一数据处理的处理结果即第一处理结果来将所述第一处理结果作为所述第二数据处理的处理对象的控制、以及向所述加速器输出所述第二数据处理的处理结果即第二处理结果来将所述第二处理结果作为所述第一数据处理的处理对象的控制中的至少一个。

本发明的一个方式是一种中央运算处理装置,其中,具备:存储部,存储从外部装置接收的数据或向所述外部装置发送的数据;数据处理执行部,使用所述存储部中存储的所述数据来进行数据处理,将处理结果存储在所述存储部中;外部转送控制部,进行控制为使得从接口电路向加速器或所述存储部转送从所述外部装置接收的数据的处理、以及控制为使得从所述加速器或所述存储部向所述接口电路转送向所述外部装置发送的数据的处理中的至少任一个;数据处理控制部,控制为使得针对从所述外部装置接收的所述数据或向所述外部装置发送的所述数据来执行利用所述加速器的数据处理和利用所述数据处理执行部的所述数据处理;以及处理结果复制部,进行向所述存储部转送利用所述加速器的所述数据处理的处理结果即第一处理结果来将所述第一处理结果作为所述数据处理执行部中的所述数据处理的处理对象的控制、以及从所述存储部向所述加速器转送利用所述数据处理执行部的所述数据处理的处理结果即第二处理结果来将所述第二处理结果作为利用所述加速器的所述数据处理的处理对象的控制中的至少一个。

本发明的一个方式是数据处理系统执行的数据处理方法,其中,具有:第一数据处理步骤,加速器进行第一数据处理;第二数据处理步骤,中央运算处理装置进行第二数据处理;外部转送步骤,中央运算处理装置进行控制为使得从接口电路向所述加速器或该中央运算处理装置转送从外部装置接收的数据的处理、以及控制为使得从所述加速器或该中央运算处理装置向所述接口电路转送向所述外部装置发送的数据的处理中的至少任一个;数据处理控制步骤,中央运算处理装置控制为使得针对从所述外部装置接收的所述数据或向所述外部装置发送的所述数据来执行利用所述第一数据处理步骤的所述第一数据处理和利用所述第二数据处理步骤的所述第二数据处理;以及处理结果复制步骤,中央运算处理装置进行向所述中央运算处理装置输出所述第一数据处理的处理结果即第一处理结果来将所述第一处理结果作为所述第二数据处理的处理对象的控制、以及向所述加速器输出所述第二数据处理的处理结果即第二处理结果来将所述第二处理结果作为所述第一数据处理的处理对象的控制中的至少一个。

发明效果

利用本发明,能够使加速器与中央运算处理装置协调地进行数据处理。

附图说明

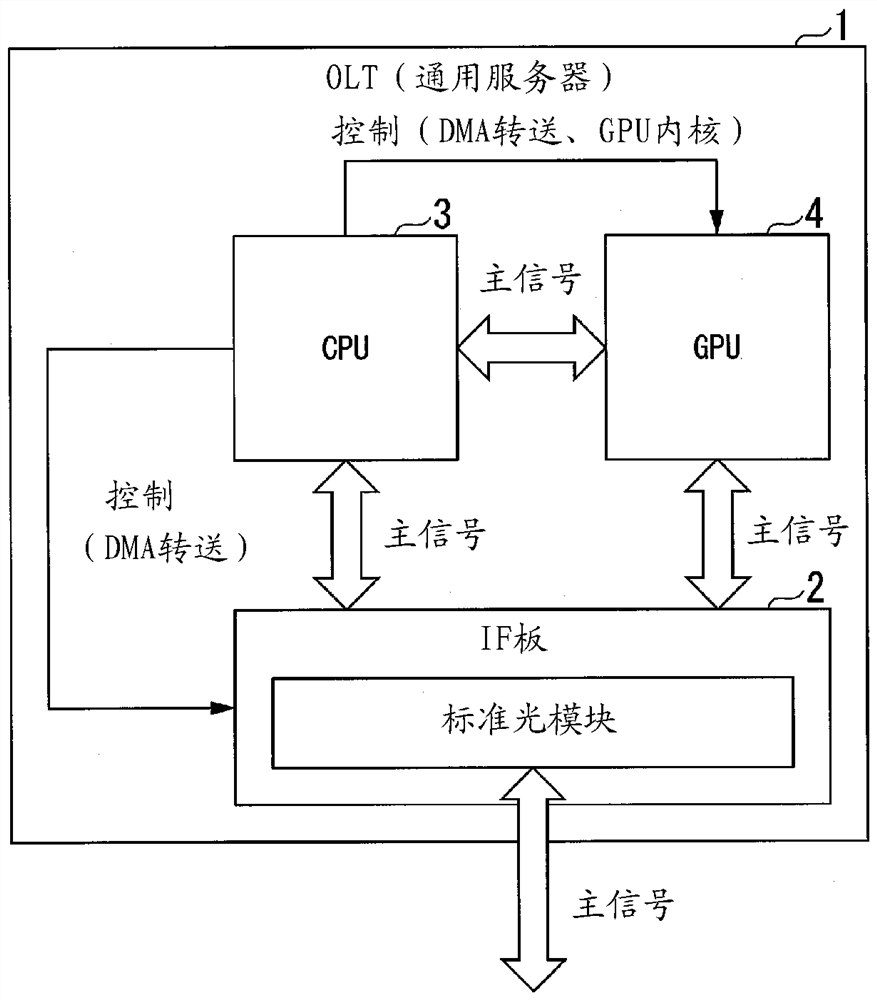

图1是示出根据本发明的第一实施方式的OLT的结构的图。

图2是示出根据该实施方式的OLT的处理的流程图。

图3是示出根据第二实施方式的OLT的下行信号的处理相关的结构的图。

图4是示出现有技术的OLT中的编码处理相关的功能的图。

图5是示出现有技术的OLT中的信号转送的图。

图6是示出现有技术的OLT中的信号转送的图。

具体实施方式

以下,一边参照附图一边详细地说明本发明的实施方式。

在本实施方式的数据处理系统中,IF(接口)板以周期性的定时启动CPU(centralprocessing unit;中央运算处理装置)的中断处理程序(interrupt handler)。中断处理程序指定从CPU或IF板向GPU转送数据时的GPU上的转送目的地存储器、和从GPU向IF板或CPU转送数据时的GPU上的转送源存储器,进而,进行CPU的函数启动、GPU的内核(kernel)启动、CPU与GPU间的存储器复制、GPU与IF板或IF板间的DMA(Direct Memory Access,直接存储器访问)转送的命令。

根据本实施方式的数据处理系统,能够在CPU-GPU间进行协调的处理并且还能够进行向外部的连续信号转送。因此,通过将本实施方式的数据处理系统应用于通信装置,从而能够实现包括可并行处理的功能和不可并行处理的功能这两方的通信处理的高速化,进而能够实现功能整体的软件化。以下,以数据处理系统是接入系统的终端站装置的情况为例,说明详细的实施方式。

[第一实施方式]

图1是示出根据本实施方式的OLT1的结构的图。OLT1是数据处理系统的一例。OLT1例如使用通用服务器来实现。通过该图所示的结构,OLT1进行CPU-GPU协调运算。OLT1具备IF板2、CPU3、以及GPU4。

IF板2例如是通过FPGA(field-programmable gate array)、专用板等实现的接口电路。IF板2进行外部装置与处理器之间的信号的输入输出。例如,外部装置是ONU(Opticalnetwork unit,光网络单元)和上位装置,处理器是CPU3和GPU4。IF板2周期性地启动CPU3的中断处理程序。IF板2依照来自CPU3的中断处理程序的控制来进行DMA转送。即,IF板2将从外部装置接收的信号中包括的主信号转送到CPU3和GPU4。此外,IF板2从CPU3保持的存储器或GPU4保持的存储器取得发给外部装置的主信号,将所取得的主信号输出到外部装置。IF板2具有进行电信号与光信号的变换的标准光模块。标准光模块将经由光传送路从ONU接收的光信号变换为电信号。此外,标准光模块将发给ONU的电信号变换为光信号,将光信号输出到光传送路。

CPU3通过来自IF板2的中断而启动中断处理程序。中断处理程序针对IF板2执行用于进行CPU3和GPU4与IF板2之间的DMA转送的控制。此外,中断处理程序针对GPU4执行用于进行CPU3与GPU4之间的DMA转送的控制、以及GPU4的内核的启动的控制。由此,主信号不仅在IF板2和处理器之间,还在CPU3-GPU4之间进行收发。此外,CPU3针对IF板2接收到的或从IF板2发送的主信号进行PCS(physical coding sublayer)中包括的数据处理之中的串行处理。

GPU4是加速器的一例。GPU4依照来自CPU3的控制而执行内核。GPU4通过内核针对从IF板2或CPU3转送的主信号进行PCS(physical coding sublayer)中包括的数据处理之中的可并行处理的数据处理。

图2是示出OLT1中的处理的流程图。使用该图来说明OLT1的IF板2、CPU3和GPU4的功能。首先,IF板2在完成了从外部的信号输入或向外部的信号输出的准备时,向CPU3发送中断信号(步骤S11)。

CPU3当从IF板2接收到中断信号时,启动中断处理程序。中断处理程序首先通过进行存储器控制来决定对CPU3的函数作为运算对象的数据进行存储的CPU3的存储器区域、对GPU4的内核作为运算对象的数据进行存储的GPU4的存储器区域(步骤S12)。再有,存储输入数据的存储器区域和存储输出数据的存储器区域可以是不同的。接着,中断处理程序向IF板2通知CPU3的存储器地址和GPU4的存储器地址中的一者或两者,进而向IF板2指示外部转送(步骤S13)。IF板2向所通知的地址的CPU3的存储器和GPU4的存储器中的一者或两者转送主信号的数据(步骤S14)。

在接下来的中断周期内,IF板2向CPU3发送中断信号(步骤S15)。CPU3当从IF板2接收到中断信号时,启动中断处理程序。中断处理程序针对在步骤S12中决定的存储器地址的存储器区域进行函数启动或内核启动(步骤S16)。再有,中断处理程序在步骤S14中向CPU3的存储器转送了数据的情况下进行函数启动,在向GPU4的存储器转送了数据的情况下进行内核启动。此外,在启动GPU4的内核的情况下,中断处理程序向GPU4通知在步骤S12中决定的GPU4的存储器地址、由GPU4并行执行的处理等。

在步骤S16中进行了函数启动的情况下,CPU3针对存储器地址所示出的CPU3的存储器区域中存储的主信号进行函数运算,将该函数运算的运算结果写入到CPU3的存储器区域中。另一方面,在步骤S16中进行了内核启动的情况下,GPU4启动内核,针对GPU4的存储器区域中存储的主信号并行地执行从CPU3的中断处理程序所指示的处理。GPU4将这些并行执行的处理的执行结果写入到GPU4的存储器区域中(步骤S17)。

接着,中断处理程序指示CPU3-GPU4之间的存储器复制(步骤S18)。CPU3和GPU4依照中断处理程序的指示来进行DMA转送(步骤S19)。即,当检测到结束了在步骤S16中启动的函数运算时,中断处理程序将步骤S17中的函数运算的执行结果被存储的CPU3的存储器区域的内容复制到在步骤S12中决定的GPU4的存储器区域。或者,当检测到结束了在步骤S16中启动的GPU4的并行处理时,中断处理程序将步骤S17中的GPU4的并行处理的执行结果被存储的GPU4的存储器区域的内容复制到在步骤S12中决定的存储器地址所示出的CPU3的存储器区域。再有,中断处理程序既可以通过从GPU4接受通知来检测GPU4中的并行处理的结束,也可以通过检测在并行处理的结束时写入到GPU4的存储器的结束标志来检测GPU4中的并行处理的结束。

之后,CPU3和GPU4根据需要,重复步骤S16~步骤S19的处理(步骤S20~步骤S23)。即,中断处理程序任意地重复函数启动和内核启动,重复CPU3和GPU4各自中的运算,在CPU3和GPU4之间复制运算结果的数据。

最后,当OLT1进行与步骤S16和步骤S17同样的处理时(步骤S24和步骤S25),中断处理程序通过将DMA启动的命令送到IF板2来开始IF板2的DMA(步骤S26)。此时,中断处理程序将步骤S25中的函数运算的执行结果被存储的CPU3的存储器地址、或步骤S25中的并行处理的执行结果被存储的GPU4的存储器地址作为数据转送源,通知给IF板2。IF板2从数据转送源复制数据(步骤S27)。IF板2将从CPU3或GPU4转送的数据发送到ONU或上位装置。该数据是主信号。连续地重复IF板2中的中断(步骤S28)。

如上所述,根据本实施方式,能够通过将依照CPU3的存储器复制命令的CPU3-GPU4之间的DMA的执行加入到信号转送的流中,来在CPU3-GPU4之间进行DMA转送(主信号)。此外,CPU3在指示外部转送时,能够选择是CPU3-IF板2之间的转送还是GPU4-IF板2之间的转送、以及是向IF板2的转送还是来自IF板2的转送。因此,CPU3和GPU4均能够进行与IF板2之间的双方向的DMA转送(主信号的转送)。进而,通过重复存储器复制和函数/内核启动任意次数,能够以任意的顺序将任意的处理分配给CPU、GPU。

[第二实施方式]

在本实施方式中,以从处理器向IF板的方向(下行)的信号处理为例,说明OLT1的详细的结构例。

图3是示出OLT1中的下行的信号处理相关的结构的图。10G-EPON、NG-PON2、XGS-PON等PON规范的OLT采取与该图同样的结构。

CPU3具有主存储器31、中断处理程序32、以及函数执行部33。主存储器31是存储从外部装置接收的主信号或向外部装置发送的主信号的存储部的一例。主存储器31具有输入输出用的存储器区域h_output。中断处理程序32具备存储器控制部321、函数启动部322、存储器复制部323、内核启动部324、以及外部转送控制部325。存储器控制部321进行对函数作为运算对象的CPU3的存储器地址、以及由GPU4的内核所启动的并行处理作为运算对象的GPU4的存储器地址进行决定的存储器控制。函数启动部322向函数执行部33指示函数的执行。存储器复制部323进行IF板2或GPU4与主存储器31之间的数据的复制。内核启动部324向GPU4指示内核启动。外部转送控制部325指示IF板2与CPU3或GPU4之间的DMA转送。

GPU4具备全局存储器41、以及内核执行部42。全局存储器41具有输入用的存储器区域d_input、以及输出用的存储器区域d_output。内核执行部42启动内核来执行并行处理。

IF板2具备DMA执行部21、以及外部转送部22。DMA执行部21接受来自CPU3的指示,从CPU3或GPU4复制主信号的数据。外部转送部22将DMA执行部21复制的主信号变换为光信号,发送到ONU。

接着,说明OLT1中的下行信号的处理。

在本实施方式中,主信号的输入被保持在CPU3的主存储器31内的存储器区域h_output中。存储器区域h_output具有N个缓冲器。利用index的值来特别指定是这N个缓冲器中的哪个。每当主信号的输入时,CPU3一边使示出存储器区域h_output的缓冲器的地址的index发生变化一边在CPU3上执行作为串行功能的加扰。

具体而言,当IF板2启动CPU3的中断处理程序32时,存储器控制部321决定在主存储器31中使用的存储器区域h_output的地址、以及在全局存储器41中使用的存储器区域d_input和存储器区域d_output的地址。外部转送控制部325向IF板2通知示出存储器区域h_output的地址的index,进而向IF板2指示以使得转送主信号。IF板2的外部转送部22向index所示出的存储器区域h_output的缓冲器转送主信号。

在向主存储器31转送主信号的接下来的周期内,CPU启动中断处理程序32时,函数启动部322向函数执行部33通知存储器区域h_output的index,进而,向函数执行部33指示加扰的启动。加扰进行替换数据列的比特位置的处理。函数执行部33将从index所示出的存储器区域h_output的缓冲器中读出的主信号用作输入数据,执行具有加扰功能的函数,将函数的执行结果写入到该缓冲器中。

全局存储器41的存储器区域d_input和存储器区域d_output也分别具有N个缓冲器。利用index的值来特别指定是这N个缓冲器中的哪个。再有,存储器区域h_output具有的缓冲器的数量、存储器区域d_input具有的缓冲器的数量、以及存储器区域d_output具有的缓冲器的数量也可以是不同的。存储器控制311通过下述的式子来决定示出GPU4的输入用/输出用的存储器地址的索引index。GPU4一边依次地使全局存储器41中的存储器区域d_input和存储器区域d_output各自的index发生变化一边进行数据的转送。

在此,N是GPU4具有的缓冲器的个数,mod示出求余运算。之后,存储器复制部323针对存储器控制部321决定的存储器地址,从CPU3向GPU4进行存储器复制。进而,内核启动部324针对GPU4指定转送的存储器的地址,进行内核启动。GPU4启动内核,并行地执行作为可并行处理的功能的报头添加、FEC、填补、抑制,将计算结果储存在输出用的存储器区域d_input中。

具体而言,在加扰处理的结束后,存储器复制部323向GPU4输出主存储器31的索引、以及全局存储器41的存储器区域d_input的索引,进而,向GPU4指示存储器复制。GPU4基于所通知的这些索引,从主存储器31的存储器区域h_output的缓冲器向全局存储器41的存储器区域d_input的缓冲器复制主信号。

接着,中断处理程序32向GPU4通知全局存储器41的存储器区域d_input和存储器区域d_output各自的index,进而,向GPU4指示报头添加、FEC编码、填补和抑制的并行执行。报头添加是向主信号添加报头的处理。填补是向发送中使用的字段的空区域附加规定模式的数据的处理。抑制是删除向数据前头附加的0等附加到规定位置的多余数据的处理。GPU4的内核执行部42使用所通知的索引所示出的存储器区域d_input的缓冲器中存储的数据,来并行地执行报头添加、FEC编码、填补和抑制的处理。内核执行部42将各并行处理的处理结果写入到所通知的index所示出的存储器区域d_output的缓冲器中。

CPU3的外部转送控制部325向IF板2通知示出全局存储器41的存储器区域d_output的缓冲器的index,进而,向IF板2发送外部转送的命令。IF板2的DMA执行部21开始DMA,从所通知的index所示出的存储器区域d_output的缓冲器转送主信号。外部转送部22将从GPU4读出的主信号变换为光信号,将光信号输出到ONU等外部装置。

根据上述的实施方式,利用可通过CPU和GPU协调地处理的架构,连续地进行可实现信号转送的控制。因此,能够实现包括如PCS的编码处理那样的可并行处理的功能和不可并行处理的功能这两方的通信处理的高速化,能够扩大接入系统的软件区域。

根据以上说明的实施方式,数据处理系统具备与外部装置通信的接口电路、进行第一数据处理的加速器、以及控制加速器和接口电路的中央运算处理装置。例如,数据处理系统是OLT1,加速器是GPU4,中央运算处理装置是CPU3。中央运算处理装置具备数据处理执行部、外部转送控制部、数据处理控制部、以及处理结果复制部。例如,数据处理执行部是函数执行部33,外部转送部是外部转送控制部325,数据处理控制部是函数启动部322和内核启动部324,处理结果复制部是存储器复制部323。数据处理执行部进行第二数据处理。外部转送部进行控制为使得从接口电路向加速器或中央运算处理装置转送从外部装置接收的数据的处理、以及控制为使得从加速器或中央运算处理装置向接口电路转送向外部装置发送的数据的处理中的至少任一个。数据处理控制部控制为使得针对从外部装置接收的数据或向外部装置发送的数据来执行利用加速器的第一数据处理、以及利用数据处理执行部的第二数据处理。处理结果复制部进行向中央运算处理装置的存储部输出第一数据处理的处理结果即第一处理结果来将输出的第一处理结果作为第二数据处理的处理对象的控制、以及从存储部向加速器输出第二数据处理的处理结果即第二处理结果来将输出的第二处理结果作为第一数据处理的处理对象的控制中的至少一个。

例如,加速器进行的第一数据处理是并行处理,中央运算处理装置进行的第二数据处理是串行处理。在数据处理系统是PON系统中的终端站装置的情况下,第一数据处理是报头添加、前向纠错编码、填补和抑制的并行处理,第二数据处理是包括加扰处理的处理。

以上,参照附图详述了本发明的实施方式,但是,具体的结构并不限于本实施方式,还包括不脱离本发明的主旨的范围的设计等。

产业上的利用可能性

能够利用于具有中央运算处理装置和加速器的装置。

附图标记的说明

1…OLT,2…IF板,3…CPU,4…GPU,21…DMA执行部,22…外部转送部,31…主存储器,32…中断处理程序,33…函数执行部,41…全局存储器,42…内核执行部,321…存储器控制部,322…函数启动部,323…存储器复制部,324…内核启动部,325…外部转送控制部。

- 数据处理系统、中央运算处理装置和数据处理方法

- 中央运算处理装置以及微型计算机