阵列基板的制备方法与显示面板

文献发布时间:2023-06-19 10:38:35

技术领域

本发明涉及显示技术领域,具体涉及一种阵列基板的制备方法与显示面板。

背景技术

OLED(Organic Light-Emitting Diode,有机发光二极管)技术是当前面板行业的最热门的发展趋势之一,相比传统LCD(Liquid Crystal Display,液晶显示器)技术而言,OLED具有结构简化,色域更广,响应时间更快,可实现柔性显示等优点。在OLED的像素设计中,一般采用顶栅自对准型非晶氧化物薄膜晶体管构成的3T1C电路来驱动OLED发光,但顶栅自对准结构的薄膜晶体管制备工艺非常复杂,大幅增加了OLED背板的制作成本。

相比而言,背沟道刻蚀(BCE,Back Channel Etch)工艺制备的氧化物薄膜晶体管具有显著的成本优势。然而,非晶氧化物对多种蚀刻液、等离子体都非常敏感,导致源漏刻蚀工艺变得非常困难,通常刻蚀源漏后,非晶氧化物的背沟道表面也将遭到破坏,使器件的稳定性变差。

发明内容

本发明提供一种阵列基板及其制备方法与显示面板,可解决当前在背沟道蚀刻型薄膜晶体管中,有源层背沟道区域的表面易在蚀刻时受到破坏,而导致器件稳定性变差的问题。

为解决上述问题,第一方面,本发明提供一种阵列基板的制备方法,所述制备方法包括下列步骤:

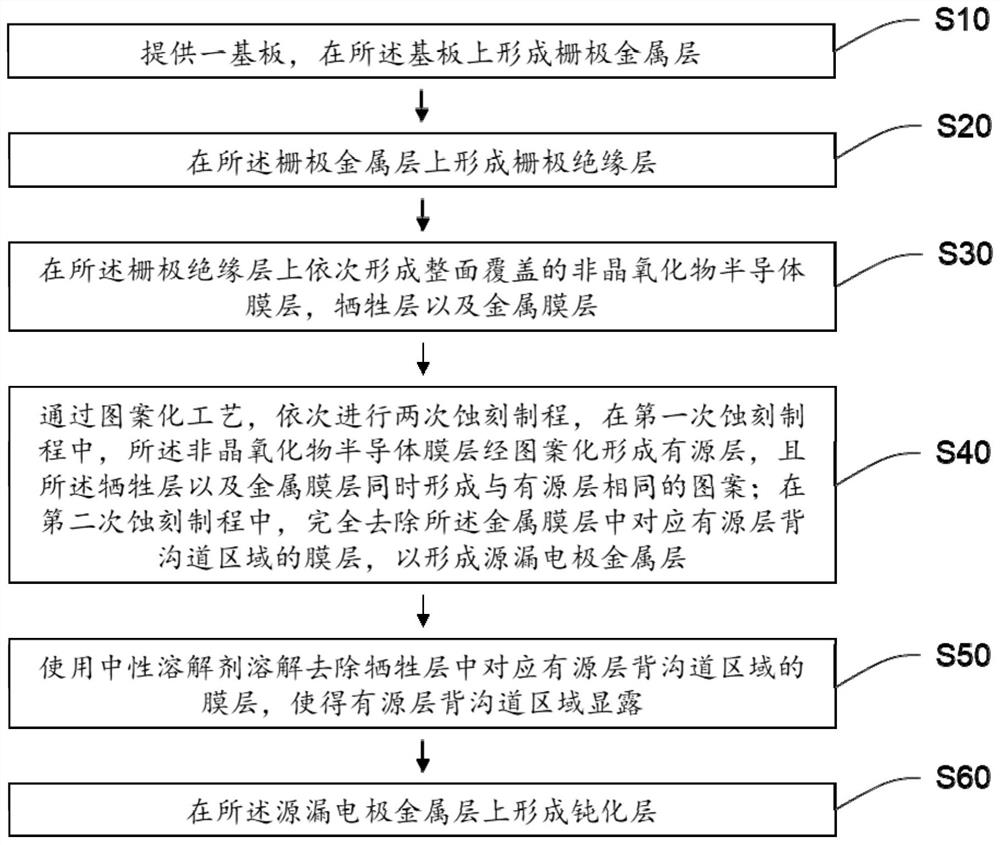

S10:提供一基板,在所述基板上形成栅极金属层;

S20:在所述栅极金属层上形成栅极绝缘层;

S30:在所述栅极绝缘层上依次形成整面覆盖的非晶氧化物半导体膜层,牺牲层以及金属膜层;

S40:通过图案化工艺,依次进行两次蚀刻制程,在第一次蚀刻制程中,所述非晶氧化物半导体膜层经图案化形成有源层,且所述牺牲层以及金属膜层同时形成与有源层相同的图案;在第二次蚀刻制程中,完全去除所述金属膜层中对应有源层背沟道区域的膜层,以形成源漏电极金属层;

S50:使用中性溶解剂溶解去除牺牲层中对应有源层背沟道区域的膜层,使得有源层背沟道区域显露;以及

S60:在所述源漏电极金属层上形成钝化层。

进一步地,在所述步骤S40中,蚀刻去除所述金属膜层中对应有源层背沟道区域的膜层后,还蚀刻去除了所述牺牲层中对应有源层背沟道区域的部分膜层。

进一步地,所述步骤S40具体包括:

S401:通过半色调掩膜版工艺,在所述金属膜层上对应所述有源层的区域形成光阻,其中,对应所述有源层背沟道区域的部分为第一光阻,剩余部分为第二光阻,所述第一光阻的高度低于所述第二光阻的高度;

S402:在所述光阻的遮蔽下,进行所述第一次蚀刻制程;

S403:对所述光阻进行整体减薄,直至所述第一光阻完全去除,得到减薄后的光阻;以及

S404:在所述减薄后的光阻的遮蔽下,进行所述第二次蚀刻制程。

进一步地,在完成所述步骤S404后,立即剥离去除所述减薄后的光阻,或,在完成所述步骤S50后,再剥离去除所述减薄后的光阻。

进一步地,所述非晶氧化物半导体膜层的材料选自氧化铟镓锌、氧化铟锌与氧化铟锌锡中的一者。

进一步地,所述牺牲层的材料为可溶解于水或有机溶剂中的材料,所述中性溶解剂选自水或有机溶剂。

进一步地,所述牺牲层的材料为水溶性氧化钨。

进一步地,所述水溶性氧化钨的密度为5.2-5.9g/cm

进一步地,采用湿法蚀刻工艺进行所述第一次蚀刻制程与所述第二次蚀刻制程,采用干法灰化工艺对所述光阻进行整体减薄。

第二方面,本发明还提供了一种显示面板,所述显示面板包括阵列基板,所述阵列基板根据上述阵列基板的制备方法制备而得。

有益效果:本发明提供了一种阵列基板及其制备方法与显示面板,在所提供的制备方法中,在所述有源层上形成由可溶性材料构成的牺牲层,在完成源漏电极金属层蚀刻制程后,再使用不会对有源层造成损伤的中性溶解剂将有源层背沟道区域的对应的牺牲层溶解去除,如此设计,即可有效避免漏电极金属层蚀刻过程中,酸性蚀刻剂或等离子体对有源层背沟道区的表面造成损伤,而造成薄膜晶体管性能不稳定的问题。

附图说明

为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1是本发明实施例提供的一种阵列基板的制备方法的文字流程示意图;

图2a-2j是本发明实施例提供的一种阵列基板的制备方法的结构流程示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

在本发明的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个所述特征。在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

在本发明中,“示例性”一词用来表示“用作例子、例证或说明”。本发明中被描述为“示例性”的任何实施例不一定被解释为比其它实施例更优选或更具优势。为了使本领域任何技术人员能够实现和使用本发明,给出了以下描述。在以下描述中,为了解释的目的而列出了细节。应当明白的是,本领域普通技术人员可以认识到,在不使用这些特定细节的情况下也可以实现本发明。在其它实例中,不会对公知的结构和过程进行详细阐述,以避免不必要的细节使本发明的描述变得晦涩。因此,本发明并非旨在限于所示的实施例,而是与符合本申请所公开的原理和特征的最广范围相一致。

本发明实施例提供了一种阵列基板的制备方法,以下结合图1提供的文字流程示意图,以及图2a-2j提供的结构流程示意图,进行详细说明。

具体地,所述制备方法包括下列步骤:

S10:提供一基板100,在所述基板100上形成栅极金属层110,即形成如图2a所示的结构;

其中,所述基板100根据实际工艺需求,可为刚性基板或柔性基板,所述栅极金属层110通过成膜,曝光,蚀刻等工艺形成,所述栅极金属层的材料选自Mo、Al、Ti、Cu等金属中的一种或者几种的组合。

S20:在所述栅极金属层110上形成栅极绝缘层120,即形成如图2b所示的结构;

其中,所述栅极绝缘层120通过化学气相沉积工艺形成整面的绝缘膜层,不需进行图案化工艺,所述栅极绝缘层120的材料选自SiO

S30:在所述栅极绝缘层120上依次形成整面覆盖的非晶氧化物半导体膜层130,牺牲层140以及金属膜层150,即形成如图2c所示的结构;

S40:通过图案化工艺,依次进行两次蚀刻制程,在第一次蚀刻制程中,所述非晶氧化物半导体膜层130经图案化形成有源层131,且所述牺牲层140以及金属膜层150同时形成与有源层相同的图案,即形成如图2c所示的结构;在第二次蚀刻制程中,完全去除所述金属膜层150中对应有源层背沟道区域的膜层,以形成源漏电极金属层151,即形成如图2g所示的结构;

S50:使用中性溶解剂溶解去除牺牲层131中对应有源层背沟道区域的膜层,使得有源层背沟道区域显露,即形成如图2h所示的结构;以及

S60:在所述源漏电极金属层151上形成钝化层170,即形成如图2j所示的结构,所述钝化层170通过成膜,曝光,蚀刻等工艺形成,并在源漏电极金属层151漏极对应的位置形成过孔,实现与上层像素电极/阳极的电性导通,所述钝化层170的材料选自SiO

在本实施例所提供的制备方法中,首先,有源层的蚀刻并不是在形成整面半导体膜层后,立即进行图案化工艺,而是在整面半导体膜层之上继续沉积整面的牺牲层以及源漏电极的金属层之后,再一并进行蚀刻,即,在有源层蚀刻制程中,上表面始终被其他膜层覆盖,不会造成沟道区膜层损伤;

其次,在进行源漏电极金属层的蚀刻制程中,有源层的上表面也始终被牺牲层覆盖,同样不会造成沟道区膜层损伤;

最后,再使用不会对有源层造成损伤的中性溶解剂将有源层背沟道区域的对应的牺牲层溶解去除,如此设计,即可有效避免在阵列基板的过程中,湿法蚀刻制程的酸性蚀刻剂或干法蚀刻制程的等离子体对有源层背沟道区的表面造成损伤,从而造成薄膜晶体管性能不稳定的问题。

在一些实施例中,由于牺牲层在所述中性溶解剂中的溶解速率较慢,导致该溶解制程的工艺时间较长,为了进一步降低时间成本,在所述步骤S40中,蚀刻去除所述金属膜层150中对应有源层背沟道区域的膜层后,还蚀刻去除了所述牺牲层140中对应有源层背沟道区域的部分膜层,即如图2g所示,可以理解的是,牺牲层的蚀刻速率远大于溶解速率,此处,在保证下层有源层131上表面不裸露的前提下,尽可能的蚀刻去除更多的牺牲层140,当然,为减小制备时间,所述牺牲层所沉积的整体膜厚也不会太厚,通常为5-100nm。

在一些实施例中,所述步骤S40中进行的两次蚀刻制程,可分别通过两道光罩形成的两层光阻进行,为了简化制程,也可采用半色调掩膜版工艺,仅需一道光罩即可完成,具体包括:

S401:通过半色调掩膜版工艺,在所述金属膜层150上对应所述有源层的区域形成光阻160,其中,对应所述有源层背沟道区域的部分为第一光阻161,剩余部分为第二光阻162,所述第一光阻161的高度低于所述第二光阻162的高度,即形成如图2d所示的结构,此处所述第一光阻161与第二光阻162的高度差,由对应半色调掩膜版区域不同的透光度形成,具体形成步骤不再赘述,本领域技术人员应当很容易理解;

S402:在所述光阻160的遮蔽下,进行所述第一次蚀刻制程,即形成如图2e所示的结构;

S403:对所述光阻进行整体减薄,直至所述第一光阻完全去除,得到减薄后的光阻163,即形成如图2f所示的结构,所述减薄后的光阻163仅遮蔽源漏电极的预设区域,露出有源层背沟道区;以及

S404:在所述减薄后的光阻163的遮蔽下,进行所述第二次蚀刻制程,即形成如图2g所示的结构。

在一些实施例中,在完成所述步骤S404后,立即剥离去除所述减薄后的光阻(此情形未给出具体的结构示意图,但应当很容易理解),或,在完成所述步骤S50后,再剥离去除所述减薄后的光阻163,即由如图2h所示的结构转变为如图2i所示的结构,在前述的两种情形中,后者,将光阻剥离的制程后置于牺牲层溶解制程之后,即可通过光阻的遮蔽,以避免源漏电极金属层的上表面在溶解制程中发生可能的性能变化,即避免了漏极与上层的像素电极(图中未示出)的接触界面发生变化,造成器件性能偏移的问题。

在一些实施例中,所述非晶氧化物半导体膜层的材料,即有源层的材料,选自氧化铟镓锌、氧化铟锌与氧化铟锌锡中的一者,或是其他的非晶氧化物半导体材料。

在一些实施例中,所述中性溶解剂需选自不会对有源层膜层造成损伤的水或有机溶剂,相对应地,所述牺牲层的材料为可溶解于水或有机溶剂中的材料,当然,由于牺牲层的设置,源极与漏极分别通过牺牲层与有源层实现导通,牺牲层材料的电阻率也不能过低,因此,示例性地,我们可以选择水溶性的WOx作为牺牲层材料,一方面,为保证WOx的溶解性,其密度控制在较低水平,经验证,当WOx为5.2~5.9g/cm3时,其溶解性可适用于制备的工艺需求,另一方面,从牺牲层的电性方面考虑,按目前的氧化铟镓锌薄膜晶体管应用和实验制备的20nm WOx膜层来看,源漏极寄生电阻不会超过10kohm,以纯欧姆电阻来计算,WOx的电阻率应<1000ohm*cm,考虑到肖特基情况,WOx实际电阻率可做到<1ohm*cm;同时WOx可通过物理气相沉积工艺进行沉积,以及传统的蚀刻工艺进行图案化,制程工艺简单,无需引入新设备以及新工艺。

在一些实施例中,采用湿法蚀刻工艺进行所述第一次蚀刻制程与所述第二次蚀刻制程,采用干法灰化工艺对所述光阻进行整体减薄。

需要说明的是,上述显示面板的制备方法实施例中仅描述了上述结构,可以理解的是,除了上述结构之外,还可以根据需要,通过常规工艺形成任何其他的必要结构,具体此处不作限定。

本发明实施例还提供了一种阵列基板,由上述实施例中所提供的阵列基板的制备方法制备而得,所述阵列基板的具体结构已在上述实施例中揭露,此处不再赘述。

本发明实施例还提供了一种显示面板,包括上述实施例所提供的阵列基板,作为驱动背板。所述显示面板的类型包括但不限于液晶显示面板,OLED显示面板以及Micro LED显示面板。

在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见上文针对其他实施例的详细描述,此处不再赘述。

以上对本发明实施例所提供的一种阵列基板的制备方法与显示面板进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

- 阵列基板、显示面板以及阵列基板的制备方法

- 阵列基板的制备方法、阵列基板及液晶显示面板