一种面向卷积神经网络的可重构近似张量乘加单元及方法

文献发布时间:2023-06-19 10:48:02

技术领域

本发明属于可重构计算领域,具体涉及一种面向卷积神经网络的可重构近似张量乘加单元及方法。

背景技术

在过去的几十年里,基于低功耗人工智能的物联网系统的设计和优化变得非常重要。这是因为这些电池供电的物联网设备需要具有低功耗和可靠精度的定制神经网络加速器来高效地处理每个神经网络层的能量计算。

卷积神经网络,是深度学习的代表算法之一,卷积神经网络主要分为卷积层、池化层和全连接层,它通过局部感知的方式对输入进行特征提取和分类。在语音识别、图像识别、图像分割,自然语言处理等领域中得到了广泛应用。

由于神经网络的计算中并不需要完全精确的结果,因此引入了近似计算。近似计算是一种新兴的基于人工智能的物联网设备电路设计技术,通过牺牲一定的精度,在满足精度要求的前提下,通过近似设计,提高电路的运算速度并显著降低设计成本。通过近似计算,能在一定程度上提高电路的性能并改良电路特性。卷积操作中涉及大量的乘加操作,这些操作需要消耗大量的计算资源,因此,提出了一种面向卷积神经网络的可重构近似张量乘加单元,它能改进传统乘完再加的运算方式面积大、功耗高的问题,为卷积神经网络中的乘加操作带来低功耗、高速的解决办法。

发明内容

本发明所要解决的技术问题是:提出一种面向卷积神经网络的可重构近似张量乘加单元及方法,以优化卷积操作中大量的乘加运算,并实现低功耗、高速度地完成计算任务。

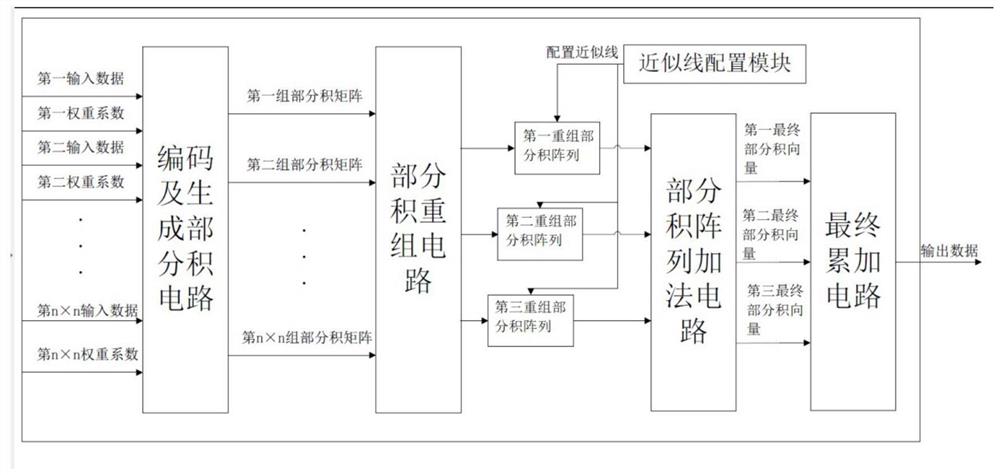

一种面向卷积神经网络的可重构近似张量乘加单元,包括依次连接的编码及生成部分积电路、部分积重组电路、部分积阵列加法电路和最终累加电路。

输入n×n张量数据和权重到编码及生成部分积电路,编码及生成部分积电路对权重进行编码,并对输入的n×n张量数据每一位进行混合布斯编码操作后生成部分积矩阵,生成的部分积矩阵将被顺序输出到部分积重组电路当中。

部分积重组电路将部分积矩阵的相同行放在一起,对部分积矩阵进行重新排列,并生成n×n重组部分积阵列,所生成的n×n重组部分积阵列的数量由权重的位数决定,每个n×n行重组部分积阵列依次输出到部分积阵列加法电路当中。

部分积阵列加法电路将输入的每个n×n行重组部分积阵列累加,形成累加结果,将累加结果分别经过移位后形成最终部分积向量,最终部分积向量的数量与n×n重组部分积阵列的数量相同,所述最终部分积向量均为一行部分积向量,所有的最终部分积向量经最终累加电路后,最终累加电路的输出即为乘加单元最终的输出结果。

本发明的一种面向卷积神经网络的可重构近似张量乘加单元输入一组n×n张量数据与权重到编码及生成部分积电路,所述的n×n张量数据可以是n×n卷积核,16bit,编码及生成部分积电路对权重进行编码,并对输入的n×n张量数据每一位进行混合布斯编码操作后生成部分积矩阵,生成的部分积矩阵被顺序输出到部分积重组电路当中,部分积重组电路将输入的部分积矩阵按照相同行排列在一起的原则进行重新排列,即将部分积矩阵中同样位于第一行的部分积排列在一起构成重组部分积阵列,位于其他行的部分积也做相同的操作,对于编码及生成部分积电路中输入的是8bit权重来说,重组部分积阵列为三个重组部分积阵列。对于16bit输入,每行重组部分积阵列大小均为n×n×17,其中n×n为阵列的行数,其大小为n×n的卷积核规模,17为阵列的列数,将三个重组部分积阵列将输入到部分积阵列加法电路中,累加结果经过移位后形成三个最终部分积向量,再经最终累加电路后的输出即为乘加单元最终的输出结果。

优选的,编码及生成部分积电路通过基-4和基-8混合布斯编码的方式对输入的权重进行编码,对于高位权重,用基-4编码,对于低位权重,用近似的基-8编码,将基-8布斯编码中×3操作修改为×4,在编码电路中引入近似操作;输入的权重经混合编码后生成编码后权重部分积,对于8bit权利来说,所述编码后权重部分积为三行部分积阵列。

采用混合布斯编码的方式不仅可以缩小部分积生成电路的规模,其带来偏大的误差还可以对后续的误差起到补偿作用,以提高整体精度。对于8bit权重,使用混合编码后仅生成三行部分积阵列,大大减少了部分积数量,且降低了所需硬件规模。

优选的,部分积阵列加法电路包括加法树累加电路,加法树累加电路包括加法器,加法器采用复用的方式。

加法树累加电路用于对依次输入的n×n重组部分积阵列分别进行累加,利用树形的相加结构使加法部分能并行执行,有效地提高了电路的速度。加法树累加电路中树形结构的第一层用于将n×n重组部分积两两相加并输出到树形结构的第二层,树形结构的第二层用于将第一层输出的(n×n)/2行部分积两两相加并输出到树形结构的第三层,以此类推,直到每个n×n重组部分积阵列中所有的部分积均彼此相加为止,每个n×n重组阵列加法最后会生成一个最终部分积向量,所述最终部分积向量为一行部分积,加法树累加电路中树形结构的每一层均由加法器构成。对于大规模的卷积核,在加法树累加电路中的加法器采取复用的方式,以减小硬件规模。

本发明的一种面向卷积神经网络的可重构近似张量乘加单元还包括似线配置模块,所述加法器为近似加法器,近似加法器用于通过近似线配置模块设置每个n×n重组部分积阵列近似线的位置k,并将每个重组部分积阵列近似相加。

在近似加法器中,每个n×n重组部分积阵列的部分积均采用扩展符号位后不移位相加的方式,每个n×n重组部分积阵列中,位于近似线后的k位部分积采用或门代替精确全加器的方式,而位于近似线前的17-k位依然采用精确全加器相加,第17-k位部分积的进位来自于近似线后1位的两个部分积通过与门生成。

该近似加法方案有效地降低了电路整体的功耗和面积,且能维持一定的精度。近似加法器通过近似线配置模块修改不同重组部分积阵列近似线的位置以达到精度可调的功能。由于每行最终部分积阵列之间是移位相加,因此对不同重组部分积阵列配置不同的近似线可以使该乘加单元功能更灵活,针对不同应用场景达到功耗和精度间的最佳权衡。近似线配置模块对每个重组积阵列配置不同的近似线,并将部分积阵列近似相加,输出到最终累加电路当中。

本发明还提出了一种面向卷积神经网络的可重构近似张量乘加方法,该方法步骤如下:

步骤1:一组的n×n张量数据和权重首先经过编码并生成部分积电路,经过权重编码和生成部分积操作后生成n×n的部分积阵列。

步骤2:n×n的部分积阵列经过部分积重组电路,在部分积重组电路中将部分积阵列中同样位于第一行的部分积排列在一起构成一行重组部分积阵列,重组后的部分积将形成m个n×n的部分积阵列,n×n的部分积阵列的数量由权重的位数决定。

步骤3:m个n×n重组部分积阵列依次输入到部分积阵列加法电路中,部分积阵列加法电路包括加法树累加电路,加法树累加电路包括加法器,所述加法器为近似加法器,近似加法器通过近似线配置模块配置每个部分积阵列近似线的位置K。

步骤4:在部分积阵列加法电路中,每个n×n重组部分积阵列中的数据进行不移位相加,对于每个n×n重组部分积阵列中的两行部分积,先扩展符号位,然后通过已配置的近似线进行近似相加;对于每行重组部分积阵列部分积阵列之间,使用树形结构将所有部分积近似累加起来,形成m个累加结果,将m个累加结果分别经过移位后形成m个最终部分积向量。

步骤5:m个最终部分积向量经过最终累加电路,生成最后的乘加结果,该乘加结果即为一组数据和权重对应乘加后的结果。

有益效果:

(1)针对卷积神经网络的卷积运算,提出一种乘加计算方法,该乘加方法改变了数据乘完后再相加的传统运算模式,通过将部分积重排列成部分积阵列而后相加的方式,提高乘加运算操作的灵活性,便于近似操作的引入。

(2)部分积阵列排列成重组部分积阵列,由于采用相同行排列在一起的原则,相比传统乘加操作,其部分积排列更紧密,因此能在精度相当的情况下,降低更多电路的功耗与面积。在重组部分积阵列中引入近似线,对近似线后的k位部分积进行近似运算,能在运算精度下降有限的情况下,显著降低电路的功耗和面积。

(3)近似线配置模块通过对不同部分积阵列配置不同的近似线,达到精度可调的功能,灵活配置近似线能够针对不同的应用场景下的精度要求,达到精度和电路硬件优化之间的最佳权衡。

(4)编码和生成部分积电路中使用基-4和近似基-8混合布斯编码的方式,显著减少了部分积的数量,通过将基-8布斯编码的×3操作修改为×4,不仅能有效降低运算的复杂度,缩小电路的规模,其引入偏大的误差能和部分积阵列中引入的偏小误差互相补偿,进而提高整体运算精度。

附图说明

图1是本发明的整体示意图;

图2是本发明的以3×3卷积核为例,部分积的编码重组过程示意图;

图3是三个重组部分积阵列依次输入到部分积阵列加法电路中示意图

图4是本发明加法树累加电路计算过程示意图,其中近似线k=10;

图5是本发明计算方法的流程图;

具体实施方式

图1是本发明提出的方框示意图,一种面向卷积神经网络的可重构张量乘加单元包括依次连接的编码及生成部分积电路、部分积重组电路、部分积阵列加法电路和最终累加电路。

输入n×n张量数据和8bit权重到编码及生成部分积电路,编码及生成部分积电路对8bit权重进行编码,并对输入数据矩阵每一位进行混合布斯编码操作生成部分积矩阵,生成的部分积矩阵将被顺序输出到部分积重组电路当中。

部分积重组电路将部分积矩阵的相同行放在一起,对部分积矩阵进行重新排列,并生成重组部分积阵列,重组部分积阵列输出到部分积阵列加法电路当中。

部分积阵列加法电路将重组部分积阵列近似累加成一行部分积,不同行部分积移位后组成最终部分积向量并输出到最终累加电路当中。在部分积阵列加法电路中,部分积阵列的加法运算过程运用加法树累加电路,并在重组部分积阵列中添加近似线,得到精度可调的近似累加阵列结构,最终累加电路将输出的最终部分积向量累加以得到最终的输出结果。

本实例结合图2、图3对该近似乘加单元给出具体说明,如下:

实例中,编码及生成部分积电路的输入为3×3的卷积核,输入数据为9×16bit,权重为9×8bit。

在编码及生成部分积电路中,首先对8bit权重系数进行布斯编码,采用混合编码的方式,编码过程中相邻位有1bit交叠,对低6bit,采用近似的基-8编码,对于高3bit,采用基-4编码,得到的编码后权重部分积为三行部分积阵列,编码后权重部分积与输入的卷积核进行运算输出9个部分积矩阵。

在部分积重组电路中,将输入的9个部分积矩阵进行重组,输出重组的3个部分积阵列,分别为第一重组部分积阵列、第二重组部分积阵列和第三重组部分积阵列,第一重组部分积阵列、第二重组部分积阵列和第三重组部分积阵列均包括3×3×17bit部分积。

对第一重组部分积阵列、第二重组部分积阵列和第三重组部分积阵列,依次输入到部分积阵列加法电路中进行张量计算,所述的张量计算是指将三个重组部分积阵列分别进行加法树计算,本实施例中的加法树为三层,即进行三层加法树的计算,分别为加法树第一层计算S1、加法树第二层计算S2和加法树第三层计算S3。第一重组部分积阵列、第二重组部分积阵列和第三重组部分积阵列对应的进行第一张量计算、第二张量计算和第二张量计算。如图3所示,部分积阵列加法电路包括加法树累加电路,加法树累加电路包括加法器,加法树的每一层由加法器构成,如图3所示,展示了加法树累加电路的计算过程。

对于输入的3*3行重组部分积阵列,通过加法树累加电路进行累加,将3*3行重组部分积阵列中的部分积两两相加。图3中,加法树累加电路中树形结构的第一层,其中,1#1表示树形结构第一层中的第一个加法器,1#2表示树形结构第一层中的第二个加法器,依次论推,1#4表示树形结构第一层中的第4个加法器;加法树累加电路中树形结构的第一层,在4个加法器中将8个数据两两相加,得到4个19bit中间和,加法树累加电路中树形结构第二层,在2个加法器中将4个19bit中间和两两相加得到2个20bit中间和,加法树累加电路中树形结构的第三层,在一个加法器中将2个20bit中间和相加得到1个21bit的最终结果。

本发明的一种面向卷积神经网络的可重构近似张量乘加单元还包括似线配置模块,所述加法器为近似加法器,近似加法器用于通过近似线配置模块设置每个n×n重组部分积阵列近似线的位置k,本实例中第一重组部分积阵列的近似线为k=10、第二重组部分积阵列近似线为k=8、第三重组部分积阵列近似线为k=6。

在部分积阵列加法电路中的近似加法器中,对于第一重组部分积阵列来说,后10位部分积之间用或门代替全加器进行相加,前7位部分积依旧用精确全加器相加,第7位的进位来自第8位的两个部分积通过与门得到,第一重组部分积阵列经近似加法器后得到对应的第一最终部分积向量。

第二重组部分积阵列和第三重组部分积阵列也采用相同的方式将两行部分积相加。对于第二重组部分积阵列来说,后8bit部分积之间用或门代替全加器进行相加,前9位部分积依旧用精确全加器相加,第9位的进位来自第10位的两个部分积通过与门得到,第二重组部分积阵列经近似加法器后得到对应的第二最终部分积向量;对于第三重组部分积阵列来说,后6位部分积之间用或门代替全加器进行相加,前11位部分积依旧用精确全加器相加,第11位的进位来自第12位的两个部分积通过与门得到,第三重组部分积阵列经近似加法器后得到对应的第三最终部分积向量。

本实施例中,在部分积阵列加法电路中,三个重组部分积阵列,按照流水线的工作方式,依次通过加法树结构,得到三个21bit的最终部分积向量,分别是第一最终部分积向量、第二最终部分积向量和第三最终部分积向量,第一最终部分积向量、第二最终部分积向量和第三最终部分积向量移位排列后,再通过最终累加电路,累加成最后的28bit输出结果,完成基于3×3卷积核的16bit输入数据矩阵和8bit权重的乘加计算。

- 一种面向卷积神经网络的可重构近似张量乘加单元及方法

- 一种面向物联网领域的动态可重构卷积神经网络加速器架构