芯片上突波保护电路

文献发布时间:2023-06-19 11:06:50

技术领域

本发明涉及突波保护电路技术领域,尤其涉及一种整合在芯片上的突波保护电路。

背景技术

突波(surge),又称为涌浪,是指出现在电路中的瞬间过载的电流或电压,它可能造成电路的损坏。

图1显示几种突波事件的肇因。

突波事件可能来自:(1A)直接雷击(direct lightning stroke),落在位于室外的外部电路(例如,配电箱11)者;(1B)非直接雷击(indirect lightning stroke),冲击到云端网络或产生干扰电磁场12者;或(1C)放电耦合能量(discharge coupling energy),邻近于直接接地(direct ground)13者。

图2显示电子装置2的等效电路图,其使用“电路板上”(on-board)的突波保护单元26。

典型地,电子装置2包括一次侧(primary side)变压器21、二次侧(secondaryside)变压器22、及芯片23。芯片23例如是前端积体电路(front-end integrated circuit,FEIC)芯片。芯片23的发送端(TX)包括负端(-)及正端(+)。在图2中,突波24经由一次侧变压器21与二次侧变压器22的耦合效应,会在二次侧变压器22处感应出过载电流25,流经芯片23的发送端。

对此,现有的解决方案是使用“电路板上”的突波保护单元26来泄放过载电流至大地(ground)。突波保护单元26可包括外部电阻261及/或突波保护器262,例如,瞬态电压抑制器(transient voltage suppressor,TVS)、齐纳二极管(Zener diode)、闸流体(thyristor)、突波抑制器(surge suppressor)等。无论如何,这种突波保护单元26只是位于“电路板上”,但位于芯片23的外部,需要引进额外元件,投入额外设计,并占用电路板的额外面积。

因此,亟须提出一种全新的突波保护电路,以改进上述问题。

发明内容

有鉴于此,本发明旨在提出一种芯片上(on-chip)突波保护电路,以达成下列第一目的的任何一者或其结合:(1-1)泄放突波所引起的过载电流;(1-2)免除芯片外部的突波保护单元,例如,免除图2的外部电阻(亦即,外部电阻261等于0欧姆(Ω))及/或图2的免除外部突波保护器;(1-3)将突波保护电路整合于芯片内部;及/或(1-4)达成芯片对付突波的自动自我保护机制(auto self-protection)。

优选地,本发明的芯片上突波保护电路亦旨在达成下列第二目的的任何一者或其结合:(2-1)免除突波侦测器;(2-2)免除用于控制突波保护器的额外触发电路;(2-3)减少突波保护电路所占用的面积;及/或(2-4)降低突波保护电路的复杂度。它们属于片级(chip-level)的课题。

更优地,本发明的芯片上突波保护电路亦旨在达成的下列第三目的:满足突波通过规格(surge pass specification),芯片的运作必须足以承受1kV的(差分)突波通过其发送端的接脚(pin)。

根据本发明的一种观点,提出一种芯片上突波保护电路,包括低压轨、差分负发送端、差分正发送端、及突波保护元件。突波保护元件包括第一端、第二端、及控制端。第一端连接至差分负发送端。第二端连接至差分正发送端。控制端连接至低压轨。

可选地,或优选地,突波保护元件整合于芯片内部。

可选地,或优选地,突波在差分负发送端引起差分负突波电压,而在差分正发送端引起差分正突波电压。突波保护元件组态成:根据差分负突波电压、差分正突波电压、及低压轨的电压来开启。

可选地,或优选地,突波保护元件组态成:若没有突波或突波消失,则关闭。

可选地,或优选地,低压轨的电压作为突波保护元件的突波控制信号。

可选地,或优选地,突波保护元件在差分负发送端与差分正发送端之间形成分流路径来泄放突波电流。

可选地,或优选地,分流路径是双向路径,根据差分负突波电压与差分正突波电压来决定自差分负发送端流向差分正发送端,或自差分正发送端流向差分负发送端。

可选地,或优选地,突波保护元件是双极性结型晶体管(BJT)、硅控整流器(SCR)、场氧化层晶体管(FOD)、金属氧化物半导体(MOS)场效晶体管。

可选地,或优选地,突波保护元件是寄生元件。

可选地,或优选地,突波保护元件由氧化物扩散二极管结构或井二极管结构所形成。

可选地,或优选地,芯片上突波保护电路还包括第一上拉元件、第二上拉元件、第一下拉元件、及第二下拉元件。第一上拉元件设置在高压轨与差分正发送端之间。第二上拉元件设置在高压轨与差分负发送端之间。第一下拉元件设置在差分正发送端与低压轨之间。第二下拉元件设置在差分负发送端与低压轨之间。

可选地,或优选地,第一上拉元件、第二上拉元件、第一下拉元件、及/或第二下拉元件是二极管、硅控整流器、双极性结型晶体管、或金属氧化物半导体场效晶体管。

可选地,或优选地,第一上拉元件、第二上拉元件、第一下拉元件、及/或第二下拉元件由在位于深N型井中形成P型井与N型井来制成。

可选地,或优选地,突波保护元件是因第一上拉元件、第二上拉元件、第一下拉元件、及第二下拉元件所生的寄生元件。

可选地,或优选地,芯片上突波保护电路组态成:在开路电压波为1.2μs/50μs,而短路电流波为8μs/20μs的规格下,足以承受0至4kV的突波电压。

可选地,或优选地,芯片上突波保护电路组态成:在开路电压波为10μs/700μs,而短路电流波为5μs/320μs的规格下,足以承受0至4kV的突波电压。

根据本发明的另一种观点,提出一种电子装置,包括一次侧变压器、二次侧变压器、及芯片。二次侧变压器耦合至一次侧变压器。芯片连接至二次侧变压器,并包括上述突波保护电路。

可选地,或优选地,电子装置不存在外部电阻,亦不存在外部突波保护器。

可选地,或优选地,电子装置是电路板或数字用户回路。

下文将配合附图并详细说明,使本发明的其他目的、优点、及新颖特征更明显。

附图说明

图1是几种突波事件的肇因;

图2是电子装置的等效电路图;

图3是参考例1的突波保护电路;

图4是本发明的一实施例的自动自我保护芯片的示意图;

图5是一种突波的波形;

图6是突波测试网络的等效电路图;

图7是突波、差分负突波电压、及差分正突波电压的波形图;

图8是本发明的实施例1的芯片上突波保护电路的电路图;

图9A是一种NPN型的BJT;

图9B是图9A的BJT的等效电路图;

图10是本发明的实施例2的芯片上突波保护电路的电路图;

图11是本发明的实施例3的芯片上突波保护电路的电路图;

图12是本发明的实施例4的芯片上突波保护电路的电路图;

图13A、图13B、图13C、及图13D分别是本发明的实施例4的芯片上突波保护元件在使用双极性结型晶体管、硅控整流器、场氧化层晶体管、或金属氧化物半导体场效晶体管时的具体接法;

图14是本发明的另一实施例的BJT结构;

图15是本发明的一实施例的电子装置的等效电路图;

图16是本发明的一实施例的芯片上突波保护电路的电路图。

符号说明:

2、2’ 电子装置

21 一次侧变压器

22 次侧变压器

23 (已知)芯片

24 突波

25 过载电流

261 外部电阻

262 突波保护器

3、3’ 突波保护电路

31 偏压单元

32 突波侦测单元

33 突波保护单元

4 (自动自我保护)芯片

5、5’ 突波保护电路

51 高压轨

52 低压轨

53 第一节点

54 第二节点

551 第一二极管

552 第二二极管

553 第三二极管

554 第四二极管

56 双极性结型晶体管(BJT)

571 静电放电保护元件

572 静电放电侦测器

6、6’ 突波保护电路

61 突波保护元件

601 高压轨

602 低压轨

611 第一端

612 第二端

613 控制端

614 第一硅控整流器

615 第二硅控整流器

621 第一上拉元件

622 第二上拉元件

623 第一下拉元件

624 第二下拉元件

7 BJT结构

AVDD 高压轨的电压

AVDD33 接脚

AVSS 低压轨的电压

AVSS33 接脚

EN 特别控制信号

iB 基极电流

iC 集极电流

iE 射极电流

LD 第一逻辑元件

LNA 第二逻辑元件

OX1、OX2 氧化物

N1、N2、N3 掺杂区

NW1、NW2 N井

P1 主流路径

P2 分流路径

PSUB P型基板

RXN 差分负接收端

RXP 差分正接收端

S 突波

T、T1、T2 时间区间

Td 持续时间

Tf 前缘时间

TXN 差分负发送端

TXN_PCB 电路板的正端

TXP 差分正发送端

TXP_PCB 电路板的负端

VB 基极电压

VBE 基极-射极电压

VC 集极电压

VCE 集极-射极电压

VE 射极电压

VDD 电压

VGND 接地电压

VTXN 差分负突波电压

VTXP 差分正突波电压

具体实施方式

以下提供本发明的不同实施例。这些实施例是用于说明本发明的技术内容,而非用于限制本发明的权利范围。一实施例的一特征可通过合适的修饰、置换、组合、分离,以应用于其他实施例。

应注意的是,在本文中,除了特别指明的之外,具备“一”元件不限于具备单一的该元件,而可具备一或更多的该元件。

此外,在本文中,除了特别指明的之外,“第一”、“第二”等序数,只是用于区别具有相同名称的多个元件,并不表示它们之间存在位阶、层级、执行顺序、或工艺顺序。一“第一”元件与一“第二”元件可能一起出现在同一构件中,或分别出现在不同构件中。序数较大的一元件的存在不必然表示序数较小的另一元件的存在。

此外,在本文中,所谓的“上”、“下”、“左”、“右”、“前”、“后”、或“之间”等用语,只是用于描述多个元件之间的相对位置,并在解释上可推广成包括平移、旋转、或镜射的情形。

此外,在本文中,除了特别指明的之外,“一元件在另一元件上”或类似叙述不必然表示该元件接触该另一元件。

此外,在本文中,“优选”或“更优”是用于描述可选的或附加的元件或特征,亦即,这些元件或特征并不是必要的,而可能加以省略。

此外,各元件可以适合的方式来包括一或多个有源元件,例如,晶体管或逻辑门,或一或多个无源元件,例如,电阻、电容、或电感,但不限于此。各元件可以适合的方式来彼此连接,例如,分别配合输入信号及输出信号,使用一或多条线路来形成串联或并联。此外,各元件可允许输入信号及输出信号依序或并列进出。上述组态皆是依照实际应用而定。

此外,在本文中,“系统”、“设备”、“装置”、“模块”、或“单元”等用语,是指一电子元件或由多个电子元件所组成的一数字电路、一类比电路、或其他更广义电路,且除了特别指明的之外,它们不必然有位阶或层级关系。

此外,在本文中,除了特别指明的之外,两个元件的电性连接可包括直接连接或间接连接。在间接连接中,该两个元件之间可能存在一或多个其他元件,例如,电阻、电容、或电感。电性连接用于传递一或多个信号,例如,直流或交流的电流或电压,依照实际应用而定。

(参考例1)

图3显示参考例1的突波保护电路3。

在图3中,突波保护电路3设置在差分(differential)负发送端TXN与差分正发送端TXP之间。突波保护电路3包括偏压(bias)单元31、突波侦测单元32、及突波保护单元33。偏压单元31连接至突波侦测单元32以施加预定偏压给突波侦测单元32。突波侦测单元32连接至突波保护单元33,在突波侦测单元32侦测到TXN与TXP之间出现突波时,它就会产生特别控制信号EN,以启动突波保护单元33。

在其他实施例中,优选地,偏压单元31及突波侦测单元32可加以省略,而突波保护单元33可不必由特别控制信号EN来控制,借此减少突波保护电路所占用的面积,及/或降低突波保护电路的复杂度。

(本发明宗旨)

图4显示本发明的一实施例的自动自我保护芯片4的示意图。

在图4中,突波24经由一次侧变压器21与二次侧变压器22的耦合效应,会在二次侧变压器22处感应出过载电流25,流经自动自我保护芯片4的发送端。本发明旨在将芯片上突波保护电路实现在自动自我保护芯片4内部,因此,在图4中,已免除芯片外部的突波保护单元。

自动自我保护芯片4包括下列接脚:

差分负接收端RXN(可参考例如图13A),又称为接收器差分输入负端(receiverdifferential input N);差分正接收端RXP(可参考例如图13A),又称为接收器差分输入正端(receiver differential input P);差分负发送端TXN,又称为发送器差分输出负端(transmitter differential output N);及差分正发送端TXP,又称为发送器差分输出正端(transmitter differential output P)。差分负接收端RXN与差分正接收端RXP构成自动自我保护芯片4的接收端RX,而差分负发送端TXN与差分正发送端TXP构成自动自我保护芯片4的发送端TX。

图5显示一种突波的波形。

为了测试各装置对付突波的效能,可使用突波结合波产生器(combination wavegenerator,CWG)来产生突波。本发明亟欲满足下列规格1及规格2。

规格1:开路电压波(open voltage wave)为1.2μs/50μs,而短路电流波(shortcurrent wave)为8μs/20μs。us是指微秒(microsecond),其定义详见表1。

表1规格1

规格2:开路电压波为10μs/700μs,而短路电流波为5μs/320μs,其定义详见表2。

表2规格2

图6显示突波测试网络的等效电路图。在图6中,突波24经由一次侧变压器21与二次侧变压器22的耦合效应,会在二次侧变压器22处感应出过载电流25,自电路板的正端TXN_PCB,流向电路板的负端TXP_PCB,途经若干电阻(未标示元件符号),各电阻例如是10欧姆。

图7显示突波S、差分负突波电压VTXN、及差分正突波电压VTXP的波形图。在遭遇突波事件时,突波S会在TXN引起差分负突波电压VTXN,而在TXP引起差分正突波电压VTXP。

(实施例1)

图8显示本发明的实施例1的芯片上突波保护电路5的电路图。

如图8所示,本发明的芯片上突波保护电路5包括高压轨51、低压轨52、第一节点53、及第二节点54。高压轨51连接至接脚AVDD33,低压轨52连接至接脚AVSS33,第一节点53连接至差分负发送端TXN,而第二节点54连接至差分正发送端TXP。

芯片上突波保护电路5还包括第一二极管551、第二二极管552、第三二极管553、第四二极管554、及双极性结型晶体管(bipolar junction transistor,BJT)56。第一二极管551的阴极(-)连接至高压轨51,其阳极(+)连接至第一节点53。第二二极管552的阴极(-)连接至高压轨51,其阳极(+)连接至第二节点54。第三二极管553的阴极(-)连接至第一节点53,其阳极(+)连接至低压轨52。第四二极管554的阴极(-)连接至第二节点54,其阳极(+)连接至低压轨52。BJT 56的集极(C)连接至TXN,其射极(E)连接至TXP,其基极(B)连接至低压轨52。

上述各二极管可由在位于深N型井(deep n-well,DNW)中形成P型井(p-well,PW)与N型井(n-well,NW)来制成。

在芯片上突波保护电路5中,BJT 56即是作为芯片内部的突波保护元件,它设置在TXN、TXP、及接地GND(即低压轨52)之间。在其他实施例中,可将BJT 56置换成硅控整流器(silicon controlled rectifier,SCR)、场氧化层晶体管(field oxide device,FOD)、或金属氧化物半导体(metal-oxide-silicon,MOS)场效晶体管,而不限于此。各实施例将在下文中加以说明。

图9A显示一种NPN型的BJT,并标示其集极电流i

在没有遭遇突波事件或突波事件已消失的正常运作下,TXN的电压大于0,而TXP的电压亦大于0,因此,BJT 56不开启,而呈现关闭。发送信号(TX signal)可正常地自芯片的发送端TX发出,经由变压器,前往预定的接收器。例如,发送信号可传送至他处的接收器;或在验证(verification)时,则可回传至本处的接收器。

如前所述,请参考图7,在遭遇突波事件时,突波S会在TXN引起差分负突波电压VTXN,而在TXP引起差分正突波电压VTXP。

此时,BJT的三个极TXN、TXP、及接地GND(即低压轨52)各自的电压VTXN、TXP、及VGND之间的关系,可能产生下列情形的任何一种:(情形1)VTXN小于VGND,且VGND又小于VTXP(亦即,VTXN<VGND<VTXP);或(情形2)VTXP小于VGND,且VGND又小于VTXN(亦即,VTXP<VGND<VTXN)。由上述BJT开启的条件(V

应该注意的是,上述触发机制,归功于本发明已理解到,突波S在TXN及TXP分别引起差分负突波电压VTXN及差分正突波电压VTXP,恰可满足例如BJT等的突波保护元件的开启条件。本发明将其称为“自动触发机制”:在突波耦合至二次侧变压器乃至于自发送端TX进入芯片时,突波保护元件会自动开启。

据此,可达成突波保护电路的简化。具体而言,根据本发明的自动触发机制,图3的参考例1的突波保护电路3的偏压单元31及突波侦测单元32可加以省略,而突波保护单元33可不必由特别控制信号EN来控制,借此减少突波保护电路所占用的面积,及/或降低突波保护电路的复杂度。

回到图8,可选地或优选地,本发明的芯片上突波保护电路5还可包括静电放电(electrostatic discharge,ESD)保护元件571及静电放电侦测器572。静电放电保护元件571例如是晶体管,其源极与漏极分别连接至高压轨51与低压轨52,而其栅极连接至静电放电侦测器572。静电放电侦测器572组态成:若侦测到静电放电事件,则开启静电放电保护元件571,以便泄放静电放电所产生的电流。

(实施例2)

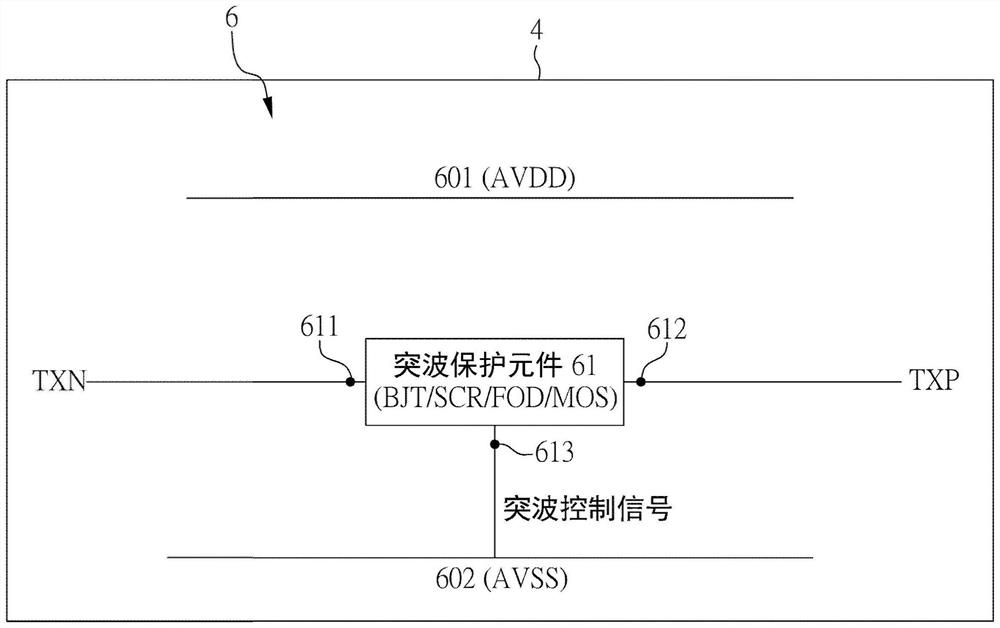

图10显示本发明的实施例2的芯片上突波保护电路6的电路图。

本发明的芯片上突波保护电路6存在于芯片4内部。突波保护电路6包括高压轨601(电压为AVDD)、低压轨602(电压为AVSS)、差分负发送端TXN、差分正发送端TXP、及突波保护元件61。

突波保护元件61包括第一端611、第二端612、及控制端613,分别连接至TXN、TXP、及602。优选地,第一端611与第二端612具有对称性。若第二端612的电压小于AVSS,且AVSS又小于第一端611的电压,则突波保护元件61将开启,使电流自第一端611流至第二端612。若第一端611的电压小于AVSS,且AVSS又小于第二端612的电压,则突波保护元件61亦将开启,使电流自第二端612流至第一端611。应该注意的是,电压的比较不只必须考虑到绝对值,还必须考虑到正负号。

就此而言,突波保护元件61例如是双极性结型晶体管、硅控整流器、场氧化层晶体管、或金属氧化物半导体场效晶体管,而不限于此。

本发明已理解到,突波S在TXN及TXP会分别引起差分负突波电压VTXN及差分正突波电压VTXP,而发生下列情形的任何一种:(情形1)VTXN小于AVSS,且AVSS又小于VTXP(亦即,VTXN<AVSS<VTXP);或(情形2)VTXP小于AVSS,且AVSS又小于VTXN(亦即,VTXP<AVSS<VTXN),恰可满足突波保护元件61的开启条件,而达成突波保护元件61的自动触发机制。

就更深层的理解而言,突波保护元件61的控制端613所连接的AVSS(即接地GND)俨然成为固有的突波控制信号。也就是说,本发明在理解到差分突波电压的特性的基础下,直接使用AVSS(即接地GND)作为突波控制信号,不需要如图3所示的突波侦测单元32(及其附带的偏压单元31)来特地产生特别控制信号EN。据此,可达成突波保护电路的简化。

(实施例3)

图11显示本发明的实施例3的芯片上突波保护电路6’的电路图。

图11的实施例3的芯片上突波保护电路6’是以图10的实施例2的芯片上突波保护电路6为基础来改良而成,除了原有的高压轨601(电压为AVDD)、低压轨602(电压为AVSS)、差分负发送端TXN、及差分正发送端TXP之外,还包括第一上拉(pull-up)元件621、第二上拉元件622、第一下拉(pull-down)元件623、及第二下拉元件624。

第一上拉元件621设置在高压轨601与TXN之间,第二上拉元件622设置在高压轨601与TXP之间,第一下拉元件623设置在TXN与低压轨602之间,而第二下拉元件624设置在TXP与低压轨602之间。第一上拉元件621、第二上拉元件622、第一下拉元件623、及第二下拉元件624例如是二极管、硅控整流器、双极性结型晶体管、或金属氧化物半导体场效晶体管,而不限于此。

在实施例3中,突波保护元件61可以寄生元件的形式来存在,而包括寄生路径。关于突波保护元件61的自动自我保护机制,特别是自动触发机制,请参考实施例2的说明。

(实施例4)

图12显示本发明的实施例4的芯片上突波保护电路5’的电路图。

图12的芯片上突波保护电路5’的电路图是以图8的芯片上突波保护电路5为基础来改良而成,图8的BJT 56在图12中已置换成广义的突波保护元件61,它例如是双极性结型晶体管、硅控整流器、场氧化层晶体管、或金属氧化物半导体场效晶体管。针对图12的元件已出现在图8者,则省略其说明。

图13A、图13B、图13C、及图13D分别显示本发明的实施例4的芯片上突波保护元件61在使用双极性结型晶体管、硅控整流器、场氧化层晶体管、或金属氧化物半导体场效晶体管时的具体接法。同时,亦显示突波保护元件61在电子装置上的相对位置。电子装置例如是电路板或数字用户回路。

电子装置包括一次侧变压器21、二次侧变压器22、回路元件27、及第一逻辑元件LD、及第二逻辑元件LNA。TXN、TXP、RXP、及RXN都是芯片的接脚,前已叙及。本发明的突波保护元件61即是存在于TXN与TXP之间且整合于芯片内部。

归功于本发明关于差分突波的特性的考察,不需要设置额外突波侦测器,直接使用变压器21及22作为固有的突波侦测器,即可触发芯片4的自动自我保护机制。

图13A的突波保护元件61使用双极性结型晶体管,可参考图8的BJT56。

图13B的突波保护元件61使用两个硅控整流器614及615,第一硅控整流器611的阳极连接至TXP,其阴极连接至TXN,其栅极连接至低压轨52。第二硅控整流器612的阳极连接至TXN,其阴极连接至TXP,其栅极连接至低压轨52。

图13C的突波保护元件61使用场氧化层晶体管,其漏极连接至TXN,其源极连接至TXP,其基体(body)极连接至低压轨52。当然,根据金属氧化物半导体场效晶体管的对称性,漏极与源极可互换。

图13D的突波保护元件61使用金属氧化物半导体场效晶体管,其漏极连接至TXN,其源极连接至TXP,其栅极与基体极都连接至低压轨52。当然,根据金属氧化物半导体场效晶体管的对称性,漏极与源极可互换。

(测试结果)

在外部电阻261为0欧姆的情况下,将没有使用本发明的芯片上突波保护电路的芯片、及使用本发明的芯片上突波保护电路5的自动自我保护芯片4的效能进行比较。测试条件是设定成使用突波结合波产生器来产生开路电压波及短路电流波,并满足上述表1的规格1及表2的规格2。

实际测试结果(称为“silicon result”)显示,在外部电阻261为0欧姆的情况下,没有使用本发明的芯片上突波保护电路的芯片面对规格1的条件,只可承受电压为750V的突波;面对规格2的条件,只可承受电压为250V的突波。

优选地,使用本发明的芯片上突波保护电路5的自动自我保护芯片4面对规格1的条件,可承受甚高的电压,例如高达4kV的突波;面对规格2的条件,可承受甚高的电压,例如高达3.5kV-4kV的突波,其效能提升甚为明显,充分满足本发明所追求的足以承受1kV的突波的目的。

在本发明的一实施例中,BJT结构的形成,是在P型基板PSUB上形成P井PW;通过两个氧化物OX1及OX2来形成三个岛部;进而在三个岛部上形成三个N+掺杂区N1、N2、及N3。N1连接至差分负发送端TXN,N2连接至差分正发送端TXP,而PSUB则可作为接地。BJT可视为存在于TXN、TXP、及PSUB之间,它由氧化物扩散(oxide diffusion,OD)二极管所形成。

图14显示本发明的一实施例的BJT结构7。

图14的BJT结构7的形成,是在P型基板PSUB上形成P井PW;在P井PW的两侧分别形成两个N井NWl及NW2,它们优选还包括深N井;在PW、NW1、及NW2上分别形成三个N+掺杂区N1、N2、及N3。N1连接至差分负发送端TXN,N2连接至差分正发送端TXP,而PSUB则可作为接地。BJT可视为存在于TXN、TXP、及PSUB之间,它由井二极管所形成。

可依照实际应用,来决定使用上述何种实施例的BJT结构。关于氧化物扩散二极管与(深)N型井二极管的电性特征,在二极管的击穿电压耐压方面,前者较弱,后者较强;在对付突波的效能评估方面,前者不佳,后者较佳。

(本发明的优点)

本发明的突波保护元件是“芯片上”(on-chip)元件,其设置在TXN、TXP、及GND之间。突波保护元件可通过TXN、TXP、及GND之间的差分电压差来泄放突波电流。优选地,突波保护元件可为寄生(parasitic)元件,其存在于TXN与TXP之间的电路布局(layout)。

本发明的一项优点是,降低成本,包括:节省板级(board-level)突波保护单元的费用及/或节省在供应板级突波保护单元上所需的束缚成本(bonding cost)。图15显示本发明的一实施例的电子装置2’的等效电路图,其中,外部电阻261及突波保护器262已免除(打叉表示省略)。

本发明的另一项优点是,免除突波侦测器及/或免除用于控制突波保护器的额外触发电路,而减少突波保护电路所占用的面积及/或降低突波保护电路的复杂度。这归功于,本发明由在系统(芯片)中固有的信号作为突波控制信号。图16显示本发明的一实施例的芯片上突波保护电路3’的电路图,其中,偏压单元31、突波侦测单元32、及特别控制信号EN已省略(打叉表示省略)。

最后,本发明的又一项优点是,达成芯片对付突波的自动自我保护机制,足以泄放高压能量。

尽管本发明已通过多个实施例来说明,应理解的是,只要不背离本发明的精神及权利要求所主张的,可作出许多其他可能的修饰及变化。

- 芯片上突波保护电路

- 突波保护电路及利用该突波保护电路的连接器与电子装置