一种具有自保护功能的推挽输出缓冲器

文献发布时间:2023-06-19 11:21:00

技术领域

本发明涉及电路保护技术领域,更具体的说是涉及一种具有自保护功能的推挽输出缓冲器。

背景技术

目前,推挽输出缓冲器由于其结构简单,带宽大,驱动能力强,在高压高速驱动放大器中有广泛的应用。

但是,在实际应用中,有一些极端情况导致器件损害。比如输出OUT端被短路到电源或者地,外界雷击浪涌灌入OUT端,OUT管脚对INP管脚静电放电等等。

因此,提供一种具有自保护功能的推挽输出缓冲器是本领域技术人员亟需解决的问题。

发明内容

有鉴于此,本发明提供了一种具有自保护功能的推挽输出缓冲器,通过控制单元感应干扰电压,控制阻断单元对输入信号进行阻断,保护电路元件的安全,且电容负载较小,对缓冲器频率影响低。

为了实现上述目的,本发明采用如下技术方案:

一种具有自保护功能的推挽输出缓冲器,包括:缓冲器,控制单元和阻断单元;

所述缓冲器通过所述阻断单元与输入端连接,所述控制单元与所述缓冲器、所述阻断单元和输出端连接。

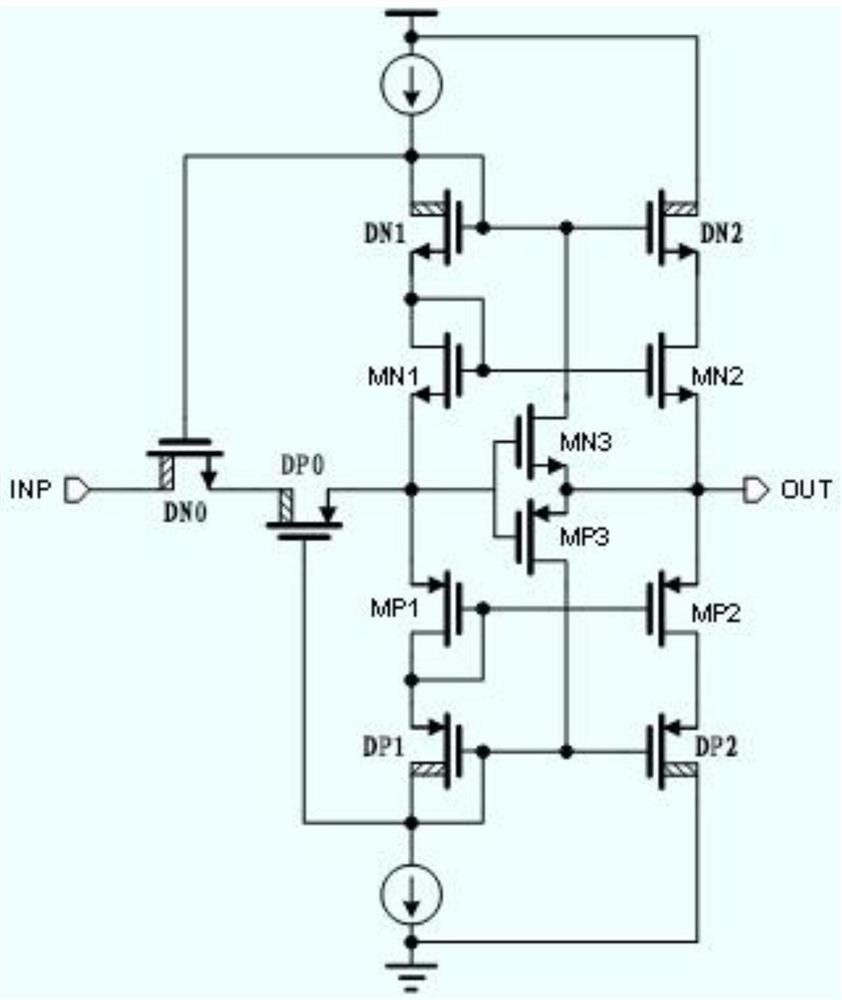

优选的,所述缓冲器的电路结构为:第一恒流源的一端接地,另一端与晶体管DN1的集电极相连,晶体管DN1的基极与晶体管DN2的基极相连,还与自身集电极相连,发射极与晶体管MN1的集电极相连,晶体管MN1的基极与晶体管MN2的基极相连,还与自身的集电极相连,发射极与晶体管MP1的发射极相连,晶体管MP1的基极与其自身的集电极相连,还与晶体管MP2的基极相连,集电极与晶体管DP1的发射极相连,晶体管DP1的基极与其自身的集电极相连,其还有晶体管DP2的基极相连,集电极与第二恒流源相连,第二恒流源接地;晶体管DN2的集电极接地,发射极与晶体管MN2的集电极相连,晶体管MN2的发射极与晶体管MP2的发射极相连,集电极与晶体管DP2的发射极相连,还与输出端连接,晶体管MP2的集电极与晶体管DP2的发射极相连,晶体管DP2的集电极通过第二恒流源接地。

优选的,所述控制单元的电路结构为:晶体管MN3的集电极与晶体管DN1的基极相连,基极与晶体管MP3的基极相连,还与晶体管MN1的集电极和阻断单元连接,发射极与晶体管MP3的发射极相连,还与输出端连接,晶体管MP3的集电极与晶体管DP1的基级连接。

优选的,所述阻断单元的电路结构为:晶体管DN0和晶体管DP0,晶体管DN0的基极与晶体管DN1的集电极相连,晶体管DP0的基极与晶体管DP1的集电极相连,其中一个晶体管的集电极与输入端相连,发射极与另一个晶体管的集电极相连,另一个晶体管的发射极与晶体管MN1的集电极相连。

优选的,晶体管为双极性晶体管或场效应晶体管。

经由上述的技术方案可知,与现有技术相比,本发明公开提供了一种具有自保护功能的推挽输出缓冲器,通过控制单元感应干扰电压,控制阻断单元对输入信号进行阻断,保护电路元件的安全,且电容负载较小,对缓冲器频率影响低。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

图1附图为本发明提供的电路结构示意图。

图2附图为本发明提供的控制单元电路结构示意图。

图3附图为本发明提供的阻断单元电路结构示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

本发明实施例公开了一种具有自保护功能的推挽输出缓冲器,包括:缓冲器,控制单元和阻断单元;

缓冲器通过阻断单元与输入端连接,控制单元与缓冲器、阻断单元和输出端连接。

为进一步优化上述技术方案,缓冲器的电路结构为:第一恒流源的一端接地,另一端与晶体管DN1的集电极相连,晶体管DN1的基极与晶体管DN2的基极相连,还与自身集电极相连,发射极与晶体管MN1的集电极相连,晶体管MN1的基极与晶体管MN2的基极相连,还与自身的集电极相连,发射极与晶体管MP1的发射极相连,晶体管MP1的基极与其自身的集电极相连,还与晶体管MP2的基极相连,集电极与晶体管DP1的发射极相连,晶体管DP1的基极与其自身的集电极相连,其还有晶体管DP2的基极相连,集电极与第二恒流源相连,第二恒流源接地;晶体管DN2的集电极接地,发射极与晶体管MN2的集电极相连,晶体管MN2的发射极与晶体管MP2的发射极相连,集电极与晶体管DP2的发射极相连,还与输出端连接,晶体管MP2的集电极与晶体管DP2的发射极相连,晶体管DP2的集电极接地。

为进一步优化上述技术方案,控制单元的电路结构为:晶体管MN3的集电极与晶体管DN1的基极相连,基极与晶体管MP3的基极相连,还与晶体管MN1的集电极和阻断单元连接,发射极与晶体管MP3的发射极相连,还与输出端连接,晶体管MP3的集电极与晶体管DP1的基级连接。

为进一步优化上述技术方案,阻断单元的电路结构为:晶体管DN0和晶体管DP0,晶体管DN0的基极与晶体管DN1的集电极相连,晶体管DP0的基极与晶体管DP1的集电极相连,其中一个晶体管的集电极与输入端相连,发射极与另一个晶体管的集电极相连,另一个晶体管的发射极与晶体管MN1的集电极相连。

为进一步优化上述技术方案,晶体管为双极性晶体管或场效应晶体管。

以场效应晶体管为例,进行说明:

第一部分,添加了一对互补MOS管MN3和MP3,分别是NMOS管和PMOS管。MN3和MP3的栅极均连接在输入端,源极都接到输出端。

第二部分,添加了一对高压DMOS管DN0和DP0,分别是高压NMOS和高压PMOS。DN0和DP0串联,并插入到输入端和缓冲器之间。DN0的栅极接MN3的漏极,DN0的漏极接输入输入端;DP0的栅极接MP3的漏极,DP0的源极接缓冲器的输入端。DN0的源极和DP0的漏极相接。

第三部分,MP3和MN3为低压CMOS器件,尺寸较小,对缓冲器引入的电容负载较小,进而对缓冲器的频率响应影响较小。

当缓冲器输出端遇到电压源型干扰下拉到地时,MN3管会打开将DN1的栅极下拉,进而DN0关断,高压管DN0可以隔离缓冲器和输入端,进而保护缓冲器。当缓冲器输出端遇到电压源型干扰上拉到电源时,MP3管会打开将DP1的栅极上拉,进而DP0关断,高压管DP0可以隔离缓冲器和输入端,同样保护缓冲器。

DN0开启电压为MN1栅源电压和DN1栅源电压之和,DP0开启电压为MP1栅源电压和DP1栅源电压之和。由于信号从输入端传输到缓冲器需要经过DN0和DP0的开启电阻,可以保证DN0和DP0有较低的开启阻抗,进而输入端到缓冲器输入端的传递函数的有较好的频率平坦度,并且开启电压不随信号变化,开启阻抗也跟输入信号无关,信号传递时线性度不受影响。

本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。对于实施例公开的装置而言,由于其与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

- 一种具有自保护功能的推挽输出缓冲器

- 一种具有自保护功能的LED灯恒流输出电路