发光元件

文献发布时间:2023-06-19 11:26:00

技术领域

本发明涉及一种发光元件,尤其涉及一种层叠多个发光层的发光元件。

背景技术

发光二极管作为无机光源,被多样地用于显示装置、车辆用灯具、一般照明等多种领域。发光二极管具有寿命长、功耗低且响应速度快的优点,因此正快速地替代现有光源。

尤其,显示装置通常利用蓝色、绿色及红色的混合色实现多样的颜色。显示装置的各个像素配备蓝色、绿色及红色的子像素,并且通过这些子像素的颜色来确定特定像素的颜色,并且通过这些像素的组合来实现图像。

发光二极管在显示装置中主要被用作背光源。然而,最近正在开发作为利用发光二极管直接实现图像的下一代显示器的微型LED(micro LED)。

发明内容

技术问题

本发明要解决的技术问题为提供一种提高了光效率的发光元件。

本发明要解决的技术问题并不局限于以上提到的技术问题,未提到的其他技术问题能够通过下文的记载而被本领域技术人员明确地理解。

技术方案

为了实现要解决的一技术课题,根据本发明的实施例的发光元件包括:第一发光部,包括第1-1型半导体层、第一活性层及第1-2型半导体层;第二发光部,布置于所述第一发光部上,并包括第2-1型半导体层、第二活性层及第2-2型半导体层;第三发光部,布置于所述第二发光部上,并包括第3-1型半导体层、第三活性层及第3-2型半导体层;第一导电图案,包括布置于所述第二发光部的内部并与所述第1-1型半导体层、第1-2型半导体层、第2-1型半导体层、第2-2型半导体层中的至少一个电连接的第一部分及从所述第一部分向所述第二发光部与所述第三发光部之间的第二发光部的一面延伸的第二部分;以及第二导电图案,布置于所述第三发光部并与所述第一导电图案电连接,其中,所述第二导电图案包括与所述第一导电图案的第二部分的至少一部分重叠的区域。

根据实施例,所述第二发光部可以具有贯通所述第二发光部的至少一部分的通孔,所述第一导电图案的第一部分沿所述通孔形成,所述通孔内部利用绝缘物质填充。

根据实施例,所述第三发光部可以具有贯通所述第三发光部的通孔,所述第二导电图案包括:第一部分,沿所述第三发光部的通孔布置;第二部分,从所述第二导电图案的第一部分向所述第三发光部的一面延伸,所述第一导电图案的第二部分与所述第二导电图案的第一部分部分重叠。

根据实施例,所述第一导电图案的第一部分与所述第二导电图案的第一部分可以具有相同的宽度。

根据实施例,所述发光元件还可以包括:垫,与所述第二导电图案的第二部分电连接。

根据实施例,所述第二发光部可以具有贯通所述第二发光部的至少一部分的通孔,所述第一导电图案的第一部分填充所述通孔。

根据实施例,所述第三发光部可以具有贯通所述第三发光部的通孔,所述第二导电图案包括:第一部分,填充所述第三发光部的通孔;第二部分,从所述第二导电图案的第一部分向所述第三发光部的一面上延伸,所述第一导电图案的第二部分与所述第二导电图案的第一部分包括重叠的至少一部分区域。

根据实施例,所述第一导电图案的第一部分与所述第二导电图案的第一部分可以具有相同的宽度。

根据实施例,所述发光元件还可以包括:垫,与所述第二导电图案的第二部分电连接。

根据实施例,所述第一导电图案的第一部分与所述第1-1型半导体层可以电连接,所述第一导电图案的第二部分在所述第二发光部的一面与所述第2-1型半导体层电连接,所述第二导电图案包括:第一部分,与所述第一导电图案的第二部分电连接;第二部分,从所述第二导电图案的第一部分延伸而与所述第3-1型半导体层电连接。

根据实施例,所述第一导电图案的第一部分与所述第1-2型半导体层可以电连接,所述第二导电图案包括:第一部分,与所述第一导电图案的第二部分电连接;第二部分,从所述第二导电图案的第一部分向所述第三发光部的一面延伸。

根据实施例,所述第一导电图案的第一部分与所述第2-2型半导体层可以电连接,所述第二导电图案包括:第一部分,与所述第一导电图案的第二部分电连接;第二部分,从所述第二导电图案的第一部分向所述第三发光部的一面延伸。

根据实施例,所述发光元件还可以包括:第三导电图案,与所述第3-2型半导体层电连接。

根据实施例,所述第三发光部可以具有贯通所述第三发光部的至少一部分的通孔,所述第三导电图案包括:第一部分,沿所述通孔布置;第二部分,从所述第三导电图案的第一部分向所述第三发光部的一面延伸。

根据实施例,所述发光元件还可以包括:垫,与所述第三导电图案的第二部分电连接。

根据实施例,所述第三发光部可以具有贯通所述第三发光部的至少一部分的通孔,所述第三导电图案包括:第一部分,填充所述通孔;第二部分,从所述第三导电图案的第一部分向所述第三发光部的一面延伸。

根据实施例,所述第一发光部至第三发光部分别可以具有倾斜的外侧壁。

根据实施例,所述发光元件还可以包括:绝缘膜,布置于所述第一导电图案的第一部分与所述第二发光部的侧面之间。

根据实施例,所述绝缘膜可以向所述第二发光部的外侧壁延伸。

根据实施例,所述发光元件还可以包括:第一粘结部,粘结所述第一发光部及第二发光部之间;以及第二粘结部,粘结所述第二发光部及第三发光部之间,其中,所述第一粘结部向所述第一发光部的外侧壁延伸,所述第二粘结部向所述第二发光部的外侧壁延伸。

根据实施例,所述发光元件还可以包括:绝缘膜,向所述第一导电图案的第一部分的外侧壁及所述第二发光部的外侧壁延伸,其中,所述绝缘膜布置于所述第二发光部与所述第二粘结部之间。

根据实施例,所述第一发光部及第二发光部分别可以具有倾斜的外侧壁,在所述第一发光部的外侧壁的侧面,所述第一粘结部具有从所述第一发光部向所述第二发光部方向逐渐变大的宽度,在所述第二发光部的外侧壁的侧面,所述第二粘结部具有从所述第二发光部向所述第三发光部方向逐渐变大的宽度。

其他实施例的具体事项包含在具体实施方式以及附图中。

有益效果

对于根据本发明的实施例的发光元件而言,在多个发光部分别形成通孔,并形成填充通孔内部的至少一部分且向各个发光部的一部分延伸的导电图案,从而相比于在发光部全部层叠之后一次形成通孔的情形,能够更稳定地电连接导电图案与第一垫、第二垫、第三垫及公共垫。

并且,多个发光部分别在形成通孔的期间进行元件分离,从而能够减轻施加到基板的拉张应力。

附图说明

图1a是用于说明根据本发明的一实施例的发光元件的平面图。

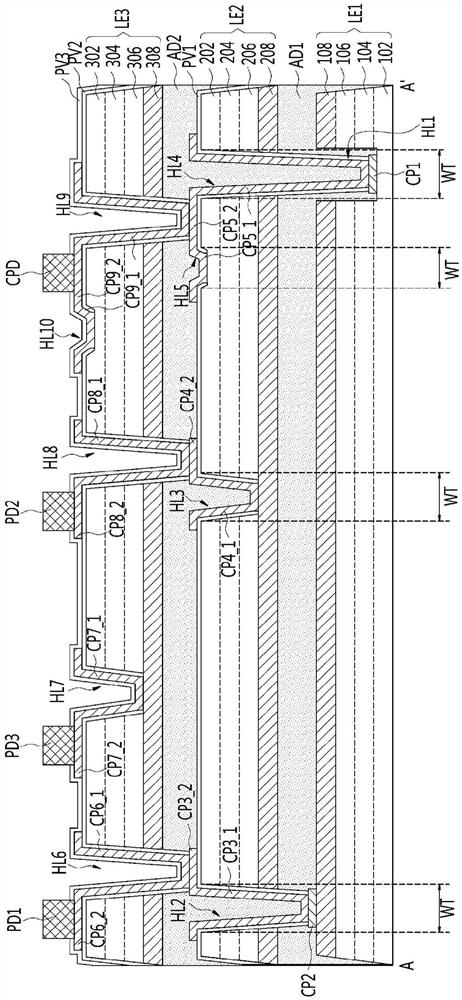

图1b及图1c是将图1a的发光元件沿A-A'截取的剖视图。

图2至图16是用于说明根据一实施例的发光元件的制造方法的剖视图。

图17及图18是用于说明将根据本发明的一实施例的发光元件贴装于贴装基板上的方法的剖视图。

最佳实施方式

为了充分理解本发明的构成及效果,参照附图对本发明的优选实施例进行说明。然而,本发明并不局限于以下公开的实施例,可以实现为多种形态,并且能够进行多样的变更。

并且,在本发明的实施例中使用的术语除非被另外定义,否则可以被解释为对相应技术领域中具有通常知识的人员通常已知的含义。

以下,参照附图对根据本发明的实施例的发光元件进行详细说明。

图1a是用于说明根据本发明的一实施例的发光元件的平面图,图1b及图1c是将图1a的发光元件沿A-A'截取的剖视图。

参照图1a至图1c,发光元件可以包括第一发光部LE1、第二发光部LE2及第三发光部LE3。

第一发光部LE1的一面可以与第二发光部LE2相向,第一发光部LE1的与一面相对的另一面是发光元件的光提取面。在第一发光部LE1的另一面为光提取面的情况下,从第一发光部LE1发出的光的波长可以最短,从第二发光部LE2发出的光的波长大于从第一发光部LE1发出的光的波长并小于从第三发光部LE3发出的光的波长,从第三发光部LE3发出的光的波长最长。例如,第一发光部LE1可以发出蓝色光,第二发光部LE2发出绿色光,第三发光部LE3发出红色光。

在又一实施例中,第一发光部LE1和第二发光部LE2的层叠顺序可以与上述的实施例不同。例如,虽然在上述的实施例中第二发光部LE2层叠于第一发光部LE1上,但是与此不同地,第一发光部LE1可以层叠于第二发光部LE2上。因此,第二发光部LE2的一面可以与第一发光部LE1相向,第二发光部LE2的与一面相对的另一面是发光元件的光提取面。

第一发光部LE1可以包括垂直层叠的第一n型半导体层102、第一活性层104、第一p型半导体层106及第一欧姆层108。第二发光部LE2可以包括垂直层叠的第二欧姆层208、第二p型半导体层206、第二活性层204及第二n型半导体层202。第三发光部LE3可以包括垂直层叠的第三欧姆层308、第三p型半导体层306、第三活性层304及第三n型半导体层302。

第一n型半导体层102、第二n型半导体层202及第三n型半导体层302分别可以是掺杂有Si的氮化镓系半导体层。第一p型半导体层106、第二p型半导体层206及第三p型半导体层306分别可以是掺杂有Mg的氮化镓系半导体层。第一活性层104、第二活性层204及第三活性层304分别可以包括多量子阱结构(Multi Quantum Well:MQW),并且可以确定其组成比以发出所期望的峰值波长的光。第一欧姆层108、第二欧姆层208及第三欧姆层308各自可以使用氧化锡(SnO)、氧化铟(InO

发光元件还可以包括:第一导电图案CP1,与通过第一发光部LE1的孔暴露的第一n型半导体层102电接触;第二导电图案CP2,与第一欧姆层108电接触。第一导电图案CP1及第二导电图案CP2各自可以包括选自由Au、Ag、Ni、Al、Rh、Pd、Ir、Ru、Mg、Zn、Pt、Hf、Cr、Ti及Cu构成的组中的至少一种。并且,可以包括上述物质的合金。选择性地,第一导电图案CP1及第二导电图案CP2可以省略。

第一发光部LE1可以与第二发光部LE2隔开布置。作为一例,第一发光部LE1的第一欧姆层108与第二发光部LE2的第二欧姆层208可以相向布置。作为另一例,第一发光部LE1的第一欧姆层108与第二发光部LE2的第二n型半导体层202可以相向布置。

发光单元还可以包括在第一发光部LE1与第二发光部LE2之间粘结第一发光部LE1与第二发光部LE2之间的第一粘结部AD1。第一粘结部AD1可以是透明的,具有绝缘性,并且具有粘结特性。第一粘结部AD1可以包括玻璃(glass)、聚合物(polymer)、抗蚀剂(resist)或聚酰亚胺(polyimide)。例如,第一粘结部AD1可以包括旋涂玻璃(SOG:Spin-On-Glass)、苯并环丁二烯(BCB:benzocycloButadiene)、氢倍半硅氧烷(HSQ:HydrogenSilsesQuioxanes)、聚甲基丙烯酸甲酯(PMMA:polymethylmethacrylate)、聚对二甲苯或SU-8光刻胶(photoresist)等。根据一实施例,第一粘结部AD1可以填充第一发光部LE1的第一孔HL1的内部而布置。

根据一实施例,第一发光部LE1可以具有倾斜的侧面而使宽度越向下方越大。即,第一发光部LE1的第一n型半导体层102可以具有大于第一活性层104的宽度,第一活性层104可以具有大于第一p型半导体层106的宽度,第一p型半导体层106可以具有大于第一欧姆层108的宽度。第一粘结部AD1可以延伸为包围第一发光部LE1的外侧壁。

选择性地,发光元件还可以包括布置于第一发光部LE1与第二发光部LE2之间的第一滤色器。作为一例,第一滤色器可以布置于第一发光部LE1的第一欧姆层108上。作为另一例,第一滤色器可以布置于第二发光部LE2的第二欧姆层208上。第一滤色器可以反射从第一发光部LE1发出的光,并使从第二发光部LE2及第三发光部LE3分别发出的光透射,使得从第一发光部LE1发出的光不对第二发光部LE2及第三发光部LE3分别造成影响。第一滤色器可以包括具有交替层叠TiO

第二发光部LE2可以包括:第二孔HL2,贯通第二发光部LE2及第一粘结部AD1而使第二导电图案CP2暴露;第三孔HL3,使第二发光部LE2的第二欧姆层208暴露;第四孔HL4,贯通第二发光部LE2及第一粘结部AD1而使第一导电图案CP1暴露。作为一例,第二发光部LE2还可以包括蚀刻第二n型半导体层202的一部分而使第二n型半导体层202暴露的第五孔HL5。第五孔HL5可以选择性地形成,并且可以根据情况省略。

选择性地,在省略第一导电图案CP1及第二导电图案CP2的情况下,第二孔HL2可以使第一欧姆层108的一部分暴露,第四孔HL4可以在第一孔HL1内使第一n型半导体层102的一部分暴露。

根据一实施例,第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5分别可以具有宽度越向下方越小的倾斜的侧面。第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5各自的宽度WT可以具有实质相同的大小。此时,孔的宽度WT表示孔的最大宽度。例如,第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5各自的宽度WT可以是发光元件大小的1/10左右。

发光元件还可以包括:第三导电图案CP3,填充第二孔HL2的至少一部分并与第二导电图案CP2电接触,且向第二发光部LE2的上部延伸;第四导电图案CP4,填充第三孔HL3的至少一部分并与第二欧姆层208电接触,且向第二发光部LE2的上部延伸;第五导电图案CP5,填充第四孔HL4及第五孔HL5的至少一部分并与第一导电图案CP1电接触,且向第二发光部LE2的上部延伸。第三导电图案CP3、第四导电图案CP4及第五导电图案CP5各自可以包括选自由Au、Ag、Ni、Al、Rh、Pd、Ir、Ru、Mg、Zn、Pt、Hf、Cr、Ti及Cu构成的组中的至少一种。并且,可以包括上述物质的合金。

选择性地,在省略第一导电图案CP1及第二导电图案CP2的情况下,第三导电图案CP3可以与在第二孔HL2底面暴露的第一欧姆层108电接触,第五导电图案CP5可以与在第四孔HL4底面暴露的第一n型半导体层102电接触。

根据图1b所示的一实施例,第三导电图案CP3可以未完全地埋设第二孔HL2,而沿第二孔HL2的内侧壁较薄地共形(conformally)形成。第三导电图案CP3可以包括:第一部分CP3_1,布置于第二孔HL2;第二部分CP3_2,从第一部分CP3_1向第二发光部LE2的上部面延伸。第四导电图案CP4可以未完全地埋设第三孔HL3,而沿第三孔HL3的内侧壁较薄地共形形成。第四导电图案CP4可以包括:第一部分CP4_1,布置于第三孔HL3;第二部分CP4_2,从第一部分CP4_1向第二发光部LE2的上部面延伸。第五导电图案CP5可以未完全地分别埋设第四孔HL4及第五孔HL5,而沿第四孔HL4及第五孔HL5各自的内侧壁较薄地共形形成。第五导电图案CP5可以包括:第一部分CP5_1,分别布置于第四孔HL4及第五孔HL5;第二部分CP5_2,连接第一部分CP5_1并从第一部分向第二发光部LE2的上部面延伸。作为一例,第五导电图案CP5的第二部分CP5_2可以布置于第四孔HL4与第五孔HL5之间,但是并不局限于此。

根据图1c所示的另一实施例,第三导电图案CP3可以包括:第一部分CP3_1,埋设第二孔HL2;第二部分CP3_2,从第一部分CP3_1延伸并沿第二发光部LE2的上部面延伸。第四导电图案CP4可以包括:第一部分CP4_1,埋设第三孔HL3;第二部分CP4_2,从第一部分CP4_1延伸并沿第二发光部LE2的上部面延伸。第五导电图案CP5可以包括:第一部分CP5_1,分别埋设第四孔HL4及第五孔HL5;第二部分CP5_2,连接第一部分CP5_1,并从第一部分CP5_1向第二发光部LE2的上部面延伸。

发光元件还可以包括:第一钝化膜PV1(或者,也称为“绝缘膜”),在第三导电图案CP3与第二孔HL2之间包围第三导电图案CP3的外侧壁,在第四导电图案CP4与第三孔HL3之间包围第四导电图案CP4的外侧壁,在第五导电图案CP5与第四孔HL4及第五孔HL5之间包围第五导电图案CP5的外侧壁,并且向第二发光部LE2的上部面延伸,从而使第三导电图案CP3、第四导电图案CP4及第五导电图案CP5与第二发光部LE2绝缘。第一钝化膜PV1可以包括选自由SiN

根据一实施例,第二发光部LE2可以具有倾斜的侧面以使宽度越向下方越大。即,第二发光部LE2的第二欧姆层208可以具有大于第二p型半导体层206的宽度,第二p型半导体层206可以具有大于第二活性层204的宽度,第二活性层204可以具有大于第二n型半导体层202的宽度。第二粘结部AD2可以延伸为包围第二发光部LE2的外侧壁。并且,第一钝化膜PV1可以布置于第二发光部LE2的外侧壁与第二粘结部AD2之间。在另一示例在中,可以在第二发光部LE2的外侧壁与第二粘结部AD2之间省略第一钝化膜PV1。

第二发光部LE2可以与第三发光部LE3隔开布置。作为一例,第二发光部LE2的第二n型半导体层202与第三发光部LE3的第三欧姆层308可以相向布置。作为另一例,第二发光部LE2的第二n型半导体层202与第三发光部LE3的第三n型半导体层302可以相向布置。

发光单元还可以包括在彼此隔开的第二发光部LE2及第三发光部LE3之间粘结第二发光部LE2与第三发光部LE3之间的第二粘结部AD2。第二粘结部AD2可以是透明的,具有绝缘性,并且具有粘结特性。第二粘结部AD2可以包括如玻璃、聚合物、抗蚀剂或聚酰亚胺等与第一粘结部AD1相同的物质。例如,第二粘结部AD2可以包括SOG、BCB、HSQ或SU-8光刻胶等。根据图1b所示的一实施例,第二粘结部AD2可以将形成有第三导电图案CP3的第二孔HL2、形成有第四导电图案CP4的第三孔、形成有第五导电图案CP5的第四孔HL4及第五孔HL5的内部填充而布置。

另外,选择性地,发光元件还可以包括布置于第二发光部LE2与第三发光部LE3之间的第二滤色器。作为一例,第二滤色器可以布置于第三欧姆层308上。第二滤色器可以反射分别从第一发光部LE1及第二发光部LE2发出的光,并使从第三发光部LE3发出的光透射,使得分别从第一发光部LE1及第二发光部LE2发出的光不对第三发光部LE3造成影响。第二滤色器可以包括具有交替层叠TiO

第三发光部LE3可以包括:第六孔HL6,贯通第三发光部LE3及第二粘结部AD2而使第三导电图案CP3暴露;第七孔HL7,使第三发光部LE3的第三欧姆层308暴露;第八孔,贯通第三发光部LE3及第二粘结部AD2而使第四导电图案CP4暴露;第九孔,贯通第三发光部LE3及第二粘结部AD2而使第五导电图案CP5暴露。作为一例,第三发光部LE3还可以包括蚀刻第三n型半导体层302的一部分而使第三n型半导体层302暴露的第十孔HL10。第十孔HL10可以选择性地形成,并且可以根据情况省略。

第六孔HL6可以使第三导电图案CP3的第二部分CP3_2暴露,第八孔HL8可以使第四导电图案CP4的第二部分CP4_2暴露,第九孔HL9可以使第五导电图案CP5的第二部分CP5_2暴露。如图所示,第三导电图案CP3的第二部分CP3_2、第四导电图案CP4的第二部分CP4_2及第五导电图案CP5的第二部分CP5_2分别可以在第二发光部LE2的上部面延伸而位于同一平面。因此,第六孔HL6、第八孔HL8及第九孔HL9分别可以具有实质相同的高度(height)。

根据一实施例,第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10分别可以具有宽度越向下方越小的倾斜的侧面。第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10各自的宽度WT可以具有实质相同的大小。并且,第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10各自的宽度WT可以与第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5各自的宽度WT实质相同。例如,第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10各自的宽度WT可以是发光元件大小的1/10左右。

发光元件还可以包括:第六导电图案CP6,填充第六孔HL6的至少一部分并与第三导电图案CP3的第二部分电接触,且向第三发光部LE3的上部延伸;第七导电图案CP7,填充第七孔HL7的至少一部分并与第三欧姆层308电接触,且向第三发光部LE3的上部延伸;第八导电图案CP8,填充第八孔HL8的至少一部分并与第四导电图案CP4的第二部分电接触,且向第三发光部LE3的上部延伸;第九导电图案CP9,填充第九孔HL9及第十孔HL10各自的至少一部分并与第五导电图案CP5电接触,且向第三发光部LE3的上部延伸。第六导电图案CP6、第七导电图案CP7、第八导电图案CP8及第九导电图案CP9各自可以包括选自由Au、Ag、Ni、Al、Rh、Pd、Ir、Ru、Mg、Zn、Pt、Hf、Cr、Ti及Cu构成的组中的至少一种。并且,可以包括上述物质的合金。

根据一实施例,第六导电图案CP6可以与第三导电图案CP3电连接,第三导电图案CP3可以与第二导电图案CP2电连接,第二导电图案CP2可以与第一欧姆层108电连接。据此,第六导电图案CP6可以与第一发光部LE1的第一欧姆层108电连接。第七导电图案CP7可以与第三发光部LE3的第三欧姆层308电连接。第八导电图案CP8可以与第四导电图案CP4电连接,第四导电图案CP4可以与第二欧姆层208电连接。据此,第八导电图案CP8可以与第二发光部LE2的第二欧姆层208电连接。第九导电图案CP9可以与第三n型半导体层302及第五导电图案CP5电连接,第五导电图案CP5可以与第二n型半导体层202及第一导电图案CP1电连接,第一导电图案CP1可以与第一n型半导体层102电连接。据此,第九导电图案CP9可以共同电连接第一n型半导体层102、第二n型半导体层202及第三n型半导体层302。

根据图1b所示的一实施例,第六导电图案CP6可以未完全地埋设第六孔HL6,而沿第六孔HL6的内侧壁较薄地共形形成。第六导电图案CP6可以包括:第一部分CP6_1,布置于第六孔HL6;第二部分CP6_2,从第一部分CP6_1向第三发光部LE3的上部面延伸。第七导电图案CP7可以未完全地埋设第七孔HL7,而沿第七孔HL7的内侧壁较薄地共形形成。第七导电图案CP7可以包括:第一部分CP7_1,布置于第七孔HL7;第二部分CP7_2,从第一部分CP7_1向第三发光部LE3的上部面延伸。第八导电图案CP8可以未完全地埋设第八孔HL8,而沿第八孔HL8的内侧壁较薄地共形形成。第八导电图案CP8可以包括:第一部分CP8_1,布置于第八孔HL8;第二部分CP8_2,从第一部分CP8_1向第三发光部LE3的上部面延伸。第九导电图案CP9可以未完全地埋设第九孔HL9及第十孔HL10,而沿第九孔HL9及第十孔HL10的内侧壁较薄地共形形成。第九导电图案CP9可以包括:第一部分CP9_1,布置于第九孔HL9及第十孔HL10;第二部分CP9_2,在第一部分CP9_1之间连接第一部分CP9_1并向第三发光部LE3的上部面延伸。第九导电图案CP9的第二部分CP9_2可以布置于第九孔HL9与第十孔HL10之间,但是并不局限于此。

根据图1c所示的另一实施例,第六导电图案CP6可以包括:第一部分CP6_1,埋设第六孔HL6;第二部分CP6_2,从第一部分CP6_1延伸并沿第三发光部LE3的上部面延伸。第七导电图案CP7可以包括:第一部分CP7_1,埋设第七孔HL7;第二部分CP7_2,从第一部分CP7_1延伸并沿第三发光部LE3的上部面延伸。第八导电图案CP8可以包括:第一部分CP8_1,埋设第八孔HL8;第二部分CP8_2,从第一部分CP8_1延伸并沿第三发光部LE3的上部面延伸。第九导电图案CP9可以包括:第一部分CP9_1,分别埋设第九孔HL9与第十孔HL10;第二部分CP9_2,连接第一部分CP9_1,并从第一部分CP9_1延伸。

发光元件还可以包括:第二钝化膜PV2,在第六导电图案CP6与第六孔HL6之间包围第六导电图案CP6的外侧壁,在第七导电图案CP7与第七孔HL7之间包围第七导电图案CP7的外侧壁,在第八导电图案CP8与第八孔HL8之间包围第八导电图案CP8的外侧壁,在第九导电图案CP9与第九孔HL9及第十孔HL10之间包围第九导电图案CP9的外侧壁,并且向第三发光部LE3的上部面延伸,从而使第六导电图案CP6、第七导电图案CP7、第八导电图案CP8及第九导电图案CP9与第三发光部LE3绝缘。第二钝化膜PV2可以包括与第一钝化膜PV1相同的物质,例如,可以包括选自由SiN

根据一实施例,第三发光部LE3可以具有倾斜的侧面以使宽度越向下方越大。即,第三发光部LE3的第三欧姆层308可以具有大于第三p型半导体层306的宽度,第三p型半导体层306可以具有大于第三活性层304的宽度,第三活性层304可以具有大于第三n型半导体层302的宽度。第二钝化膜PV2可以延伸为包围第三发光部LE3的外侧壁。

发光元件还可以包括:第一垫PD1,在与第一欧姆层108电连接的第六导电图案CP6上与第六导电图案CP6电接触;第二垫PD2,在与第二欧姆层208电连接的第八导电图案CP8上与第八导电图案CP8电接触;第三垫PD3,在与第三欧姆层308电连接的第七导电图案CP7上与第七导电图案CP7电接触;公共垫CPD,和与第一n型半导体层102、第二n型半导体层202及第三n型半导体层302电连接的第九导电图案CP9电接触。第一垫PD1、第二垫PD2、第三垫PD3及公共垫CPD分别可以包括选自由Au、Ag、Ni、Al、Rh、Pd、Ir、Ru、Mg、Zn、Pt、Hf、Cr、Ti及Cu构成的组中的至少一种。并且,可以包括上述列举的物质的合金。

根据一实施例,从平面上观察,在发光元件具有四边形结构的情况下,第一垫PD1、第二垫PD2、第三垫PD3及公共垫CPD分别可以布置于发光元件的各个边角部位。作为一例,第一垫PD1可以布置于第一边角CN1,第二垫PD2可以布置于第三边角CN3,第三垫PD3可以布置于第二边角CN2,公共垫CPD可以布置于第四边角CN4。

并且,发光元件还可以包括:第三钝化膜PV3,在第三发光部LE3上覆盖除了第一垫PD1、第二垫PD2、第三垫PD3及公共垫CPD之外的其他部分。第三钝化膜PV3可以包括与第一钝化膜PV1或第二钝化膜PV2相同的物质,例如,包括选自由SiN

作为图1b所示的一例,第三钝化膜PV3可以以未完全埋设形成有第六导电图案CP6、第七导电图案CP7、第八导电图案CP8及第九导电图案CP9的第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10的方式共形形成于第二钝化膜PV2上。与此不同地,第三钝化膜PV3也可以填充形成有第六导电图案CP6、第七导电图案CP7、第八导电图案CP8及第九导电图案CP9的第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10而形成。

作为图1c所示的另一例,第三钝化膜PV3可以形成于第六导电图案CP6、第七导电图案CP7、第八导电图案CP8及第九导电图案CP9各自的上部面及第二钝化膜PV2上。

在如上所述的发光元件中,在第二发光部LE2及第一粘结部AD1可以形成有,使与第一欧姆层108电连接的第二导电图案CP2暴露的第二孔HL2、使第二欧姆层208暴露的第三孔HL3、使与第一n型半导体层102电连接的第一导电图案CP1暴露的第四孔HL4以及使第二n型半导体层202暴露的第五孔HL5,并且布置有填充第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5的至少一部分的第三导电图案CP3、第四导电图案CP4、第五导电图案CP5。并且,在第三发光部LE3及第二粘结部AD2可以形成有,使第三导电图案CP3暴露的第六孔HL6、使第三欧姆层308暴露的第七孔HL7、使第四导电图案CP4暴露的第八孔HL8、使第五导电图案CP5暴露的第九孔HL9以及使第三n型半导体层302暴露的第十孔HL10,并且布置有填充第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10的至少一部分的第六导电图案CP6、第七导电图案CP7、第八导电图案CP8及第九导电图案CP9。这样,在第二发光部LE2及第一粘结部AD1布置与第一发光部LE1电连接的导电图案,在第三发光部LE3及第二粘结部AD2额外布置与和第一发光部LE1电连接的导电图案电连接的导电图案。因此,第一垫PD1可以沿第六导电图案CP6通过第三导电图案CP3及第二导电图案CP2与第一欧姆层108稳定地电连接。第二垫PD2可以沿第八导电图案CP8通过第四导电图案CP4与第二欧姆层208稳定地电连接。第三垫PD3可以通过第七导电图案CP7与第三欧姆层308稳定地电连接。并且,公共垫CPD可以通过第九导电图案CP9与第三n型半导体层302稳定地电连接,沿第九导电图案CP9通过第五导电图案CP5与第二n型半导体层202稳定地电连接,沿第五导电图案CP5通过第一导电图案CP1与第一n型半导体层102稳定地电连接。

另外,发光元件在蓝宝石等基板进行工序,在进行工序期间产生拉张应力(tensile stress),从而发生基板的中心部位向下凹陷的弯曲现象,但是第一粘结部AD1及第二粘结部AD2可以减轻施加到基板的拉张应力。

并且,虽然将在后文的制造方法中进行详细的说明,但是在形成第一孔HL1的期间,第一发光部LE1进行元件分离,在形成第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5的期间,第二发光部LE2进行元件分离,在形成第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10的期间,第三发光部LE3进行元件分离,从而能够进一步减轻施加到基板的拉张应力。

具体实施方式

以下,对制造图1a及图1b的发光元件的方法进行说明。

图2至图16是用于说明根据一实施例的发光元件的制造方法的剖视图。

参照图2,可以在第一基板100上依次形成第一n型半导体层102、第一活性层104、第一p型半导体层106及第一欧姆层108,进而形成第一发光部LE1。

第一基板100作为能够使氮化镓系半导体层生长的基板,可以包括蓝宝石(Al

可以在第一基板100上利用金属有机化学气相沉积(MOCVD:Metal-OrganicChemical Vapor Deposition)、分子束外延(MBE:Molecular Beam Epitaxy)、氢化物气相外延(HVPE:Hydride Vapor Phase Epitaxy)、金属有机氯化物(MOC:Metal-OrganicChloride)等生长方法依次形成第一n型半导体层102、第一活性层104及第一p型半导体层106。

在第一p型半导体层106上可以通过化学气相沉积(CVD:Chemical VaporDeposition)、物理气相沉积(PVD:Physical Vapour Deposition)工序等形成第一欧姆层108。

参照图3,可以对第一欧姆层108、第一p型半导体层106、第一活性层104进行蚀刻而在第一发光部LE1形成第一孔HL1。蚀刻工序也可以对第一n型半导体层102上部的一部分进行蚀刻。

形成第一孔HL1,并对第一欧姆层108、第一p型半导体层106、第一活性层104及第一n型半导体层102进行蚀刻,进而可以对第一发光部LE1进行元件分离。

如上所述,通过对第一发光部LE1进行元件分离,能够减小施加到基板的拉张应力。

参照图4,在第一发光部LE1可以分别形成第一导电图案CP1及第二导电图案CP2。第一导电图案CP1可以在第一孔HL1内部与第一发光部LE1隔开形成。第二导电图案CP2可以形成于第一欧姆层108上。

作为一例,在沿形成有第一孔HL1的第一发光部LE1的上部面形成导电膜之后,可以通过常规的图案化工序分别形成第一导电图案CP1及第二导电图案CP2。

参照图5,可以在第二基板200上依次形成第二n型半导体层202、第二活性层204、第二p型半导体层206及第二欧姆层208,进而形成第二发光部LE2。

第二基板200作为能够使氮化镓系半导体层生长的基板,可以包括蓝宝石(Al

可以在第二基板200上利用MOCVD、MBE、HVPE、MOC等生长方法依次形成第二n型半导体层202、第二活性层204及第二p型半导体层206。

可以在第二p型半导体层206上通过CVD、PVD工序等形成第二欧姆层208。

参照图6,可以翻转第二基板200而使第一发光部LE1的第一欧姆层108与第二发光部LE2的第二欧姆层208相向布置,并且通过第一粘结部AD1粘结第一发光部LE1及第二发光部LE2。

作为一例,可以在第一发光部LE1上以埋设形成有第一导电图案CP1的第一孔HL1的方式形成第一粘结部AD1,并且在第一欧姆层108上相向地布置第二欧姆层208之后,通过热工序固化第一粘结部AD1而粘结第一发光部LE1及第二发光部LE2。

此时,第一发光部LE1的侧面被第一粘结部AD1包裹,第一粘结部AD1可以是保护第一发光部LE1的侧面的保护层。

在通过第一粘结部AD1粘结第一发光部LE1及第二发光部LE2之后,第二基板200可以通过激光剥离(LLO:Laser Lift-Off)工序去除。

参照图7,可以对第二发光部LE2及第一粘结部AD1进行蚀刻,从而形成使第二导电图案CP2暴露的第二孔HL2、使第二欧姆层208暴露的第三孔HL3、使第一导电图案CP1暴露的第四孔HL4以及使第二n型半导体层202的一部分暴露的第五孔HL5。选择性地,可以不形成第五孔HL5。

第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5分别可以具有彼此相同的宽度WT。并且,第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5分别可以具有宽度越向下方越小的倾斜的侧面。

在形成第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5的期间,可以对第二n型半导体层202、第二活性层204、第二p型半导体层206及第二欧姆层208进行蚀刻,进而对第二发光部LE2进行元件分离。

这样,通过对第二发光部LE2进行元件分离,能够减小施加到基板的拉张应力。并且,第二发光部LE2具有侧面呈锥形的形态。换句话而言,第二发光部LE2具有截面积从基板开始越向上部方向越小的形状。

参照图8,可以沿第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5的内侧壁及第二n型半导体层202的上部面形成第一钝化膜PV1。

作为一例,可以以不完全埋设第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5的方式,在形成有第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5的第二发光部LE2及第一粘结部AD1上共形形成第一钝化膜PV1。此时,第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5分别具有倾斜的侧面,从而能够易于共形形成第一钝化膜PV1。接着,可以去除形成于第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5各自的底面的第一钝化膜PV1。

第一钝化膜PV1可以残留于第二发光部LE2的外侧壁。与此不同地,第一钝化膜PV1可以从第二发光部LE2的外侧壁去除。

参照图9,可以分别形成将形成有第一钝化膜PV1的第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5各自的至少一部分填充的第三导电图案CP3、第四导电图案CP4及第五导电图案CP5。

作为一例,可以通过沉积工序以不完全埋设形成有第一钝化膜PV1的第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5的方式在第一钝化膜PV1上共形形成导电膜(未图示)。如上所述,第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5分别具有倾斜的侧面,从而能够易于共形形成第一导电膜。接着,第一导电膜可以分别形成:第三导电图案CP3,与第二导电图案CP2电连接并填充第二孔HL2的至少一部分;第四导电图案CP4,与第二欧姆层208电连接并填充第三孔HL3的至少一部分;以及第五导电图案CP5,与第一导电图案CP1电连接并填充第四孔HL4的至少一部分,而且与第二n型半导体层202电连接并填充第五孔HL5的至少一部分。

第三导电图案CP3可以包括:第一部分CP3_1,形成于第二孔HL2;第二部分CP3_2,从第一部分CP3_1向形成于第二n型半导体层202上的第一钝化膜PV1上延伸。第四导电图案CP4可以包括:第一部分CP4_1,形成于第三孔HL3;第二部分CP4_2,从第一部分CP4_1向形成于第二n型半导体层202上的第一钝化膜PV1上延伸。第五导电图案CP5可以包括:第一部分CP5_1,分别形成于第四孔HL4及第五孔HL5;第二部分CP5_2,连接第一部分CP5_1之间而向形成于第二n型半导体层202上的第一钝化膜PV1上延伸。

在本实施例中图示了第三导电图案CP3、第四导电图案CP4及第五导电图案CP5分别未完全埋设第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5而较薄地共形形成的情形而进行说明,但是第三导电图案CP3、第四导电图案CP4及第五导电图案CP5可以分别填充第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5而形成。

参照图10,可以在第三基板300上依次形成第三n型半导体层302、第三活性层304、第三p型半导体层306及第三欧姆层308,进而形成第三发光部LE3。

第三基板300作为能够使氮化镓系半导体层生长的基板,可以包括蓝宝石(Al

可以在第三基板300上利用MOCVD、MBE、HVPE、MOC等生长方法依次形成第三n型半导体层302、第三活性层304及第三p型半导体层306。

可以在第三p型半导体层306上通过CVD、PVD等形成第三欧姆层308。

参照图11,可以翻转第三基板300而使第二发光部LE2的第二n型半导体层202与第三发光部LE3的第三欧姆层308相向布置,并且通过第二粘结部AD2粘结第二发光部LE2及第三发光部LE3。

作为一例,可以在第二发光部LE2上以埋设形成有第三导电图案CP3、第四导电图案CP4及第五导电图案CP5的第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5的方式形成第二粘结部AD2,并且在第二n型半导体层202上相向地布置第三欧姆层308之后,通过热工序固化第二粘结部AD2而粘结第二发光部LE2及第三发光部LE3。

此时,第二发光部LE2的侧面可以被第二粘结部AD2包裹,第二粘结部AD2可以是保护第二发光部LE2侧面的保护层。

在通过第二粘结部AD2粘结第二发光部LE2及第三发光部LE3之后,第三基板300可以通过LLO工序去除。

参照图12,可以对第三发光部LE3及第二粘结部AD2进行蚀刻,从而形成使第三导电图案CP3的第二部分暴露的第六孔HL6、使第三欧姆层308暴露的第七孔HL7、使第四导电图案CP4的第二部分暴露的第八孔HL8、使第五导电图案CP5的第二部分暴露的第九孔HL9以及使第三n型半导体层302的一部分暴露的第十孔HL10。选择性地,可以不形成第十孔HL10。

第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10分别可以具有彼此相同的宽度WT。并且,第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10分别可以具有与第二孔HL2、第三孔HL3、第四孔HL4及第五孔HL5相同的宽度WT。并且,第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10分别可以具有宽度越向下方越小的倾斜的侧面。

在形成第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10的期间,可以对第三n型半导体层302、第三活性层304、第三p型半导体层306及第三欧姆层308进行蚀刻,进而对第三发光部LE3进行元件分离。

这样,通过对第三发光部LE3进行元件分离,能够减小施加到基板的拉张应力。

参照图13,可以沿第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10的内侧壁及第三n型半导体层302的上部面形成第二钝化膜PV2。

作为一例,可以以不完全埋设第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10的方式,在形成有第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10的第三发光部LE3及第二粘结部AD2上共形形成第二钝化膜PV2。此时,第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10分别具有倾斜的侧面,从而能够易于共形形成第二钝化膜PV2。接着,可以去除形成于第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10各自的底面的第二钝化膜PV2。

第二钝化膜PV2可以残留于第三发光部LE3的外侧壁。与此不同地,第二钝化膜PV2可以从第三发光部LE3的外侧壁去除。

参照图14,可以分别形成将形成有第二钝化膜PV2的第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10各自的至少一部分填充的第六导电图案CP6、第七导电图案CP7、第八导电图案CP8及第九导电图案CP9。

作为一例,可以以不完全埋设形成有第二钝化膜PV2的第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10的方式在第二钝化膜PV2上共形形成第二导电膜(未图示)。如上所述,第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10分别具有倾斜的侧面,从而能够易于共形形成第二导电膜。接着,第二导电膜可以通过常规的蚀刻工序分别形成:第六导电图案CP6,与第三导电图案CP3的第二部分CP3_2电连接并填充第六孔HL6的至少一部分;第七导电图案CP7,与第三欧姆层308电连接并填充第七孔HL7的至少一部分;第八导电图案CP8,与第四导电图案CP4的第二部分CP4_2电连接并填充第八孔HL8的至少一部分;以及第九导电图案CP9,与第五导电图案CP5的第二部分CP5_2电连接并填充第九孔HL9及第十孔HL10各自的至少一部分。

第六导电图案CP6可以包括:第一部分CP6_1,形成于第六孔HL6;第二部分CP6_2,从第一部分CP6_1向形成于第三n型半导体层302上的第二钝化膜PV2上延伸。第七导电图案CP7可以包括:第一部分CP7_1,形成于第七孔HL7;第二部分CP7_2,从第一部分CP7_1向形成于第三n型半导体层302上的第二钝化膜PV2上延伸。第八导电图案CP8可以包括:第一部分CP8_1,形成于第八孔HL8;第二部分CP8_2,从第一部分CP8_1向形成于第三n型半导体层302上的第二钝化膜PV2上延伸。第九导电图案CP9可以包括:第一部分CP9_1,分别形成于第九孔HL9及第十孔HL10;第二部分CP9_2,连接第一部分CP9_1之间而向形成于第三n型半导体层302上的第二钝化膜PV2上延伸。

在本实施例中图示了第六导电图案CP6、第七导电图案CP7、第八导电图案CP8及第九导电图案CP9分别未完全埋设第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10而较薄地共形形成的情形而进行说明,但是第六导电图案CP6、第七导电图案CP7、第八导电图案CP8及第九导电图案CP9可以分别填充第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10而形成。

参照图15,可以在第六导电图案CP6、第七导电图案CP7、第八导电图案CP8及第九导电图案CP9、第二钝化膜PV2上共形形成第三钝化膜PV3。第三钝化膜PV3可以未完全埋设形成有第六导电图案CP6、第七导电图案CP7、第八导电图案CP8及第九导电图案CP9的各个第六孔HL6、第七孔HL7、第八孔HL8、第九孔HL9及第十孔HL10而较薄地共形形成。

另外,在形成于第三发光部LE3的外侧壁的第二钝化膜PV2上可以形成第三钝化膜PV3。

参照图16,可以分别形成与第六导电图案CP6电连接的第一垫PD1、与第八导电图案CP8电连接的第二垫PD2、与第七导电图案CP7电连接的第三垫PD3以及与第九导电图案CP9电连接的公共垫CPD。

作为一例,可以蚀刻第三钝化膜PV3而形成使第六导电图案CP6的第二部分CP6_2暴露的第一开口OP1、使第八导电图案CP8的第二部分CP8_2暴露的第二开口OP2、使第七导电图案CP7的第二部分CP7_2暴露的第三开口OP3、以及使第九导电图案CP9的第二部分CP9_2暴露的第四开口OP4。

可以埋设第一开口OP1、第二开口OP2、第三开口OP3及第四开口OP4而在第三钝化膜PV3上形成第三导电膜(未图示)。第三导电膜可以通过常规的蚀刻工序分别形成:第一垫PD1,埋设第一开口OP1并与第六导电图案CP6电接触,进而与第一欧姆层108电连接;第二垫PD2,埋设第二开口OP2并与第八导电图案CP8电接触,进而与第二欧姆层208电连接;第三垫PD3,埋设第三开口OP3并与第七导电图案CP7电接触,进而与第三欧姆层308电连接;公共垫CPD,埋设第四开口OP4并与第九导电图案CP9电接触,进而与第三n型半导体层302、第二n型半导体层202及第一n型半导体层102共同电连接。

根据本实施例,可以在第二发光部LE2及第一粘结部AD1形成有,暴露与第一欧姆层108电连接的第二导电图案CP2的第二孔HL2、暴露第二欧姆层208的第三孔HL3、暴露与第一n型半导体层102电连接的第一导电图案CP1的第四孔HL4以及暴露第二n型半导体层202的第五孔HL5。在另一工序中,可以在第三发光部LE3及第二粘结部AD2形成有使第三导电图案CP3暴露的第六孔HL6、使第三欧姆层308暴露的第七孔HL7、使第四导电图案CP4暴露的第八孔HL8、使第五导电图案CP5暴露的第九孔HL9以及使第三n型半导体层302暴露的第十孔HL10。因此,若形成一次贯通第一发光部LE1、第二发光部LE2及第三发光部LE3的孔,则由于诸如横纵比(aspect ratio)等问题而导致关于蚀刻工序的问题较多,但是可以在第二发光部LE2及第一粘结部AD1执行一蚀刻工序,在第三发光部LE3及第二粘结部AD2执行另一蚀刻工序,从而能够克服上述的问题

并且,在第二发光部LE2及第一粘结部AD1可以布置与第一发光部LE1电连接的第三导电图案CP3、第四导电图案CP4及第五导电图案CP5,在第三发光部LE3及第二粘结部AD2可以另外布置电连接于与第一发光部LE1电连接的第三导电图案CP3、第四导电图案CP4及第五导电图案CP5的第六导电图案CP6、第七导电图案CP7、第八导电图案CP8及第九导电图案CP9。因此,第一垫PD1可以沿第六导电图案CP6通过第三导电图案CP3及第二导电图案CP2与第一欧姆层108稳定地电连接。第二垫PD2可以沿第八导电图案CP8通过第四导电图案CP4与第二欧姆层208稳定地电连接。第三垫PD3可以通过第七导电图案CP7与第三欧姆层308稳定地电连接。并且,公共垫CPD可以通过第九导电图案CP9与第三n型半导体层302稳定地电连接,沿第九导电图案CP9通过第五导电图案CP5与第二n型半导体层202稳定地电连接,沿第五导电图案CP5通过第一导电图案CP1与第一n型半导体层102稳定地电连接。

以下,对将在图2至图16中说明的发光元件贴装于贴装基板上的方法进行说明。

图17及图18是用于说明将根据本发明的一实施例的发光元件贴装于贴装基板上的方法的剖视图。

参照图17,可以将通过图2至图16形成的多个发光元件LED贴装到目标贴装基板MB上。在贴装基板MB可以形成有分别与第一垫PD1、第二垫PD2、第三垫PD3及公共垫CPD电粘结的接合垫BPD。在接合垫BPD上可以分别形成有粘结球BL。各个粘结球BL可以包括In、Au、Sn、Cu等。与此不同地,粘结球BL可以分别形成于第一垫PD1、第二垫PD2、第三垫PD3及公共垫CPD。

接合垫BPD及粘结球BL可以与贴装发光元件LED的位置对应地形成。

可以翻转形成有多个发光元件LED的第一基板100,进而使发光元件LED与形成有接合垫BPD的贴装基板MB相向布置。

在翻转后的第一基板100上的对应于要从第一基板100分离的发光元件LED的位置可以提供具有能够使激光透射的孔的掩模图案MSK。

参照图18,可以利用掩模图案MSK对第一基板100选择性地执行激光剥离(selective LLO)工序,从而将布置于贴装基板MB的目标贴装位置的发光元件LED从第一基板100分离。在向所述第一基板100照射激光而将发光元件LED从第一基板100分离的情况下,通过在第一基板100上设置掩模图案MSK,能够更准确地向要从第一基板100分离的发光元件LED执行激光照射。但是,若能够适当地向要分离的发光元件LED照射激光,则掩模图案MSK可以省略。

分离的发光元件LED之间的间隔距离可以根据贴装基板MB而改变。

分离的发光元件LED各自的第一垫PD1、第二垫PD2、第三垫PD3及公共垫CPD分别可以与形成于接合垫BPD上的粘结球BL粘结。据此,可以将发光元件LED贴装于贴装基板MB。

若发光元件LED全部贴装于目标位置,则可以不额外执行去除第一基板100的工序而从发光元件LED分离第一基板100。

以上,虽然参照附图对本发明的实施例进行了说明,但是在本发明所属技术领域中具有通常知识的人员可以理解本发明能够在不改变其技术思想或必要特征的情况下实施为其他具体的形态。因此,应该理解以上所述的实施例在所有方面均为示意性而并非限定性的。

- 发光元件用组合物、发光元件用组合物的制造方法、发光元件用组合物的评价方法、发光元件和发光元件的制造方法

- 发光材料和使用其的有机发光元件、波长变换发光元件、光变换发光元件、有机激光二极管发光元件、色素激光器、显示装置以及照明装置