一种低触发电压的SCR器件及其制备方法

文献发布时间:2023-06-19 11:54:11

技术领域

本发明涉及半导体保护器件领域,具体涉及一种静电放电保护器件,尤其涉及一种低触发电压的SCR器件及其制备方法。

背景技术

可控硅器件(Silicon Controlled Rectifier,SCR)在功率器件中广泛应用,由于它可以在高阻态和低阻态之间切换,因此可以被用作电源开关,同时也是一种常用于静电放电(Electro-Static Discharge,ESD)防护的器件,具有极好地释放静电的能力。与二极管、三极管以及场效应晶体管相比,自身的正反馈机制使得可控硅器件具有电流泄放能力强、单位面积泄放效率高、导通电阻小、鲁棒性强、防护级别高等优点,能够在半导体平面工艺上,以较小的芯片面积达成较高的静电防护等级。

触发电压是指可控硅器件开启时需要的最小电压。一般普通的可控硅器件具有较高的触发电压,其触发电压很可能大于工作电压较低的电路的所承受的电压极限。所以对于工作电压较低的电路,为了保护其在可控硅器件开启并泄放电流之前不被损坏,应该使用触发电压尽可能低的可控硅器件来保护工作电压较低的电路,因此针对以上问题,迫切需要设计出一种低触发电压的SCR器件及其制备方法,以满足实际使用的需要。

发明内容

针对现有技术中存在的上述问题,现提供一种低触发电压的SCR器件及其制备方法,其触发电压较低,静电泄放能力强、稳定性和可靠性较佳。

本发明所解决的技术问题可以采用以下技术方案来实现:

本发明提供一种低触发电压的SCR器件,包括:

一衬底;

一外延层,形成于所述衬底的上表面,所述外延层中包括:

一第一P型掺杂区,所述第一P型掺杂区中包括第一N型注入区、第二N型注入区;

一第一N型掺杂区,所述第一N型掺杂区中包括第三N型注入区、第一P型注入区;

一第二P型掺杂区,所述第二P型掺杂区中包括第四N型注入区、第三P型注入区;

第二N型掺杂区,所述第二N型掺杂区中包括第五N型注入区、第四P型注入区;

第二P型注入区,所述第二P型注入区与所述第一N型掺杂区、所述第二P型掺杂区耦接;

隔离结构,所述隔离结构纵向的自所述外延层的上表面贯穿所述外延层至所述衬底中,所述第一P型掺杂区被所述隔离结构隔离;

一介质层,形成于所述外延层的上表面;

多个金属层,分别形成于每个N型注入区和P型注入区的上方;

多条金属连线,用以使所述第一N型注入区、所述第三N型注入区、所述第一P型注入区、所述第五N型注入区和所述第四P型注入区相连接并引出作为所述器件的阳极,所述第四N型注入区和所述第三P型注入区相连接并引出作为所述器件的阴极,所述第二N型注入区和所述第二P型注入区相连接。

优选地,所述外延层的电阻率大于所述衬底的电阻率。

优选地,所述第一P型掺杂区的注入元素为硼,离子注入剂量为5E12~5E13每平方厘米,注入能量60~100KeV;

所述第二P型掺杂区的注入元素为硼,离子注入剂量为5E14~8E14每平方厘米,注入能量40~60KeV;

所述第一N型掺杂区和所述第二N型掺杂区的注入元素为磷,离子注入剂量为5E13~1E14每平方厘米,注入能量60~80KeV。

优选地,每个所述N型注入区的注入元素为磷或砷,离子注入剂量为1E15~1E16每平方厘米,注入能量为80~100KeV,于离子注入后进行热退火,热退火温度为850℃~950℃,时间为30~60分钟。

优选地,所述第四N型注入区与所述第一N型掺杂区之间的距离,以及所述第四N型注入区与所述第二N型掺杂区之间的距离不超过6μm。

优选地,所述第一N型注入区和所述第二N型注入区之间的距离不超过5μm。

优选地,每个所述P型注入区的注入元素为硼或二氟化硼,离子注入剂量为1E15~1E16每平方厘米,注入能量为40~80KeV,于离子注入后进行热退火,热退火温度为950~1050℃,时间为10~30秒。

优选地,所述P型注入区之间的距离不小于2μm。

本发明还提供一种低触发电压的SCR器件的制备方法,用于制备如上述的低触发电压的SCR器件,包括:

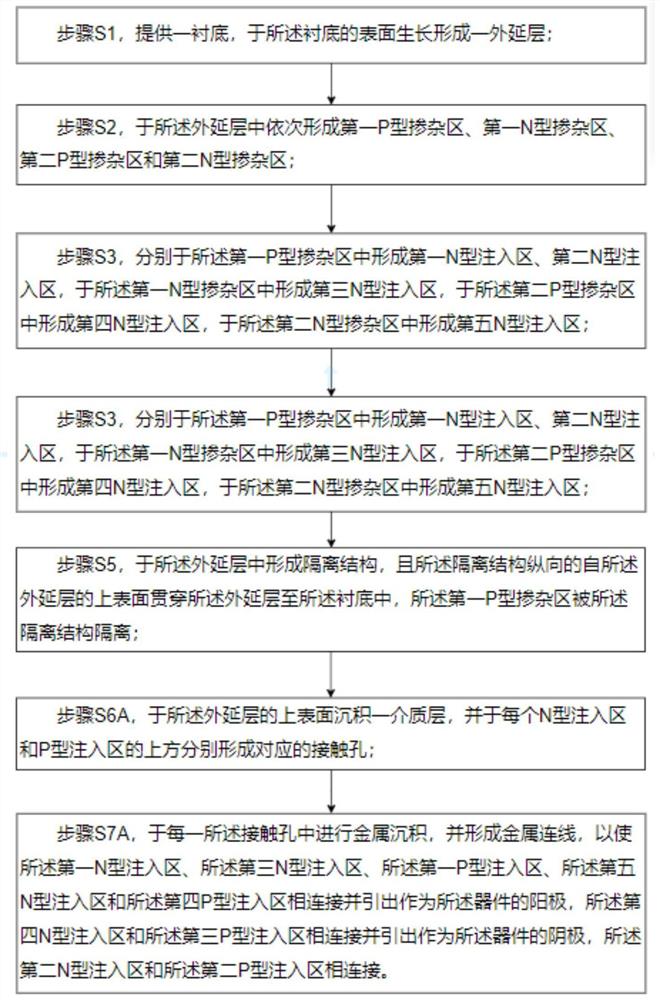

步骤S1,提供一衬底,于所述衬底的表面生长形成一外延层;

步骤S2,于所述外延层中依次形成第一P型掺杂区、第一N型掺杂区、第二P型掺杂区和第二N型掺杂区;

步骤S3,分别于所述第一P型掺杂区中形成第一N型注入区、第二N型注入区,于所述第一N型掺杂区中形成第三N型注入区,于所述第二P型掺杂区中形成第四N型注入区,于所述第二N型掺杂区中形成第五N型注入区;

步骤S4,分别于所述第一N型掺杂区中形成第一P型注入区,于所述外延层中形成第二P型注入区,于所述第二P型掺杂区中形成第三P型注入区,于所述第二N型掺杂区中形成第四P型注入区,其中,所述第二P型注入区与所述第一N型掺杂区、所述第二P型掺杂区耦接;

步骤S5,于所述外延层中形成隔离结构,且所述隔离结构纵向的自所述外延层的上表面贯穿所述外延层至所述衬底中,所述第一P型掺杂区被所述隔离结构隔离;

步骤S6A,于所述外延层的上表面沉积一介质层,并于每个N型注入区和P型注入区的上方分别形成对应的接触孔;

步骤S7A,于每一所述接触孔中进行金属沉积,并形成金属连线,以使所述第一N型注入区、所述第三N型注入区、所述第一P型注入区、所述第五N型注入区和所述第四P型注入区相连接并引出作为所述器件的阳极,所述第四N型注入区和所述第三P型注入区相连接并引出作为所述器件的阴极,所述第二N型注入区和所述第二P型注入区相连接。

本发明还提供一种低触发电压的SCR器件的制备方法,用于制备如上述的低触发电压的SCR器件,包括:

步骤S1,提供一衬底,于所述衬底的表面生长形成一外延层;

步骤S2,于所述外延层中依次形成第一P型掺杂区、第一N型掺杂区、第二P型掺杂区和第二N型掺杂区;

步骤S3,分别于所述第一P型掺杂区中形成第一N型注入区、第二N型注入区,于所述第一N型掺杂区中形成第三N型注入区,于所述第二P型掺杂区中形成第四N型注入区,于所述第二N型掺杂区中形成第五N型注入区;

步骤S4,分别于所述第一N型掺杂区中形成第一P型注入区,于所述外延层中形成第二P型注入区,于所述第二P型掺杂区中形成第三P型注入区,于所述第二N型掺杂区中形成第四P型注入区,其中,所述第二P型注入区与所述第一N型掺杂区、所述第二P型掺杂区耦接;

步骤S5,于所述外延层中形成隔离结构,且所述隔离结构纵向的自所述外延层的上表面贯穿所述外延层至所述衬底中,所述第一P型掺杂区被所述隔离结构隔离;

步骤S6B,于所述外延层的上表面沉积一介质层,于所述介质层中形成一多晶硅层,所述多晶硅层位于所述第二N型注入区和所述第三N型注入区之间,并于每个N型注入区和P型注入区的上方,以及所述多晶硅层的两端分别形成对应的接触孔;

步骤S7B,于每一所述接触孔中进行金属沉积,并形成金属连线,以使所述第一N型注入区、所述第三N型注入区、所述第一P型注入区、所述第五N型注入区和所述第四P型注入区相连接并引出作为所述器件的阳极,所述第四N型注入区和所述第三P型注入区相连接并引出作为所述器件的阴极,所述第二N型注入区、所述多晶硅层和所述第二P型注入区相连接。

本发明技术方案的有益效果在于:

本发明所提供的SCR器件的触发电压较低,ESD静电放电泄放能力较强,稳定性较佳和可靠性高;并联多条导通路径,可同时释放电流,有利于将ESD事件均匀分流,增强了静电泄放能力。

附图说明

图1是本发明中一种低触发电压的SCR器件的制备方法的流程示意图;

图2是本发明中一种低触发电压的SCR器件的制备方法步骤S1的结构示意图;

图3是本发明中一种低触发电压的SCR器件的制备方法步骤S2的结构示意图;

图4是本发明中一种低触发电压的SCR器件的制备方法步骤S3的结构示意图;

图5是本发明中一种低触发电压的SCR器件的制备方法步骤S4的结构示意图;

图6是本发明中一种低触发电压的SCR器件的制备方法步骤S5的结构示意图;

图7是本发明中一种低触发电压的SCR器件的制备方法步骤S6A的结构示意图;

图8是本发明中制备得到的低触发电压的SCR器件具体实施例一的结构示意图;

图9是本发明中一种低触发电压的SCR器件具体实施例一的等效电路图;

图10是本发明中一种低触发电压的SCR器件的的制备方法具体实施例二的流程示意图;

图11是本发明中制备得到的低触发电压的SCR器件具体实施例二的结构示意图;

图12是本发明中一种低触发电压的SCR器件具体实施例二的等效电路图。

附图标记:

01、阳极;02、阴极;1、衬底;2、外延层;31、第一P型掺杂区;32、第二P型掺杂区;41、第一N型掺杂区;42、第二N型掺杂区;51、第一N型注入区;52、第二N型注入区;53、第三N型注入区;54、第四N型注入区;55、第五N型注入区;61、第一P型注入区;62、第二P型注入区;63、第三P型注入区;64、第四P型注入区;7、隔离结构;8、介质层;81、接触孔;9、金属;10、多晶硅层;

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动的前提下所获得的所有其他实施例,都属于本发明保护的范围。

需要说明的是,在不冲突的情况下,本发明中的实施例及实施例中的特征可以相互组合。

下面结合附图和具体实施例对本发明作进一步说明,但不作为本发明的限定。

实施例一:

本发明提供一种低触发电压的SCR器件,如图8所示,包括:

一衬底1;

一外延层2,形成于衬底1的上表面,外延层2中包括:

一第一P型掺杂区31,第一P型掺杂区31中包括第一N型注入区51、第二N型注入区52;

一第一N型掺杂区41,第一N型掺杂区41中包括第三N型注入区53、第一P型注入区61;

一第二P型掺杂区32,第二P型掺杂区32中包括第四N型注入区54、第三P型注入区63;

第二N型掺杂区42,第二N型掺杂区42中包括第五N型注入区55、第四P型注入区64;

第二P型注入区62,第二P型注入区62与第一N型掺杂区41、第二P型掺杂区32耦接;

隔离结构7,隔离结构7纵向的自外延层2的上表面贯穿外延层至衬底1中,第一P型掺杂区31被隔离结构7隔离;

一介质层8,形成于外延层2的上表面;

多个金属层9,分别形成于每个N型注入区和P型注入区的上方;

多条金属连线,用以使第一N型注入区51、第三N型注入区53、第一P型注入区61、第五N型注入区55和第四P型注入区64相连接并引出作为器件的阳极,第四N型注入区54和第三P型注入区63相连接并引出作为器件的阴极,第二N型注入区52和第二P型注入区62相连接。

实施例二:

本发明提供一种低触发电压的SCR器件的制备方法,属于半导体保护器件领域,如图1所示,具体包括如下步骤:

步骤S1,如图2所示,提供一第一导电类型的衬底1N-sub,于衬底1的表面生长形成一第二导电类型的外延层2P-epi;

其中,第一导电类型为N型或P型,即若衬底1的导电类型为N型,则外延层2的导电类型为P型;若衬底1的导电类型为P型,则外延层2的导电类型为N型,本发明中以N型衬底1,P型外延层2为例;

在步骤S1中,首先,选用一个N型硅片作为衬底1,在一个具体实施例中,衬底1采用高电阻材料制成,作为优选,在本实施例中,衬底1所用材料的电阻率为[0.1Ω*cm,1Ω*cm];

通过高温外延工艺,在衬底1的表面生长P型外延层2,外延层2的厚度为[10μm,15μm],外延层2的电阻率要大于衬底1的电阻率,在本实施例中,外延层2的电阻率为[50Ω*cm,100Ω*cm],使用高电阻率的外延层2能够有利于降低器件的电容,可应用于高速信号端口。

步骤S2,如图3所示,于外延层2中依次形成第一P型掺杂区31PW1、第一N型掺杂区41NW1、第二P型掺杂区32和第二N型掺杂区42;

在步骤S2中,通过光刻工艺定义第一P型掺杂区31,然后进行离子注入;再通过光刻工艺定义第二P型掺杂区32,然后再次进行离子注入;最后通过光刻工艺定义第一N型掺杂区41和第二N型掺杂区42,然后再次进行离子注入,于离子注入后,进入炉管中通过高温推进工艺,使得第一P型掺杂区31PW1、第一N型掺杂区41NW1、第二P型掺杂区32和第二N型掺杂区42扩散至一定结深度。优选的,第二P型掺杂区32的结深度小于第二N型掺杂区42的结深度,且第二P型掺杂区32邻接于第二N型掺杂区42。

进一步的,第一P型掺杂区31、第一N型掺杂区41、第二P型掺杂区32和第二N型掺杂区42为依次形成于P型外延层2中的阱区,即第一P型掺杂区31和第二P型掺杂区32为形成于外延层2中的P型阱区,第一N型掺杂区41和第二N型掺杂区42为形成于外延层2中的N型阱区。

在一个较佳的实施例中,优选的,第一P型掺杂区31的注入元素为硼,离子注入剂量为5E12~5E13每平方厘米,注入能量60~100KeV;

优选的,第二P型掺杂区32的注入元素为硼,离子注入剂量为5E14~8E14每平方厘米,注入能量40~60KeV;

优选的,第一N型掺杂区41和第二N型掺杂区42的注入元素为磷,离子注入剂量为5E13~1E14每平方厘米,注入能量60~80KeV。

进一步的,于离子注入后通过高温推进工艺使得第一P型掺杂区31、第二P型掺杂区32、第一N型掺杂区41以及第二N型掺杂区42的结深度为2~6μm,推进温度为1050℃~1150℃,推进时间为30~120分钟。优选的,根据所制备的低触发电压的SCR器件的产品需要,可进行多次高温推进。

步骤S3,如图4所示,分别于第一P型掺杂区31中形成第一N型注入区51、第二N型注入区52,于第一N型掺杂区41中形成第三N型注入区53,于第二P型掺杂区32中形成第四N型注入区54,于第二N型掺杂区42中形成第五N型注入区55;

在步骤S3中,通过光刻工艺及离子注入工艺在掺杂区的表面进行N+选择性注入形成注入区,然后进入炉管进行退火,以修复注入损伤。

作为优选的实施方式,每个N型注入区的注入元素分别为磷或砷,离子注入剂量为1E15~1E16每平方厘米,注入能量为80~100KeV,于离子注入后进行快速热退火,快速热退火温度为850℃~950℃,时间为30~60分钟。

作为优选的实施方式,形成于第二P型掺杂区32内的第四N型注入区54与第一N型掺杂区41之间的距离不超过6μm,同样优选的,第四N型注入区54与第二N型掺杂区42之间的距离也不超过6μm。

作为优选的实施方式,形成于第一P型掺杂区31内的两个N型注入区之间的距离不超过5μm,即第一N型注入区51和第二N型注入区52之间的距离不超过5μm。

步骤S4,如图5所示,分别于第一N型掺杂区41中形成第一P型注入区61,于外延层2中形成第二P型注入区62,于第二P型掺杂区32中形成第三P型注入区63,于第二N型掺杂区42中形成第四P型注入区64,其中,第二P型注入区62与第一N型掺杂区41、第二P型掺杂区32耦接;

在步骤S4中,通过光刻工艺及离子注入工艺在掺杂区的表面进行P+选择性注入形成注入区,然后进行快速热退火,以修复注入损伤。

作为优选的实施方式,每个P型注入区的注入元素分别为硼或二氟化硼,离子注入剂量为1E15~1E16每平方厘米,注入能量为40~80KeV,于离子注入后进行快速热退火,快速热退火温度为950~1050℃,时间为10~30秒。

作为优选的实施方式,第一N型掺杂区41、第二P型掺杂区32交界处的注入区,即第二P型注入区62作为注入电流的接入点。

作为优选的实施方式,各P型注入区之间的距离不小于2μm。

步骤S5,如图6所示,于外延层2中形成隔离结构7,且隔离结构7纵向的自外延层2的上表面贯穿外延层2至衬底1中,第一P型掺杂区31被隔离结构7隔离;

在步骤S5中,在外延层2中刻蚀深槽,并填充介质,以形成隔离结构7,隔离结构7为深槽隔离(Deep Trench Isolatin,DTI),DTI深槽隔离纵向的贯穿外延层2直至衬底1,通过形成的深槽隔离能够提高器件集成密度。

步骤S6A,如图7所示,于外延层2的上表面沉积一介质层8,并于每个N型注入区和P型注入区的上方分别形成对应的接触孔81;

作为优选的实施方式,在步骤S5制备的得到的器件的上表面进行介质淀积形成介质层8,介质层8可以是氧化层,也可以是硼磷玻璃,也可以是多层绝缘膜质复合层;随后通过光刻工艺及刻蚀工艺形成多个接触孔81,每一接触孔81分别对应每个注入区,且位于每一注入区的上表面。

步骤S7A,如图8所示,于上述表面的每一接触孔81中进行金属9沉积,然后通过光刻工艺、金属刻蚀形成金属连线,以使第一N型注入区51、第三N型注入区53、第一P型注入区61、第五N型注入区55和第四P型注入区64相连接并引出作为器件的阳极01,第四N型注入区54和第三P型注入区63相连接并引出作为器件的阴极02,第二N型注入区52和第二P型注入区62相连接。

实施例三:

本实施例为实施例二的等效电路,如图9所示,包括:

一二极管D1,二极管D1的阳极连接至一第一端口,二极管D1的阴极连接至一第二端口,其中第一端口为器件的阳极01,第二端口为器件的阴极02;

一第一三极管Q1,第一三极管Q1的发射极连接第一端口,第一三极管Q1的基极通过一第一电阻R-Nw连接第一端口;

一第二三极管Q2,第二三极管Q2的基极连接第一三极管Q1的集电极,第二三极管Q2的集电极极连接第一三极管Q1的基极,第二三极管Q2的发射极连接第二端口;

一瞬态二极管TVS,瞬态二极管TVS包括一第一电极和一第二电极,第一电极连接第一端口,第二电极直接连接第二三极管TVS的基极。

首先,选用一个N型硅片作为衬底1,在一个具体实施例中,衬底1采用高电阻材料制成,作为优选,在本实施例中,衬底1所用材料的电阻率为[0.1Ω*cm,1Ω*cm];

通过高温外延工艺,在衬底1的表面生长P型外延层2,外延层2的厚度为[10μm,15μm],外延层2的电阻率要大于衬底1的电阻率,在本实施例中,外延层2的电阻率为[50Ω*cm,100Ω*cm],使用高电阻率的外延层2能够有利于降低器件的电容,可应用于高速信号端口。

然后,在外延层2中形成二极管D1、第一三极管Q1、第二三极管Q2、瞬态二极管TVS、第一电阻R-Nw。

作为优选的实施方式,第一三极管Q1为PNP晶体管,由第一N型掺杂区41、第三N型注入区53、第一P型注入区61、第二P型注入区62共同形成;第二三极管Q2为NPN晶体管,由第一N型掺杂区41、第三N型注入区53、第二P型注入区62、第二P型掺杂区32、第四N型注入区54共同形成;瞬态二极管TVS是由第一N型注入区51、第一P型掺杂区31、第二N型注入区52形成的低雪崩击穿或穿通击穿的基极浮空三极管;第一电阻R-Nw为第二N型掺杂区42的寄生电阻,二极管D1是由第二P型掺杂区32、第二N型掺杂区42形成的二极管。

本实施例中,第一P型掺杂区31具有较高的掺杂浓度,其内部的第一N型注入区51和第二N型注入区52之间形成的TVS的击穿电压远远小于NW1/P+的击穿电压,第一P型掺杂区31的击穿电压在5V以内;而第二P型掺杂区32、第一N型掺杂区41、第二N型掺杂区42具有较低的掺杂浓度,其击穿电压一般为20V以上。

当可控硅器件的阳极01遭遇静电放电(ESD)事件时,电压升高瞬间,首先瞬态二极管TVS击穿,电流到达第一N型掺杂区41与第二P型掺杂区32的交界处的第二P型注入区62,即注入电流的接入点,电流流经第二P型注入区62、第二P型掺杂区32、第三P型注入区63到达阴极02,静电放电ESD电压持续增加,电流通过R_PW1流到阴极02。由于第二P型掺杂区32具有较低的掺杂浓度,因此第二P型掺杂区32的寄生电阻较大,只要很小的电流通过第二P型掺杂区32的寄生电阻,就能使其两端的电压差达到0.7V以上,即第二三极管Q2的发射结(第一P型掺杂区和N+注入区)正偏,由于第二三极管Q2的集电结本身处于反偏状态,因此第二三极管Q2导通。第二三极管Q2导通后,产生基极电流,即第一N型掺杂区41和第二P型注入区62,以及第四N型注入区54和第二P型掺杂区32结产生电流,电流路径为第一N型掺杂区41、第二P型注入区62、第二P型掺杂区32至第四N型注入区54,之后第一三极管Q1也将导通,本发明SCR器件进入正反馈,处于大负阻导通状态,从而有效保护后级电路。

作为优选的实施方式,可控硅器件的触发电压主要由瞬态二极管TVS的击穿电压决定,由于第一P型掺杂区31具有很高的掺杂浓度,N+注入区也具有很高的掺杂浓度,因此第一N型注入区51、第一P型掺杂区31、第二N型注入区52之间的PN结的击穿电压很低,通过离子注入精确控制掺杂浓度,能够将击穿电压控制在5V以内,因此,可控硅器件具有极低的触发电压,可以保护更多工作电压较低的电路。

作为优选的实施方式,当可控硅器件的阳极01遭遇负向浪涌时,负向浪涌可以通过二极管D1到达阴极02,使得负向浪涌得以释放。

作为优选的实施方式,可控硅器件采用重复单元结构,并联多条导通路径,可以同时释放电流,有利于将ESD事件均匀分流,因此具有很强的ESD泄放能力、极佳的稳定性和较高的可靠性。

实施例四:

本发明还提供一种低触发电压的SCR器件的制备方法,如图10所示,包括:

步骤S1,如图2所示,提供一第一导电类型的衬底1,于衬底1的表面生长形成一第二导电类型的外延层2;

步骤S2,如图3所示,于外延层2中依次形成第一P型掺杂区31、第一N型掺杂区41、第二P型掺杂区32和第二N型掺杂区42;

步骤S3,如图4所示,分别于第一P型掺杂区31中形成第一N型注入区51、第二N型注入区52,于第一N型掺杂区41中形成第三N型注入区53,于第二P型掺杂区32中形成第四N型注入区54,于第二N型掺杂区42中形成第五N型注入区55;

步骤S4,如图5所示,分别于第一N型掺杂区41中形成第一P型注入区61,于外延层2中形成第二P型注入区62,于第二P型掺杂区32中形成第三P型注入区63,于第二N型掺杂区42中形成第四P型注入区64,其中,第二P型注入区62与第一N型掺杂区41、第二P型掺杂区32耦接;

步骤S5,如图6所示,于外延层2中形成隔离结构7,且隔离结构7纵向的自外延层2的上表面贯穿外延层2至衬底1中,第一P型掺杂区31被隔离结构7隔离;

步骤S6B,如图11所示,于外延层2的上表面沉积一介质层8,于介质层8中形成一多晶硅层10,多晶硅层10位于第二N型注入区52和第三N型注入区53之间,并于每个N型注入区和P型注入区的上方,以及多晶硅层10的两端分别形成对应的接触孔81;

步骤S7B,如图10所示,于每一接触孔81中进行金属9沉积,并形成金属连线,以使第一N型注入区51、第三N型注入区53、第一P型注入区61、第五N型注入区55和第四P型注入区64相连接并引出作为器件的阳极01,第四N型注入区54和第三P型注入区63相连接并引出作为器件的阴极02,第二N型注入区52、多晶硅层10和第二P型注入区62相连接。

在实施例三中,步骤S1-步骤S5的具体实施方式与实施例一中的步骤S1-步骤S5的相同,例如导电类型、各掺杂区以及各注入区的注入离子元素,注入能量、采用的工艺等均可一致,在此不再赘述,本实施例在实施例一的基础上,增加了多晶硅层10,作为限流电阻,多晶硅层10上方的两端分别通过光刻工艺及刻蚀工艺形成接触孔81,以使限流电阻的一端通过金属连线连接第二N型注入区52,限流电阻的另一端通过金属连线连接第二P型注入区62。优选的实施方式中,多晶硅层10的阻值为[100Ω,200Ω]。

实施例五:

本实施例为实施例三的等效电路,如图12所示,包括:

一二极管D1,二极管D1的阳极01连接至一第一端口,二极管D1的阴极连接至一第二端口;

一第一三极管Q1,第一三极管Q1的发射极连接第一端口,第一三极管Q1的基极通过一第一电阻R-Nw连接第一端口;

一第二三极管Q2,第二三极管Q2的基极连接第一三极管Q1的集电极,第二三极管Q2的集电极极连接第一三极管Q1的基极,第二三极管Q2的发射极连接第二端口;

一瞬态二极管TVS,瞬态二极管TVS包括一第一电极和一第二电极,第一电极连接第一端口,第二电极通过一第二电阻R-poly连接第二三极管的基极。

具体的,在实施例二的基础上增加了一个第二电阻R-poly,作为限流电阻,第二电阻R-poly的阻值为[100Ω,200Ω]。

本发明技术方案的有益效果在于:

本发明所提供的SCR器件的触发电压较低,ESD静电放电泄放能力较强,稳定性较佳和可靠性高;并联多条导通路径,可同时释放电流,有利于将ESD事件均匀分流,增强了静电泄放能力。

以上所述仅为本发明较佳的实施例,并非因此限制本发明的实施方式及保护范围,对于本领域技术人员而言,应当能够意识到凡运用本发明说明书及图示内容所作出的等同替换和显而易见的变化所得到的方案,均应当包含在本发明的保护范围内。

- 一种低触发电压的SCR器件及其制备方法

- 一种基于埋层触发的低触发电压双向SCR器件