氮化物半导体器件的制造方法

文献发布时间:2023-06-19 11:55:48

技术领域

本公开内容涉及氮化物半导体器件的制造方法。

本申请主张基于在2018年12月27日申请的日本申请第2018-245213号的优先权,引用在所述日本申请中记载的全部记载内容。

背景技术

氮化镓(GaN)等氮化物半导体通过在半导体基板上外延生长来形成。这样的氮化物半导体例如通过有机金属气相生长法(MOCVD法)形成。在下述专利文献1、2中公开了利用所谓的横向流动方式的晶体生长方法。在下述专利文献1中公开了用于抑制比基板更靠上游侧的原料的热分解和中间反应的晶体生长装置的构成。在下述专利文献2中公开了利用HCl除去堆积在反应室的内壁上的堆积物,然后实施晶体生长。

现有技术文献

专利文献

[专利文献1]日本特开第2008-28270号公报

[专利文献2]日本特开第2014-55103号公报

发明内容

本公开内容的一个方面所涉及的氮化物半导体器件的制造方法具有:使用将H

附图说明

[图1]图1是表示在第一实施方式所涉及的氮化物半导体器件中使用的半导体基板的截面图。

[图2]图2是表示设置有半导体基板的半导体生长装置的示意截面图。

[图3]图3是用于说明第一实施方式所涉及的氮化物半导体器件的制造方法的时间图。

[图4A]图4A是说明第一实施方式所涉及的氮化物半导体器件的制造方法的示意图。

[图4B]图4B是说明第一实施方式所涉及的氮化物半导体器件的制造方法的示意图。

[图4C]图4C是说明第一实施方式所涉及的氮化物半导体器件的制造方法的示意图。

[图5A]图5A是说明第一实施方式所涉及的氮化物半导体器件的制造方法的示意图。

[图5B]图5B是说明第一实施方式所涉及的氮化物半导体器件的制造方法的示意图。

[图5C]图5C是说明第一实施方式所涉及的氮化物半导体器件的制造方法的示意图。

[图6A]图6A是表示期间D3后的炉内状态的示意截面图。

[图6B]图6B是表示期间D4后的炉内状态的示意截面图。

[图7]图7是用于说明以往的氮化物半导体器件的制造方法的时间图。

[图8A]图8A是表示通过以往的制造方法生长的阻挡层和分隔层的SIMS测定结果的图。

[图8B]图8B是表示通过第一实施方式所涉及的制造方法生长的阻挡层和分隔层的SIMS测定结果的图。

[图9]图9是用于说明变形例所涉及的氮化物半导体器件的制造方法的时间图。

[图10A]图10A是表示通过变形例所涉及的制造方法生长的阻挡层和分隔层的SIMS测定结果的图。

[图10B]图10B是表示现有技术、第一实施方式和变形例的In组成的图。

[图10C]图10C是表示现有技术、第一实施方式和变形例的Ga组成的图。

[图11A]图11A是说明第二实施方式所涉及的氮化物半导体器件的制造方法的示意图。

[图11B]图11B是说明第二实施方式所涉及的氮化物半导体器件的制造方法的示意图。

[图11C]图11C是说明第二实施方式所涉及的氮化物半导体器件的制造方法的示意图。

[图12A]图12A是说明第三实施方式所涉及的氮化物半导体器件的制造方法的示意图。

[图12B]图12B是说明第三实施方式所涉及的氮化物半导体器件的制造方法的示意图。

[图12C]图12C是说明第三实施方式所涉及的氮化物半导体器件的制造方法的示意图。

[图13]图13是表示现有技术、第一实施方式、第二实施方式、第三实施方式和第四实施方式的Ga组成的图。

[图14]图14是表示堆积在喷出头的表面上的GaN量的推移的表。

具体实施方式

[本公开内容所要解决的问题]

对于将通过上述MOCVD法生长的GaN层作为沟道层的高电子迁移率晶体管(HEMT),要求进一步改善高频特性。作为改善HEMT的高频特性的方法,例如可以列举阻挡层的薄化、二维电子气(2DEG)的高浓度化等。在将包含AlGaN晶体的阻挡层薄化的情况下,该阻挡层的载流子面密度的减小倾向于变大。为了确保该阻挡层的载流子面密度,可以列举增大该阻挡层相对于沟道层的应变。作为增大该应变的方法之一,例如可以列举增加AlGaN阻挡层的Al组成。理论上,对于AlGaN晶体,其作为两端组成的从GaN到AlN,都可以不发生相分离地制作混晶。但是,实际上,Al组成大于0.3的AlGaN晶体不能在GaN层上生长。因此,在利用应变来调节AlGaN阻挡层的载流子面密度方面存在局限。

在此,从降低阻挡层的电阻的观点考虑,使阻挡层中包含铟(In)受到关注。例如,In组成为0.17的InAlN(即,In

另外,在In

但是,当在GaN层上生长InAlN晶体时,存在大量的Ga混入InAlN晶体内的倾向。在此情况下,阻挡层的晶格常数没有达到预期值,导致膜中固有的应变量变大。鉴于这样的问题,本公开内容的目的在于,提供能够生长包含InAlN类化合物的优质阻挡层的氮化物半导体器件的制造方法。

[本公开内容的效果]

根据本公开内容,能够提供能够生长包含InAlN类化合物的优质阻挡层的氮化物半导体器件的制造方法。

[本公开内容的实施方式的说明]

首先,列举本公开内容的实施方式的内容来进行说明。本公开内容的一个实施方式为氮化物半导体器件的制造方法,具有:使用将H

在该制造方法中,实施如下的工序:在设定为比第一温度高的第二温度、将H

在保持SiC基板的工序中,可以向MOCVD炉内供给H

第二温度可以比第一温度高20℃以上。在此情况下,在保持SiC基板的工序中,能够更良好地除去MOCVD炉内的包含Ga的堆积物。

上述制造方法在保持SiC基板的工序之后且在生长InAlN层的工序之前,还可以具有如下的工序:使用将H

在所述第四温度更接近所述第三温度和第二温度当中的第三温度的情况下可以将载气设为N

MOCVD炉具有支承SiC基板的支承部和在SiC基板的厚度方向上与支承部相对的原料供给部,在保持SiC基板的工序中,可以将SiC基板与原料供给部的间隔设定为第一间隔,在生长InAlN层的工序中,可以将SiC基板与原料供给部的间隔设定为比第一间隔宽的第二间隔。而且,第一间隔可以是6mm以下,第二间隔可以是15mm以上。在这些情况下,在生长InAlN层的工序中,堆积物中所含的Ga不易到达InAlN层。因此,能够生长包含InAlN类化合物的更优质阻挡层。

MOCVD炉具有原料供给部,在保持SiC基板的工序中,可以将原料供给部的温度设定为第一装置温度,在生长InAlN层的工序中,可以将原料供给部的温度设定为比第一装置温度低的第二装置温度。而且,第一装置温度可以是60℃以上,第二装置温度可以是30℃以下。在这些情况下,在保持SiC基板的工序中包含Ga的堆积物被良好地除去。

本公开内容的另一实施方式为氮化物半导体器件的制造方法,具有:使用将H

在该制造方法中实施如下的工序:在设定为1000℃以上且第一温度以下的高第二温度、将H

上述制造方法可以在保持SiC基板的工序之后且在生长InAlN层的工序之前,具有如下的工序:将H

在所述第四温度更接近所述第一温度和第三温度当中的第一温度的情况下可以将载气设为N

MOCVD炉具有支承SiC基板的支承部和在SiC基板的厚度方向上与支承部相对的原料供给部,在保持SiC基板的工序中,可以将SiC基板与原料供给部的间隔设定为第一间隔,在生长InAlN层的工序中,可以将SiC基板与原料供给部的间隔设定为比第一间隔宽的第二间隔。而且,第一间隔可以是6mm以下,第二间隔可以是15mm以上。在这些情况下,在生长InAlN层的工序中,堆积物中所含的Ga不易到达InAlN层。因此,能够生长包含InAlN类化合物的更优质阻挡层。

MOCVD炉具有原料供给部,在保持SiC基板的工序中,可以将原料供给部的温度设定为第一装置温度,在生长InAlN层的工序中,可以将原料供给部的温度设定为比第一装置温度低的第二装置温度。而且,第一装置温度可以是60℃以上,第二装置温度可以是30℃以下。在这些情况下,在保持SiC基板的工序中包含Ga的堆积物被良好地除去。

[本公开内容的实施方式的说明]

本公开内容的发现可以通过参考作为例示示出的附图并考虑以下的详细记述来容易地理解。以下,参考附图,对本公开内容的优选实施方式详细地说明。需要说明的是,在以下的说明中,对相同的要素或具有相同功能的要素使用相同的符号,并省略重复的说明。

(第一实施方式)

图1是表示在第一实施方式所涉及的氮化物半导体器件中使用的半导体基板的截面图。如图1所示,在作为氮化物半导体器件的一例的高电子迁移率晶体管(以下,称为“HEMT”)中使用的半导体基板1具有基板10、缓冲层12、沟道层14、分隔层16、阻挡层18以及盖帽层20。在半导体基板1中,在基板10上依次层叠有作为氮化物半导体层的缓冲层12、沟道层14、分隔层16、阻挡层18以及盖帽层20。缓冲层12、沟道层14、分隔层16、阻挡层18以及盖帽层20分别例如通过MOCVD法生长。

基板10为半绝缘性的SiC基板(碳化硅基板)。缓冲层12作为对于沟道层14的缓冲层和晶种层起作用,是在基板10上外延生长的AlN层。缓冲层12的厚度例如是10nm以上且30nm以下。

沟道层14作为载流子传输层起作用,是在缓冲层12上外延生长的i型GaN层(GaN沟道层)。GaN由于对SiC的浸润性,因而不能直接生长在基板10上。因此,沟道层14隔着缓冲层12的AlN而生长。沟道层14的厚度例如为300nm以上且1000nm以下。

分隔层16是位于沟道层14与阻挡层18之间的层,是在沟道层14上外延生长的AlN层。分隔层16的厚度例如为0.5nm以上且2nm以下。

阻挡层18作为载流子产生层起作用,是在分隔层16上外延生长的氮化物半导体层。阻挡层18例如是包含In(铟)的氮化物半导体层。阻挡层18例如包含InAlN类化合物。在第一实施方式中,阻挡层18为InAlN层。优选该InAlN层中所含的镓(Ga)少。阻挡层18的厚度例如为3nm以上且10nm以下。在沟道层14与阻挡层18之间发生自发极化。由此,在沟道层14与分隔层16的界面在沟道层14侧产生二维电子气(2DEG),在沟道层14内形成沟道区域。

盖帽层20是在阻挡层18上外延生长的GaN层。盖帽层20的厚度例如为0nm以上且5nm以下。即,不一定必须设置盖帽层20。盖帽层20可以为n型化的。

可以在半导体基板1上设置保护膜。保护膜例如为SiN膜等绝缘膜。保护膜例如通过低压化学气相沉积法(Low Pressure Chemical Vapor Deposition;LPCVD)、MOCVD法、CVD法等形成。在使用MOCVD法的情况下,也可以利用生长半导体基板1的装置形成保护膜。在此情况下,能够在不将半导体基板1暴露在空气等中的情况下形成保护膜。

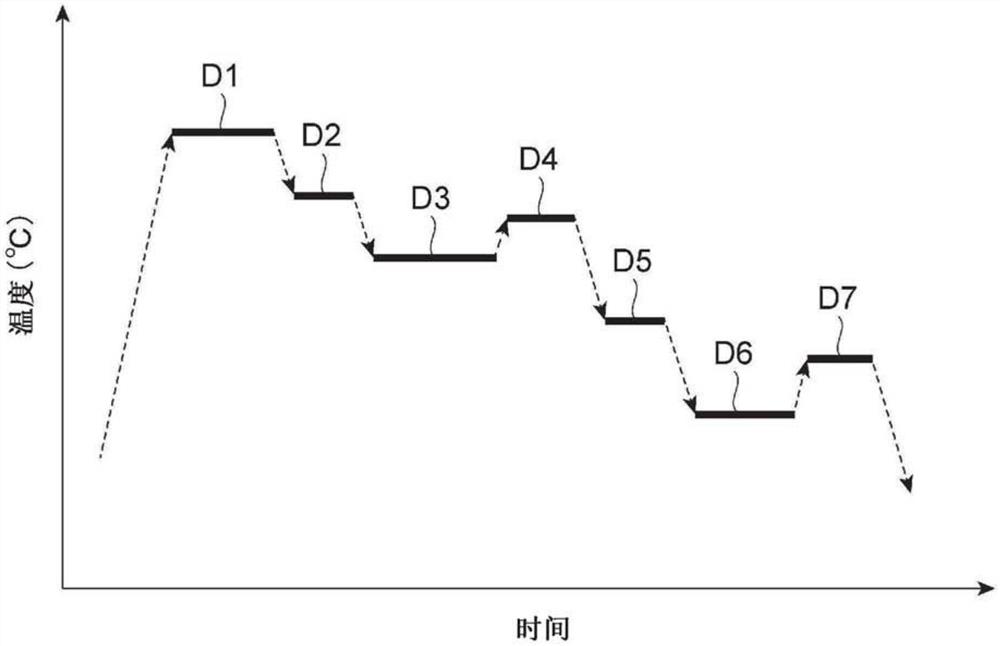

接着,一边使用图2、图3、图4A~图4C、图5A~图5C以及图6A、图6B,一边对半导体基板1的制造方法进行说明。图2是表示设置有半导体基板的半导体生长装置的示意截面图。图3是用于说明第一实施方式所涉及的氮化物半导体器件的制造方法的时间图。图4A~图4C和图5A~图5C是说明第一实施方式所涉及的氮化物半导体器件的制造方法的示意图。图6A是表示后述的期间D3后的炉内状态的示意截面图,图6B是表示后述的期间D4后的炉内状态的示意截面图。需要说明的是,在图3中,横轴表示时间,纵轴表示温度。另外,在图6A、图6B中省略了在基板10上生长的半导体。

首先,如图2所示,将基板10容纳在半导体生长装置30的炉31内。在第一实施方式中,半导体生长装置30是所谓的垂直流方式的MOCVD装置。因此,炉31是立式MOCVD炉。因此,通过MOCVD法在容纳在炉31内的基板10上生长半导体层。炉31具有承载(支承)基板10的基座32(支承部)和将原料向炉31内喷出的喷出头33(原料供给部)。在基座32中与喷出头33相对的区域中设置有承载基板10的凹部32a。喷出头33例如是具有多个喷出孔33a的喷淋头。喷出孔33a的出口在基板10的厚度方向上与基座32相对。基座32与喷出头33的间隔S例如为8mm以上且12mm以下。

接着,在图3所示的期间D1中,在基板10承载在基座32上的状态下将炉31内进行加热。由此,实施对基板10的表面和炉31内的清洁。在期间D1的工序中,例如向炉31内供给氢气(H

接着,在图3所示的期间D2,如图4A所示,在基板10上生长缓冲层12。在期间D2的工序中,首先,将炉31内的温度设定为比期间D1低的温度。然后,持续向炉31内供给作为载气的H

接着,在图3所示的期间D3,如图4B所示,在缓冲层12上生长沟道层14。在期间D3的工序中,首先,将炉31内的温度设定为比期间D2低的温度(第一温度)。然后,将H

如上所述,由于炉31内的基座32与喷出头33的间隔S窄,因此在期间D3中,存在Ga原子附着在喷出孔33a的出口等处的倾向。由此,如图6A所示,有时在喷出头33的表面上形成Ga原子、Ga簇、GaN多晶等的堆积物41。在形成有堆积物41的情况下,Ga混入在沟道层14上生长的半导体层(例如,分隔层16和阻挡层18)中。在此情况下,导致该半导体层的膜品质降低。为了防止这样的问题,在图3所示的期间D4中,将炉31内保持在比期间D3高的温度(第二温度)下预定期间。由此,如图6B所示,将堆积物41从炉31内除去。在期间D4中,首先,停止TMG的供给,然后使炉31内的温度升高。将期间D4中的炉31的温度设定为比期间D3中的炉31的温度高20℃以上。然后,在向炉31内供给H

在期间D4中,堆积物41被供给到炉31内的H

接着,在图3所示的期间D5中,如图5A所示,在沟道层14上生长分隔层16。在期间D5的工序中,首先,将炉31内的温度设定为比期间D4低的温度(第四温度)。然后,将H

接着,在图3所示的期间D6中,如图5B所示,在分隔层16上生长阻挡层18。在期间D6的工序中,首先,为了防止堆积在分隔层16上的In被除去,将载气由H

接着,在图3所示的期间D7中,如图5C所示,在阻挡层18上生长盖帽层20。在期间D7的工序中,首先,将炉31内的温度设定为比期间D6高的温度。然后,将N

经过以上的期间D1~D7,在基板10上形成半导体基板1。使用该半导体基板1,能够形成作为氮化物半导体器件的HEMT等。

一边参考图7和图8A、8B,一边对通过以上说明的氮化物半导体器件的制造方法得到的作用效果进行说明。图7是用于说明以往的氮化物半导体器件的制造方法的时间图。图8A是表示通过以往的制造方法生长的阻挡层和分隔层的SIMS测定结果的图,图8B是表示通过第一实施方式所涉及的制造方法生长的阻挡层和分隔层的SIMS测定结果的图。在图8A、8B中,横轴表示从阻挡层表面起算的距离,纵轴表示构成元素的组成。另外,曲线51、61表示Al的测定结果,曲线52、62表示Ga的测定结果,曲线53、63表示In的测定结果。需要说明的是,在图8A、8B中,纵轴利用线性标度表示,将Al、Ga和In的组成的合计设定为1。

如图7所示,以往不实施期间D4的工序。因此,以往是在期间D3中喷出头33上形成有堆积物41的状态下生长分隔层、阻挡层和盖帽层。在此情况下,TMI中所含的In原子倾向于与堆积物41中的Ga原子置换。因此,在期间D3后生长作为阻挡层起作用的InAlN层的情况下,导致包含In的AlGaN层(即,包含大量的Ga的InAlN类晶体)生长。实际上,如图8A所示,阻挡层内的Ga的组成明显高于In的组成。需要说明的是,推测In原子与Ga原子的置换通过在炉31内喷出头33和堆积物41被加热而得到促进。

当在半导体生长装置30内容纳GaN基板并在该GaN基板上直接生长InAlN层的情况下,生长的是基本上不含Ga的InAlN层。由该情况也可知,由于堆积物41的存在而导致在阻挡层等中混入大量的Ga。而且还可知,仅通过供给H

与此相对,在第一实施方式所涉及的制造方法中,实施期间D4的工序。由此,在分隔层16和阻挡层18的生长前,能够良好地除去堆积物41。实际上,如图8B所示,阻挡层18内的Ga的组成变得比以往低,并且阻挡层18内的In的组成变得比以往明显高。另外,沿半导体基板1的厚度方向的阻挡层18内的各原子的组成比稳定。因此,根据第一实施方式,能够生长包含InAlN类化合物的优质阻挡层18。

通常,在InAlN类晶体中,Ga浓度越是升高,则该晶体的a轴越倾向于从GaN偏离。在此情况下,包含Ga的InAlN类晶体中的应变变大。当该应变变大时,存在在InAlN类晶体中产生裂纹以及表面凹坑增加的倾向。在使用这样的InAlN类晶体制造氮化物半导体器件(HEMT、FET)的情况下,存在该器件的漏电流变大的倾向。因此,在InAlN类晶体中含有Ga越多,则氮化物半导体器件的性能和可靠性越倾向于降低。因此,可以说通过应用第一实施方式所涉及的制造方法生长包含InAlN类化合物的优质阻挡层18是有用的。

在期间D4中,H

如第一实施方式所示,在期间D4中设定的第二温度可以比在期间D3中设定的第一温度高20℃以上。在此情况下,能够良好地除去堆积物41。

如第一实施方式所示,在期间D4的工序之后且在期间D6的工序之前,可以使用将N

如第一实施方式那样,炉31具有承载基板10的基座32和喷出原料的喷出头33,基座32与喷出头33的间隔S可以是8mm以上且12mm以下。在此情况下,由于原料能够在原料的热分解等发生之前到达基板10,因此能够在基板10上高效地外延生长半导体层。另一方面,在将间隔S设定在上述范围内的情况下,Ga容易附着在喷出头33等上。即,在将间隔S设定在上述范围内的情况下,容易形成堆积物41。但是,根据第一实施方式,由于在期间D4中堆积物41被良好地除去,因此能够在抑制阻挡层18的膜品质劣化的同时,高效地外延生长半导体层。

以下,一边参考图9和图10A~图10C,一边对第一实施方式的变形例进行说明。需要说明的是,在以下的变形例中,省略与第一实施方式重复的部分的说明。因此,以下主要对与第一实施方式不同的部分进行说明。

图9是用于说明变形例所涉及的氮化物半导体器件的制造方法的时间图。如图9所示,变形例的时间图表示与第一实施方式的期间D4不同的期间D14。期间D14位于期间D3、D5之间,设定为与期间D4相同的温度。另外,在期间D14中,向炉31内供给H

在该变形例中,通过向炉31中供给TMI,堆积物41(参考图6A)的Ga被In置换。由此,变得容易除去Ga。而且,炉31内的温度大于1000℃,并且向炉31内供给H

图10A是表示通过上述变形例所涉及的制造方法生长的阻挡层和分隔层的SIMS测定结果的图。在图10A中,曲线71表示Al的测定结果,曲线72表示Ga的测定结果,曲线73表示In的测定结果。如图10A所示,上述变形例中的阻挡层18内的Ga的组成相比第一实施方式进一步减小。具体而言,上述变形例中的阻挡层18内的Ga的组成为0.04以下。

图10B是表示现有技术、第一实施方式和上述变形例的In组成的图。在图10B中,符号81表示现有技术的阻挡层中的In组成,符号82表示第一实施方式的阻挡层中的In组成,符号83表示上述变形例的阻挡层中的In组成。如图10B所示,上述变形例中的阻挡层的In组成最高,现有技术的阻挡层的In组成最低。

图10C是表示现有技术、第一实施方式和上述变形例的Ga组成的图。在图10C中,符号91表示现有技术的阻挡层中的Ga组成,符号92表示第一实施方式的阻挡层中的Ga组成,符号93表示上述变形例的阻挡层中的Ga组成。如图10C所示,现有技术的阻挡层的Ga组成(约27%)最高,上述变形例中的阻挡层的Ga组成最低。由这些结果,在第一实施方式和上述变形例的任一者中均能够比现有技术提高阻挡层的膜品质。

在第一实施方式和上述变形例中,示出了在980℃下、采用H

(第二实施方式)

以下,一边参考图11A~图11C,一边对第二实施方式进行说明。在第二实施方式中省略与第一实施方式重复的部分的说明。因此,以下主要对与第一实施方式不同的部分进行说明。

图11A~图11C是说明第二实施方式所涉及的氮化物半导体器件的制造方法的示意图。图11A是表示第二实施方式中的期间D3后的炉内状态的示意截面图,图11B是表示第二实施方式中的期间D4中的炉内状态的示意截面图,图11C是表示第二实施方式中的期间D6中的炉内状态的示意截面图。如图11A所示,在第二实施方式中,将在基座32中与喷出头33相对的表面32b和在基板10中与喷出头33相对的表面10a视为同一平面。因此,在基板10的厚度方向上,基座32与喷出头33的间隔相当于基板10与喷出头33的间隔。在期间D3之后,基板10与喷出头33的间隔S1例如为8mm以上且12mm以下。在第二实施方式的期间D3中,例如在与第一实施方式相同的条件下,生长厚度为1μm的GaN层。

如图11B所示,期间D4中的基板10与喷出头33的间隔S2(第一间隔)比间隔S1窄。即,在期间D4中,将基板10与喷出头33的间隔设定为比间隔S1窄的间隔S2。例如,通过使用致动器等使喷出头33向基座32侧移动,在期间D4中,基座32与喷出头33接近。喷出头33的移动例如在期间D4中实施。喷出头33可以在将炉31内升温的过程中移动,也可以在升温前移动,也可以在升温后移动。间隔S2例如为2mm以上且6mm以下。在间隔S2为6mm以下的情况下,喷出头33的表面温度容易变高,因此容易除去堆积物41。在第二实施方式的期间D4中,除了间隔S2以外,在与第一实施方式相同的条件下除去堆积物41。

如图11C所示,期间D6中的基板10与喷出头33的间隔S3(第二间隔)比间隔S1宽。即,在期间D6中,将基板10与喷出头33的间隔设定为比间隔S1宽的间隔S3。例如,通过使用致动器等使喷出头33移动从而远离基座32,从而在期间D6中喷出头33离开基座32。喷出头33的移动例如在期间D6中实施。喷出头33可以在将炉31内降温的过程中移动,也可以在降温之前移动,也可以在降温之后移动。另外,喷出头33可以在向炉31内供给TMI之前移动,也可以在向炉31内供给TMI的过程中移动。间隔S3例如为15mm以上且20mm以下。在间隔S3为15mm以上的情况下,由于残留在喷出头33上的Ga不易到达基座32,因此在InAlN层中不易包含Ga。另外,在间隔S3为20mm以下的情况下,能够防止InAlN层的生长速度显著降低。在第二实施方式的期间D6中,除了间隔S3以外,在与第一实施方式相同的条件下生长厚度为8nm的InAlN层。

在以上说明的第二实施方式所涉及的制造方法中也实现与上述第一实施方式相同的作用效果。而且,通过在期间D4中使基板10与喷出头33的间隔变窄,容易除去堆积物41。例如,通过在期间D4中将基板10与喷出头33的间隔设定为6mm以下,容易良好地除去堆积物41。此外,通过在期间D6中扩大基板10与喷出头33的间隔,残留在喷出头33上的堆积物41中所含的Ga不易到达InAlN层。因此,在InAlN层中更不易包含Ga。例如,通过在期间D6中将基板10与喷出头33的间隔设定为15mm以上,在InAlN层中更不易包含Ga。

在第二实施方式中,将期间D5中的基板10与喷出头33的间隔设定为间隔S2,但不限于此。例如,期间D5中的基板10与喷出头33的间隔也可以比间隔S2宽。在此情况下,可以将期间D5中的基板10与喷出头33的间隔重新设定为间隔S1,也可以设定为间隔S3。例如,期间D5中的基板10与喷出头33的间隔可以设定为15mm。

(第三实施方式)

以下,一边参考图12A~12C,一边对第三实施方式进行说明。在第三实施方式中,省略与第一实施方式和第二实施方式重复的部分的说明。因此,以下主要对与第一实施方式和第二实施方式不同的部分进行说明。

图12A~12C是说明第三实施方式所涉及的氮化物半导体器件的制造方法的示意图。图12A是表示第三实施方式中的期间D1中的炉内状态的示意截面图,图12B是表示第三实施方式中的期间D4中的炉内状态的示意截面图,图12C是表示第三实施方式中的期间D6中的炉内状态的示意截面图。如图12A~12C所示,在第三实施方式中,半导体生长装置30A的炉31A具有基座32和设置有多个喷出孔33a和多个冷却通路34的喷出头33A。冷却通路34是冷却介质通过的空腔,设置在比喷出孔33a靠基端的一侧(隔着喷出孔33a与基座32相反的一侧)。冷却介质用于将喷出头33A的温度保持在预定范围内,例如为气体或液体。冷却介质的温度是可变的。在第三实施方式中,使用水作为冷却介质,但不限于此。

在第三实施方式中,喷出头33A的表面温度相当于喷出头33A的装置温度,但不限于此。例如,可以将供给到冷却通路34的冷却介质的温度视为喷出头33A的表面温度(装置温度)。在此情况下,在供给到冷却通路34的冷却介质的温度为50℃的情况下,将喷出头33A的装置温度视为50℃。供给到冷却通路34的冷却介质相当于即将导入冷却通路34之前的冷却介质的温度。

在图12A中,向冷却通路34中供给冷却介质,使得喷出头33A的装置温度成为温度T1。温度T1例如为40℃以上且60℃以下。在第三实施方式中,将温度T1设定为50℃。因此,将能够将温度T1设定为50℃的温度的冷却介质供给到冷却通路34中。该冷却介质例如从期间D1到期间D3被供给。

在图12B中,向冷却通路34中供给冷却介质,使得喷出头33A的装置温度成为温度T2。温度T2比温度T1高,例如为60℃以上且90℃以下。在此情况下,容易除去位于喷出头33A上的堆积物41。即,存在堆积物41中所含的Ga脱离的倾向。在第三实施方式中,将作为期间D4中的喷出头33A的装置温度(第一装置温度)的温度T2设定为70℃。因此,将能够将温度T2设定为70℃的温度的冷却介质供给到冷却通路34中。该冷却介质例如从期间D4到期间D5被供给。

在图12C中,向冷却通路34中供给冷却介质,使得喷出头33A的装置温度成为温度T3。温度T3比温度T2低,例如为20℃以上且40℃以下。在此情况下,难以除去残留在喷出头33A上的堆积物41。即,存在堆积物41中所含的Ga不脱离的倾向。作为期间D6中的喷出头33A的装置温度(第二装置温度)的温度T3可以比温度T1低。在第三实施方式中,将温度T3设定为30℃。因此,将能够将温度T3设定为30℃的温度的冷却介质供给到冷却通路34中。该冷却介质例如从期间D6到期间D7被供给。

在以上说明的第三实施方式所涉及的制造方法中也实现与上述第一实施方式相同的作用效果。而且,堆积物41中的Ga的脱离量与喷出头33A的装置温度成比例关系。因此,通过在期间D4中提高喷出头33A的装置温度,容易除去堆积物41。例如,通过在期间D4中将喷出头33A的装置温度设定为60℃以上,容易良好地除去堆积物41。此外,通过在期间D6中降低喷出头33A的装置温度,残留在喷出头33A上的堆积物41中所含的Ga不易到达InAlN层。因此,在InAlN层中更不易包含Ga。例如,通过在期间D6中将喷出头33A的装置温度设定为30℃以下,在InAlN层中更不易包含Ga。

在第三实施方式中,将期间D5中的喷出头33A的装置温度设定为温度T2,但不限于此。例如,期间D5中的喷出头33A的装置温度可以比温度T2低。在此情况下,可以将期间D5中的喷出头33A的装置温度重新设定为温度T1,也可以设定为温度T3。

(第四实施方式)

以下,对第四实施方式进行说明。在第四实施方式中,省略与第一实施方式~第三实施方式重复的部分的说明。因此,以下主要对与第一实施方式~第三实施方式不同的部分进行说明。

第四实施方式是将上述第二实施方式与上述第三实施方式组合而得到的实施方式。因此,在期间D4中,将喷出头33A与基板10的间隔设定为间隔S2,并且将喷出头33A的装置温度设定为温度T2。另外,在期间D6中,将喷出头33A与基板10的间隔设定为间隔S3,并且将喷出头33A的装置温度设定为温度T3。

在以上说明的第四实施方式所涉及的制造方法中也实现与上述第一实施方式相同的作用效果。而且,在InAlN层中更好地不易包含Ga。

图13是表示现有技术、第一实施方式、第二实施方式、第三实施方式和第四实施方式的Ga组成的图。在图13中,符号101表示现有技术的阻挡层中的Ga组成,符号102表示第一实施方式的阻挡层中的Ga组成,符号103表示第二实施方式的阻挡层中的Ga组成,符号104表示第三实施方式的阻挡层中的Ga组成,符号105表示第四实施方式的阻挡层中的Ga组成。如图13所示,第二实施方式中的阻挡层的Ga组成(约9%)和第三实施方式中的阻挡层的Ga组成(约8%)均比第一实施方式中的阻挡层的Ga组成(约15%)低。而且,第四实施方式中的阻挡层的Ga组成为约3%。因此,通过实施喷出头与基座的间隔调节以及喷出头的温度调节中的至少一者,能够进一步提高阻挡层的膜品质。另外,通过实施上述两种调节,能够更良好地提高阻挡层的膜品质。

图14是表示堆积在喷出头的表面上的GaN量的推移的表。在图14中,横轴表示时间,纵轴表示堆积在喷出头的表面上的GaN量。另外,符号111表示期间D4、D5中的第一实施方式的堆积物的GaN量的推移,符号112表示期间D4、D5中的第二实施方式的堆积物的GaN量的推移,符号113表示期间D4、D5中的第四实施方式的堆积物的GaN量的推移。另外,符号121表示期间D6中的第一实施方式的堆积物的GaN量的推移,符号122表示期间D6中的第二实施方式的堆积物的GaN量的推移,符号123表示期间D6中的第四实施方式的堆积物的GaN量的推移。如图14所示,在期间D4、D5中,第二实施方式和第四实施方式的堆积物的GaN量均存在比第一实施方式减少的倾向。由此也可知,喷出头与基座的间隔调节以及喷出头的温度调节对于除去堆积在喷出头上的GaN是有效的。

根据本公开内容的氮化物半导体器件的制造方法不限于上述实施方式和变形例,其它各种变形是可能的。例如,上述实施方式和变形例中的半导体基板可以包含除缓冲层、沟道层、分隔层、阻挡层和盖帽层以外的层。或者,半导体基板可以不具有分隔层。

图6A所示的堆积物41呈层状,但不限于此。附着在喷出头上的堆积物有时会局部地设置。例如,堆积物有时仅设置在喷出孔的出口及其周边。另外,堆积物有时也设置在炉的内壁上。

符号说明

1…半导体基板,10…基板,10a…表面,12…缓冲层,14…沟道层,16…分隔层,18…阻挡层,20…盖帽层,30、30A…半导体生长装置,31、31A…炉(MOCVD炉),32…基座(支承部),32a…凹部,32b…表面,33、33A…喷出头(原料供给部),33a…喷出孔,34…冷却通路,41…堆积物,S、S1…间隔,S2…间隔(第一间隔),S3…间隔(第二间隔)。

- 复合GaN衬底、制造复合GaN衬底的方法、III族氮化物半导体器件和制造III族氮化物半导体器件的方法

- Ⅲ族氮化物半导体晶体及其制造方法、Ⅲ族氮化物半导体器件及其制造方法以及发光器件