骤回静电放电(ESD)电路、ESD保护电路及其制造方法

文献发布时间:2023-06-19 12:00:51

技术领域

本发明的实施例涉及骤回静电放电(ESD)电路、ESD保护电路及其制造方法。

背景技术

集成电路(IC)小型化的最新趋势已导致更小的器件消耗更少的功率,但比以前提供了更高的速度。由于各种因素,例如更薄的电介质层厚度和相关的降低的电介质击穿电压,小型化工艺还增加了器件对静电放电(ESD)事件的敏感性。ESD是电子电路损坏的原因之一,也是半导体先进技术中的考虑因素之一。

发明内容

根据本发明实施例的一个方面,提供了一种骤回静电放电(ESD)保护电路,包括:第一阱,位于衬底中,第一阱具有第一掺杂剂类型;晶体管的漏极区,漏极区在第一阱中,并且具有不同于第一掺杂剂类型的第二掺杂剂类型;晶体管的源极区,源极区在第一阱中,具有第二掺杂剂类型,并且在第一方向上与漏极区分开;晶体管的栅极区,栅极区在第一阱和衬底上方;以及第二阱,嵌入在第一阱中,并且与漏极区的部分相邻,并且第二阱具有第二掺杂剂类型。

根据本发明实施例的另一个方面,提供了一种静电放电(ESD)保护电路,包括:第一阱,位于衬底中,第一阱具有第一掺杂剂类型;第一晶体管的漏极区,漏极区位于第一阱中,并且具有与第一掺杂剂类型不同的第二掺杂剂类型;第一晶体管的源极区,源极区在第一阱中,具有第二掺杂剂类型,并且在第一方向上与漏极区分开;第一晶体管的栅极区,栅极区在第一阱和衬底上方;第二阱,嵌入在第一阱中,并且与源极区的部分相邻,并且第二阱具有第二掺杂剂类型;以及抽头阱,位于第一阱中且具有第一掺杂剂类型,并且耦接到源极区。

根据本发明实施例的又一个方面,提供了一种制造骤回ESD保护电路的方法,方法包括:在衬底中制造第一阱,第一阱在第一方向上延伸,并且具有第一掺杂剂类型;在第一阱中制造晶体管的漏极区,漏极区在第一方向上延伸,并且具有不同于第一掺杂剂类型的第二掺杂剂类型;在第一阱中制造晶体管的源极区,源极区在第一方向上延伸,具有第二掺杂剂类型,并且在不同于第一方向的第二方向上与漏极区分开;在第一阱中制造第二阱,第二阱在第一方向上延伸,具有第二掺杂剂类型,并且与漏极区的部分相邻,以及制造晶体管的栅极区,栅极区在漏极区和源极区之间,并且在第一阱和衬底上方。

附图说明

当结合附图进行阅读时,从以下详细描述可最佳理解本发明的各个方面。应该强调,根据工业中的标准实践,各个部件未按比例绘制并且仅用于说明的目的。实际上,为了清楚的讨论,各个部件的尺寸可以任意地增大或减小。

图1A是根据一些实施例的集成电路的示意框图。

图1B是根据一些实施例的集成电路的部分的等效电路的电路图。

图2A是根据一些实施例的集成电路的截面图。

图2B是根据一些实施例的集成电路的等效电路的截面图。

图2C是与其他方法相比的一些实施例的波形图。

图3A是根据一些实施例的具有多个骤回器件单元的骤回器件阵列的框图。

图3B是根据一些实施例的布局设计的图。

图4A是根据一些实施例的集成电路的示意框图。

图4B是根据一些实施例的布局设计的图。

图5A是根据一些实施例的集成电路的截面图。

图5B是根据一些实施例的集成电路的等效电路的截面图。

图5C是根据一些实施例的布局设计的图。

图6A是根据一些实施例的集成电路的截面图。

图6B是根据一些实施例的集成电路的等效电路的截面图。

图6C是根据一些实施例的布局设计的图。

图7A-图7C是根据一些实施例的对应布局设计的对应图。

图8A-图8C是根据一些实施例的对应布局设计的对应图。

图9是根据一些实施例的形成或制造ESD电路的方法的流程图。

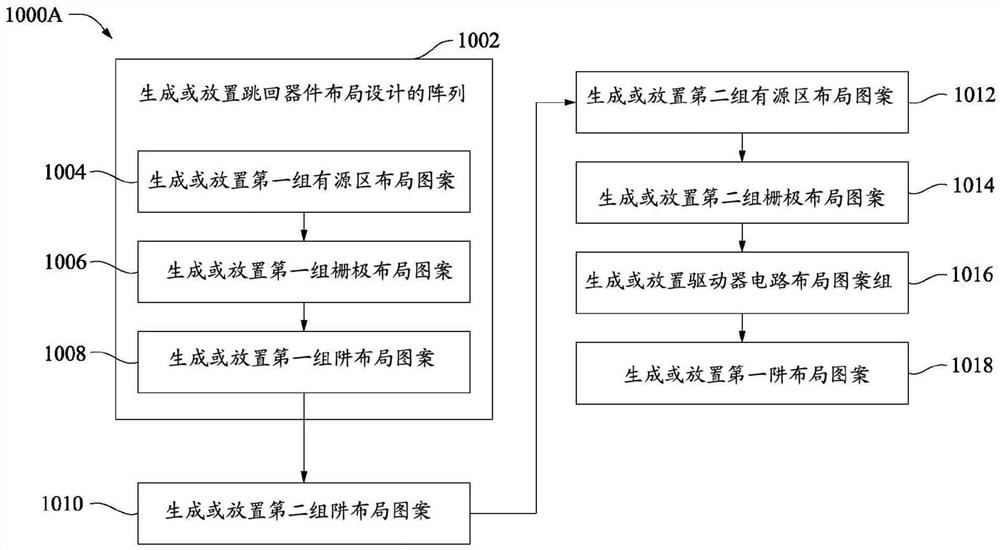

图10A是根据一些实施例的集成电路设计和制造流程的至少部分的功能流程图。

图10B是根据一些实施例的制造集成电路器件的方法的功能流程图。

图11是根据一些实施例的操作电路的方法的流程图。

图12是根据一些实施例的用于设计IC布局设计和制造IC电路的系统的示意图。

图13是根据本公开的至少一个实施例的集成电路(IC)制造系统以及与其相关联的IC制造流程的框图。

具体实施方式

以下公开内容提供了许多用于实现本发明的不同特征不同的实施例或实例。下面描述了组件和布置的具体实施例或实例以简化本发明。当然,这些仅是实例而不旨在限制。例如,在以下描述中,在第二部件上方或者上形成第一部件可以包括第一部件和第二部件直接接触形成的实施例,并且也可以包括在第一部件和第二部件之间可以形成附加部件,从而使得第一部件和第二部件可以不直接接触的实施例。此外,本发明可以在各个示例中重复参考数字和/或字母。该重复是为了简单和清楚的目的,并且其本身不指示讨论的各个实施例和/或配置之间的关系。

此外,为了便于描述,本文中可以使用诸如“在...下方”、“在...下面”、“下部”、“在...上面”、“上部”等的间隔关系术语,以描述如图中所示的一个元件或部件与另一元件或部件的关系。除了图中所示的方位外,间隔关系术语旨在包括器件在使用或操作工艺中的不同方位。器件可以以其它方式定位(旋转90度或在其它方位),并且在本文中使用的间隔关系描述符可以同样地作相应地解释。

在ESD保护器件中要考虑的参数是ESD阈值电压或触发电压,在该阈值电压或ESD电压下,ESD保护器件被接通,即变为导通,以释放高和有害的ESD事件的电压和/或电流远离要保护的电路。高ESD触发电压可能对要保护的电路有害,和/或可能导致ESD保护器件本身导通不均匀和/或过早失效。在一些实施例中,为了减小ESD阈值电压或触发电压,将附加N阱添加到ESD保护器件的P阱,从而增加ESD保护器件的寄生双极结晶体管(BJT)的基极电阻。

在一些实施例中,在ESD事件期间,增加寄生BJT的基极电阻会降低寄生BJT的ESD阈值电压,从而导致寄生BJT在更低的ESD触发电压下更早地导通,并且ESD电压能够比其他方法更快地被放电。换句话说,ESD触发电压降低,从而提高了ESD性能。与其他方法相比,至少一个或多个实施例有利地提供了布局设计或布局解决方案,用于在不进行附加制造工艺的情况下降低骤回(snapback)器件的ESD触发电压,并具有改善的ESD性能。

图1A是根据一些实施例的集成电路100A的示意框图。

集成电路100A包括内部电路102、电压源端子104、参考电压源端子106、输入/输出(IO)焊盘108、ESD钳位器110和骤回器件120。在一些实施例中,至少集成电路100A、100B(图1B)或400A(图4A)被并入单个集成电路(IC)或单个半导体衬底上。在一些实施例中,至少集成电路100A、100B或400A包括并入在一个或多个单个半导体衬底上的一个或多个IC。

内部电路102耦合到电压源端子104(例如VDD)、参考电压源端子106(例如VSS)和IO焊盘108。内部电路102配置为接收来自电压源端子104的电源电压VDD(例如,VDD)、来自参考电压源端子106(例如,VSS)的参考电压VSS和来自IO焊盘108的IO信号。

内部电路102包括被配置为生成或处理由IO焊盘108接收或输出到IO焊盘108的IO信号的电路。在一些实施例中,内部电路102包括被配置为以低于电压源端子104的电源电压VDD的电压工作的核心电路。在一些实施例中,内部电路102包括至少一个n型或p型晶体管器件。在一些实施例中,内部电路102至少包括逻辑门单元。在一些实施例中,逻辑门单元包括与(AND)、或(OR)、与非(NAND)、或非(NOR)、异或(XOR)、反相(INV)、与或反相(AOI)、或与反相(OAI)、复用器(MUX)、触发器、缓冲器(BUFF)、锁存器、延迟或时钟单元。在一些实施例中,内部电路102至少包括存储器单元。在一些实施例中,存储器单元包括静态随机存取存储器(SRAM)、动态RAM(DRAM)、电阻RAM(RRAM)、磁阻RAM(MRAM)或只读存储器(ROM)。在一些实施例中,内部电路102包括一个或多个有源或无源元件。有源元件的示例包括但不限于晶体管和二极管。晶体管的示例包括但不限于金属氧化物半导体场效应晶体管(MOSFET)、互补金属氧化物半导体(CMOS)晶体管、双极结型晶体管(BJT)、高压晶体管、高频晶体管、p沟道和/或或n沟道场效应晶体管(PFET/NFET)等)、FinFET和源/漏电压升高的平面MOS晶体管。无源元件的示例包括但不限于电容器、电感器、熔断器和电阻器。

电压源端子104被配置为接收用于内部电路102的正常操作的电源电压VDD。类似地,参考电压源端子106被配置为接收用于内部电路102的正常操作的参考电源电压VSS。在一些实施例中,至少电源端子104是电压源焊盘。在一些实施例中,至少参考电压源端子106是参考电压源焊盘。在一些实施例中,焊盘至少是导电表面、引脚、节点或总线。电压源端子104或参考电压源端子106也被称为电源电压总线或电源电压轨。在图1A-1B和图4A的示例配置中,电源电压VDD是正电源电压,电压源端子104是正电源电压,参考电源电压VSS是接地电源电压,参考电压源端子106是接地电压端子。其他电源布置在本公开的范围内。

IO焊盘108耦合到内部电路102。IO焊盘108被配置为从内部电路102接收IO信号,或者被配置为向内部电路102输出IO信号。IO焊盘108是至少一个耦合到内部电路102的引脚。在一些实施例中,IO焊盘108是耦合到内部电路102的节点、总线或导电表面。

ESD钳位器110耦合在电压源端子104(例如,电源电压VDD)和参考电压源端子106(例如,VSS)之间。如果发生ESD事件,则ESD钳位器110被配置为在电压源端子104(例如,电源电压VDD)和参考电压源端子106(例如,VSS)之间提供分流路径。当没有ESD事件发生时,ESD钳位器110应被关闭。例如,当没有ESD事件发生时,ESD钳位器110被关闭,并且因此在内部电路102的正常操作期间是不导电的器件或电路。当发生ESD事件时,ESD钳位器110应该被接通以释放ESD电流。例如,当发生ESD事件时,ESD钳位器110两端的电压差等于或大于ESD钳位器110的阈值电压,并且ESD钳位器110被接通,从而在电压源端子104(例如,VDD)和参考电压源端子106(例如VSS)之间传导电流。

在一些实施例中,ESD钳位器110包括大的NMOS晶体管,其被配置为在不进入ESD钳位器110的雪崩击穿区域的情况下承载ESD电流。在一些实施例中,ESD钳位器110被实现为在ESD钳位器110内部不具有雪崩结,也称为“无骤回保护方案”。

骤回器件120耦合在IO焊盘108和参考电压源端子106之间。骤回器件120被配置为对内部电路102或集成电路100A-100B或400A的正常行为(例如,没有ESD条件)具有最小的影响。换句话说,骤回器件120在没有ESD事件的情况下被关闭或不导通。在内部电路102的正常操作施加到IO焊盘108期间,当ESD电压或电流高于预期的电压或电流水平时,会发生ESD事件。在没有骤回器件120的情况下,这样的ESD事件会导致过度的和潜在的损坏内部电路102和/或驱动器电路440(图4A)中的电压或电流。在ESD条件下,骤回器件120被配置为接通并表现出骤回。换句话说,在ESD条件下,骤回器件120被配置为接通,并且在骤回器件120的雪崩击穿区域中操作,从而承载将通过骤回器件120而不是通过内部电路102放电的大电流ESD电流。

在一些实施例中,骤回器件120被配置为在发生ESD应力或事件的正-VSS(PS)模式时接通或操作。例如,在PS模式下,正ESD应力或ESD电压(至少大于参考电源电压VSS)被施加到IO焊盘108,而电压源端子104(例如,VDD)浮置并且参考电压源端子106(例如VSS)接地。至少在该示例中,当ESD电压大于骤回器件120的ESD触发电压Vth或的阈值电压时,骤回器件120被接通并且通过接通的骤回器件120将IO焊盘108上的ESD电压放电至参考电压源端子106(例如,VSS),如图1A中的箭头“PS模式”所示。

在一些实施例中,当发生ESD应力或事件的负-VSS(NS)模式时,骤回器件120被禁用或被配置为关闭或不工作。在一些实施例中,当ESD应力或事件的NS模式发生时,骤回器件120被关闭或不可操作。在NS模式下,IO焊盘108接收负ESD应力,而电压源端子104(例如,VDD)浮置并且参考电压源端子106(例如,VSS)接地。

在一些实施例中,骤回器件120包括但不限于具有寄生NPN BJT、骤回MOS器件、场氧化物器件(FOD)、可控硅整流器(SCR)等的骤回器件。

在一些实施例中,集成电路100A还包括与骤回器件120类似的附加骤回器件(未示出),但是耦合在IO焊盘108和电压源端子104之间。在一些实施例中,附加骤回器件(未示出)的截面图类似于集成电路200A-200B(图2A-2B)。

在一些实施例中,附加骤回器件被配置为在发生ESD应力或事件的正-VDD(PD)模式时接通或操作。例如,在PD模式下,正ESD应力或ESD电压(至少大于电源电压VDD)被施加到IO焊盘108,而电压源端子104(例如VDD)接地并且参考电压源端子106(例如VSS)浮置。至少在该示例中,当ESD电压大于附加骤回器件的ESD触发电压Vth或阈值电压时,附加骤回器件被接通并且通过被接通的附加骤回器件来释放IO焊盘108上的ESD电压到电压源端子104(例如,VDD)。

在一些实施例中,当发生ESD应力或ESD事件的负-VDD(ND)模式时,附加骤回器件被禁用或被配置为关闭或不操作。在一些实施例中,当ESD应力或ESD事件的ND模式发生时,附加骤回器件被关闭或不操作。在ND模式下,IO焊盘108接收负ESD应力,而电压源端子104(例如,VDD)接地并且参考电压源端子106(例如,VSS)浮置。

在一些实施例中,附加骤回器件包括但不限于具有寄生NPN BJT、骤回MOS器件、场氧化器件(FOD)、可控硅整流器(SCR)等的骤回器件。

图1B是根据一些实施例的集成电路100A的部分的等效电路100B的电路图。

等效电路100B是集成电路100A的变体,并且示出了骤回器件120的寄生晶体管140,因此省略了类似的详细描述。例如,根据一些实施例,等效电路100B对应于图1A的骤回器件120,具有寄生元件(例如,寄生晶体管140)。

对与图1A-1B、图2B-2C、图3、图4A-4B、图5A-5C、图6A-6C、图7A-7C、图8A-8C和图9-13(如下所示)中的一个或多个相同或类似的组件,给予相同的附图标记,并因此省略其详细描述。

等效电路100B包括IO焊盘108、参考电压源端子106、骤回器件120和寄生晶体管140。

寄生晶体管140是双极结型晶体管(BJT)。在一些实施例中,寄生晶体管140是NPN寄生晶体管。寄生晶体管140包括对应于骤回器件120的漏极区的BJT的集电极、对应于骤回器件120的源极区的BJT的发射极、对应于骤回器件120的P阱和P衬底的BJT的基极、以及对应于骤回器件120的P阱和P衬底的电阻的基极电阻器Rb。

寄生晶体管140的集电极耦合到IO焊盘108。基极电阻器Rb耦合在寄生晶体管140的基极和寄生晶体管140的发射极之间。寄生晶体管140的发射极还耦合到参考电压源端子106。

在一些实施例中,在正ESD应力期间(例如PS模式),当ESD电压大于寄生晶体管140的ESD触发电压Vth或阈值电压时,寄生晶体管140接通,从而放电ESD电压到参考电压源端子106(例如,VSS)。

寄生晶体管140的触发电压Vth与基极电流Ib和基极电阻Rb中的每个成反比。例如,至少基极电流Ib或基极电阻Rb的减小导致寄生晶体管140的触发电压Vth增大。例如,至少基极电流Ib或基极电阻Rb的增大导致寄生晶体管140的触发电压Vth减小。在一些实施例中,为了减小ESD触发电压Vth,在骤回器件120中包括N阱(图2A-2B),其减小了P-晶体管的有效面积。在一些实施例中,通过减小骤回器件120内的P阱(图2A-2B)的有效面积,使得基极电阻Rb增加,并且通过减小骤回器件120内的P阱(图2A-2B)的有效面积,并且当不包括附加N阱(图2A-2B)时,触发电压Vth降低。

与其他方法相比,至少一个实施例有利地提供了一种用于降低ESD触发电压Vth的设计技术共同优化解决方案,而无需包括调谐过程在内的其他制造过程。

在至少一个实施例中,较低的ESD触发电压Vth有利地避免了在其他方法中与较高的ESD触发电压Vth相关的一个或多个问题,包括但不限于对要保护的电路的潜在损坏、非均匀接通或ESD保护器件本身过早出现故障。

图2A是根据一些实施例的集成电路200A的截面图。图2B是根据一些实施例的集成电路200A的等效电路200B的截面图。例如,等效电路200B对应于具有寄生BJT 240的集成电路200A。例如,与图2B相比,为了便于说明,图2A的集成电路200A未示出图2B的寄生BJT240。图2C是与其他方法相比的一些实施例的波形图200C。

集成电路200A是骤回器件120的实施例。

集成电路200A包括衬底202。衬底202是p型衬底。在一些实施例中,衬底202是n型衬底。在一些实施例中,衬底202包括元素半导体,包括晶体、多晶或非晶结构中的硅或锗;化合物半导体,包括碳化硅、砷化镓、磷化镓、磷化铟、砷化铟和锑化铟;合金半导体,包括SiGe、GaAsP、AlInAs、AlGaAs、GaInAs、GaInP和GaInAsP的;任何其他合适的材料;或其组合。在一些实施例中,合金半导体衬底具有梯度SiGe特征,其中Si和Ge组成从梯度SiGe特征的一个位置处的一个比率改变为另一位置处的另一比率。在一些实施例中,合金SiGe形成在硅衬底上方。在一些实施例中,衬底202是应变SiGe衬底。在一些实施例中,半导体衬底具有绝缘体上半导体结构,例如绝缘体上硅(SOI)结构。在一些实施例中,半导体衬底包括掺杂的外延层或掩埋层。在一些实施例中,化合物半导体衬底具有多层结构,或者衬底包括多层化合物半导体结构。

集成电路200A在衬底202中还包括P阱204和N阱206。N阱206与P阱204相邻。P阱204在第一方向X上具有宽度W0,并且N阱206在第一方向X上具有宽度W1'。在一些实施例中,宽度W0大于宽度W1'。P阱204具有与N阱206的掺杂杂质类型相反的掺杂杂质类型。N阱206包括n型掺杂杂质,并且P阱包括p型掺杂杂质。

N阱206位于晶体管260的漏极侧。在一些实施例中,通过将N阱206包括在集成电路200A中,减小了集成电路200A中的P阱204的有效面积,从而在ESD事件期间增加了P阱204和衬底202的基极电阻Rb。与不包括N阱206时相比,通过增加基极电阻Rb导致在ESD事件期间集成电路200A的触发电压Vth1减小。

集成电路200A还包括在P阱204上方的栅极结构230。栅极结构230包括栅极电介质222和栅电极230a。集成电路200A还包括在栅极结构230的相对侧上的侧壁。

集成电路200A还包括漏极区212和源极区214。源极区214是具有注入到P阱204中的N型掺杂剂的N型有源区。漏极区212是在至少P阱204或N阱206中注入有N型掺杂剂的N型有源区。在一些实施例中,至少源极区214或漏极区212在衬底202上方延伸。在一些实施例中,N阱206嵌入在P阱204中。在一些实施例中,N阱206与漏极区212的部分相邻。在一些实施例中,第一元件与第二元件相邻对应于第一元件直接在第二个元件旁边。在一些实施例中,第一元件与第二元件相邻对应于第一元件不直接紧邻第二元件。在一些实施例中,N阱206直接接触漏极区212的部分。

在一些实施例中,图2A至图2B的晶体管260的漏极区212和源极区214被称为氧化物定义(OD)区域,其限定了图4A(下面描述)的集成电路200A-200B或NMOS晶体管N1的源极或漏极扩散区域。

在一些实施例中,集成电路200A还包括与源极区214和漏极区212相邻并且在侧壁220下方的轻掺杂漏极(LDD)区域218。在一些实施例中,LDD区域360帮助晶体管260保持低漏电流。

集成电路200A还包括在P阱204上的P阱抽头216、浅沟槽隔离(STI)区域208和210。STI区域208被配置为将漏极区212与集成电路200A的其他部分(未显示)隔离。STI区域210被配置为将源极区214与集成电路200A的其他部分隔离。在一些实施例中,区域210被配置为将源极区214与抽头区域216隔离。图2A至图2B及图2至图3B为一实施例。图5A-5B示出了STI区域208在N阱206内,在一些实施例中,STI区域208不在N阱206内。在一些实施例中,STI区域208邻近N阱206或直接在其附近。在实施例中,N阱206位于漏极区212和STI区域208之间。在一些实施例中,STI区域208不形成在与N阱206相同的区域或空间中。在一些实施例中,STI区域208不形成在N阱206中。在一些实施例中,集成电路200A或200B不包括STI区域208或210。

在一些实施例中,漏极区212、源极区214、LDD区域218、侧壁220和栅极结构230一起形成晶体管260。在一些实施例中,晶体管260是NMOS晶体管。在一些实施例中,晶体管260是PMOS晶体管。在一些实施例中,晶体管260对应于图1A-图1B的骤回器件120。在一些实施例中,晶体管260对应于图4A的驱动器器件440。

在一些实施例中,漏极区212耦合到IO焊盘108,并且源极区214和抽头区域216耦合到参考电压源端子106(例如,电压VSS)。在一些实施例中,栅极结构230还耦合到源极区214、抽头区域216和参考电压源端子106(例如,电压VSS),并且因此对应于接地栅极NMOS(ggNMOS)器件。

在一些实施例中,根据鳍式场效应晶体管(FinFET)互补金属-氧化物-半导体(CMOS)技术,漏极区212和源极区214包括鳍。在一些实施例中,漏极区212和源极区214包括纳米片晶体管的纳米片。在一些实施例中,漏极区212和源极区214包括纳米线晶体管的纳米线。在一些实施例中,根据平面CMOS技术,漏极区212和源极区214没有鳍。其他类型的晶体管在本公开的范围内。

在一些实施例中,漏极区212是延伸的漏极区,并且具有比源极区214更大的尺寸。在至少一个实施例中,硅化物层(未示出)覆盖漏极区212的部分,但不是全部。漏极区212的这种部分硅化的配置改善了晶体管260对ESD事件的自我保护。在至少一个实施例中,漏极区212被完全硅化。

栅极结构230布置在漏极区212和源极区214之间。在一些实施例中,栅电极230a包括诸如金属或多晶硅(在本文中也称为“POLY”)的导电材料。在一些实施例中,栅极结构230耦合到电压源端子104(例如,电压VDD)或参考电压源端子106(例如,电压VSS)。在一些实施例中,如相对于图4A所描述的,栅极结构230耦合到外部控制电路。

图2B是根据一些实施例的集成电路200A的等效电路200B的截面图。例如,与图2B相比,图2A的集成电路200A未示出图2B的寄生BJT 240。

集成电路200B包括集成电路200A、寄生BJT 240(以下称为“BJT 240”)和寄生基极电阻器Rb。

BJT 240包括基极242、集电极244和发射极246。BJT240是寄生晶体管140的实施例,因此省略类似的详细描述。与图1B的集成电路100B的寄生晶体管140相比,基极242代替了寄生晶体管140的基极,集电极244代替了寄生晶体管140的集电极,并且发射极246代替了寄生晶体管140的发射极,省略了类似的详细描述。图2B的基极电阻Rb对应于图1B的基极电阻Rb,因此省略了类似的详细描述。

BJT 240是由至少P阱204和衬底202中的N型漏极区212和N型源极区214形成的NPN寄生BJT。P阱204和衬底202对应于BJT 240的基极242,晶体管260的漏极区212对应于BJT240的集电极244,晶体管260的源极区214对应于BJT 240的发射极246。

IO焊盘108通过导电区域270耦合到漏极区212,从而将IO焊盘108耦合到BJT 240的集电极244。参考电压源106(例如,VSS)通过导电区域272耦合到源极区214和P阱抽头216,从而将BJT 240的发射极246耦合到参考电压源106(例如,VSS)。换句话说,集电极244和发射极246耦合在IO焊盘108和参考电压源106(例如,VSS)之间。

基极电阻Rb至少对应于P阱204的电阻或衬底202的衬底电阻。基极电阻Rb耦合在基极242和P阱抽头216之间。由于参考电压源106(例如,VSS)耦接至源极区214和P阱抽头216,基极电阻Rb两端的电压降对应于BJT 240的基极242和发射极246之间的基极-发射极电压Vbe。

在没有ESD事件的情况下,BJT 240的Vbe低于BJT 240的阈值电压或触发电压,因此BJT 240截止。例如,在一些实施例中,Vbe为零,并且BJT 240截止。在一些实施例中,如关于图1A-1B所描述,当晶体管260的栅极结构230耦合到参考电压源端子106(例如,VSS)时,晶体管260也截止而不影响内部电路140的正常操作。当晶体管260的栅极结构230被配置为从驱动器电路(未示出)接收驱动器控制信号DRV(如参照图4A所描述)时,响应于驱动器控制信号DRV而导通或截止晶体管260,以在内部电路140的正常操作期间将IO焊盘108的电压可控制地拉至参考电压源端子106的参考电压VSS。

在ESD事件中,向IO焊盘108施加ESD电压。IO焊盘108上的ESD电压比栅极结构230的电压高得多,并产生强电场。强电场可能导致移动电荷载流子猛烈撞击紧密相连的电荷载流子,然后这些电荷载流子会断裂。该过程导致产生新的电荷载流子,并重复进行直到雪崩击穿发生并产生雪崩电流为止。当将ESD电压施加到IO焊盘108时,N型漏极区212和P阱204之间的PN结被反向偏置,直到雪崩击穿发生为止。此时,漏极电流增加,产生的空穴向BJT 240的基极242漂移。来自雪崩击穿的带正电的空穴流在BJT 240的基极电阻Rb两端引起电压降。由于基极242的电压增大导致BJT 240的基极-发射极结变得更正向偏置,导致BJT 240的基极-发射极结达到阈值电压,从而使BJT 240导通并将ESD电流I1从集电极244放电到发射极246。来自ESD事件的高电流被重定向离开晶体管260的栅极结构230。在一些实施例中,基极电阻Rb通过降低BJT 240的集电极-发射极触发电压来控制触发BJT 240的雪崩模式的速度。例如,通过增加基极电阻Rb,使BJT 240的触发雪崩模式的速度增加,从而使BJT 240以较低的阈值电压导通并且比其他方法更快地释放ESD电流I1。

在一些实施例中,BJT 240的基极电阻Rb两端的电压降对应于Vbe。IO焊盘108上的ESD电压越高,Vbe越高。当Vbe达到BJT 240的阈值电压时,BJT 240导通并导致ESD电流I1从漏极区212流到源极区214。结果,IO焊盘108上的ESD电压通过导通BJT 240而放电到参考电压源端子106(例如,VSS)。Vbe达到BJT 240的阈值电压的电压是图1A-1B的晶体管260或骤回器件120的ESD触发电压。

结果,在相同的ESD电压下,其他方法中的Vbe低于包括N阱206的实施例中的Vbe。换句话说,包括N阱206的实施例允许Vbe以较低的ESD电压达到BJT 240的阈值电压,因此,与其他方法相比,具有较低的ESD触发电压。在至少一个实施例中,较低的ESD触发电压有利地避免了在其他方法中与较高的ESD触发电压相关的一个或多个问题,包括但不限于对要保护的电路的潜在损坏、不均匀的导通、ESD保护器件本身的早期故障。

图2C是与其他方法相比的一些实施例的波形图200C。

根据一些实施例,波形图200C包括集成电路200A的电流电压(I-V)特性曲线。波形图200C还包括其他方法的I-V特性曲线282。

如图2C所示,x轴对应于漏极电压,y轴对应于漏极电流。

如图2C所示,当漏极电压具有曲线280的电压值Vt1时,BJT 240导通,而当其他方法的晶体管的漏极电压具有曲线282的电压值Vt2时,其他方法的寄生BJT导通。曲线280的电压值Vt1和曲线282的电压值Vt2小于晶体管260的破坏性电压Vb1。

如图2C所示,一旦BJT 240导通,就不存在开始雪崩过程的高电场来维持漏极电流,这被称为骤回。例如,漏极电流在比电压Vt1低的漏极电压下增加。因此,漏极电压减小到保持电压Vh,并且观察到骤回行为。在BJT 240导通之后,漏极电压的增加还增加了漏极电流,直到在电压Vt2处发生对晶体管260的热损坏为止。在一些实施例中,保持电压Vh大于电源电压VDD,从而防止晶体管260导通并防止闩锁。

在一些实施例中,通过在晶体管260中包括N阱206,减小了晶体管260中的P阱204的有效面积,从而增加了P阱204和衬底202的基极电阻Rb。与在相同的ESD触发电压下的其他方法相比,该方法导致在ESD事件期间晶体管260的触发电压Vth的减小。与其他方法相比,至少一个实施例有利地提供了一种用于降低ESD触发电压Vth的设计技术共同优化解决方案,而无需包括调谐过程在内的附加制造过程。在至少一个实施例中,较低的ESD触发电压Vth有利地避免了在其他方法中与较高的ESD触发电压Vth相关的一个或多个问题,包括但不限于对要保护的电路的潜在损坏、不均匀的导通、ESD保护器件本身的早期故障。

图3A是根据一些实施例的具有多个骤回器件单元(例如,集成电路200A-200B)的骤回器件阵列300’的框图。例如,图1A-1B的骤回器件120和寄生晶体管130或2A-2B的集成电路200A-200B可用作骤回器件阵列301中的一个或多个骤回器件。

骤回器件阵列301'包括具有M'行和N'列的骤回器件301[1,1]',301[1,2]',...,301[2,2]',...,301[M',N']的阵列(统称为“骤回器件301A'的阵列”),其中N'是与骤回器件301A'的阵列中的列数相对应的正整数,M’是与骤回器件301A'的阵列中的行数相对应的正整数。骤回器件301A'的阵列中单元的行沿第一方向X布置。骤回器件301A'的阵列中单元的列沿第二方向Y布置。第二方向Y不同于第一方向X。在一些实施例中,第二方向Y垂直于第一方向X。

在一些实施例中,骤回器件301A'的阵列中的每个骤回器件301[1,1]',301[1,2]',...,301[2,2]',...,301[M',N']'包括相应的晶体管260。

在一些实施例中,位于阵列的外围的骤回器件301A'的阵列中的每个骤回器件301[1,1]',301[1,2]',...,301[2,2]',...,301[M',N']'包括类似于集成电路200A-200B的电路,并且位于阵列的外围的骤回器件301A'的阵列中的每个骤回器件301[1,1]',301[1,2]',...,301[2,2]',...,301[M',N']'包括与没有P阱抽头216的集成电路200A-200B类似的电路,并且类似的详细因此省略描述。

骤回器件阵列301'中的骤回器件单元的不同类型在本公开的预期范围内。

图3B是根据一些实施例的布局设计300B的图。

布局设计300B是图3A的骤回器件阵列300A的布局图。布局设计300B可用于制造图3A的骤回器件阵列300A。在一些实施例中,布局设计300B的部分可用于制造图1A-1B的骤回器件120和寄生晶体管130。图1A至图1B的集成电路或者图2A-2B的集成电路200A至200B。在一些实施例中,图3B包括图3A中未示出的附加元件。

至少集成电路100A-100B(图1A-1B)、200A-200B(图2A-2B)、400A(图4A)、500A-500B(图5A-5B)或600A-600B(图6A-6B)或骤回器件阵列300A(图3A)的结构关系(包括对准、距离、长度、宽度和节距)以及配置与至少布局设计300B(图3B)、400B(图4B)、500C(图5C)、600C(图6C)、700A-700C(图7A-7C)或800A-800C(图8A-8C)的相应结构关系和相应配置类似,并且为了简洁,类似的详细描述将在图1A-1B、图2A-2C、图3A-3B、图4A-4B、图5A-5C、图6A-6C、图7A-7C、图8A-8C和图9-图13中省略。

布局设计300B包括骤回器件布局阵列301。骤回器件布局阵列301包括具有M行和N列的骤回器件布局设计301[1,1],301[1,2],...,301[2,2],...,301[M,N]的阵列(统称为“骤回器件布局设计301A的阵列”),其中N是与骤回器件布局设计301A的阵列中的列数相对应的正整数,M是与骤回器件布局设计301A的阵列中的行数相对应的正整数。骤回器件布局设计301A的阵列中单元的行沿第一方向X布置。骤回器件布局设计301A的阵列中单元的列沿第二方向Y布置。在一些实施例中,至少M或N等于图4A的M'或N'。

在一些实施例中,骤回器件布局设计301A的阵列中的每个骤回器件布局设计301[1,1],301[1,2],...,301[2,2],...,301[M,N]可用于制造骤回器件301A'的阵列中相应的骤回器件301[1,1]',301[1,2]',...,301[2,2]',...,301[M',N']'。

在一些实施例中,骤回器件布局设计301A的阵列中的每个骤回器件布局设计301[1,1],301[1,2],...,301[2,2],...,301[M,N]包括相应的晶体管260的布局设计。

在一些实施例中,骤回器件布局设计301A的阵列中的每个骤回器件布局设计301[1,1],301[1,2],...,301[2,2],...,301[M,N]包括相应集成电路200A-200B的相应布局设计。

骤回器件布局阵列301中的每个布局设计对应于集成电路200A或200B的布局设计。在一些实施例中,集成电路200A或等效电路200B的截面图对应于与平面A-A’相交的布局设计300B。

图3B示出了骤回器件布局设计301[1,1],301[1,2],301[2,2]和301[2,2]的细节,并且为简洁,省略了骤回布局器件阵列301中的其他骤回器件布局设计的细节。但是,骤回布局器件阵列301中其他骤回器件布局设计的细节与骤回器件布局设计301[1,1],301[1,2],301[2,2]和301[2,2]的细节类似,因此省略类似的详细描述。

在一些实施例中,骤回器件布局设计301[1,1]和301[1,2]包括有源区布局图案312a。在一些实施例中,骤回器件布局设计301[2,1]和301[2,2]包括有源区布局图案312b。

在一些实施例中,骤回器件布局设计301[1,1]和301[2,1]包括阱布局图案316a。在一些实施例中,骤回器件布局设计301[1,1]和301[2,1]包括栅极布局图案330a和330b,以及栅极布局图案330c的至少部分。

在一些实施例中,骤回器件布局设计301[1,2]和301[2,2]包括阱布局图案316b。在一些实施例中,骤回器件布局设计301[1,2]和301[2,2]包括栅极布局图案330d,以及栅极布局图案330c和330e的至少部分。

骤回器件布局设计301的阵列中的骤回器件布局设计的不同类型在本公开的预期范围内。

布局设计300B至少包括在第二方向Y上延伸的有源区布局图案312a或312b(统称为“有源区布局图案组312”)。有源区布局图案组312的有源区布局图案312a或312b在第二方向Y上彼此分离。

在一些实施例中,有源区布局图案组312的每个有源区布局图案的端与有源区布局图案组312的相邻有源区布局图案的端在方向Y上以距离D1分开。

在一些实施例中,有源区布局图案312a可用于制造图2A-2B的晶体管260的有源区(例如,漏极区212和源极区214)。在一些实施例中,有源区布局图案312b可用于制造图2A-2B的晶体管260的有源区(例如,漏极区212和源极区214)或图4A的NMOS晶体管N1的漏极区和源极区。

在一些实施例中,至少有源区布局图案312a或312b对应于P阱204。有源区布局图案312a或312b是骤回器件布局阵列301的相应行1或行2的部分。

在一些实施例中,至少有源区布局图案312a或312b是在第一方向X上延伸的连续布局图案。在一些实施例中,至少有源区布局图案312a或312b包括在第一方向X上延伸的至少N个不连续的布局图案,其中N对应于骤回器件布局阵列301中的列数。

在一些实施例中,有源区布局图案组312位于第一层上。在一些实施例中,第一层级对应于布局设计300B、400B、500C、600C、700A-700C或800A-800C(图3B、图4B、图5C、图6C、图7A-7C或图8A-8C)中的一个或多个的有源层级或OD层级或集成电路200A-200B、500A-500B、600A-600B(图2A-2B、图5A-5B或图6A-6B)。

至少有源区布局图案组312中的图案的其他配置、水平或数量在本公开的范围内。

布局设计300B还至少包括分别在第二方向Y上延伸的栅极布局图案330a、330b、330c、330d或330e(统称为“栅极布局图案组330”)。栅极布局图案组330的图案在第一方向X上与栅极布局图案组330的相邻栅极布局图案分开第一节距。在一些实施例中,栅极布局图案组330的每个栅极布局图案的端部与栅极布局图案组330的相邻栅极布局图案的端部在第一方向X上以节距P1分开。

在一些实施例中,至少栅极布局图案330a、330b、330c、330d或330e可用于制造类似于栅极结构230的栅极。在一些实施例中,至少栅极布局图案330a、330b、330c、330d或330e 330e可用于制造类似于图4A中的NMOS晶体管N1的栅极的栅极。在一些实施例中,至少栅极布局图案330a、330c和330e可用于制造图2A-2B中的伪栅极结构(未示出)。

栅极布局图案330b或330d是骤回器件布局阵列301的相应列1或列2的部分。在一些实施例中,栅极布局图案330a或330c的至少部分是骤回器件布局阵列301的列1的部分。在一些实施例中,栅极布局图案330c或330e的至少部分是骤回器件布局阵列301的列2的部分。

栅极布局图案组330位于与第一层级不同的第二层级(POLY)上。栅极布局图案组330与有源区布局图案组312重叠。在一些实施例中,第二层级对应于布局设计300B、400B、500C、600C、700A-700C或800A-800C(图3B、图4B、图5C、图6C、图7A-7C或图8A-8C)或集成电路200A-200B、500A-500B、600A-600B(图2A-2B、图5A-5B或图6A-6B)中的一个或多个的POLY层级。

栅极布局图案组330中的图案的其他配置、水平或数量在本公开的范围内。

布局设计300B还至少包括分别在第二方向Y上延伸的阱布局图案316a或316b(统称为“阱布局图案组316”)。阱布局图案组316中的每个阱布局图案在第一方向X上与阱布局图案组316的相邻的阱布局图案分开。阱布局图案组316的每个阱布局图案具有在第一方向X上延伸的宽度W1。至少阱布局图案316a或316b可用于制造N阱206。宽度W1小于节距P1。在一些实施例中,宽度W1等于间距P1。

在一些实施例中,阱布局图案组316与有源区布局图案组312重叠。阱布局图案316a在栅极布局图案330b和330c之间。阱布局图案316b在栅极布局图案330d和330e之间。阱布局图案316a或316b是骤回器件布局阵列301的相应列1或列2的部分。在一些实施例中,至少阱布局图案316a或316b位于骤回器件布局阵列301的相应有源区布局图案312a或312b的漏极侧。至少阱布局图案316a或316b具有矩形形状。在一些实施例中,至少阱布局图案316a或316b具有多边形形状。

在一些实施例中,至少阱布局图案316a或316b是在第二方向Y上延伸的连续阱布局图案。在一些实施例中,至少阱布局图案316a或316b包括在第二方向Y上延伸的至少M个不连续的阱布局图案,其中M对应于骤回器件布局阵列301中的行数。

在一些实施例中,至少阱布局图案316a或316b将有源区布局图案组312分成布置成列的不连续布局图案。在一些实施例中,至少阱布局图案316a或316b将有源区布局图案组312分成不连续布局图案,从而将P阱204分成布置成列的不连续图案。

阱布局图案组316位于第三层级上。在一些实施例中,第三层级不同于第一层级和第二层级。在一些实施例中,第三层级与第一层级相同。在一些实施例中,第三层级对应于布局设计300B、400B、500C、600C、700A-700C或800A-800C(图3B、图4B、图5C、图6C、图7A-7C或图8A-8C)或集成电路200A-200B、500A-500B、600A-600B(图2A-2B、图5A-5B或图6A-6B)中的一个或多个的有源层级或OD层级。

阱布局图案组316中的图案的其他配置、水平或数量在本公开的范围内。

布局设计300B还包括至少一个在第一方向和第二方向Y上延伸的抽头单元布局图案326。布局图案326围绕骤回器件布局阵列301。抽头单元布局图案326与骤回器件布局阵列301在第一方向X和第二方向Y上分开。在一些实施例中,抽头单元布局图案326是在第一方向X和第二方向Y上延伸的连续布局图案。

抽头单元布局图案326可用于制造图2A-2B的P阱抽头216。在一些实施例中,抽头单元布局图案326可用于制造图4A的NMOS晶体管N1的体端子。

在一些实施例中,抽头单元布局图案326位于第一层级上。抽头单元布局图案326中图案的其他配置、水平或数量在本公开的范围内。

图4A是根据一些实施例的集成电路400A的示意框图。

集成电路400A是集成电路100A-100B的变体,因此省略了类似的详细描述。例如,根据一些实施例,集成电路400A是图1A的集成电路100A与驱动器电路440组合的部分。尽管在图4A的集成电路400A中示出了集成电路100A的部分,但是应当理解,集成电路400A可以被修改为包括与类似于图4中所示的驱动器电路440组合的集成电路100A的每个特征,为了简洁,因此省略类似的详细描述。

集成电路400A包括内部电路102、IO焊盘108、参考电压源端子106、骤回器件120和驱动器电路440。

驱动器电路440是N型金属氧化物半导体(NMOS)晶体管N1。在一些实施例中,驱动器电路440是P型金属氧化物半导体(PMOS)晶体管。

驱动器电路440耦合在IO焊盘108和参考电压源端子106(例如VSS)之间。NMOS晶体管N1的栅极被配置为接收驱动器信号DRV。NMOS晶体管N1的漏极耦合到I/O焊盘108和骤回器件120,并且NMOS晶体管N1的源极耦合到参考电压源端子106和骤回器件120。NMOS晶体管N1的源极还耦合到NMOS晶体管N1的体。

在一些实施例中,驱动器电路440耦合到内部电路102,并且被配置为处理内部电路102、参考电压源端子104的电源电压VDD和参考电压源端子106的参考电压VSS之间的信号传输。

驱动器电路440与骤回器件120并联耦合。在一些实施例中,驱动器电路440被包括为骤回器件120的部分。例如,在一些实施例中,驱动器电路440的NMOS晶体管N1对应于集成电路200A-200B的骤回器件的NMOS器件。在没有ESD事件的情况下,NMOS晶体管N1被配置为在内部电路102的正常操作期间在驱动器信号DRV的控制下操作为驱动器电路。当发生ESD事件时,NMOS晶体管N1被配置操作为关于图1A-1B和图2A-2C所描述的ESD保护器件(例如,骤回器件)。在这些实施例中,驱动器电路440的NMOS晶体管N1被配置为与集成电路200A或骤回器件120共享P阱204。

驱动器电路440在NMOS晶体管N1的栅极和NMOS晶体管N1的漏极之间具有寄生电容Cgd。在一些实施例中,在正ESD应力(例如PS模式)期间,NMOS晶体管N1的栅极通过寄生电容Cgd电容耦合到NMOS晶体管N1的漏极和IO焊盘108,从而接收正ESD应力。通过在ESD事件期间接收正ESD应力,使NMOS晶体管N1至少稍微导通,从而在NMOS晶体管N1的p阱中产生沟道电流I2。在一些实施例中,由于驱动器电路440的NMOS晶体管N1与集成电路200A-200B或骤回器件120共享P阱204,所以驱动器电路440的NMOS晶体管N1向也共享P阱204的其他器件(例如,集成电路200A-200B、骤回器件120或骤回阵列301A'中的其他骤回器件)贡献沟道电流,从而为集成电路200A-200B或骤回器件120产生比其他方法更高的基极电流Ib。在一些实施例中,驱动器电路440的较早的导通行为与较高的基极电流Ib相结合触发了骤回阵列301A'中的并联的其他骤回器件共同导通,从而还降低了集成电路200A-200B和400A或骤回器件120的触发电压Vth。

在一些实施例中,附加驱动器电路(未示出)耦合在IO焊盘108和图1A的集成电路100A的电压源端子104之间。在一些实施例中,附加驱动器电路(未示出)是PMOS晶体管。在一些实施例中,附加驱动器电路(未示出)类似于驱动器电路440,因此省略类似的详细描述。

集成电路400A中的其他电路配置或数量在本公开的范围内。

图4B是根据一些实施例的布局设计400B的图。

布局设计400B是集成电路400A的布局图。布局设计400B可用于制造集成电路400A。在一些实施例中,图4B包括图4B中未示出的附加元件。

布局设计400B是布局设计300B(图3B)的变体,因此省略了类似的详细描述。例如,布局设计400B示出了将驱动器电路布局图案450与骤回器件布局阵列301的骤回器件布局图案301[1,1],...,301[M,1]放置在相同的P阱列(例如,列1)中的示例。

在一些实施例中,通过将驱动器电路布局图案450定位在与骤回器件布局阵列301的骤回器件布局图案301[1,1],...,301[M,1]相同的P阱列(例如,列1)中,驱动器电路布局图案450与骤回器件布局图案301[1,1],...,301[M,1]共享P阱204,因此具有与以上针对图4A描述的优点类似的优点,为了简明这里不再重复。

布局设计400B是图3A的骤回器件阵列300A的布局图。布局设计400B可用于制造图3A的骤回器件阵列300A。

布局设计400B包括布局设计300B和驱动器电路布局图案450。

驱动器电路布局图案450可用于制造图4A的驱动器电路440。在一些实施例中,驱动器电路布局图案450对应于图4A的驱动器电路440的位置。在一些实施例中,驱动器电路440对应于晶体管260,因此驱动器电路布局图案450对应于晶体管260的布局设计。

在一些实施例中,骤回器件布局阵列301的列1中的每个布局设计均包括驱动器电路布局图案450。在一些实施例中,骤回器件布局阵列301中的布局设计中的至少一个包括驱动器电路布局图案450。

在一些实施例中,骤回器件布局阵列301中的至少另一列包括类似于驱动器电路布局图案450的布局图案,因此省略类似的详细描述。

驱动器电路布局图案450中的图案的其他配置或数量在本公开的范围内。

图5A是根据一些实施例的集成电路500A的截面图。如图5B是根据一些实施例的集成电路500A的等效电路500B的截面图。如图5C是根据一些实施例的布局设计500C的图。在一些实施例中,集成电路500A或等效电路500B的截面图对应于与平面B-B’相交的布局设计500C。

集成电路500A是骤回器件120的实施例。

集成电路500A是集成电路200A的变体,因此省略了类似的详细描述。举例来说,集成电路500A示出其中将附加N阱(例如,N阱506)添加到骤回器件120或集成电路200A的示例。在一些实施例中,通过将附加N阱(例如,N阱506)放置到P阱(例如,P阱204)中,还减小了P阱(例如,P阱204)的有效面积。

与图2A的集成电路200A相比,集成电路500A还包括N阱506。N阱506类似于N阱206,因此省略类似的详细描述。

P阱204和N阱506在衬底202中。N阱506在P阱204内。N阱506在第一方向X上具有宽度W2'。在一些实施例中,宽度W2'与宽度W1'不同。在一些实施例中,宽度W2’等于宽度W1’。

至少N阱506或206具有与P阱204的掺杂杂质类型相反的掺杂杂质类型。N阱506包括n型掺杂杂质,并且P阱204包括p型掺杂杂质。虽然图5A-5B和图6A-6B示出了STI区域210在N阱506内,在一些实施例中,STI区域210不在N阱506内。在一些实施例中,STI区域210邻近N阱506或直接在其附近。在实施例中,N阱506在源极区214和STI区域210之间。在一些实施例中,STI区域210不形成在与N阱506相同的区域或空间中。在一些实施例中,STI区域210不形成在N阱506中。在一些实施例中,集成电路500A或500B不包括STI区域208或210。在一些实施例中,集成电路600A或600B不包括STI区域208或210。

N阱506位于晶体管260的源极侧。在一些实施例中,通过将N阱506包括在集成电路500A中,减小了集成电路500A中的P阱204的有效面积,从而在ESD事件期间增加了P阱204和衬底202的基极电阻Rb。通过增加基极电阻Rb,与不包括N阱206和506时相比,在ESD事件期间集成电路500A的触发电压Vth降低。

N阱506的其他配置、尺寸或数量在本公开的范围内。

图5B是根据一些实施例的集成电路500A的等效电路500B的截面图。例如,等效电路500B对应于具有寄生BJT 540的集成电路500A。例如,与图5B相比,为了便于说明图5A的集成电路500A未示出图5B的寄生BJT 540。

图5C是根据一些实施例的布局设计500C的图。

布局设计500C是集成电路500A或等效电路500B的布局图。布局设计500C可用于制造集成电路500A或等效电路500B。在一些实施例中,图5C包括未示出的附加元件。

在一些实施例中,集成电路500A或等效电路500B的截面图对应于与平面B-B'相交的布局设计500C。

布局设计500C是图3A的骤回器件阵列300A的布局图。布局设计500C可用于制造图3A的骤回器件阵列300A。

布局设计500C是布局设计300B(图3B)的变体,因此省略类似的详细描述。例如,布局设计500C示出了将阱布局图案516a添加到骤回器件布局阵列301的列1,以及将阱布局图案516b添加到骤回器件布局阵列301的列2的示例。通过将阱布局图案516a定位在骤回器件布局阵列301的列1中,并且将阱布局图案516b定位在骤回器件布局阵列301的列2中,布局设计500C的骤回器件布局阵列301中的每个骤回器件布局图案可用于制造至少集成电路,类似于具有两个N阱(例如N阱206和N阱506)的集成电路500A-500B,从而还减小P阱204的面积,因此具有与上面针对图5A描述的那些优点,为了简洁这里不再重复描述。

与图3B的布局设计300B相比,布局设计500C还包括阱布局图案516a和阱布局图案516b。阱布局图案516a或516b类似于相应的阱布局图案316a或316b,因此省略类似的详细描述。

与图3B的布局设计300B相比,阱布局图案组516代替了图3B的阱布局图案组316,因此省略了类似的详细描述。阱布局图案组516至少包括阱布局图案316a、316b、516a或516b。

阱布局图案516a或516b各自在第二方向Y上延伸。在第一阱布局图案组516中的每个阱布局图案与阱布局图案组516中的相邻阱布局图案在第一方向上分离。至少阱布局图案516a或516b具有在第一方向X上延伸的宽度W2。在一些实施例中,宽度W2等于宽度W1。在一些实施例中,宽度W2不同于宽度W1。宽度W2小于节距P1。在一些实施例中,宽度W2等于节距P1。

至少阱布局图案516a或516b可用于制造N阱506。

阱布局图案516a位于栅极布局图案330a和330b之间(例如,在骤回器件布局阵列301的相应有源区布局图案312a或312b的源极侧)。阱布局图案516b位于栅极布局图案330c和330d之间(例如,在骤回器件布局阵列301的相应有源区布局图案312a或312b的源极侧)。

阱布局图案516a或516b是骤回器件布局阵列301的相应列1或列2的部分。在一些实施例中,至少阱布局图案516a或516b还将有源区布局图案组312分成另外的布置在列中的不连续布局图案。在一些实施例中,至少阱布局图案516a或516b还将有源区布局图案组31分成另外的不连续布局图案,从而将P阱204还分成布置在列中的不连续图案。

阱布局图案组516位于第三层级上。阱布局图案组516中的图案的其他配置、水平或数量在本公开的范围内。

图6A是根据一些实施例的集成电路600A的截面图。图6B是根据一些实施例的集成电路600A的等效电路600B的截面图。图6C是根据一些实施例的布局设计600C的图。在一些实施例中,集成电路600A或等效电路600B的截面图对应于与平面C-C’相交的布局设计600C。

集成电路600A是骤回器件120的实施例。

集成电路600A是集成电路500A的变体,因此省略了类似的详细描述。例如,集成电路600A示出了在骤回器件120或集成电路200A中的漏极侧不包括N阱(例如,N阱206)的示例。

与图5A的集成电路500A相比较,集成电路600A不包括N阱206。因此,集成电路600A在漏极侧不包括N阱(例如,N阱206),但是在源极侧包括N阱(例如,N阱206)。在一些实施例中,通过在集成电路600A的源极侧上包括N阱506,减小了集成电路600A中的P阱204的有效面积,从而在ESD事件期间增加了P-阱204和衬底202的基极电阻Rb。与不包括N阱506时相比,通过增加基极电阻Rb导致ESD事件期间集成电路600A的触发电压Vth的减小。

集成电路600A中的元件的其他配置、尺寸或数量在本公开的范围内。

图6B是根据一些实施例的集成电路600A的等效电路600B的截面图。例如,等效电路600B对应于具有寄生BJT 640的集成电路600A。例如,与图6B相比,为了易于说明图6A的集成电路600A未示出图6B的寄生BJT 640。

图6C是根据一些实施例的布局设计600C的图。

布局设计600C是集成电路600A或等效电路600B的布局图。布局设计600C可用于制造集成电路600A或等效电路600B。在一些实施例中,图6C包括未示出的附加元件。

在一些实施例中,集成电路600A或等效电路600B的截面图对应于与平面C-C'相交的布局设计600C。

布局设计600C是图3A的骤回器件阵列300A的布局图。布局设计600C可用于制造图3A的骤回器件阵列300A。

布局设计600C是布局设计500C(图5C)的变体,因此省略了类似的详细描述。与图5C的集成电路500C相比,布局设计600C不包括阱布局图案316a和316b。因此,布局设计600C在漏极侧不包括阱布局图案316a和316b,而在晶体管260的源极侧包括阱布局图案516a和516b。

在一些实施例中,通过将阱布局图案516a或516b定位在漏极侧上的骤回器件布局阵列301的相应列1或列2中,布局设计600C的骤回器件布局阵列301中的每个骤回器件布局图案可用于制造至少一个类似于在漏极侧具有N阱506的集成电路600A或等效电路600B的集成电路,从而还减小P阱204的面积,因此具有与上述图6A类似的优点,为了简明这里不再重复描述。

布局设计600C中的其他配置、图案的层级或数量在本公开的范围内。

图7A是根据一些实施例的布局设计700A的图。

布局设计700A是集成电路200A或等效电路200B的布局图。布局设计700A可用于制造集成电路200A或等效电路200B。在一些实施例中,图7A至图7C的实施例未示出的附加元件。

在一些实施例中,集成电路200A或等效电路200B的截面图至少对应于与平面A-A'相交的布局设计700A。

布局设计700A是图3A的骤回器件阵列300A的布局图。布局设计700A可用于制造图3A的骤回器件阵列300A。

布局设计700A是布局设计300B(图3B)的变体,因此省略了类似的详细描述。与图3B的布局设计300B相比较,布局设计700A还包括阱布局图案组730。阱布局图案组730至少包括阱布局图案730a或阱布局图案730b。至少阱布局图案730a或730b类似于阱布局图案316a或316b,因此省略类似的详细描述。

阱布局图案730a或730b各自在第一方向X上延伸。在第二阱布局图案组730中的每个阱布局图案与第二个阱布局图案组730中的相邻阱布局图案分离。阱布局图案730a具有在第二方向Y上延伸的宽度W3,并且阱布局图案730b具有在第二方向Y上延伸的宽度W4。在一些实施例中,宽度W3等于宽度W4。在一些实施例中,宽度W3不同于宽度W4。

阱布局图案730a与有源区布局图案312a在第二方向Y上以距离D2分开。阱布局图案730b与骤回器件布局阵列301的行M中的有源区布局图案(未示出)在第二方向Y上以距离D2(未示出)分开。在一些实施例中,至少宽度W3或宽度W4等于距离D2。在一些实施例中,至少宽度W3或宽度W4不同于距离D2。

至少阱布局图案730a或730b可用于制造类似于N阱506的相应N阱。在一些实施例中,至少阱布局图案730a或730b可用于制造骤回器件阵列布局301中的相应N阱,并且定位在与布局设计700A-700C中所示的位置类似的位置。

至少阱布局图案730a或730b位于骤回器件布局阵列301的外部。至少阱布局图案730a或730b位于骤回器件布局阵列301和阱布局图案326之间。在第一方向X上的至少阱布局图案730a或730b的长度与在第一方向X上的骤回器件阵列布局301的长度相同。在一些实施例中,在第一方向X上的至少阱布局图案730a或730b的长度与在第一方向X上的骤回器件阵列布局301的长度不同。

在一些实施例中,通过将阱布局图案730a定位在阱布局图案326与有源区312a之间,并且将阱布局图案730b定位在阱布局图案326与骤回器件布局阵列301的行M的有源区(未示出)之间,布局设计700A-700C可用于制造相应的集成电路,类似于具有类似于N阱316a或316b的附加N阱(未示出)的集成电路300A,从而还增加了P阱抽头216和骤回器件阵列301A'的晶体管260的每个漏极之间的基极电阻Rb。与不包括附加N阱时相比,通过增加基极电阻Rb,导致ESD事件期间,由布局设计700A-700C制造的集成电路的触发电压Vth降低。

阱布局图案组730位于第三层级上。阱布局图案组730中的图案的其他配置、水平或数量在本公开的范围内。例如,在一些实施例中,布局设计700A不包括阱布局图案730a或730b。

图7B-7C是根据一些实施例的对应布局设计700B-700C的图。

至少布局设计700B或700C是集成电路200A或等效电路200B的布局图。至少布局设计700B或700C可用于制造集成电路200A或等效电路200B。

至少布局设计700B或700C是图3A的骤回器件阵列300A的布局图。至少布局设计700B或700C可用于制造图3A的骤回器件阵列300A。

图7B是根据一些实施例的对应的布局设计700B的图。

在一些实施例中,集成电路500A或等效电路500B的截面图至少对应于与平面B-B'相交的布局设计700B。

布局设计700B是布局设计500C(图5C)和布局设计700A(图7A)的变体,因此省略类似的详细描述。例如,布局设计700B至少示出了将阱布局图案730a和730b添加到图5C的布局设计500C的实施例,因此省略类似的详细描述。换句话说,布局设计700B包括添加在图5C的布局设计500C中的图7A的阱布局图案730a和730b。

图7C是根据一些实施例的对应的布局设计700C的图。

在一些实施例中,集成电路600A或等效电路600B的截面图对应于至少与平面C-C'相交的布局设计700C。

布局设计700C是布局设计600C(图6C)和布局设计700A(图7A)的变体,因此省略类似的详细描述。例如,布局设计700C至少示出了将阱布局图案730a和730b添加到图6C的布局设计600C的实施例,省略类似的详细描述。换句话说,布局设计700C包括添加在图6C的布局设计600C中的图7A的阱布局图案730a和730b。

至少出于与以上针对图7A类似的原因,在一些实施例中,通过将阱布局图案730a定位在阱布局图案326与有源区312a之间,并且将阱布局图案730b定位在阱布局图案326与骤回器件布局阵列301的行M的有源区(未示出)之间,布局设计700B和700C可用于制造在P阱抽头216与骤回器件阵列301A'中的晶体管260的每个漏极之间具有增大的基极电阻Rb的相应集成电路,因此具有与上述关于图7A类似的优点,为了简洁这里不再重复描述。

至少布局设计700B或700C中的图案的其他配置、水平或数量在本公开的范围内。例如,在一些实施例中,至少布局设计700B或700C不包括阱布局图案730a或730b。

图8A是根据一些实施例的布局设计800A的图。

布局设计800A是集成电路200A或等效电路200B的布局图。布局设计800A可用于制造集成电路200A或等效电路200B。在一些实施例中,图8A至图8C包括未示出的附加元件。

在一些实施例中,集成电路200A或等效电路200B的截面图至少对应于与平面A-A'相交的布局设计800A。

布局设计800A是图3A的骤回器件阵列300A的布局图。布局设计800A可用于制造图3A的骤回器件阵列300A。

布局设计800A是布局设计700A(图7A)的变体,因此省略了类似的详细描述。与图7A的布局设计700A相比,布局设计800A还包括有源区布局图案812和814,以及栅极布局图案组830和840。

至少有源布局图案812或814类似于对应的有源布局图案312a或312b,因此省略类似的详细描述。至少有源布局图案812或814在第二方向Y上延伸。有源区布局图案812和814在第二方向Y上彼此分离。在一些实施例中,至少有源区布局图案812或814在相应的阱。布局图案730a或730b上。

至少有源区布局图案812或814位于骤回器件布局阵列301的外部。至少有源区布局图案812或814位于骤回器件布局阵列301和阱布局图案326之间。

在一些实施例中,有源区布局图案312a可用于制造类似于图2A-2B的晶体管260的晶体管的有源区(例如,漏极区212和源极区214),但是是伪晶体管。

在一些实施例中,至少有源区布局图案812或814是在第一方向X上延伸的连续布局图案。在一些实施例中,至少有源区布局图案812或814包括在第一方向X上延伸的不连续布局图案。

在一些实施例中,至少有源区布局图案812或814位于第一层级上。至少有源区布局图案812或814中的图案的其他配置、层级或数量在本公开的范围内。

至少栅极布局图案组830或840与栅极布局图案组330类似,因此省略类似的详细描述。

栅极布局图案组830至少包括栅极布局图案830a,830b,...,830f或830g。栅极布局图案组840包括至少栅极布局图案840a,840b,...,840f或840g。栅极布局图案组830和840各自在第二方向Y上延伸。栅极布局图案组830或840的每个栅极布局图案与相应的栅极布局图案组830或840中的对应的相邻栅极布局图案在第一方向X上以第二节距(未示出)分开。

在一些实施例中,至少栅极布局图案830a,830b,...,830f或830g或至少栅极布局图案840a,840b,...,840f或840g可用于制造类似于至少栅极结构230或830、NMOS晶体管N1的栅极的栅极,但是是伪栅极结构。在一些实施例中,伪栅极结构是非功能栅极结构。

在一些实施例中,至少栅极布局图案组830或840中的栅极布局图案的数量与栅极布局图案330的数量相同。在一些实施例中,至少栅极布局图案组830或840中的栅极布局图案的数量与栅极布局图案330的数量不同。

栅极布局图案组830或840位于第二层级上。栅极布局图案组830或840中的图案的其他配置、层级或数量在本公开的范围内。

在一些实施例中,通过将阱布局图案730a、有源区布局图案812和栅极布局图案组830定位在阱布局图案326和有源区312a之间,并且将阱布局图案730b、有源区布局图案组814和栅极布局图案组840定位在阱布局图案326和骤回器件布局阵列301的行M中的有源区(未示出)之间,布局设计800A-800C可用于制造相应的集成电路,类似于具有类似于N阱316a或316b的附加N-阱(未示出)的集成电路300A,从而还增加了骤回器件301A’阵列中的P阱抽头216与晶体管260的每个漏极之间的基极电阻Rb。与不包括另外的N阱时相比,通过增加基极电阻Rb,在ESD事件期间导致由布局设计800A-800C制造的集成电路的触发电压Vth的减小。

至少布局设计800A中的图案的其他配置、层级或数量在本公开的范围内。例如,在一些实施例中,布局设计800A不至少包括阱布局图案830a或830b、有源区布局图案812或814或栅极布局图案组830或840。

图8B-8C是根据一些实施例的对应布局设计800B-800C的图。

至少布局设计800B或800C是集成电路200A或等效电路200B的布局图。至少布局设计800B或800C可用于制造集成电路200A或等效电路200B。

至少布局设计800B或800C是图3A的骤回器件阵列300A的布局图。至少布局设计800B或800C可用于制造图3A的骤回器件阵列300A。

图8B是根据一些实施例的对应的布局设计800B的图。

在一些实施例中,集成电路500A或等效电路500B的截面图对应于至少与平面B-B'相交的布局设计800B。

布局设计800B是布局设计700B(图7B)和布局设计800A(图8A)的变体,因此省略了类似的详细描述。举例来说,布局设计800B说明至少一个实施例,其中将有源区布局图案812和814以及栅极布局图案组830和840添加到图7B的布局设计700B,省略了类似的详细描述。换句话说,布局设计800B包括添加到图7B的布局设计700B中的有源区布局图案812和814、以及图8A的栅极布局图案组830和840。

图8C是根据一些实施例的对应的布局设计800C的图。

在一些实施例中,集成电路600A或等效电路600B的截面图至少对应于与平面C-C'相交的布局设计800C。

布局设计800C是布局设计700C(图7C)和布局设计800A(图8A)的变体,因此省略类似的详细描述。例如,布局设计800C示出至少一个实施例,其中将有源区布局图案812和814以及栅极布局图案组830和840添加到图7C的布局设计700C,省略了类似的详细描述。换句话说,布局设计800C包括被添加到图7C的布局设计700C中的有源区布局图案812和814以及图8A的栅极布局图案组830和840。

至少由于与以上针对图8A所述的原因类似的原因,在一些实施例中,通过将阱布局图案730a、有源区布局图案812和栅布局图案组830定位在阱布局图案326和有源区312a之间,并且将阱布局图案730b、有源区布局图案814和栅极布局图案组840定位在阱布局图案326和骤回器件布局阵列301的行M中的有源区(未示出)之间,布局设计800B和800C可用于制造相应集成电路,其在P阱抽头216和骤回器件阵列301A'的中的晶体管260的每个漏极之间具有增加的基极电阻Rb,因此具有与以上针对图8A所述的优点类似的优点,为了简洁不再重复描述。

至少布局设计800B或800C中的图案的其他配置、层级或数量在本公开的范围内。例如,在一些实施例中,至少布局设计800B或800C不至少包括阱布局图案830a或830b、有源区布局图案812或814或栅极布局图案组830或840。

图9是根据一些实施例的形成或制造ESD电路的方法900的流程图。应当理解,可以在图9所示的方法900之前、之中和/或之后执行附加操作。在图9中示出了其他操作,并且这里仅简要描述一些其他操作。在一些实施例中,方法900可用于形成ESD电路,例如集成电路100A-100B、200A、400A、500A、600A(图1A-1B、图2A、图4A、图5A或图6A),骤回器件阵列300A(图3A)或等效电路200B(图2B),500B(图5B)或600B(图6B)。在一些实施例中,方法900可用于形成具有与布局设计300B、400B、500C、600C、700A-700C或800A-800C(图3B、图4B、图5C、图6C、图7A-7C或图8A-8C)中的一个或多个类似的结构关系的ESD电路。在一些实施例中,方法900的其他操作顺序在本公开的范围内。方法900包括示例性操作,但是这些操作不一定以所示的顺序执行。根据所公开的实施例的精神和范围,可以适当地增加、替换、改变顺序和/或消除操作。

在方法900的操作902中,生成ESD电路的布局设计。操作902由配置为执行用于生成布局设计的指令的处理器件(例如,处理器1202(图12))执行。在一些实施例中,布局设计是图形数据库系统(GDSII)文件格式。

在一些实施例中,方法900的ESD电路至少包括集成电路100A-100B、200A、400A、500A、600A(图1A-1B、图2A、图4A、图5A或图6A),骤回器件阵列300A(图3A),500B(图5B)或600B(图6B)或等效电路200B(图2B)。在一些实施例中,方法900的布局设计至少包括布局设计300B、400B、500C、600C、700A-700C或800A-800C(图3B、图4B、图5C、图6C、图7A-7C或图8A-8C)。

在方法900的操作904中,基于布局设计来制造ESD电路。在一些实施例中,方法900的操作904包括:基于布局设计来制造至少一个掩模,以及基于所述至少一个掩模来制造ESD电路。

图10A是根据一些实施例的集成电路设计和制造流程1000A的至少部分的功能流程图。应当理解,可以在图10A所示的方法1000A之前、之中和/或之后执行附加操作,并且这里仅简要描述一些其他过程。在一些实施例中,方法1000A的其他操作顺序在本公开的范围内。方法1000A包括示例性操作,但是这些操作不一定以所示的顺序执行。根据所公开的实施例的精神和范围,可以适当地增加、替换、改变顺序和/或消除操作。

在一些实施例中,方法1000A是方法900的操作902的实施例。在一些实施例中,方法1000A可用于至少产生或放置集成电路的布局设计300B、400B、500C、600C、700A-700C或800A-800C(图3B、图4B、图5C、图6C、图7A-7C或图8A-8C)中的一个或多个布局图案,诸如集成电路100A-100B、200A、400A、500A、600A(图1A-1B、图2A、图4A、图5A或图6A)的,骤回器件阵列300A(图3A)或等效电路200B(图2B)、500B(图5B)或600B(图6B)。

在方法1000A的操作1002中,生成或放置了骤回器件布局设计阵列。在一些实施例中,方法1000A的骤回器件布局设计阵列至少包括布局设计300B、400B、500C、600C、700A-700C或800A-800C。在一些实施例中,方法1000A的骤回器件布局设计的阵列至少包括布局设计301[1,1],301[1,2],...,301[2,2],...,301[M,N]中的布局设计。在一些实施例中,操作1002至少包括操作1004、1006或1008。

在方法1000A的操作1004中,生成第一组有源区布局图案或将其放置在布局设计的第一层级上。在一些实施例中,方法1000A的布局设计至少包括布局设计。在一些实施例中,方法1000A的第一层级对应于OD层级。在一些实施例中,方法1000A的第一层级对应于说明书中描述的第一层级。在一些实施例中,方法1000A的第一组有源区布局图案包括至少有源区布局图案组312中的至少一个或多个有源区布局图案。

在方法1000A的操作1006中,第一组栅极布局图案被生成或放置在布局设计的第二层级上。在一些实施例中,方法1000A的第二层级对应于POLY层级。在一些实施例中,方法1000A的第二层级对应于说明书中描述的至少一个层级。在一些实施例中,方法1000A的第栅极布局图案组包括至少栅极布局图案组330中的至少一个或多个栅极布局图案。

在方法1000A的操作1008中,第一组阱布局图案被生成或放置在布局设计的第三层级上。在一些实施例中,方法1000A的第三层级对应于N阱层级。在一些实施例中,方法1000A的第三层级对应于说明书中描述的至少一个层级。在一些实施例中,方法1000A的第一组阱布局图案包括至少阱布局图案组316或516中的至少一个或多个阱布局图案。

在方法1000A的操作1010中,第二组阱布局图案被生成或放置在布局设计的第三层级上。在一些实施例中,方法1000A的第二组阱布局图案包括至少阱布局图案组730中的至少一个或多个阱布局图案。

在方法1000A的操作1012中,第二组有源区布局图案被生成或放置在布局设计的第一层级上。在一些实施例中,方法1000A的第二组有源区布局图案包括至少有源区布局图案组812或814中的至少一个或多个有源区布局图案。

在方法1000A的操作1014中,第二组栅极布局图案被生成或放置在布局设计的第二层级上。在一些实施例中,方法1000A的第二组栅极布局图案包括至少栅极布局图案组830或840中的至少一个或多个栅极布局图案。

在方法1000A的操作1016中,在布局设计上生成或放置驱动器电路布局图案组。在一些实施例中,方法1000A的驱动器电路布局图案组包括阱布局图案450的至少一个或多个部分。在一些实施例中,方法1000A的驱动器电路布局图案组包括与阱布局图案450的至少部分组合的晶体管的布局设计301[1,1],301[1,2],...,301[2,2],...,301[M,N]中的至少一个或多个布局设计。

在一些实施例中,操作1016包括一个或多个操作,以在骤回器件布局图案301的阵列中生成或放置单个列和行。在一些实施例中,操作1016包括将驱动器电路布局图案放置在骤回ESD保护电路阵列的布局设计的第一行中,其中驱动器电路布局图案对应于制造驱动器电路440。在一些实施例中,放置驱动器电路布局图案包括在第一布局层级中放置第一组有源布局图案的第三有源区布局图案,第三有源区布局图案沿第一方向延伸,并且对应于制造驱动器电路的漏极区;并且在第一布局层级中放置第一组有源区布局图案中的第四有源区布局图案,第四有源区布局图案沿第一方向延伸,并对应于制造驱动器电路的源极区,驱动器电路与骤回ESD保护电路阵列中的第一骤回ESD保护电路共享骤回ESD保护电路的p阱。在一些实施例中,第一有源区布局图案和第二有源区布局图案在骤回ESD保护电路阵列的布局设计的第二行中,第二行与第一行相邻。

在方法1000A的操作1018中,在布局设计的第三层级上生成或放置第一阱布局图案。在一些实施例中,方法1000A的第一阱布局图案包括阱布局图案326的至少部分。

在一些实施例中,执行方法1000A的一个或多个操作以生成第一布局图案或将第一布局图案放置在方法1000A的布局设计上,然后重复方法1000A的一个或多个操作以生成或在方法1000A的布局设计上放置其他布局图案。在一些实施例中,执行方法1000A的一个或多个操作以在方法1000A的布局设计上生成或放置第一布局设计,然后重复方法1000A的一个或多个操作以生成或在方法1000A的布局设计上放置其他布局。

在一些实施例中,方法1000A的至少一个或多个操作由诸如图12的系统1200的EDA工具执行。在一些实施例中,至少一种方法,例如以上讨论的方法1000A,全部或部分地由至少一个EDA系统(包括系统1200)执行。在一些实施例中,EDA系统可用作图13的IC制造系统1300的设计室的部分。

方法1000A的一个或多个操作由配置为执行用于制造方法1000A的集成电路的指令的处理器件执行。在一些实施例中,使用与方法1000A的不同一个或多个操作中所使用的处理器件相同的处理器件来执行方法1000A的一个或多个操作。在一些实施例中,与用于执行方法1000A的不同一个或多个操作的处理器件不同的处理器件执行方法1000A的一个或多个操作。

图10B是根据一些实施例的制造集成电路(IC)器件的方法的功能流程图。应当理解,可以在图1所示的方法1000B之前、之中和/或之后执行附加操作,并且这里仅简要描述一些其他过程。在一些实施例中,方法1000B的其他操作顺序在本公开的范围内。方法1000B包括示例性操作,但是这些操作不一定以所示的顺序执行。根据所公开的实施例的精神和范围,可以适当地增加、替换、改变顺序和/或消除操作。

在一些实施例中,方法1000B是方法900的操作904的实施例。在一些实施例中,方法1000B可用于制造或制造至少集成电路100A-100B、200A、400A、500A、600A(图1A-1B、图2A、图4A、图5A或图6A),骤回器件阵列300A(图3A)或等效电路200B(图2B)、500B(图5B)或600B(图6B),或者具有至少与布局设计300B、400B、500C、600C,700A-700C或800A-800C(图3B、图4B、图5C、图6C、图7A-7C或图8A-8C)类似特征的集成电路。

在方法1000B的操作1030中,在衬底中制造第一阱。在一些实施例中,第一阱在第二方向Y上延伸,并具有第一掺杂剂类型。在一些实施例中,方法1000B的第一阱至少包括P阱204。在一些实施例中,方法1000B的衬底至少包括衬底202。

在一些实施方案中,第一阱包含p型掺杂剂。在一些实施例中,p型掺杂剂包括硼、铝或其他合适的p型掺杂剂。在一些实施例中,第一阱包括在衬底202上生长的外延层。在一些实施例中,通过在外延工艺期间添加掺杂剂来掺杂外延层。在一些实施例中,在形成外延层之后,通过离子注入来掺杂外延层。在一些实施例中,通过掺杂衬底202形成第一阱。在一些实施例中,通过离子注入执行掺杂。在一些实施例中,第一阱的掺杂剂浓度在1×10

在方法1000B的操作1032中,在第一阱中制造晶体管的漏极区。在一些实施例中,漏极区在第二方向Y上延伸,并具有第二掺杂剂类型。在一些实施例中,方法1000B的漏极区至少包括漏极区212、晶体管260的漏极或NMOS晶体管N1的漏极。在一些实施例中,方法1000B的晶体管至少包括晶体管260或NMOS晶体管N1。

在方法1000B的操作1034中,在第一阱中制造晶体管的源极区。在一些实施例中,源极区在第二方向Y上延伸,具有第二掺杂剂类型,并且在第一方向X上与漏极区分开。在一些实施例中,方法1000B的源极区至少包括源极区214、晶体管260的源极或NMOS晶体管N1的源极。

在一些实施例中,至少操作1032或1034包括在衬底中形成源极/漏极部件的形成。在一些实施例中,源极/漏极部件的形成包括,去除衬底的部分以在每个间隔件220a,220b的边缘处形成凹部,然后通过将凹部填充在衬底中来执行填充工艺。在一些实施例中,在去除焊盘氧化物层或牺牲氧化物层之后,蚀刻凹部,例如,湿蚀刻或干蚀刻。在一些实施例中,执行蚀刻工艺以去除与隔离区(例如,STI区208或210)相邻的有源区的顶表面部分。在一些实施例中,通过外延或外延(epi)执行填充工艺。在一些实施例中,使用与蚀刻工艺同时进行的生长工艺来填充凹部,其中蚀刻工艺的生长速率大于蚀刻工艺的蚀刻速率。在一些实施例中,使用生长工艺和蚀刻工艺的组合来填充凹部。例如,在凹部中生长材料层,然后对生长的材料进行蚀刻工艺以去除材料的部分。然后,对蚀刻的材料执行后续的生长工艺,直到在凹部中达到所需的材料厚度为止。在一些实施例中,生长过程持续到材料的顶表面在衬底的顶表面上方为止。在一些实施例中,生长过程持续到材料的顶表面与衬底的顶表面共面。在一些实施例中,通过各向同性或各向异性蚀刻工艺去除阱204的部分。蚀刻工艺选择性地蚀刻阱204,而不蚀刻栅极结构230和间隔件220。在一些实施例中,使用反应离子蚀刻(RIE)、湿蚀刻或其他合适的技术来执行蚀刻工艺。在一些实施例中,半导体材料沉积在凹部中以形成源极/漏极部件。在一些实施例中,执行外延工艺以将半导体材料沉积在凹部中。在一些实施例中,外延工艺包括选择性外延生长(SEG)工艺、CVD工艺、分子束外延(MBE)、其他合适的工艺和/或其组合。外延工艺使用与衬底202的成分相互作用的气态和/或液态前体。在一些实施例中,源极/漏极部件包括外延生长的硅(epiSi)、碳化硅或硅锗。在一些实例中,在外延工艺期间,与栅极结构230相关联的IC器件的源极/漏极部件被原位掺杂或不掺杂。如果在Epi工艺中未掺杂源极/漏极部件,则在一些情况下会在后续工艺中掺杂源极/漏极部件。通过离子注入、等离子体浸没离子注入、气体和/或固体源扩散、其他合适的过程和/或它们的组合来实现随后的掺杂工艺。在一些实施例中,在形成源极/漏极部件之后和/或在随后的掺杂工艺之后,将源极/漏极部件还暴露于退火工艺。

在方法1000B的操作1036中,在第一阱中制造第二阱。在一些实施例中,第二阱在第二方向Y上延伸,并具有第二掺杂剂类型。在一些实施例中,第二阱与漏极区的部分或源极区的部分中的一个相邻。在一些实施例中,方法1000B的第二阱至少包括N阱206或506。在一些实施例中,在形成源极区和漏极区之前形成多个阱。在一些实施例中,在形成方法1000B的源极区和漏极区之前,形成方法1000B的第二阱。例如,在一些实施例中,在操作1032和1034之前执行操作1036。在一些实施例中,在操作1030之后执行操作1036,然后在操作1036之后执行操作1032和1034。

在一些实施例中,至少第二阱、第四阱(下文描述)或第五阱(下文描述)包括n型掺杂剂。在一些实施例中,n型掺杂剂包括磷、砷或其他合适的n型掺杂剂。在一些实施例中,n型掺杂剂浓度在约1×10

在方法1000B的操作1038中,制造晶体管的栅极区。在一些实施例中,栅极区在漏极区和源极区之间。在一些实施例中,栅极区在第一阱和衬底上方。在一些实施例中,方法1000B的栅极区至少包括栅极结构230、晶体管260的栅极或NMOS晶体管N1。

在一些实施例中,至少制造操作1038的栅极区或制造操作1050的伪栅极区包括执行一个或多个沉积工艺以形成一个或多个电介质材料层。在一些实施例中,沉积工艺包括化学气相沉积(CVD)、等离子体增强CVD(PECVD)、原子层沉积(ALD)或其他适合于沉积一个或多个材料层的工艺。在一些实施例中,制造栅极区包括执行一个或多个沉积工艺以形成一个或多个导电材料层。在一些实施例中,制造栅极区包括形成栅电极或伪栅电极。在一些实施例中,制造栅极区包括沉积或生长至少一个电介质层,例如栅极电介质222。在一些实施例中,使用掺杂或非掺杂的多晶硅(或多晶硅)形成栅极区。在一些实施例中,栅极区包括金属,诸如Al、Cu、W、Ti、Ta、TiN、TaN、NiSi、CoSi、其他合适的导电材料或其组合。

在方法1000B的操作1040中,在第一阱中制造第三阱。在一些实施例中,第三阱具有在第二方向Y上延伸的第一掺杂剂类型。在一些实施例中,第三阱围绕第二阱、漏极区、源极区和栅极区。在一些实施例中,方法1000B的第三阱至少包括P阱抽头216。在一些实施例中,第三阱的制造类似于操作1030的至少部分,因此省略类似的描述。

在方法1000B的操作1042中,将一组导电区域沉积在IC上方。在一些实施例中,操作1042包括至少在漏极区上方沉积第一导电区域,从而形成晶体管260或NMOS晶体管N1的漏极接触件,在源极区上方沉积第二导电区域,从而形成晶体管260或NMOS晶体管N1的源极接触件,在第三阱上方沉积第三导电区域,从而形成晶体管260或NMOS晶体管N1的抽头接触件,在漏极接触上方沉积第四导电区域,从而将漏极接触耦合到IO焊盘区域108,或者在源极接触件和抽头接触件上方沉积第五导电区域由此将源极接触件、抽头接触件和参考电压源端子106耦合在一起。在一些实施例中,方法1000B的第四导电区域是导电区域270。在一些实施例中,方法1000B的第五导电区域是导电区域272。

在一些实施例中,操作1042还包括在栅极区上方沉积第六导电区域,从而形成晶体管260或NMOS晶体管N1的栅极接触件。

在一些实施例中,使用光刻和材料去除工艺的组合来形成方法1000B的导电区域组,以在衬底上方的绝缘层(未示出)中形成开口。在一些实施例中,光刻工艺包括图案化光致抗蚀剂,例如正性光致抗蚀剂或负性光致抗蚀剂。在一些实施例中,光刻工艺包括形成硬掩模、抗反射结构或另一种合适的光刻结构。在一些实施例中,材料去除工艺包括湿蚀刻工艺、干蚀刻工艺、RIE工艺、激光钻孔或其他合适的蚀刻工艺。然后用导电材料例如铜、铝、钛、镍、钨或其他合适的导电材料填充开口。在一些实施例中,使用CVD、PVD、溅射、ALD或其他合适的形成工艺来填充开口。

在方法1000B的操作1044中,在第一阱中制造第四阱。在一些实施例中,第四阱具有第二掺杂剂类型,在第二方向Y上延伸,并且在第一方向X上与第二阱分开。在一些实施例中,第四阱与源极区的部分或漏极区的部分中的另一个相邻。在一些实施例中,方法1000B的第四阱至少包括N阱206或506。

在方法1000B的操作1046中,在第一阱中制造第五阱。在一些实施例中,第五阱具有第二掺杂剂类型,在第一方向X上延伸,并且在第二方向Y上与第二阱分开。在一些实施例中,第五阱在第三阱与第二阱的侧面之间。在一些实施例中,第五阱是由至少阱布局图案730a或730b制造的相应阱。在一些实施例中,第五阱至少类似于N阱206或506,并且类似的详细描述被省略。

在方法1000B的操作1048中,在第四阱中制造源极区组和漏极区组。在一些实施例中,源极区组和漏极区组具有第二掺杂剂类型,并且在第二方向Y上延伸。在一些实施例中,方法1000B的源极区组是至少通过有源区布局图案812或814制造的相应源极区。在一些实施例中,方法1000B的漏极区组是至少由有源区布局图案812或814制造的相应源极区。在一些实施例中,漏极区与晶体管260的漏极区类似,并且省略类似的详细描述。在一些实施例中,源极区类似于晶体管260的源极,并且省略类似的详细描述。

在方法1000B的操作1050中,在源极区组与漏极区组之间制造了伪栅极区组。在一些实施例中,伪栅极区组在第二方向Y上延伸,并且在第一方向X上彼此分离。在一些实施例中,源极区组、漏极区组和伪栅极区组对应于伪晶体管组。在一些实施例中,方法1000B的伪栅极区组是由至少栅极布局图案组830或840制造的相应伪栅极区。在一些实施例中,伪栅极区类似于晶体管260的栅极,并且类似的详细描述被省略。

在一些实施例中,执行方法1000B的至少一个或多个操作以制造NMOS晶体管N1,并且这些操作与上述操作类似,因此省略类似的详细描述。在一些实施例中,执行方法1000B的一个或多个操作以制造类似于集成电路100A-100B、200A、400A、500A、600A(图1A-1B,图2A、图4A、图5A或图6A),骤回器件阵列300A(图3A)或等效电路200B(图2B)、500B(图5B)或600B(图6B)的集成电路或具有与至少布局设计300B、400B、500C、600C、700A-700C或800A-800C(图3B、图4B、图5C、图6C、图7A-7C或图8A-8C)类似特征的集成电路,然后重复方法1000B的一种或多种操作以制造类似于集成电路100A-100B、200A、400A、500A、600A(图1A-1B,图2A、图4A、图5A或图6A),骤回器件阵列300A(图3A)或等效电路200B(图2B)、500B(图5B)或600B(图6B)的集成电路或具有与至少布局设计300B、400B、500C、600C、700A-700C或800A-800C(图3B、图4B、图5C、图6C、图7A-7C或图8A-8C)类似特征的集成电路。

在一些实施例中,方法1000B的至少一个或多个操作由图13的系统1300执行。在一些实施例中,至少一种方法,例如以上讨论的方法1000B,全部或部分地由至少一个包括系统1300的制造系统执行。

方法1000B的一个或多个操作由IC厂商1340(图13)执行以制造IC器件1360。在一些实施例中,方法1000B的一个或多个操作由制造工具1352执行以制造晶圆1342。

图11是根据一些实施例的操作电路的方法1100的流程图。在一些实施例中,方法1100的电路至少包括集成电路100A-100B、200A、400A、500A、600A(图1A-1B、图2A、图4A、图5A或图6A),骤回器件阵列300A(图3A)或等效电路200B(图2B)、500B(图5B)或600B(图6B)。应当理解,可以在图1所示的方法1100之前、期间和/或之后执行附加操作,并且这里仅简要描述一些其他过程。应当理解,方法1100利用集成电路100A-100B、200A、400A、500A、600A(图1A-1B、图2A、图4A、图5A或图6A),骤回器件阵列300A(图3A)或等效电路200B(图2B)、500B(图5B)或600B(图6B)中的一个或多个特征。

在方法1100的操作1102中,将ESD电压施加到IO焊盘108上。在一些实施例中,ESD电压大于电压源端子104的电源电压VDD。

在操作1104中,响应于将ESD电压施加到IO焊盘108,导致晶体管260的漏极区212和P阱204之间的PN结被反向偏置,直到雪崩击穿发生为止。

在操作1106中,雪崩击穿在晶体管260中发生,从而导致漏极区212的漏极电流增加,并产生向寄生BJT(例如BJT 240)的基极242漂移的空穴。在一些实施例中,操作1106还包括响应于来自雪崩击穿的空穴的流动而引起BJT 240的基极电阻Rb两端的电压降。

在操作1108中,响应于BJT 240的基极242的电压增加,使BJT 240的基极-发射极结正向偏置。在一些实施例中,操作1108还包括使空穴的衬底电流流到衬底202中的P阱204的P阱抽头216,从而还增加寄生NPN BJT(例如,BJT 240)的基极-发射极电压。例如,如关于图2B所描述,由于参考电压端子106的低电压电平(例如,电压VSS)耦合到P阱抽头216,所以空穴的衬底电流流到衬底202中的P阱204的P阱抽头216。在P阱204和/或衬底202中流动的空穴的电流增加了跨越基极电阻Rb的电压降,从而增加了寄生NPN BJT(例如,BJT 240)的基极-发射极电压Vbe。例如,如以上在图2A-2B中所讨论的,与其他方法相比,在至少P阱204中或在衬底202上添加N阱206使得BJT 240或晶体管260的基极电阻Rb增加。因此,BJT 240的增加的基极电阻Rb导致寄生NPN BJT(例如,BJT 240)的基极-发射极电压Vbe比其他方法更快地增加。

在操作1110中,响应于基极-发射极电压等于或大于阈值电压而使寄生NPN BJT(例如BJT 240)导通,从而使ESD电流I1和/或IO焊盘108上的ESD电压通过导通的寄生NPNBJT放电到参考电压端子106。因此,来自ESD事件的高ESD电流I1被重定向远离晶体管260的栅极结构230。在一些实施例中,因为通过在至少P阱204中或在衬底202上添加N阱206增加BJT 240的基极电阻Rb,从而使基极-发射极电压Vbe朝BJT 240的阈值电压Vth更快地上升,从而使BJT 240在降低的ESD触发电压Vth处较早地接通,并且IO焊盘108上的ESD电压比其他方法更快地放电。

在一些实施例中,不执行至少方法900、1000A或1100中的一个或多个操作。尽管上面参考图2A至图2B描述了方法1100。应当理解,方法1100利用了图1A-1B和图3A-8C中的一个或多个的特征。在一些实施例中,将根据集成电路200A或等效电路200B的描述和操作来执行方法1100的其他操作。

至少集成电路100A-100B、200A、400A、500A、600A(图1A-1B、图2A、图4A、图5A或图6A),骤回器件阵列300A(图3B)或等效电路200B(图2B)、500B(图5B)或600B(图6B)中的其他晶体管类型或其他数量的晶体管在本公开的范围内。

图12是根据一些实施例的用于设计IC布局设计和制造IC电路的系统1200的示意图。在一些实施例中,系统1200生成或放置一个或多个本文所述的IC布局设计。系统1200包括硬件处理器1202和使用计算机程序代码1206(即一组可执行指令1206)进行编码(即存储)的非暂时性计算机可读存储介质1204(例如,存储器1204)。计算机可读存储介质1204被配置为与用于生产集成电路的制造机器接口。处理器1202通过总线1208电耦合到计算机可读存储介质1204。处理器1202还通过总线1208电耦合到I/O接口1210。网络接口1212也通过总线1208电耦合到处理器1202。网络接口1212连接到网络1214,以便处理器1202和计算机可读存储介质1204能够通过网络1214连接到外部元件。处理器1202配置为执行编码在计算机可读存储介质1204中的计算机程序代码1206,以便使系统1200可用于执行至少方法900或1000A中的部分或全部操作。

在一些实施例中,处理器1202是中央处理单元(CPU)、多处理器、分布式处理系统、专用集成电路(ASIC)和/或合适的处理单元。

在一些实施例中,计算机可读存储介质1204是电的、磁的、光的、电磁的、红外的和/或半导体系统(或器件或器件)。例如,计算机可读存储介质1204包括半导体或固态存储器、磁带、可移动计算机磁盘、随机存取存储器(RAM)、只读存储器(ROM)、刚性磁盘和/或光盘。在使用光盘的一些实施例中,计算机可读存储介质1204包括光盘只读存储器(CD-ROM)、光盘读/写光盘(CD-R/W)和/或数字视频光盘(DVD)。

在一些实施例中,存储介质1204存储被配置为使系统1200执行至少方法900或1000A的计算机程序代码1206。在一些实施例中,存储介质1204还存储执行至少方法900或1000A所需的信息以及在执行至少方法900或1000A期间生成的信息,例如布局设计1216,用户界面1218和制造单元1220和/或一组可执行指令来执行至少方法900或1000A的操作。在一些实施例中,布局设计1216包括至少一个布局设计300B、400B、500C、600C、700A-700C或800A-800C(图3B、图4B、图5C、图6C、图7A-7C或图8A-8C)中的一个或多个布局图案。

在一些实施例中,存储介质1204存储用于与制造机器对接的指令(例如,计算机程序代码1206)。指令(例如,计算机程序代码1206)使处理器1202能够生成制造机器可读的制造指令,以在制造过程中至少有效地实施方法900或1000A。

系统1200包括I/O接口1210。I/O接口1210耦合到外部电路。在一些实施例中,I/O接口1210包括用于将信息和命令传送到处理器1202的键盘、小键盘、鼠标、轨迹球、轨迹板和/或光标方向键。

系统1200还包括耦合到处理器1202的网络接口1212。网络接口1212允许系统1200与网络1214通信,一个或多个其他计算机系统连接到该网络。网络接口1212包括诸如BLUETOOTH、WIFI、WIMAX、GPRS或WCDMA的无线网络接口;或有线网络接口,例如ETHERNET、USB或IEEE-1394。在一些实施例中,至少方法900或1000A在两个或更多个系统1200中实现,并且诸如布局设计和用户界面之类的信息通过网络1214在不同系统1200之间交换。

系统1200被配置为通过I/O接口1210或网络接口1212接收与布局设计有关的信息。该信息通过总线1208被传送到处理器1202,以确定用于产生集成电路(例如集成集成电路)的布局设计,诸如集成电路100A-100B、200A、400A、500A、600A(图1A-1B、图2A、图4A、图5A或图6A),骤回器件阵列300A(图3A)或等效电路200B(图2B)、500B(图5B)或600B(图6B)。然后,将布局设计作为布局设计1216存储在计算机可读介质1204中。系统1200配置为通过I/O接口1210或网络接口1212接收与用户接口有关的信息。该信息作为用户存储在计算机可读介质1204中接口1200。系统1200被配置为通过I/O接口1210或网络接口1212接收与制造单元有关的信息。该信息作为制造单元1220存储在计算机可读介质1204中。在一些实施例中,制造单元1220包括由系统1200使用的制造信息。在一些实施例中,制造单元1220至少包括图13的掩模制造1334或IC厂商1340

在一些实施例中,至少方法900或1000A被实现为用于由处理器执行的独立软件应用。在一些实施例中,至少方法900或1000A被实现为作为附加软件应用程序的部分的软件应用程序。在一些实施例中,至少方法900或1000A被实现为软件应用程序的插件。在一些实施例中,至少方法900或1000A被实现为作为EDA工具的部分的软件应用。在一些实施例中,至少方法900或1000A被实现为由EDA工具使用的软件应用。在一些实施例中,EDA工具用于生成集成电路器件的布局。在一些实施例中,布局被存储在非暂时性计算机可读介质上。在一些实施例中,使用诸如可从CADENCE DESIGN SYSTEMS,Inc.获得的工具或另一种合适的布局生成工具来生成布局。在一些实施例中,基于基于原理图设计创建的网表来生成布局。在一些实施例中,至少一种方法900或1000A的至少部分由制造器件实施,以使用基于由系统1200生成的一个或多个布局设计而制造的一组掩模来制造集成电路。在一些实施例中,系统1200一种制造器件,其使用基于本公开的一个或多个布局设计而制造的掩模组来制造集成电路。在一些实施例中,图12的系统1200产生比其他方法小的集成电路的布局设计。在一些实施例中,图12的系统1200产生集成电路结构的布局设计,其比其他方法占据更少的面积并提供更好的路由资源。

图13是根据本公开的至少一个实施例的集成电路(IC)制造系统1300以及与其相关联的IC制造流程的框图。在一些实施例中,基于布局图,使用制造系统1300制造(A)一个或多个半导体掩模中的至少一个或(B)半导体集成电路的层中的至少一个组件中的至少一个。

在图13中,IC制造系统1300(以下称为“系统1300”)包括在设计中相互交互的实体,例如设计室1320、掩模室1330和IC制造商/厂商(“fab”)1340,其与制造IC器件1360有关的开发、制造周期和/或服务。系统1300中的实体通过通信网络连接。在一些实施例中,通信网络是单个网络。在一些实施例中,通信网络是各种不同的网络,例如企业内部网和因特网。通信网络包括有线和/或无线通信信道。每个实体与一个或多个其他实体进行交互,并向一个或多个其他实体提供服务和/或从其中一个或多个其他实体接收服务。在一些实施例中,设计室1320、掩模室1330和IC fab 1340中的一个或多个由单个较大的公司拥有。在一些实施例中,设计室1320、掩模室1330和IC fab 1340中的一个或多个在公共设施中共存并使用公共资源。

设计室(或设计团队)1320生成IC设计布局1322。IC设计布局1322包括为IC器件1360设计的各种几何图案。几何图案对应于构成金属层、氧化物层或半导体层的图案将要制造的IC器件1360的各种组件。各个层组合形成各种IC功能。例如,IC设计布局1322的部分包括各种IC部件,例如有源区、栅电极、源电极和漏电极、层间互连的金属线或通孔以及用于焊盘的开口,这些开口将形成在半导体衬底(例如硅晶圆)和设置在半导体衬底上的各种材料层。设计室1320实施适当的设计过程以形成IC设计布局1322。设计过程包括逻辑设计、物理设计或布局和布线中的一个或多个。IC设计布局1322呈现在具有几何图案信息的一个或多个数据文件中。例如,IC设计布局1322可以以GDSII文件格式或DFII文件格式表达。

掩模室1330包括数据准备1332和掩模制造1334。掩模室1330使用IC设计布局1322来制造一个或多个掩模1345,该掩模用于根据IC设计布局1322来制造IC器件1360的各个层。掩模房室1330执行掩模数据准备1332,其中IC设计布局1322被翻译成代表性数据文件(“RDF”)。掩模数据准备1332提供RDF以掩模制造1334。掩模制造1334包括掩模写入器。掩模写入器将RDF转换为衬底上的图像,例如掩模(掩模版)1345或半导体晶圆1342。通过掩模数据准备1332来控制设计布局1322以符合掩模写入器的特定特性和/或IC晶圆厂1340的要求。在图13中,掩模数据准备1332和掩模制造1334被示为单独的元件。在一些实施例中,掩模数据准备1332和掩模制造1334可以被统称为掩模数据准备。

在一些实施例中,掩模数据准备1332包括光学接近度校正(OPC)、其使用光刻增强技术来补偿图像误差,诸如可能由衍射、干涉、其他处理效果(如OPC调整IC设计布局1322)等引起的那些图像误差。在一些实施例中,掩模数据准备1332包括其他分辨率增强技术(RET),例如离轴照明、子分辨率辅助功能、相移掩模、其他合适的技术等或其组合。在一些实施例中,还使用反光刻技术(ILT),其将OPC视为反成像问题。

在一些实施例中,掩模数据准备1332包括掩模规则检查器(MRC),掩模规则检查器使用一组掩模创建规则来检查已经在OPC中进行过处理的IC设计布局,掩模创建规则包含一些几何和/或连接性限制以确保足够余量,以解决半导体制造工艺中的可变性等问题。在一些实施例中,MRC修改IC设计布局以补偿掩模制造1334期间的限制,其可以撤消由OPC执行的修改的部分以满足掩模创建规则。

在一些实施例中,掩模数据准备1332包括光刻工艺检查(LPC),其模拟将由IC fab1340实施以制造IC器件1360的工艺。LPC基于IC设计布局1322来仿真该工艺以创建仿真的制造品。LPC仿真中的处理参数可以包括与IC制造周期的各种过程相关联的参数,与用于制造IC的工具相关联的参数和/或制造过程的其他方面。LPC考虑了各种因素,例如航空图像对比度、焦深(“DOF”)、掩模误差增强因素(“MEEF”)、其他合适的因素等或其组合。在一些实施例中,在通过LPC创建了模拟的制造器件之后,如果模拟的器件在形状上不够接近以满足设计规则,则重复OPC和/或MRC以还完善IC设计布局1322。

应该理解,为了清楚,掩模数据准备1332的以上描述已经被简化。在一些实施例中,数据准备1332包括诸如逻辑操作(LOP)的附加特征,以根据制造规则来修改IC设计布局。另外,可以以各种不同的顺序执行在数据准备1332期间应用于IC设计布局1322的处理。

在掩模数据准备1332之后以及在掩模制造1334期间,基于修改的IC设计布局1322来制造掩模1345或掩模组1345。在一些实施例中,掩模制造1334包括基于IC设计1322进行一次或多次光刻曝光。在一些实施例中,基于修改的IC设计布局1322,使用电子束(e-beam)或多个电子束的机构在掩模(光掩模或掩模版)1345上形成图案。掩模1345可以以各种技术形成。在一些实施例中,使用二进制技术形成掩模1345。在一些实施例中,掩模图案包括不透明区域和透明区域。用于曝光已经涂覆在晶圆上的图像敏感材料层(例如,光致抗蚀剂)的辐射束,例如紫外线(UV)束,被不透明区域阻挡并且透射通过透明区域。在一个示例中,掩模的二元形式1345包括透明衬底(例如,熔融石英)和涂覆在该二元掩模的不透明区域中的不透明材料(例如,铬)。在另一示例中,使用相移技术形成掩模1345。在掩模1345的相移掩模(PSM)版本中,在掩模上形成的图案中的各种部件被配置为具有适当的相位差以增强分辨率和成像质量。在各种示例中,相移掩模可以是衰减的PSM或交替的PSM。由掩模制造1334产生的掩模用于多种工艺中。例如,在离子注入过程中使用这样的掩模,以在半导体晶圆中形成各种掺杂区域,在蚀刻过程中使用这种掩模,以在半导体晶圆中形成各种蚀刻区域,和/或在其他合适的过程中使用。

IC fab 1340是IC制造实体,其包括一个或多个用于制造各种不同IC产品的制造设施。在一些实施例中,IC Fab 1340是半导体铸造厂。例如,可能有一个制造工厂用于多个IC产品的前端制造((FEOL),而第二个制造工厂可以为互连和封装提供后端制造(BEOL)IC产品的制造,第三制造工厂可以为铸造实体提供其他服务。

IC fab 1340包括被配置为在半导体晶圆1342上执行各种制造操作的晶圆制造工具1352(以下称为“制造工具1352”),从而根据掩模(例如,掩模1345)来制造IC器件1360。在各种实施例中,制造工具1352包括晶圆步进器、离子注入机、光致抗蚀剂涂覆机、处理室(例如,CVD室或LPCVD炉)、CMP系统、等离子体蚀刻系统、晶圆清洁系统中的一个或多个,或其他能够执行本文所述的一种或多种合适制造工艺的制造器件。

IC fab 1340使用由掩模罩1330制造的掩模1345来制造IC器件1360。因此,IC fab1340至少间接地使用IC设计布局1322来制造IC器件1360。在一些实施例中,半导体晶圆1342由IC fab 1340使用掩模1345形成IC器件1360。在一些实施例中,IC制造包括至少间接基于IC设计1322进行一次或多次光刻曝光。半导体晶圆1342包括硅衬底或其他在其上形成有材料层的合适衬底。半导体晶圆1342还包含各种掺杂区、电介质部件、多层互连等中的一个或一个以上(在随后的制造步骤中形成)。

系统1300被示为具有设计室1320、掩模室1330或IC fab 1340作为单独的组件或实体。然而,应理解,设计室1320、掩模室1330或IC fab 1340中的一个或多个是相同组件或实体的部分。

关于集成电路(IC)制造系统(例如,图13的系统1300)以及与之相关联的IC制造流程的细节例如在2016年2月9日授权的美国专利号9,256,709,2015年10月1日发布的授权前公开号第20150278429号,2014年2月6日发布的美国授权前公告号第20140040838号,以及2007年8月21日授权的美国专利第7,260,442号中找到,其全部内容通过引用结合于此。

例如,在美国专利号9,256,709中,在设计室(或设计团队)生成IC设计布局。IC设计布局包括为IC器件设计的各种几何图案。几何图案对应于构成要制造的IC器件的各种组件的金属,氧化物或半导体层的图案。各个层组合形成各种IC功能。例如,IC设计布局的部分包括各种IC部件,例如有源区域、栅电极、源极和漏极、层间互连的金属线或通孔,以及用于在半导体中形成的用于焊盘的开口,开口将形成在半导体衬底(例如硅晶圆)和设置在半导体衬底上的各种材料层。设计室执行适当的设计过程以形成IC设计布局。设计过程可以包括逻辑设计、物理设计和/或布局布线。IC设计布局被呈现在具有几何图案信息的一个或多个数据文件中。掩模室使用IC设计布局来制造一个或多个掩模,掩模用于根据IC设计布局来制造IC器件的各个层。掩模室执行掩模数据准备,其中将IC设计布局转换成可以由掩模编写器物理写入的形式,其中将由掩模数据准备准备的设计布局修改为遵守特定的掩模制造商和/或掩模厂商,然后进行制造。在本实施例中,掩模数据准备和掩模制造被图示为单独的元件,然而,掩模数据准备和掩模制造可以被统称为掩模数据准备。掩模数据准备通常包括光学接近度校正(OPC),其使用光刻增强技术来补偿图像误差,诸如可能由于衍射、干涉或其他处理效应而引起的那些图像误差。掩模数据准备可以包括其他分辨率增强技术(RET),例如离轴照明、子分辨率辅助特征、相移掩模、其他合适的技术或其组合。掩模数据准备132还包括掩模规则检查器(MRC),掩模规则检查器使用一组掩模创建规则来检查已经在OPC中进行过处理的IC设计布局,该掩模创建规则可以包含一些几何和连通性限制以确保足够的裕度。

例如,在美国授权前公开号20150278429中,在一个实施例中,IC制造系统可以采用无掩模光刻技术,诸如电子束光刻或光学无掩模光刻。在这样的系统中,掩模制造被旁路,并且IC设计布局通过适合于利用特定的无掩模光刻技术进行晶圆处理的数据准备来修改。数据准备修改了适合于IC制造系统中的后续操作的设计布局。数据准备的结果以一个或多个数据文件表示,例如GDSII文件格式或DFII文件格式的文件。一个或多个数据文件包括几何图案的信息,例如表示主要设计图案和/或辅助部件的多边形。在本实施例中,一个或多个数据文件还包括由数据准备产生的辅助数据。辅助数据将用于增强IC制造系统的各种操作,例如由掩模室进行的掩模制造和由IC制造商进行的晶圆曝光。

例如,在授权前公告号第20140040838号中,IC设计布局被呈现在具有几何图案信息的一个或多个数据文件中。在一示例中,IC设计布局以本领域已知的“GDS”格式表示。在替代实施例中,IC设计布局可以以诸如DFII、CIF、OASIS或任何其他合适的文件类型的替代文件格式在IC制造系统中的组件之间传输。IC设计布局300包括代表集成电路的部件的各种几何图案。例如,IC设计布局可以包括主要的IC部件,例如有源区、栅电极、源极和漏极、金属线、层间互连通孔,以及用于在半导体中形成的用于焊盘的开口,开口将形成在半导体衬底(例如硅晶圆)和设置在半导体衬底上的各种材料层。IC设计布局还可包括一些辅助部件,诸如用于成像效果、处理增强和/或掩模识别信息的那些部件。

例如,在美国专利第7,260,442号中,掩模制造系统包括:用于加工掩模的加工工具;与处理工具连接的计量工具,用于检查掩模并获得检查结果;控制器,与处理工具和计量工具偶偶饥饿,用于生成处理工具的制造模型,并根据设备数据、材料数据和掩模的检查结果对制造模型进行校准。掩模制造系统可包括至少一个处理工具、计量工具、控制器、数据库和制造执行系统。处理工具可以是曝光工具、显影剂、蚀刻机或光刻胶剥离剂。计量工具执行蚀刻后检查或剥离后检查,并分别获得蚀刻后检查结果或剥离后检查结果。控制器用于处理工具的运行到运行控制,包括前馈控制和后馈控制。控制器从计量工具接收蚀刻后或剥离后检查结果,并从数据库中检索器件和材料数据。与制造执行系统连接的控制器生成处理工具的制造模型,并根据设备数据、材料数据和掩模的检查结果来校准制造模型。控制器还监视处理工具的操作条件并在处理期间调整处理工具的制造模型。

此外,图1A-图13中所示的各种PMOS晶体管具有特定的掺杂剂类型(例如,N型或P型),并且仅用于说明目的。本公开的实施例不限于特定的晶体管类型,并且图1A-图13中所示的PMOS或NMOS晶体管中的一个或多个可以用不同晶体管/掺杂剂类型的对应晶体管代替。类似地,以上描述中使用的各种信号的低或高逻辑值也用于说明。当信号被激活和/或去激活时,本公开的实施例不限于特定的逻辑值。选择不同的逻辑值在各种实施例的范围内。在图1A-图13中选择不同数量的PMOS晶体管在各种实施例的范围内。

本说明书的一个方面涉及一种ESD保护电路。骤回ESD保护电路包括:第一阱,位于衬底中,第一阱具有第一掺杂剂类型;晶体管的漏极区,漏极区在第一阱中,并且具有不同于第一掺杂剂类型的第二掺杂剂类型;晶体管的源极区,源极区在第一阱中,具有第二掺杂剂类型,并且在第一方向上与漏极区分开;晶体管的栅极区,栅极区在第一阱和衬底上方;以及第二阱,嵌入在第一阱中,并且与漏极区的部分相邻,并且第二阱具有第二掺杂剂类型。

在上述骤回ESD保护电路中,还包括:抽头阱,位于第一阱中并且具有第一掺杂剂类型。

在上述骤回ESD保护电路中,还包括:输入/输出(IO)焊盘,耦接到漏极区;以及参考电源电压端子,耦接到源极区和抽头阱。

在上述骤回ESD保护电路中,还包括:寄生双极结型晶体管(BJT),位于第一阱中,寄生BJT具有基极、集电极和发射极,集电极通过漏极区耦接到IO焊盘,发射极耦接到源极区;以及第一阱和衬底的寄生基极电阻,寄生基极电阻具有通过抽头阱耦接到参考电源电压端子的第一端、以及耦接到寄生BJT的基极的第二端,其中,寄生BJT被配置为响应于寄生BJT的基极-发射极电压等于或大于从ESD电压施加到IO焊盘的阈值电压而导通,从而通过寄生BJT将ESD电压放电至参考电源电压端子。

在上述骤回ESD保护电路中,栅极区耦接到源极区、抽头阱和参考电源电压端子。

在上述骤回ESD保护电路中,第一阱在第一方向上具有第一宽度,并且第二阱在第一方向上具有第二宽度,第二宽度小于第一宽度。

在上述骤回ESD保护电路中,还包括:第三阱,嵌入在第一阱中,第三阱具有第二掺杂剂类型,并且与源极区的部分相邻。

在上述骤回ESD保护电路中,第三阱在第一方向上具有第三宽度,第三宽度至少与第一宽度或第二宽度不同。

在上述骤回ESD保护电路中,晶体管对应于驱动器电路,栅极区对应于驱动器电路的栅极;漏极区对应于驱动器电路的漏极;以及源极区对应于驱动器电路的源极。

本说明书的另一方面涉及一种ESD保护电路。在一些实施例中,ESD保护电路包括:第一阱,位于衬底中,第一阱具有第一掺杂剂类型;第一晶体管的漏极区,漏极区位于第一阱中,并且具有与第一掺杂剂类型不同的第二掺杂剂类型;第一晶体管的源极区,源极区在第一阱中,具有第二掺杂剂类型,并且在第一方向上与漏极区分开;第一晶体管的栅极区,栅极区在第一阱和衬底上方;第二阱,嵌入在第一阱中,并且与源极区的部分相邻,并且第二阱具有第二掺杂剂类型;以及抽头阱,位于第一阱中且具有第一掺杂剂类型,并且耦接到源极区。

在上述ESD保护电路中,还包括:输入/输出(IO)焊盘耦接到漏极区;以及参考电源电压端子,耦接到源极区和抽头阱。

在上述ESD保护电路中,栅极区耦接到源极区、抽头阱和参考电源电压端子。

在上述ESD保护电路中,还包括:寄生双极结型晶体管(BJT),位于第一阱中,寄生BJT具有基极、集电极和发射极,集电极通过漏极区耦接到IO焊盘,发射极耦接到源极区;以及第一阱和衬底的寄生基极电阻,寄生基极电阻具有通过抽头阱耦接到参考电源电压端子的第一端、以及耦接到寄生BJT的基极的第二端,其中,寄生BJT被配置为响应于寄生BJT的基极-发射极电压等于或大于从ESD电压施加到IO焊盘的阈值电压,从而通过寄生BJT将ESD电压放电至参考电源电压端子。

在上述ESD保护电路中,还包括:第二晶体管,与第一晶体管并联,第二晶体管对应于驱动器电路,第二晶体管包括:第二晶体管的栅极,被配置为接收驱动器信号;第二晶体管的漏极,耦接至IO焊盘和第一晶体管的漏极区;第二晶体管的主体;以及第二晶体管的源极,耦接到第二晶体管的主体、参考电源电压端子和第一晶体管的源极区。

在上述ESD保护电路中,还包括:第二晶体管的栅极和第二晶体管的漏极之间的寄生电容,其中,第二晶体管的栅极通过寄生电容与第二晶体管的漏极和IO焊盘电容耦接,在正ESD事件期间,栅极通过寄生电容接收施加到IO焊盘的ESD电压,从而引起第二晶体管导通并在第一阱中生成沟道电流。

在上述ESD保护电路中,第一阱在第一方向上具有第一宽度,并且第二阱在第一方向上具有第二宽度,第二宽度小于第一宽度。

本说明书的另一方面涉及一种制造骤回式静电放电(ESD)保护电路的方法。在一些实施例中,该方法包括:在衬底中制造第一阱,第一阱在第一方向上延伸,并且具有第一掺杂剂类型;在第一阱中制造晶体管的漏极区,漏极区在第一方向上延伸,并且具有不同于第一掺杂剂类型的第二掺杂剂类型;在第一阱中制造晶体管的源极区,源极区在第一方向上延伸,具有第二掺杂剂类型,并且在不同于第一方向的第二方向上与漏极区分开;在第一阱中制造第二阱,第二阱在第一方向上延伸,具有第二掺杂剂类型,并且与漏极区的部分相邻,以及制造晶体管的栅极区,栅极区在漏极区和源极区之间,并且在第一阱和衬底上方。

在上述方法中,还包括:在第一阱中制造第三阱,第三阱具有第一掺杂剂类型,在第一方向上延伸,并且围绕第二阱、漏极区、源极区和栅极区;在漏极区上方沉积第一导电区,从而形成漏极接触件;在源极区上方沉积第二导电区,从而形成源极接触件;在第三阱上方沉积第三导电区,从而形成抽头接触件;在漏极接触件上方沉积第四导电区,从而将漏极接触件耦接到输入/输出(IO)焊盘区;和在源极接触件和抽头接触件上方沉积第五导电区,从而将源极接触件、抽头接触件和参考电源电压端子耦接在一起。

在上述方法中,还包括:在第一阱中制造第四阱,第四阱具有第二掺杂剂类型,在第一方向上延伸,并且在第二方向上与第二阱分开,第四阱与源极区的部分相邻。

在上述方法中,还包括:在第一阱中制造第四阱,第四阱具有第二掺杂剂类型,在第二方向上延伸,并且在第一方向上与第二阱分开,第四阱在第三阱与第二阱的侧面之间;在第四阱中制造源极区组和漏极区组,源极区组和漏极区组具有第二掺杂剂类型,并且在第一方向上延伸;以及在源极区组和漏极区组之间制造伪栅极区组,伪栅极区组在第一方向上延伸并且在第二方向上彼此分离,源极区组、漏极区组和伪栅极区组对应于伪晶体管组。

本说明书的另一方面涉及一种制造骤回ESD保护电路的方法。该方法包括由处理器生成骤回ESD保护电路的布局设计,并且基于骤回ESD保护电路的布局设计来制造骤回ESD保护电路。在一些实施例中,生成骤回ESD保护电路的布局设计包括:生成在第一方向上延伸并且处于第一布局层级的第一有源区布局图案,第一有源区布局图案对应于制造p型阱中的骤回ESD保护电路。在一些实施例中,生成骤回ESD保护电路的布局设计还包括生成沿第一方向延伸并且处于第一布局层中的第二有源区布局图案,第二有源区布局图案对应于制造p阱中的骤回ESD保护电路。在一些实施例中,生成骤回ESD保护电路的布局设计还包括:生成在与第一方向不同的第二方向上延伸,在第二布局层中并且在第一有源区布局图案上方的第一阱布局图案,第一阱布局图案对应于制造骤回ESD保护电路的第一n阱,第一n阱嵌入在p阱中并与漏极区的部分相邻。

然而,本说明书的另一方面涉及一种制造骤回ESD保护电路的方法。该方法包括:由处理器放置骤回ESD保护电路阵列的布局设计;以及基于骤回ESD保护电路阵列的布局设计来制造骤回ESD保护电路的阵列。在一些实施例中,放置骤回ESD保护电路的阵列的布局设计包括将第一有源区布局图案放置在第一布局层级中,第一有源区布局图案在第一方向上延伸,并且对应于制造p阱中的骤回ESD保护电路阵列中的第一骤回ESD保护电路。在一些实施例中,放置骤回ESD保护电路的阵列的布局设计还包括将第二有源区布局图案放置在第一布局层级中,第二有源区布局图案在第一方向上延伸,并且对应于制造p阱中的骤回ESD保护电路阵列的第一骤回ESD保护电路。在一些实施例中,放置骤回ESD保护电路阵列的布局设计还包括将第一阱布局图案放置在第一有源区布局图案或第二有源区布局图案上,并且在第二布局层级中,第一阱布局图案在与第一方向不同的第二方向上延伸,并且对应于制造骤回ESD保护电路阵列中的第一骤回ESD保护电路的第一n阱,第一n阱嵌入在p阱中并与之相邻到漏极区或源极区的部分。

已经描述了多个实施例。然而,将理解,可以在不脱离本公开的精神和范围的情况下进行各种修改。例如,示出为特定掺杂剂类型的各种晶体管(例如,N型或P型金属氧化物半导体(NMOS或PMOS))是出于说明的目的。本公开的实施例不限于特定类型。为特定晶体管选择不同的掺杂剂类型在各种实施例的范围内。在以上描述中使用的各种信号的低或高逻辑值也用于说明。当信号被激活和/或去激活时,各种实施例不限于特定的逻辑值。选择不同的逻辑值在各种实施例的范围内。在各种实施例中,晶体管用作开关。代替晶体管使用的开关电路在各种实施例的范围内。在各种实施例中,晶体管的源极可以被配置为漏极,并且漏极可以被配置为源极。这样,术语源极和漏极可互换使用。各种信号由相应的电路生成,但是为简单起见,未示出电路。

各种附图示出了使用分立电容器进行说明的电容性电路。可以使用等效电路。例如,可以使用电容性器件、电路或网络(例如,电容器、电容性元件、器件、电路等的组合)代替分立电容器。上面的图示包括示例性步骤,但是步骤不一定按所示顺序执行。根据所公开的实施例的精神和范围,可以适当地添加、替换、改变顺序和/或消除步骤。

上述概述了几个实施例的特征,以便本领域技术人员可以更好地理解本公开的各个方面。本领域技术人员应当理解,他们可以容易地使用本公开作为设计或修改用于实现本文所介绍的实施例的相同目的和/或实现其相同优点的其它过程和结构的基础。本领域技术人员还应当认识到,此类等效结构不背离本发明的精神和范围,并且它们可以在不背离本发明的精神和范围的情况下在本发明中进行各种改变、替换以及改变。

- 骤回静电放电(ESD)电路、ESD保护电路及其制造方法

- 静电放电(ESD)保护电路和免受静电放电影响的方法