一种相变存储器时序可重构布尔逻辑电路、方法及装置

文献发布时间:2023-06-19 12:21:13

技术领域

本发明涉及非易失性存储器计算领域,特别是涉及一种相变存储器时序可重构布尔逻辑电路及装置。

背景技术

相变存储器(Phase Change RandomAccess Memory,PCRAM)是一种新型非易失存储器,相变存储器凭借其高速、高密度、低功耗、与标准CMOS工艺兼容等诸多优点成为率先进入大规模商业化生产的新型非易失存储器。在非易失存储领域,提出了多种非易失器件逻辑操作,但是,现在大多数的非易失逻辑计算电路都有本身的局限性,如IMPLY逻辑电路实现逻辑功能需多器件多步操作,大大增加了电路时延,其输入输出均为忆阻器阻值,可靠性低。并且目前关于相变存储领域的非易失逻辑计算探究较少。

逻辑计算设计概念中,在交叉阵列中实现逻辑计算更为简单,使用双端电极完成单个相变存储单元的控制可实现非易失器件的布尔逻辑计算。虽然其更容易提出并设定,但难以构建,器件的物理性质和制造工艺的不成熟都使得新型非易失存储器如RRAM,PCRAM的阵列操作更加困难。

发明内容

本发明所要解决的技术问题是提供一种相变存储器时序可重构布尔逻辑电路及装置,能够在单个相变存储单元中实现多种逻辑计算。

本发明解决其技术问题所采用的技术方案是:提供一种相变存储器时序可重构布尔逻辑电路,包括相变存储单元和选通器件,所述相变存储单元的第一端与第一输入电极相连,第二端与所述选通器件的漏端相连,所述选通器件的源端与第二输入电极相连,栅端与控制端相连;通过控制所述第一输入电极、第二输入电极、控制端的输入信号以及所述相变存储单元的初始状态实现逻辑运算操作。

本发明解决其技术问题所采用的技术方案是:提供一种上述相变存储器时序可重构布尔逻辑电路的逻辑运算操作方法,包括以下步骤:

初始化并确定置位操作的表达式和复位操作的表达式;

接收逻辑运算指令后,基于所述逻辑运算指令确定预配置的操作步骤,其中,所述预配置的操作步骤根据置位操作的表达式和复位操作的表达式配置;

根据确定的预配置的操作步骤在所述控制端、第一输入电极和第二输入电极施加相应的脉冲信号。

所述置位操作的表达式为:

所述预配置的操作步骤为置1操作步骤时,所述控制端处于开启状态,所述第一输入电极输入SET信号,所述第二输入电极接地,使得所述相变存储单元的电阻状态置为低阻态;

所述预配置的操作步骤为置0操作步骤时,所述控制端处于开启状态,所述第一输入电极输入RESET信号,所述第二输入电极接地,使得所述相变存储单元的电阻状态置为高阻态。

所述预配置的操作步骤为置p操作步骤时,先完成所述置0操作步骤,接着,所述控制端处于开启状态,所述第一输入电极输入SET置位操作逻辑信号p,所述第二输入电极接地,实现置p的逻辑运算;

所述预配置的操作步骤为置q操作步骤时,先完成所述置0操作步骤,接着,所述控制端处于开启状态,所述第一输入电极输入SET置位操作逻辑信号q,所述第二输入电极接地,实现置p的逻辑运算;

所述预配置的操作步骤为置

所述预配置的操作步骤为置

所述预配置的操作步骤为OR操作步骤时,先完成所述置p操作步骤,接着,所述控制端处于开启状态,所述第一输入电极输入SET置位操作逻辑信号q,所述第二输入电极接地,将所述相变单元的电阻状态置为p+q,实现OR逻辑运算;

所述预配置的操作步骤为NOR操作步骤时,先完成所述置

所述预配置的操作步骤为AND操作步骤时,先完成所述置0操作步骤,接着,所述控制端施加逻辑信号p,所述第一输入电极输入SET置位操作逻辑信号q,所述第二输入电极接地,将所述相变单元的电阻状态置为p·q,实现AND逻辑运算;

所述预配置的操作步骤为NAND操作步骤时,先完成所述置1操作步骤,接着,所述控制端施加逻辑信号p,所述第一输入电极输入RESET复位操作逻辑信号q,所述第二输入电极接地,将所述相变单元的电阻状态置为

所述预配置的操作步骤为XNOR操作步骤时,先完成所述置1操作步骤,接着,所述控制端处于开启状态,所述第一输入电极输入RESET复位操作逻辑信号p,所述第二输入电极输入RESET复位操作逻辑信号q,将所述相变单元的电阻状态置为

所述预配置的操作步骤为XOR操作步骤时,先完成所述置0操作步骤,接着,所述控制端处于开启状态,所述第一输入电极输入SET置位操作逻辑信号p,所述第二输入电极输入SET置位操作逻辑信号q,将所述相变单元的电阻状态置为

所述预配置的操作步骤为IMP操作步骤时,先完成所述置1操作步骤,接着,所述控制端施加逻辑信号p,所述第一输入电极输入RESET复位操作逻辑信号q,所述第二输入电极输入RESET复位信号,将所述相变单元的电阻状态置为

所述预配置的操作步骤为RIMP操作步骤时,先完成所述置1操作步骤,接着,所述控制端施加逻辑信号q,所述第一输入电极输入RESET复位操作逻辑信号p,所述第二输入电极输入RESET复位信号,将所述相变单元的电阻状态置为

所述预配置的操作步骤为RNIMP操作步骤时,先完成所述置0操作步骤,接着,所述控制端施加逻辑信号p,所述第一输入电极输入SET置位信号,所述第二输入电极输入SET置位操作逻辑信号q,将所述相变单元的电阻状态置为

所述预配置的操作步骤为NIMP操作步骤时,先完成所述置0操作步骤,接着,所述控制端施加逻辑信号q,所述第一输入电极输入SET置位信号,所述第二输入电极输入SET置位操作逻辑信号p,将所述相变单元的电阻状态置为pq,实现NIMP逻辑操作。

本发明解决其技术问题所采用的技术方案是:还提供一种一位全加器,包括四个以2×2排列的如权利要求1所述的相变存储器时序可重构布尔逻辑电路,在实现一位全加操作时,选通第一列第一行的相变存储器时序可重构布尔逻辑电路进行

有益效果

由于采用了上述的技术方案,本发明与现有技术相比,具有以下的优点和积极效果:本发明利用相变存储器件的非易失性与阈值转换特性,构造了可重构非易失布尔逻辑计算函数表达式,在任意相变存储阵列中的单个单元都能够实现16种逻辑计算,通过对其外围电路的控制可实现可重构逻辑计算与存储功能,在非易失相变存储阵列中实现布尔逻辑计算,减少计算过程中数据在计算单元与存储单元之间的频繁传输,极大的减少计算单元数量,降低能耗。

附图说明

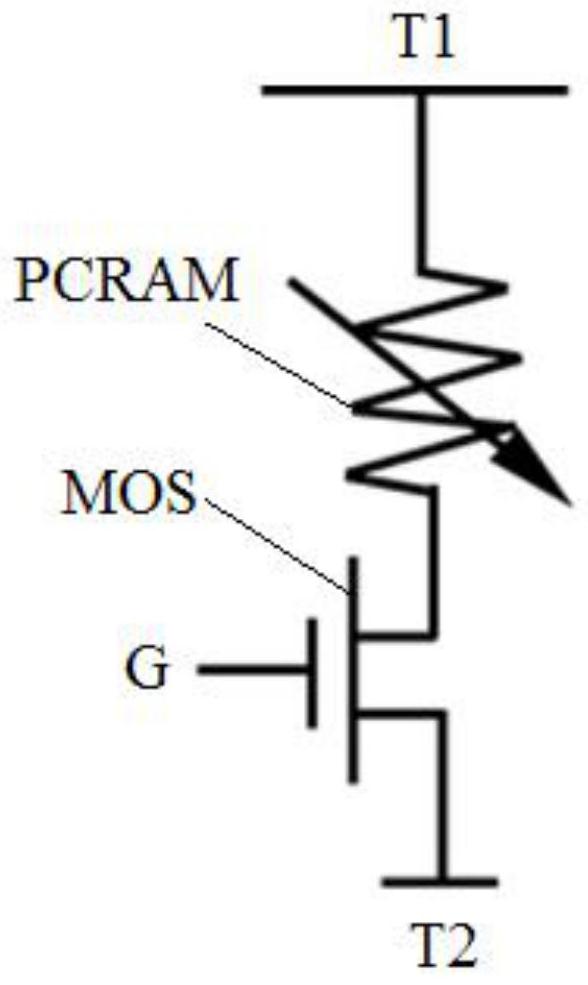

图1是本发明实施方式中相变存储器时序可重构布尔逻辑电路的简化模型图;

图2是本发明实施方式中相变存储器时序可重构布尔逻辑电路的置位操作真值表示意图;

图3是本发明实施方式中相变存储器时序可重构布尔逻辑电路的复位操作真值表示意图;

图4是本发明实施方式中相变存储器时序可重构布尔逻辑电路实现16中逻辑操作的示意图;

图5是本发明实施方式中一位全加器操作步骤示意图;

图6是本发明实施方式中Cin=0时的相变存储时序可重构逻辑计算加法器仿真结果图;

图7是本发明实施方式中Cin=1时的相变存储时序可重构逻辑计算加法器仿真结果图。

具体实施方式

下面结合具体实施例,进一步阐述本发明。应理解,这些实施例仅用于说明本发明而不用于限制本发明的范围。此外应理解,在阅读了本发明讲授的内容之后,本领域技术人员可以对本发明作各种改动或修改,这些等价形式同样落于本申请所附权利要求书所限定的范围。

本发明的实施方式涉及一种相变存储器时序可重构布尔逻辑电路,包括相变存储单元和选通器件,所述相变存储单元的第一端与第一输入电极相连,第二端与所述选通器件的漏端相连,所述选通器件的源端与第二输入电极相连,栅端与控制端相连;通过控制所述第一输入电极、第二输入电极、控制端的输入信号以及所述相变存储单元的初始状态实现逻辑运算操作。

如图1所示,本实施方式中的选通器件采用MOS管,该MOS管和相变存储单元组成的1T1R器件结构。

本实施方式的相变存储器时序可重构布尔逻辑电路的结果状态与两端的输入电极T1、输入电极T2,初始化器件状态Z’,MOS管栅极的控制端G的开启状态有关。根据阈值转变特性和输入运算变量,设计了16种逻辑操作需要的操作步骤和迭代顺序,大部分逻辑操作都可以通过一个初始化以及输入电极T1、输入电极T2、栅极的控制端G的一步迭代实现。

每个单元外围需控制电路,写入使能端、选通使能端、读出使能端同时控制,保证所有逻辑规则的实现。对于逻辑单元的操作需符合逻辑控制规则,输入控制脉冲需与初始化器件状态相对应。控制单元读写模式转换既可实现逻辑计算功能,又可完成数据的存储池,实现相变存储阵列的可重构逻辑计算。

由于相变存储器构成的是一种非易失型逻辑器件,所以其存储的阻值状态作为重要的条件参与并影响器件的逻辑操作,故在进行逻辑操作需要在第一步进行初始化处理并确定置位操作的表达式和复位操作的表达式。

置位与复位操作的真值表如图2和图3所示,其中,置位操作的表达式为:

其中,Z表示置位操作或复位操作结束后的状态,Z′表示置位操作或复位操作前的状态,T

在确定置位操作的表达式和复位操作的表达式后,可以接收逻辑运算指令,并基于所述逻辑运算指令确定预配置的操作步骤,其中,所述预配置的操作步骤根据置位操作的表达式和复位操作的表达式配置。最终可以根据确定的预配置的操作步骤在所述控制端、第一输入电极和第二输入电极施加相应的脉冲信号。

对于1T1R相变存储器件结构,定义二值逻辑“0”表示高阻态,二值逻辑“1”表示低阻态。对于逻辑算子中选通器件MOS管,当G为“1”时表示选通管导通,器件被选中,当G为“0”时表示选通管关断。

在相变存储器中实现逻辑操作,对于每种逻辑功能,都可在初始化、写入步骤完成,逻辑计算结果直接存储在相变单元中。每个器件都可单独实现所有的逻辑功能。16种不同的布尔逻辑具体的操作步骤包括:

当进行置1逻辑运算时,为控制端G施加选通信号,使得选通管导通选中操作器件,在所述上电极脉冲信号输入端T1施加SET信号,下电极脉冲信号输入端T2接GND,使得相变存储单元电阻状态置为低阻态,此时逻辑结果为1;

当进行置0逻辑运算时,为控制端G施加选通信号,使得选通管导通选中操作器件,在上电极脉冲信号输入端T1施加RESET信号,下电极脉冲信号输入端T2接GND,使得相变存储单元电阻状态置为高阻态,此时逻辑结果为0;

进行置p逻辑运算时,第一步初始化相变存储单元电阻状态,为控制端G施加选通信号,使得选通管导通选中操作器件,在上电极脉冲信号输入端T1施加RESET信号,下电极脉冲信号输入端T2接GND,使得相变存储单元电阻状态置为高阻态,完成初始化置0操作;接着,为控制端G施加选通信号,再通过对上电极脉冲信号输入端T1施加SET置位操作逻辑信号p,下电极脉冲信号输入端T2接GND,实现置p的逻辑运算;

当进行置q逻辑运算时,第一步初始化相变存储单元电阻状态,为控制端G施加选通信号,使得选通管导通选中操作器件,在上电极脉冲信号输入端T1施加RESET信号,下电极脉冲信号输入端T2接GND,使得相变存储单元电阻状态置为高阻态,完成初始化置0操作;接着,为控制端G施加选通信号,再通过对上电极脉冲信号输入端T1施加SET置位操作输入逻辑信号q,下电极脉冲信号输入端T2接GND,实现置q的逻辑运算;

当进行置

当进行置

当进行逻辑运算OR操作时,为控制端G施加选通信号,使得选通管导通选中操作器件,第一步初始化相变存储逻辑单元电阻状态,通过在上电极脉冲信号输入端T1施加RESET信号,下电极脉冲信号输入端T2接GND,使得相变存储单元电阻状态置为高阻态,即存储初始化结果为逻辑“0”;接着,为控制端G施加选通信号,再对上电极脉冲信号输入端T1施加SET置位操作输入逻辑信号p,下电极脉冲信号输入端T2接GND,将相变存储单元电阻状态置为p;然后,为控制端G施加选通信号,通过对上电极脉冲信号输入端T1施加SET置位操作输入逻辑信号q,下电极脉冲信号输入端T2接GND,将相变存储单元电阻状态置为p+q。

当进行逻辑运算NOR操作时,为控制端G施加选通信号,使得选通管导通选中操作器件,第一步在上电极脉冲信号输入端T1施加SET信号,下电极脉冲信号输入端T2接GND,使得相变存储单元电阻状态置为低阻态,完成初始化置1操作;接着,控制端G施加选通信号,再对上电极脉冲信号输入端T1施加RESET复位操作输入逻辑信号p,下电极脉冲信号输入端T2接GND,将相变存储单元电阻状态置为

当进行逻辑运算AND操作时,为控制端G施加选通信号,使得选通管导通选中操作器件,第一步在上电极脉冲信号输入端T1施加RESET信号,下电极脉冲信号输入端T2接GND,使得相变存储单元电阻状态置为高阻态,完成初始化置0操作;第二步,控制端G端施加逻辑信号p作为选通信号,对上电极脉冲信号输入端T1施加SET置位操作逻辑信号q,下电极脉冲信号输入端T2接GND,将相变存储单元电阻状态置为p·q。

当进行逻辑运算NAND操作时,为控制端G施加选通信号,使得选通管导通选中操作器件,第一步在上电极脉冲信号输入端T1施加SET信号,下电极脉冲信号输入端T2接GND,使得相变存储单元电阻状态置为低阻态,完成初始化置1操作;第二步,控制端G施加逻辑信号p作为选通信号,对上电极脉冲信号输入端T1施加RESET复位操作输入逻辑信号q,下电极脉冲信号输入端T2接GND,将相变存储单元电阻状态置为

当进行逻辑运算XNOR操作时,为控制端G施加选通信号,使得选通管导通选中操作器件,第一步在上电极脉冲信号输入端T1施加SET信号,下电极脉冲信号输入端T2接GND,使得相变存储单元电阻状态置为低阻态,完成初始化置1操作;第二步,控制端G施加选通信号,对上电极脉冲信号输入端T1施加RESET复位操作输入逻辑信号p,下电极脉冲信号输入端T2施加RESET复位操作输入逻辑信号q,将相变存储单元电阻状态置为

当进行逻辑运算XOR操作时,为控制端G施加选通信号,使得选通管导通选中操作器件,第一步在上电极脉冲信号输入端T1施加RESET信号,下电极脉冲信号输入端T2接GND,使得相变存储单元电阻状态置为高阻态,完成初始化置0操作;第二步,控制端G施加选通信号,对上电极脉冲信号输入端T1施加SET置位操作输入逻辑信号p,下电极脉冲信号输入端T2施加SET置位操作输入逻辑信号q,将相变存储单元电阻状态置为

当进行逻辑运算IMP操作时,为控制端G施加选通信号,使得选通管导通选中操作器件,在上电极脉冲信号输入端T1施加SET信号,下电极脉冲信号输入端T2接GND,使得相变存储单元电阻状态置为低阻态,完成初始化置1操作;接着,控制端G施加逻辑信号p作为选通信号,再通过对上电极脉冲信号输入端T1施加RESET复位操作输入逻辑信号q,下电极脉冲信号输入端T2施加RESET复位操作,将相变存储单元电阻状态置为

当进行逻辑运算RIMP操作时,为控制端G施加选通信号,使得选通管导通选中操作器件,在上电极脉冲信号输入端T1施加SET信号,下电极脉冲信号输入端T2接GND,使得相变存储单元电阻状态置为低阻态,完成初始化置1操作;接着,控制端G施加逻辑信号q作为选通信号,再通过对上电极脉冲信号输入端T1施加RESET复位操作输入逻辑信号q,下电极脉冲信号输入端T2施加RESET复位操作,将相变存储单元电阻状态置为

当进行逻辑运算RNIMP操作时,为控制端G施加选通信号,使得选通管导通选中操作器件,在上电极脉冲信号输入端T1施加RESET信号,下电极脉冲信号输入端T2接GND,使得相变存储单元电阻状态置为高阻态,完成初始化置0操作;接着,控制端G施加逻辑信号p作为选通信号,再通过对上电极脉冲信号输入端T1施加SET置位操作,下电极脉冲信号输入端T2施加SET置位操作输入逻辑信号q,将相变存储单元电阻状态置为

当进行逻辑运算NIMP操作时,为控制端G施加选通信号,使得选通管导通选中操作器件,在上电极脉冲信号输入端T1施加RESET信号,下电极脉冲信号输入端T2接GND,使得相变存储单元电阻状态置为高阻态,完成初始化置0操作;接着,控制端G施加逻辑信号q作为选通信号,再通过对上电极脉冲信号输入端T1施加SET置位操作,下电极脉冲信号输入端T2施加SET置位操作输入逻辑信号p,将相变存储单元电阻状态置为

如图4所示,除OR与NOR以外的逻辑操作只需两步即可完成复杂的逻辑计算,且第一步为初始化操作。

对于传统的CMOS器件的实现一位加法器需要2个异或逻辑门,2个与逻辑门,1个或逻辑门。实现一位加法器需要38个mos器件,对于面积消耗很大。使用高密度低功耗的相变存储器布尔逻辑阵列完成存算一体的一位加法器计算可以只需要4个器件,5时序步骤以内完成。

本实施方式提供一种一位全加器,包括四个以2×2排列的上述相变存储器时序可重构布尔逻辑电路,其中,第一列第一行的相变存储器时序可重构布尔逻辑电路记作WL1BL1,第一列第二行相变存储器时序可重构布尔逻辑电路记作WL2BL1,第二列第一行的相变存储器时序可重构布尔逻辑电路记作WL1BL2,第二列第二行的相变存储器时序可重构布尔逻辑电路记作WL2BL2。本实施方式基于相变存储器的非易失特性,通过五个步骤实现相变存储的加法操作,通过级联操作可以实现整体功能的存内逻辑计算功能。由于它的非易失特性,逻辑加法器实现过程需要不断地进行状态的迭代,由于相变存储器固有的非易失物理特性,器件只有经过相应迭代,才能将最终将结果保存在存储器阵列中,保证相变逻辑算子操作结果的正确性。阵列操作匹配外围读写电路,操作过程节省功耗了功耗,结果保证计算的准确性。逻辑操作过程也简单清晰,最少的功耗和器件面积。实现器件基本逻辑功能,对于外围电路与阵列的整合,对于存内计算的实现,最终组成完备的存内计算操作。

传统的加法器可以分为串行加法器、超前进位加法器和流水线加法器。其中串行加法器结构简单但延时较大;超前进位加法器优化了计算逻辑,减少了计算延迟,但是增加了器件复杂度,流水线加法器通过并行计算提高吞吐量。对于相变存储单元非易失逻辑计算,每个单元可实现16种逻辑计算,但单次逻辑操作只能实现一次逻辑操作,不能对复杂的逻辑架构进行并行处理,所以对于超前进位加法的优势不能充分展现,反而增加了时间和功耗开销。同时受器件结构限制,流水线加法器实现复杂度较大,故串行加法器是最能发挥非易失相变存储器优势的操作方式。

由于相变存储单元的非易失特性,逻辑算子的阻值状态参与每一步的逻辑计算,因此计算结果不需要级联直接存储在相变存储单元中,参与下一步同器件的逻辑计算。同时基于非易失逻辑操作算子操作规则,在不同器件单元进行的复杂逻辑计算需要外围电路的支持。逻辑操作阵列外围布局可以实现逻辑操作级联进行逻辑计算结果的传递,在串行加法器中,逻辑输出作为下一级的输入传递给下一级器件。图5表示基于1T1R相变存储器逻辑算子的一位全加器操作步骤。

对于一位全加操作的计算公式:

基于1T1R相变存储器逻辑算子的一位全加器操作步骤:

第一步:在第一列中,选通WL1BL1和WL2BL1器件单元,对选中的器件单元计算

第二步:选中WL1BL1,将第一步计算结果进行读出。

第三步:在第二列中,选通WL1BL2和WL2BL2器件单元,对选中的WL1BL2器件单元计算

第四步:选中WL2BL1单元,将第一步的计算结果读出,进行数据传输作为下一步的输入数据。

第五步:将前一步读出的结果作为输入逻辑信号,且在WL2BL2器件单元中在第三步计算存储的结果由于器件的非易失性,直接参与这一步的逻辑计算操作,得到一位加法器的进位值

本发明使用相变存储单元的SPICE模型,搭建仿真电路。设定相变存储器仿真参数Rset=10KΩ,Rreset=1MΩ,Tset=100ns,Treset=20ns,令低阻态到高阻态的阈值电压为2.5V,高阻态到低阻态的阈值电压为2.5V。逻辑实现过程需控制端、初始状态、输入脉冲信号对应从而实现所有的逻辑操作。使用相变存储单元SPICE模型进行仿真实现的逻辑计算过程,得到仿真结果如图6和图7所示,实现多次逻辑级联,根据仿真结果图可以得出,电路仿真结果均与全加器真值表一致。

不难发现,本发明提出了一种通用逻辑电路,其可以在单个相变存储单元中实现16种逻辑计算,在任意相同的阵列中实现加法器应用。基于单个的逻辑门结构,可以通用的设计组合逻辑架构,可以实现任意一种逻辑电路。对于提出的时序逻辑电路方法,可以实现可重构式计算。对比之前提出的非易失逻辑计算方式,器件更少,逻辑操作实现更便捷,提高了逻辑大规模实现的准确性,同时使用相变存储单元SPICE模型,仿真验证了加法器运算,证明在相变存储器阵列中,时序可重构逻辑计算加法器逻辑设计的可行性与有效性,并实现了多种逻辑通用结构,产生逻辑级联。相变存储逻辑计算阵列可作为性能优化的内存计算平台,由于对原始数据进行预处理计算,减少处理器与存储器之间的长距离数据传输功耗,实现在任意一个相变存储单元之间执行任意逻辑函数计算,并在任意相变存储单元阵列中执行计算与存储的可重构操作。

- 一种相变存储器时序可重构布尔逻辑电路、方法及装置

- 一种多值相变存储器单元、逻辑电路及多进制运算方法