III族氮化物增强型HEMT器件及其制作方法

文献发布时间:2023-06-19 18:29:06

技术领域

本发明涉及一种新型氮化物增强型高电子迁移率晶体管(HEMT)及其制备方法,特别涉 及一种新型的具有高可靠性和稳定性的III族氮化物增强型HEMT及其制备方法,属于半导体 电子器件技术领域。

背景技术

III族氮化物半导体被称为第三代半导体,具有禁带宽度大、化学稳定性好、击穿电压高等 优势;而且由AlGaN/GaN等异质结构成的高电子迁移率晶体管(HEMT)具有高电子浓度和迁 移率的优势,在高频、高耐压、低导通电阻等方面表现优异,可用作各类电力转化系统中的核 心器件,在消费电子、5G基站、服务器等电源应用领域具有广阔的前景。

通常,III族氮化物增强型HEMT的栅极多采用金属/p-GaN/AlGaN/GaN堆栈结构,p-GaN层 掺有Mg受主,用于抬高AlGaN/GaN层的能带以耗尽2DEG,从而达到增强型的目的,此类器件 多称为p-GaN栅增强型HEMT(p-GaN E-HEMT)。在实际应用中,p-GaN栅极电压处于高/低电 压快速切换的过程中,由于感性负载的存在可能造成栅极电压过冲现象;而且高频率的开关动 作,要求栅极堆栈结构中载流子的输运具有同步的高频响应。因此,这些实际应用的性能、特 别是可靠性,对p-GaN E-HEMT走向商用化至关重要。

常见的栅极结构为“金属/p-GaN/AlGaN/GaN”堆栈结构,如图1a所示。栅极金属层多采用蒸 发、溅射等加工方法沉积,功函数在4-6eV范围内,如Ti、Ni、Pd等;p-GaN/AlGaN/GaN叠层 多采用MOCVD外延生长,p-GaN层为几乎均匀掺Mg的、掺杂浓度1-3×10

如图1a、图1b所示,金属/p-GaN/AlGaN/GaN堆栈的栅极可以等效为金属/p-GaN构成的“肖 特基结”(J

现有的III族氮化物增强型HEMT的栅极多为金属/p-GaN/AlGaN/GaN堆栈结构,p-GaN外延 生长采用Mg掺杂等作为受主提供空穴,且存在如下缺陷:

其一,现有技术的p-GaN层多为掺杂几乎均匀、浓度大约为10

其二,现有技术的AlGaN层为Al组分均匀、且通常在10%-30%的单层结构。由于AlGaN的 禁带宽度大于GaN,因此,无论是p-GaN中的空穴注入到GaN沟道、还是GaN沟道中的电子注入 到p-GaN中,均需要克服AlGaN在价带或导带上的势垒。在动态开关过程中,由于价带势垒对p- GaN中空穴的阻挡,大量空穴会在p-GaN/AlGaN界面发生积累,从而造成动态阈值电压漂移等 动态可靠性的问题。

发明内容

本发明的主要目的在于提供一种III族氮化物增强型HEMT器件及其制作方法,以克服现 有技术中的不足。

为实现前述发明目的,本发明采用的技术方案包括:

本发明实施例一方面提供了一种III族氮化物增强型HEMT器件,包括外延结构以及与外 延结构配合的源极、漏极和栅极,所述外延结构包括依次叠设的沟道层、势垒层和p型半导 体,

所述外延结构还包括叠设在p型半导体上的Al

其中,所述势垒层为Al

进一步的,所述势垒层与p型半导体接触界面处的Al含量为0-10%。

进一步的,所述势垒层内的Al含量沿远离沟道层的方向降低。

进一步的,所述势垒层内的Al含量沿远离沟道层的方向渐变或阶跃跳变。

进一步的,所述势垒层内的平均Al组分含量为5-50%。

进一步的,所述势垒层的厚度为1-100nm,优选为5-50nm。

在一些较为具体的实施方案中,所述p型半导体和Al

在一些较为具体的实施方案中,所述势垒层的栅下区域形成有凹槽,且所述凹槽被p型半 导体的局部区域填充。

在一些较为具体的实施方案中,所述势垒层包括设置在沟道层上的第一势垒层和第二势垒 层,所述第二势垒层分布在第一势垒层与p型半导体之间,并且所述第二势垒层内的Al含量沿 远离沟道层的方向降低。

进一步的,所述第二势垒层内的Al含量沿远离沟道层的方向渐变或阶跃跳变。

进一步的,所述第一势垒层中的Al组分是均匀分布的。

在一些较为具体的实施方案中,所述第二势垒层连续覆盖第一势垒层;或者,所述第二势 垒层仅覆盖第一势垒层的栅下区域;或者,所述第一势垒层的栅下区域至少被部分移除而形成 槽状结构,所述槽状结构被第二势垒层填充。

进一步的,所述第二势垒层与p型半导体的导电类型相同。

在一些较为具体的实施方案中,所述第一势垒层包括依次层叠的第一Al

进一步的,所述GaN中间层和第二Al

在一些较为具体的实施方案中,所述第二势垒层的栅下区域形成有凹槽,且所述凹槽被p 型半导体的局部区域填充。

进一步的,所述Al

进一步的,所述Al

进一步的,所述势垒层为非故意掺杂层。

进一步的,所述p型半导体的厚度为10-300nm。

进一步的,所述p型半导体的受主掺杂浓度为(1-8)×10

在一些较为具体的实施方案中,所述的III族氮化物增强型HEMT器件还包括衬底,所述 衬底上依次叠设有过渡层、高阻层,所述沟道层叠设在高阻层上。

本发明实施例还提供了所述的III族氮化物增强型HEMT器件的制作方法,其包括:

制作外延结构,所述外延结构包括依次叠设的沟道层、势垒层、p型半导体和Al

制作与所述外延结构配合的源极、漏极和栅极。

在一些较为具体的实施方案中,所述的制作方法具体包括:在衬底上依次生长形成沟道 层、势垒层、p型半导体和Al

在一些较为具体的实施方案中,所述的制作方法具体包括:在衬底上依次生长形成沟道层 和势垒层,并将势垒层的栅下区域部分移除从而在势垒层中形成凹槽;之后在所述势垒层上继 续生长p型半导体和Al

进一步的,所述的制作方法具体包括:将p型半导体和Al

在一些较为具体的实施方案中,所述的制作方法具体包括:在沟道层上依次生长第一势垒 层和第二势垒层,从而形成所述势垒层。

进一步的,所述的制作方法具体包括:将Al

在一些较为具体的实施方案中,所述的制作方法具体包括:在沟道层上生长第一势垒层 后,将第一势垒层的栅下区域去除从而形成槽状结构,之后在第一势垒层上生长第二势垒层, 并使所述槽状结构被第二势垒层填充,从而形成所述势垒层。

在一些较为具体的实施方案中,所述的制作方法具体包括:在沟道层上依次生长第一 Al

在一些较为具体的实施方案中,所述的制作方法具体包括:将所述GaN中间层和第二 Al

在一些较为具体的实施方案中,所述的制作方法具体包括:将所述第二势垒层的栅下区域 的部分除去而形成凹槽,或者,沿所述第一势垒层及其槽状结构的表面连续生长第二势垒层, 而使所述第二势垒层位于槽状结构内的部分形成凹槽,之后在所述第二势垒层上生长p型半导 体,并使所述凹槽被p型半导体的局部区域填充。

进一步的,所述的制作方法具体包括:将p型半导体、Al

与现有技术相比,本发明的优点包括:

1)本发明实施例提供的一种具有高可靠性和稳定性的III族氮化物增强型HEMT器件,通 过在栅下的p型半导体上增加一层低掺杂浓度的(Al)GaN层,从而提高了p型半导体的晶体质 量,降低了金属/半导体形成的肖特基结结区电场强度,减小该肖特基结的失效概率;

2)本发明还在p型半导体下方的设置了可变Al组分的AlGaN势垒层,从而减小甚至消除 了p-GaN/AlGaN之间的价带带阶差,克服了动态开启过程中因空穴在此处的积累而造成的阈值 电压漂移等可靠性问题;

3)本发明提供的III族氮化物增强型HEMT器件具有更高的栅极工作寿命和更小的栅极动 态阈值电压漂移,器件的可靠性可以得到大幅提升。

附图说明

图1a是一种常规的III族氮化物增强型HEMT器件的结构及栅极等效结构示意图;

图1b是一种常规的III族氮化物增强型HEMT器件的能带结构示意图;

图2是本发明一典型实施案例中提供的一种III族氮化物增强型HEMT器件的外延结构的 结构示意图;

图3是本发明一典型实施案例中提供的一种III族氮化物增强型HEMT器件的外延结构的 结构示意图;

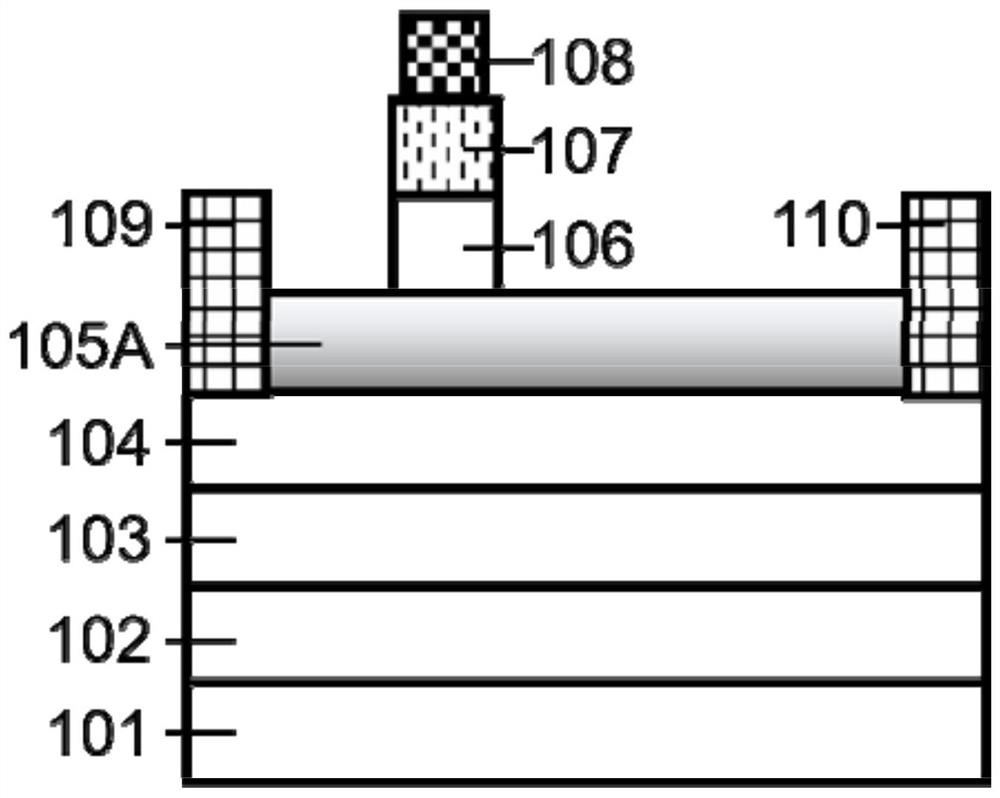

图4a是本发明一典型实施案例中提供的一种III族氮化物增强型HEMT器件的结构示意 图;

图4b是本发明一典型实施案例中提供的又一种III族氮化物增强型HEMT器件的结构示意 图;

图4c是本发明一典型实施案例中提供的又一种III族氮化物增强型HEMT器件的结构示意 图;

图4d是对比例1中提供的一种III族氮化物增强型HEMT器件的结构示意图;

图4e是对比例2中提供的又一种III族氮化物增强型HEMT器件的结构示意图;

图5是本发明一典型实施案例中提供的一种III族氮化物耗尽型HEMT器件的外延结构的 结构示意图;

图6是本发明一典型实施案例中提供的一种III族氮化物耗尽HEMT器件的外延结构的结 构示意图;

图7是本发明一典型实施案例中提供的一种III族氮化物耗尽HEMT器件的外延结构的结 构示意图;

图8是本发明一典型实施案例中提供的一种III族氮化物增强型HEMT器件的外延结构的 结构示意图;

图9a是本发明一典型实施案例中提供的一种III族氮化物增强型HEMT器件的结构示意 图;

图9b是本发明一典型实施案例中提供的又一种III族氮化物增强型HEMT器件的结构示意 图;

图9c是本发明一典型实施案例中提供的又一种III族氮化物增强型HEMT器件的结构示意 图。

具体实施方式

鉴于现有技术中的不足,本案发明人经长期研究和大量实践,得以提出本发明的技术方 案。如下将对该技术方案、其实施过程及原理等作进一步的解释说明。

针对现有技术中存在的问题,本案发明人研究发现,单一改进p-(Al)GaN或p-(In)AlN 表层受主掺杂浓度,无法改善器件的动态阈值电压漂移等性能;单一改进AlGaN势垒层或 InAlN势垒层能带结构,又无法提升器件的使用寿命;基于此,本案发明人提出同时在p-(Al) GaN层或p-(In)AlN层上方外延生长一层低掺浓度的(Al)GaN层,在p-(Al)GaN层或p-(In)AlN层下方外延生长一层Al组分可变的AlGaN势垒层或InAlN势垒层,以此增强栅极 的使用寿命、提升栅控性能的稳定性等。

具体的,本发明降低p-(Al)GaN层或p-(In)AlN层上方(Al)GaN的掺杂浓度意味着有效 受主(或施主)浓度降低,可使“肖特基结”反偏时耗尽区宽度增大,电场强度减小,载流子 不易隧穿或获得过多能量去激活原有缺陷或产生新的缺陷。此外,MOCVD生长低掺浓度的 (Al)GaN层的条件有助于提高外延层(或外延结构)的晶体质量,减少C等杂质并入以及空位 等缺陷态的产生;并且高晶体质量的(Al)GaN层不易形成缺陷态,亦可大幅提升肖特基结的可 靠性,增强器件栅极的使用寿命。

更进一步的,本发明降低与p-(Al)GaN层接触的下方AlGaN势垒层中的Al组分,或者, 采用渐变Al组分、阶跃变化的Al组分的AlGaN势垒层,可以实现p-(Al)GaN与AlGaN势垒层之间价带带阶减小甚至消失,消除动态开启过程中空穴的大量积聚,从而缓解器件动态阈值 电压漂移的问题,提升p-GaN E-HEMT的动态稳定性和可靠性。

如下将结合具体实施案例和附图对该技术方案、其实施过程及原理等作进一步的解释说 明,除非特别说明的之外,本案实施例中所采用的外延生长、图形化处理工艺、刻蚀工艺等均 可以采用现有工艺;需要说明的是,如下以AlGaN势垒层和与其对应的p-(Al)GaN层为例对 本发明的技术方案介绍,相应地,其中的势垒层亦可以是InAlN势垒层,相应地,所述p形半 导体也可以是p-(In)AlN层。

为实现上述发明目的,本发明实施例主要提供了两种技术方案来实现:

在一具体的实施方案中,请参阅图2-图4a,一种具有高可靠性和稳定性的III族氮化物增 强型HEMT的制备方法,包括如下步骤:

1)请参阅图2,在衬底101上生长III族氮化物增强型HEMT外延结构:所述外延结构具 体包括依次叠设的过渡层102、高阻耐压层(如下可简称为高阻层)103、导电沟道层(如下可 简称为沟道层)104、Al组分可变的势垒层105A、p型(Al)GaN层106和低掺杂浓度的(Al)GaN 层107;

2)请参阅图3,对栅极区域(即前述栅下区域,即位于栅极正下方的区域,或者用于生长 栅极的区域,下同)光刻图形化处理后,采用干法刻蚀等方法去除非栅极区域的(Al)GaN层107 和p型(Al)GaN106,使刻蚀终止在AlGaN势垒层105A表面;并对非栅极区域的AlGaN势垒层 105A进行一定的表面处理(表面处理的工艺可以为:先以HF进行酸清洗,之后以KOH进行 碱湿法腐蚀,然后再以HF进行酸清洗,该工艺只是其中的一种具体方式,本领域技术人员当 然还可以采用其他的表面处理工艺来达到相同的效果,下同),以去除表面氧化层和损伤层;

3)在(Al)GaN层107的栅极区域沉积栅极金属108,并退火形成栅极接触(即肖特基接 触,下同);分别在源极、漏极区域沉积源极金属109、漏极金属110,退火形成欧姆接触;形 成的器件结构如图4a-图4c所示。

在另一具体的实施方案中,请参阅图5-图8,一种具有高可靠性和稳定性的 III族氮化物增强型HEMT的制备方法,包括如下步骤:

1)请参阅图5和图6,在衬底201上生长III族氮化物耗尽型HEMT外延结构,所述外延 结构具体包括依次叠设的过渡层202、高阻耐压层203、导电沟道层204、Al组分可变的势垒层 205A,对栅极区域进行光刻图形化处理后,采用干法刻蚀等方法去除部分位于栅极区域的组分 可变的AlGaN势垒层;

2)请参阅图7,采用二次外延的方法在势垒层205A上依次外延一层p型(Al)GaN层206、 低掺杂浓度的(Al)GaN层207;

3)请参阅图8,栅极区域光刻图形化后,采用干法刻蚀等方法去除非栅极区域的p型 (Al)GaN层206、(Al)GaN层207,使刻蚀终止在AlGaN势垒层205A表面以恢复非栅区域的二 维电子气;之后对非栅极区域的AlGaN势垒层205A进行一定的表面处理,以去除表面氧化层 和损伤层;

4)在(Al)GaN层207上沉积栅极金属208,并退火形成稳定的栅极接触;分别在源极区 域、漏极区域沉积源极金属209、漏极金属210,退火形成欧姆接触,形成的器件结构如图9a- 图9c所示。

需要说明的是,以上两种方案还可以包括更多后续的器件加工工艺,比如在AlGaN势垒层 106A/B上制作表面钝化层以及沉积介质层,之后再进一步在栅极208、源极209上制作场板结 构等。

需要特别说明的是,以上两种方案的关键点均在于在p型栅堆栈结构中引入了Al组分可变 的势垒层和低掺杂浓度的(Al)GaN层,即该p型栅堆栈结构可以理解为p型栅极,该p型栅堆 栈结构或p型栅极包括叠设的p型半导体、Al

具体的,Al组分可变的势垒层的特点与功能在于:该层与p型半导体(例如p型(Al)GaN 层106/206)接触处(即接触界面)的Al组分保持一致,该接触处的Al组分从0-100%可调, 特别的,主要控制在0-10%。当然,所述势垒层可以是与p型半导体接触的部分内的Al组分可 变,也可以是整个势垒层采用Al组分渐变的方式来生长,如此从p型半导体至势垒层均不会存 在明显的能带带阶差,从而使得栅极正向电压下,空穴不易被阻挡在AlGaN势垒层表面而形成 的空穴积聚效应,从而减小动态阈值电压负移等退化现象。该Al组分可变的势垒层的厚度控制 在5-50nm,平均Al组分控制在5-50%。

具体的,低掺杂浓度的(Al)GaN层(即前述第二半导体,下同)的特点与功能在于:该层 具有较低的掺杂浓度和较高的晶体质量度,该层可以是GaN或者Al组分不超过10%的AlGaN,该层可以是p型材料(受主浓度≤5×10

实施例1

请参阅图2、图3和图4a,一种具有高可靠性和稳定性的III族氮化物增强型HEMT的制 备方法,包括如下步骤:

1)采用金属有机气相沉积(MOCVD)的方法,在Si<111>衬底101上沉积300nm AlN/AlGaN过渡层102,然后依次外延4μm C掺杂的Al

2)采用光刻胶作为掩膜,在非故意掺杂的GaN层107表面光刻图形,之后利用感应耦合等 离子体(ICP)刻蚀法去除非栅极区域的低掺杂浓度的p-GaN层107、均匀掺杂p-GaN层106,使 刻蚀停止在Al组分可变的AlGaN势垒层105A,以恢复二维电子气;

3)采用丙酮等作为清洗剂清洗去除光刻胶,然后利用氢氟酸(HF)等去去除AlGaN势垒 层表面的氧化层,并于在500℃、N

采用I-V、I-t等方法对制备的器件进行栅极失效测试,推算得到栅极工作10年1%器件发生 失效的工作电压达7.5V;采用脉冲I-V法对所获III族氮化物增强型HEMT器件进行动态阈值电压 漂移测试,该器件的阈值电压电压漂移0.15V(常规器件两组数据分别为≤6.5V,≥0.4V), 由此证实本发明制备的p型栅增强型HEMT具有很高的栅极可靠性和稳定性。

实施例2

请参阅图2、图3和图4b,一种具有高可靠性和稳定性的III族氮化物增强型HEMT的制 备方法,包括如下步骤:

1)采用金属有机气相沉积(MOCVD)等方法在Si<111>衬底101上沉积300nm AlN/AlGaN 过渡层102,然后在AlN/AlGaN过渡层102上依次外延4μm C掺杂的Al

2)采用光刻胶作为掩膜,在非故意掺杂的GaN层107表面光刻图形,之后利用ICP刻蚀等方 法去除非栅极区域的非故意掺杂的GaN层107、p-GaN层106,使刻蚀停止在Al组分可变AlGaN势 垒层105A,以恢复二维电子气;

3)采用丙酮等有机清洗的方法去除光刻胶,然后利用氢氟酸(HF)等去去除AlGaN势垒 层表面氧化层,在500℃、N

采用I-V、I-t等方法对制备的器件进行栅极失效测试,推算得到栅极工作10年1%器件发生 失效的工作电压达7.8V;采用脉冲I-V法对制备的III族氮化物增强型HEMT器件进行动态阈值电 压漂移测试,所获器件的阈值电压电压漂移0.12V(常规器件两组数据分别为≤6.5V,≥0.4 V),由此证明本发明制备的p型栅增强型HEMT具有很高的栅极可靠性和稳定性。

实施例3

请参阅图2、图3和图4c,一种具有高可靠性和稳定性的III族氮化物增强型HEMT的制 备方法与实施例2基本相同,不同之处在于:本实施例中Al组分可变的AlGaN势垒层105A为 p型半导体材料,并且所述Al组分可变的AlGaN势垒层105A仅分布在栅极区域。

实施例4

请参阅图5-8和图9a,一种具有高可靠性和稳定性的III族氮化物增强型HEMT的制备方 法,包括如下步骤:

1)采用金属有机气相沉积(MOCVD)等方法在Si<111>衬底201上沉积300nm AlN/AlGaN 过渡层202,然后在AlN/AlGaN过渡层202上依次外延4μm C掺杂的Al

2)采用光刻胶作为掩膜,在AlGaN势垒层205A表面光刻图形化后利用ICP等刻蚀方法去除 栅极区域厚度为35nm的AlGaN势垒层205A,以形成图形结构;之后采用湿法表面处理和 MOCVD高温工艺对AlGaN势垒层205A进行热处理,之后在AlGaN势垒层205A上依次二次外延 70nm Mg掺杂浓度均匀在(2-3)×10

3)采用光刻胶作为掩膜,在p型GaN层207上光刻图形,之后利用ICP刻蚀等方法去除非栅 极区域的低掺杂浓度的p-GaN层207、均匀掺杂p-GaN层206,使刻蚀停止在Al组分可变AlGaN势 垒层205A,以恢复二维电子气;

4)采用丙酮等作为清洗剂去除光刻胶;之后利用氢氟酸(HF)等去去除AlGaN势垒层 205A表面的氧化层,在500℃、N

在栅极区域沉积Ti/Au作为栅极金属208,退火后使栅极金属208与低掺杂浓度p型GaN层207 形成稳定的栅接触,分别在源极区域、漏极区域沉积Ti/Al/Ti/Au作为源极金属209、漏极金属 210,退火后形成欧姆接触,从而形成III族氮化物增强型HEMT器件。

采用I-V、I-t等方法对制备的器件进行栅极失效测试,推算得到栅极工作10年1%器件发生 失效的工作电压达7.5V;采用脉冲I-V法对制备的III族氮化物增强型HEMT器件进行动态阈值电 压漂移测试,所获器件的阈值电压电压漂移0.16V(常规器件两组数据分别为≤6.5V,≥0.4 V),由此可以证实本发明制备的p型栅增强型HEMT具有很高的栅极可靠性和稳定性。

实施例5

请参阅图5-8和图9c,一种具有高可靠性和稳定性的III族氮化物增强型HEMT的制备方 法,包括如下步骤:

1)采用金属有机气相沉积(MOCVD)等方法在Si<111>衬底201上沉积300nm AlN/AlGaN 过渡层202,然后在AlN/AlGaN过渡层202上依次外延4μm C掺杂的Al

2)采用光刻胶作掩膜,在Al

3)采用光刻胶作为掩膜,在n型Al

4)采用丙酮等作为清洗剂去除光刻胶;然后利用氢氟酸(HF)等去去除Al组分可变势垒 层205A表面的氧化层,在500℃、N

在栅极区域沉积Ti/Au作为栅极金属208,退火后使栅极金属208与n型Al

采用I-V、I-t等方法对制备的器件进行栅极失效测试,推算得到栅极工作10年1%器件发生 失效的工作电压达8.0V;采用脉冲I-V法对制备的III族氮化物增强型HEMT器件进行动态阈值电 压漂移测试,所获器件的阈值电压电压漂移0.15V(常规器件两组数据分别为≤6.5V,≥0.4 V),由此证明本发明制备的p型栅增强型HEMT具有很高的栅极可靠性和稳定性。

实施例6

请参阅图5-8和图9b,一种具有高可靠性和稳定性的III族氮化物增强型HEMT的制备方 法,包括如下步骤:

1)采用金属有机气相沉积(MOCVD)等方法在Si<111>衬底201上沉积300nm AlN/AlGaN 过渡层202,然后在AlN/AlGaN过渡层202上依次外延4μm C掺杂的Al

2)采用光刻胶作掩膜,在AlGaN势垒层205B上光刻图形,利用ICP刻蚀等方法除去栅极区 域的AlGaN势垒层205B依次对外延结构的表面进行HF酸洗、KOH碱洗、HF酸洗,之后载入MOCVD中,并在870℃、NH

3)采用光刻胶作为掩膜,在n型Al

4)采用丙酮等作为清洗剂去除光刻胶;然后利用氢氟酸(HF)等去去除Al组分可变势垒 层205A表面的氧化层,在500℃、N

在栅极区域沉积Ti/Au作为栅极金属208,退火后使栅极金属208与n型Al

采用I-V、I-t等方法对制备的器件进行栅极失效测试,推算得到栅极工作10年1%器件发生 失效的工作电压达8.2V;采用脉冲I-V法对制备的III族氮化物增强型HEMT器件进行动态阈值电 压漂移测试,所获器件的阈值电压电压漂移0.12V(常规器件两组数据分别为≤6.5V,≥0.4 V)由此证明本发明制备的p型栅增强型HEMT具有很高的栅极可靠性和稳定性。

需要特别说明的是,本发明实施例中的Al组分可变势垒层(105A、205A)的Al组分变化 方式可以为:i)渐变式:包括线性渐变和非线性渐变;ii)阶跃式:包括等组分阶跃和非等组 分阶跃;低掺杂浓度的(Al)GaN层(107、207)的掺杂可以为:i)p型,表层Mg的掺杂浓度不超过5×10

对比例1

请参阅图4d,一种III族氮化物增强型HEMT的制备方法与实施例2基本相同,不同之处 在于:本实施例中势垒层仅有20nm、均匀Al组分的AlGaN 105B层,其中的Al含量为0.2。

采用I-V、I-t等方法对制备的器件进行栅极失效测试,根据结果推算得到栅极工作10年 1%器件发生失效的工作电压达7.41V;采用脉冲I-V法对制备的III族氮化物增强型HEMT器 件进行动态阈值电压漂移测试,阈值电压电压漂移0.65V。

对比实施例1或实施例2可以发现:单一改进p-GaN表层受主掺杂浓度,栅极工作电压较 常规器件(≤6.5V)有大幅提升,表明栅极寿命延长,但阈值电压漂移(常规器件≥0.4V)并 未得到改善。

对比例2

请参阅图4e,一种III族氮化物增强型HEMT的制备方法与实施例2基本相同,不同之处 在于:本实施例中无50nm p型GaN 107层,取而代之的是120nm的Mg掺杂浓度为(2-3)×10

采用I-V、I-t等方法对制备的器件进行栅极失效测试,根据结果推算得到栅极工作10年 1%器件发生失效的工作电压为6.02V;采用脉冲I-V法对制备的III族氮化物增强型HEMT器 件进行动态阈值电压漂移测试,阈值电压电压漂移0.17V。

对比实施例1或实施例2可以发现:单一改进AlGaN层能带结构,栅极阈值电压漂移0.17 V较常规器件(≥0.4V)有大幅提升,但栅极工作电压(常规器件≤6.5V)并未得到提升,即 栅极寿命没有延长。

本发明实施例提供一种新型的具有高可靠性和稳定性的III族氮化物增强型HEMT及其制 备方法,在p-GaN层(即第一半导体)上方增加一层低掺杂浓度的(Al)GaN层(即第二半导 体),以降低金属/半导体构成结的结区电场强度,同时可通过改变MOCVD生长条件提升表层 半导体的晶体质量,最终达到高质量金属/半导体肖特基结的制备,提高器件栅极使用寿命等性 能;以及,本发明降低p-GaN层下方AlGaN势垒层中的Al组分,或者,采用渐变Al组分的势 垒层,实现p-GaN/AlGaN带阶差的减小甚至消除,从而减小动态开启过程中空穴在p- GaN/AlGaN界面的积聚效应,提升器件的动态稳定性和可靠性。

本发明同时在p-GaN的上方增加一层低掺杂浓度的(Al)GaN层,并降低p-GaN下方的 AlGaN势垒层的低Al组分或采用渐变Al组分的势垒层,以综合改善p-GaN栅极的使用寿命、 动态阈值电压稳定性和可靠性等。

本发明实施例提供的一种具有高可靠性和稳定性的III族氮化物增强型HEMT器件,通过 在栅下的p型半导体上增加一层低掺杂浓度的(Al)GaN层,从而提高了p型半导体的晶体质 量,降低了金属/半导体形成的肖特基结结区电场强度,减小该肖特基结的失效概率;同时,本 发明还在p型半导体下方的设置了可变Al组分的AlGaN势垒层,从而减小甚至消除了p- GaN/AlGaN之间的价带带阶差,克服了动态开启过程中因空穴在此处的积累而造成的阈值电压 漂移等可靠性问题;以及,本发明提供的III族氮化物增强型HEMT器件具有更高的栅极工作 寿命和更小的栅极动态阈值电压漂移,器件的可靠性可以得到大幅提升。

应当理解,上述实施例仅为说明本发明的技术构思及特点,其目的在于让熟悉此项技术的 人士能够了解本发明的内容并据以实施,并不能以此限制本发明的保护范围。凡根据本发明精 神实质所作的等效变化或修饰,都应涵盖在本发明的保护范围之内。

- 双栅四端III族氮化物增强型HEMT器件的封装结构

- 双栅四端III族氮化物增强型HEMT器件的封装结构