半导体结构及其制造方法

文献发布时间:2023-06-19 10:24:22

技术领域

本发明涉及一种半导体结构及其制造方法,更具体地,涉及一种包括嵌入在导电通孔中的着陆焊盘的半导体结构及其制造方法。

背景技术

通常,硅通孔(through-silicon via;TSV)已用于在系统级封装(System-in-Package)体系结构内形成电连接,通过半导体晶片基板连接多个半导体晶片。制造这些TSV的一种方法称为先钻孔(via-first)方法,其中在形成半导体晶片的金属层之前,先形成TSV穿过基板。制造这些TSV的另一种方法称为后钻孔(via-last)法,其中首先在基板上形成金属层,且形成TSV以使其延伸穿过基板和金属层。金属层中的着陆焊盘(landing pad)必须足够大才能与TSV连接,因此,着陆焊盘会占据较大的空间。此外,当形成TSV以与着陆焊盘连接时,TSV有时无法与着陆焊盘精确对位。

鉴于前述,需要开发一种制造TSV的新方法。

发明内容

本发明的目的在于提供一种可以在着陆焊盘和导电通孔之间提供足够的接触面积的半导体结构。

本发明提供一种半导体结构,其包括基板、介电层、导电通孔及着陆焊盘。介电层位于基板上。导电通孔从基板的下表面贯穿到介电层的上表面。着陆焊盘嵌入导电通孔中。

在一些实施方式中,着陆焊盘具有第一顶表面,第一顶表面与导电通孔的第二顶表面实质上共平面。

在一些实施方式中,着陆焊盘具有顶表面,顶表面与介电层的上表面实质上共平面。

在一些实施方式中,导电通孔具有顶表面,顶表面与介电层的上表面实质上共平面。

在一些实施方式中,着陆焊盘具有第一顶部宽度,第一顶部宽度小于导电通孔的第二顶部宽度。

在一些实施方式中,导电通孔和着陆焊盘具有梯形截面。

在一些实施方式中,导电通孔的材料不同于着陆焊盘的材料。

本发明提供一种制造半导体结构的方法,方法包括以下步骤。接收介电层与基板,其中介电层设置于基板上。在介电层上形成蚀刻停止结构,其中蚀刻停止结构具有蚀刻停止层和突出部,突出部从蚀刻停止层延伸出来且进入介电层中。从基板形成第一孔以暴露突出部的侧壁。在第一孔中形成导电通孔。移除蚀刻停止结构以在导电通孔中形成第二孔。在第二孔中形成着陆焊盘。

在一些实施方式中,方法进一步包括形成第一孔以暴露蚀刻停止层

在一些实施方式中,在第二孔中形成着陆焊盘包括:形成导电层以覆盖介电层和导电通孔;以及移除导电层的一部分以暴露介电层。

应该理解的是,前述的一般性描述和下列具体说明仅仅是示例性和解释性的,并旨在提供所要求的本发明的进一步说明。

附图说明

本发明上述和其他实施例、特征及其他优点参照说明书内容并配合附图可得到更清楚的了解,其中:

图1-图6是示意性地示出根据本发明的一些实施例的在制造半导体结构过程中各中间阶段的截面图。

图7A-图7C是示意性地示出根据本发明的一些实施例的着陆焊盘和导电通孔的俯视图。

主要附图标记说明:

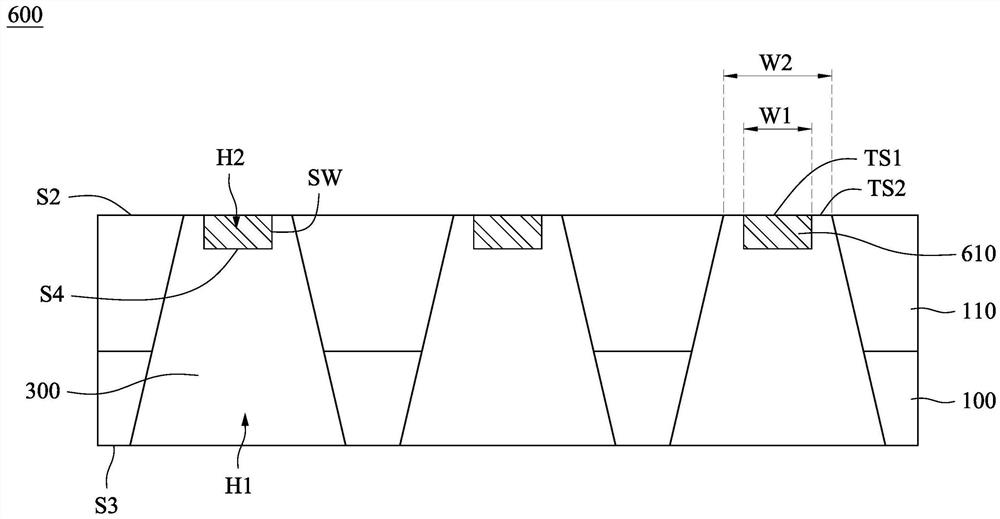

100-基板,110-介电层,120-蚀刻停止结构,122-蚀刻停止层,124-突出部,300-导电通孔,510-导电层,512-第一部分,514-第二部分,600-半导体结构,610-着陆焊盘,H1-第一孔,H2-第二孔,S1-下表面,S2-上表面,S3-下表面,S4-下表面,SW-侧壁,TS1、TS2-顶表面,W1、W2-顶部宽度。

具体实施方式

为了使本发明的叙述更加详尽与完备,可参照所附的附图及以下所述各种实施例,附图中相同的号码代表相同或相似的元件。

以下将以附图公开本发明的多个实施方式,为明确说明起见,许多实务上的细节将在以下叙述中一并说明。然而,应了解到,这些实务上的细节不应用以限制本发明。也就是说,在本发明部分实施方式中,这些实务上的细节是非必要的。此外,为简化附图起见,一些公知惯用的结构与元件在附图中将以简单示意的方式绘示。

本发明提供了一种制造半导体结构的方法。图1-图6是示意性地示出在制造半导体结构过程中各中间阶段的截面图。虽然下文中利用一系列的操作或步骤来说明在此公开的方法,但是这些操作或步骤所示的顺序不应被解释为本发明的限制。例如,某些操作或步骤可以按不同顺序进行及/或与其它步骤同时进行。此外,并非必须执行所有绘示的操作、步骤及/或特征才能实现本发明的实施方式。此外,在此所述的每一个操作或步骤可以包含多个子步骤或动作。

请参考图1。接收基板100和介电层110,其中介电层110设置在基板100上。并且,形成蚀刻停止结构120于介电层110上,其中蚀刻停止结构120具有蚀刻停止层122和突出部124,突出部124从蚀刻停止层122延伸到介电层110中。在一些实施例中,蚀刻停止结构120的材料包括氮化物、氧化物或其组合。例如,氮化物是氮化硅(SiN)。在一些实施例中,介电层110包括二氧化硅(SiO

如图2所示,从基板100形成第一孔H1,以暴露突出部124的侧壁SW和蚀刻停止层122的下表面S1。在一些实施例中,仅突出部124的侧壁SW从第一孔H1暴露出来,而蚀刻停止层122的下表面S1不暴露。在一些实施例中,第一孔H1是通过蚀刻形成。

如图3所示,在第一孔H1中形成导电通孔300。因此,蚀刻停止结构120的突出部124嵌入在导电通孔300中。在一些实施例中,导电通孔300包括铜、金、钨或其合金。

如图4所示,移除蚀刻停止结构120以在导电通孔300中形成第二孔H2。更具体地,因为蚀刻停止结构120的突出部124在先前已嵌入在导电通孔300中,所以在移除蚀刻停止结构120之后,第二孔H2形成在导电通孔300中。

如图5所示,形成导电层510以覆盖介电层110和导电通孔300。导电层510包括第一部分512和第二部分514。第二部分514从第一部分512延伸出来,且填满导电通孔300的第二孔H2。介电层110的上表面S2被导电层510的第一部分512覆盖。在一些实施例中,导电层510包括铜、金、钨或其合金。在一些实施例中,导电通孔300的材料不同于导电层510的材料。

如图6所示,移除导电层510的一部分以暴露介电层110,因此,着陆焊盘610形成在第二孔H2中。在一些实施例中,通过化学机械抛光(chemical-mechanical polishing;CMP)移除导电层510的一部分。

请仍然参考图6。半导体结构600包括基板100、介电层110、导电通孔300及着陆焊盘610。介电层110位于基板100上。导电通孔300从基板100的下表面S3贯穿到介电层110的上表面S2。着陆焊盘610嵌入在导电通孔300中。值得注意的是,着陆焊盘610和导电通孔300之间的接触面积包括着陆焊盘610的下表面S4和侧壁SW的表面。在传统结构中,着陆焊盘仅通过其下表面与导电通孔接触,与传统结构相比,本发明的半导体结构600可以在着陆焊盘610和导电通孔300之间提供足够的接触面积。

在一些实施例中,着陆焊盘610具有顶表面TS1,顶表面TS1与导电通孔300的顶表面TS2实质上共平面,如图6所示。在一些实施例中,着陆焊盘610具有顶表面TS1,顶表面TS1与介电层110的上表面S2实质上共平面,如图6所示。在一些实施例中,导电通孔300具有顶表面TS2,顶表面TS2与介电层110的上表面S2实质上共平面,如图6所示。

在一些实施例中,着陆焊盘610的顶部宽度W1小于导电通孔300的顶部宽度W2,如图6所示。与具有着陆焊盘的下表面大于导电通孔的上表面的传统结构不同,本发明的着陆焊盘610小于传统结构的着陆焊盘。因此,有利于缩小本发明的半导体结构600。

在一些实施例中,导电通孔300和着陆焊盘610具有如图6所示的梯形截面。在一些实施例中,导电通孔300包括介电层和导电柱。导电柱被介电层围绕。导电柱通过介电层与基板100和介电层110分开。在一些实施例中,导电通孔300的材料不同于着陆焊盘610的材料。

图7A-图7C是示意性地示出根据本发明的一些实施例的着陆焊盘和导电通孔的俯视图。如图7A所示,着陆焊盘720a与导电通孔710准确对位。着陆焊盘720a和导电通孔710之间的接触表面包括与导电通孔710接触的着陆焊盘720a的下表面和侧壁表面。如图7B所示,着陆焊盘720b没有与导电通孔710准确对位,着陆焊盘720b和导电通孔710之间的接触表面包括与导电通孔710接触的着陆焊盘720b的下表面和侧壁表面,因此,此接触表面足够大,以完成着陆焊盘720b和导电通孔710间的电连接。着陆焊盘720c和导电通孔710之间的接触表面包括与导电通孔710接触的着陆焊盘720c的下表面和侧壁表面,因此,此接触表面足够大,以完成着陆焊盘720c和导电通孔710间的电连接。

尽管已经参考某些实施方式相当详细地描述了本发明,但是亦可能有其他实施方式。因此,前述权利要求的精神和范围不应限于此处包含的实施方式的描述。

对于所属技术领域的技术人员来说,显而易见的是,在不脱离本发明的范围或精神的情况下,可以对本发明的结构进行各种修改和变化。鉴于前述内容,本发明意图涵盖落入前述权利要求范围内的本发明的修改和变化。

- 氮化物半导体结构、氮化物半导体发光元件、氮化物半导体晶体管元件、氮化物半导体结构的制造方法以及氮化物半导体元件的制造方法

- 用于制造腔结构、制造用于半导体结构的腔结构的方法和使用该方法制造的半导体传声器