一种基于差异测试的FPGA综合工具缺陷检测方法

文献发布时间:2023-06-19 11:22:42

技术领域

本发明涉及一种FPGA综合工具的缺陷检测方法,具体涉及一种基于差异测试的FPGA综合工具缺陷检测方法,属于计算机软件测试技术领域。

背景技术

近年来,软件的正常运行越来越依赖于硬件。几乎所有的数字计算都以这样或那样的方式依赖于逻辑综合工具,越来越多的领域使用FPGA(Field Programmable GateArray)来加速服务器上的应用程序。此外,硬件的日益复杂也导致对自动化有很大的需求,这意味着综合工具的正确性对硬件的可靠性至关重要。因此,对FPGA综合工具进行严格测试,十分必要。

为了测试FPGA综合工具的正确性,有人提出通过构造生成随机、有效、确定的或者不确定的Verilog设计并传递给综合工具,综合工具会产生一个可以与原始设计进行比较的等效的nestlist网表,然后基于Verilog设计的输出与合成的网表在时钟边缘应该总是相等的原则,对综合工具是否存在缺陷进行判断。

尽管现有的方法能够很好地为FPGA综合工具缺陷进行检测,但是,随机构造行为良好的Verilog不太可能穷尽测试许多不同的Verilog构造组合。同时,如果使用不确定的Verilog设计,需要考虑测试的代价,因为生成不确定的Verilog需要执行额外的模拟步骤来避免误报。这些将导致FPGA综合工具bug检测效率欠佳。

发明内容

本发明的目的是针对现有的FPGA综合工具缺陷检测方法效果不佳的技术问题,提出一种基于差异测试的FPGA综合工具缺陷检测方法。

本发明方法的创新点在于:通过使用两个或者更多的可供比较的参考FPGA综合工具,给定一个测试代码,将测试代码生成与其等价的变异代码,这些参考的FPGA综合工具和待测工具将对其执行编译得到各自的执行结果。由于参考综合工具和待测的FPGA综合工具在差异测试中遵循相同规约,其执行结果相同。因此,通过比较待测工具与参考工具的执行结果的一致,能够有效判断待测工具是否存在缺陷。

本发明采用以下技术方案实现。

一种基于差异测试的FPGA综合工具缺陷检测方法,包括以下步骤:

步骤1:构建FPGA综合工具测试用例种子库。

具体地,可以从测试人员输入的综合设计实例中,获取所需测试用例。例如,可以从现有的高级综合工具官网、开源社区的有效链接中,爬取、解析获得高级语言文件。

步骤2:基于遗传算法,对测试种子用例按照测试效果的优先从高到低进行排序,并依次执行。可降低测试的时间,提高测试效率。

具体地,对测试用例优先排序问题的一般性描述为:测试用例集T,测试用例的全排列集PT,排序目标函数f(x):PT→R。寻找T'∈PT,使得对任意T″∈PT(T″≠T'),有f(T')≥f(T″)。其中,T'、T″表示在测试用例的全排列集中任意选取的测试用例序列,T″≠T'。

在FPGA和软件系统的在测试中,在检测HDL时,不仅要根据信号流图对逻辑进行检测,还要依据时序图,对时变信号的一致性进行检测。针对以上的测试需求设计测试点,在测试用例集中,每一个测试用例可能对应一个或者多个测试点。

首先,定义基于测试点覆盖的评价指标APTC(Average Percentage of Test-point Coverage),即测试用例使用个数和检测错误个数之间的关系进行量化。设测试用例集T有n个测试用例,能够检测出m个缺陷。对一个给定的测试用例执行次序,TF

其中,APTC∈(0,100%),其取值越高,则缺陷检测速度越快。

如表1所示的实例,该实例中有5个测试用例和10个测试点。对于测试用例序列A-B-C-D-E和E-D-C-B-A,其中APTC的取值分别为50%、64%,所以执行次序2的效果优先。

表1测试用例与测试点的对应关系的一个实例

然后,基于遗传算法适应度函数(其值介于0-1之间),即评价指标APTC指导遗传算法进行搜索。

步骤3:选取测试用例P。

其中,选取测试用例遵循以下条件:

如果执行的是初始测试,则从步骤2中的种子库中随机选取测试用例。否则,根据测试用例APTC的取值从大到小进行选择。

步骤4:变异测试用例,得到新的测试用例P'。

其中,生成和测试用例等价的变异代码,可以使用原始的AST来分析测试用例并将其进行等价变异。分析测试用例的AST的语句,如果某一条语句未执行且其孩子也未被执行,则标记该语句为未执行语句,并对其语句进行删除或者插入操作,当进行删除该语句时,将移除它在AST子树的所有相关的词句,包括其孩子语句,当进行插入代码段时,可无限制插入语句到这些标记的未执行语句。

步骤5:使用待测的FPGA综合工具,并选取至少2个现有的参考工具,对步骤4中生成的变异测试代码P'进行转换,得到测试代码HDL的综合网表netlist。

其中,选取的参考工具与待测的FPGA综合工具有相同的规约,即,待测工具和参考工具是能够进行比较的FPGA综合工具,它们的实现秉相同的规约原则。

步骤6:判断是否有工具出现崩溃现象。如果出现测试奔溃情况,则直接进行bug报告生成并存储。如果参考工具和待测工具都对测试用例转换成功,则执行步骤7。

具体地,在FPGA综合工具中,对于一个设计的测试用例会产生一个与其进行比较的等效的netlist网表,即综合工具Verilog设计的输出与转换生成的网表在时钟边缘总是相等,当两者不相等时判定其执行崩溃。

步骤7:对比现有的参考工具和待测的FPGA综合工具的转换结果。

具体地,当测试用例被综合工具综合后形成网表文件.edf,综合工具调用自带的仿真工具进行功能仿真得出结果。

或者,综合工具也可以借助综合后的3个*.v文件,一个是testbench文件,一个是工具生成的xxx_synthesis.v,另一个是glbl.v文件来创建新的工程对其进行仿真。

步骤8:比较上一步的仿真结果是否相同,若相同,表示选取的测试用例不适合,返回步骤3,若结果不一致,则生成并存储bug报告结果。

有益效果

本发明方法,对比现有技术,通过变异产生有效的FPGA综合工具测试的测试种子用例,能够有效检测综合工具中存在的缺陷,并将其缺陷报告进行保存,可供开发人员快速的修复Bug。

附图说明

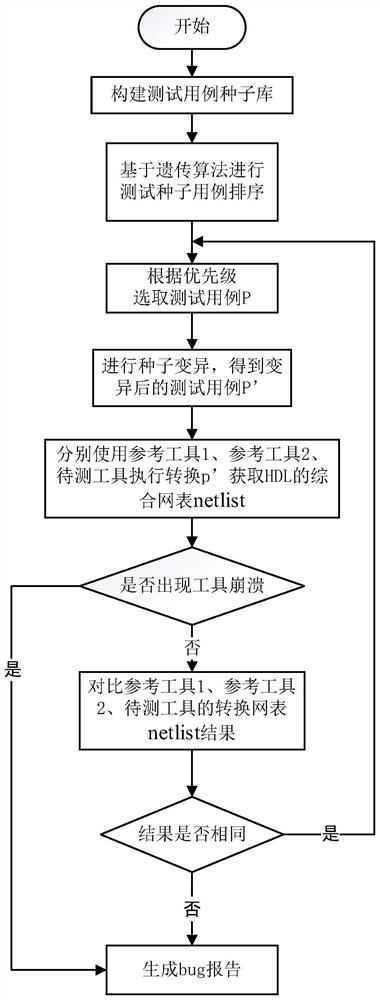

图1是本发明方法的流程示意图。

具体实施方式

下面结合附图和实施例对本发明方法做进一步详细说明。

实施例

本方法部署在在如表2所示的硬件环境下,根据实验需求安装对应的待测软件,本实验中选取的2个现有的参考工具1-Yosys 0.9、参考工具2-Vivado 18.2,对FPGA综合工具Quartus Prime 19.2进行检测,其中Yosys 0.9开源。本实施例由测试用例种子池构架、测试代码变异、测试种子用例排序等程序构成。

表2:硬件环境配置信息表

步骤1:搜集已有的FPGA综合工具的设计实例构建测试用例种子库,对种子池中的测试用例进行初始化,对每个测试用例设置初始优先级参数值c

具体为:使用爬虫技术,从一些高级综合工具的官网和开源社区的有效链接中爬取解析出高级语言文件。

步骤2:基于遗传算法对测试种子用例进行优先级排序。将测试用例按测试效果的优先从高到低进行排序并依次执行,进而可降低测试的时间,提高测试效率。

具体为:

测试用例优先排序问题的一般性描述如下:

测试用例集T,测试用例的全排列集PT,排序目标函数f(x):PT→R。寻找T'∈PT,使得对任意的T″∈PT(T″≠T')有f(T')≥f(T″)。其中,T'和T″表示在测试用例的全排列集中任意选取的测试用例序列,T″≠T'。

在FPGA和软件系统的在测试中,在检测HDL时,不仅要根据信号流图对逻辑进行检测,还要依据时序图,对时变信号的一致性进行检测。针对以上的测试需求设计测试点,在测试用例集中,每一个测试用例可能对应一个或者多个测试点。

定义基于测试点覆盖的评价指标APTC,即测试用例使用个数和检测错误个数之间的关系来量化。设测试用例集T,有n个测试用例,能够检测出m个缺陷,对一个给定的测试用例执行次序,TF

其中,APTC∈(0,100%),取值越高,则缺陷检测速度越快。

然后,基于遗传算法适应度函数,其值介于0~1之间,即评价指标APTC指导遗传算法进行搜索。

步骤3:选取测试用例P。

其中,选取测试用例遵循以下规则:

如果执行初始测试,从步骤2中的种子库中随机选取测试用例,否则,根据测试用例APTC的取值进行选择,选取高优先级的测试用例。

步骤4:变异测试用例,得到新的测试用例P'。

其中,生成和测试用例等价的变异代码,可以使用原始的AST来分析测试用例并将其进行等价变异,分析测试用例的AST的语句,如果某一条语句未执行,且其孩子也未被执行,那么就标记该语句为未执行语句,并对其语句进行删除或者插入操作。当进行删除该语句时,将会移除它在AST子树的所有相关的词句,包括其孩子语句;当进行插入代码段时,可以无限制的一直插入语句到这些标记的未执行语句。具体过程如图1所示。

步骤5:使用待测的FPGA综合工具和参考工具1、参考工具2,对步骤4中生成的变异测试代码P'进行转换,得到测试代码HDL的综合网表netlist,参考工具1和参考工具2的实现是和待测的FPGA综合工具有相同的规约,即待测对象工具和参考对象工具是可以进行比较的FPGA综合工具,它们的实现秉着相同的规约原则。

步骤6:判断是否有工具出现崩溃现象;如果出现测试奔溃情况,直接进行bug报告生成并存储,如果参考工具和待测工具都对测试用例转换成功,则执行下一步骤。

具体为:

在FPGA综合工具中,对于一个设计的测试用例,会产生一个与其进行比较的等效的netlist网表,即综合工具Verilog设计的输出与转换生成的网表在时钟边缘应该总是相等的,当两者不相等时,判定其执行崩溃。

步骤7:对比参考工具1、参考工具2和待测的FPGA综合工具的转换结果。

具体为:

借助综合后的3个*.v文件。一个是testbench文件,一个是工具生成的xxx_synthesis.v,另一个是glbl.v文件,使用ModelSim对期进行仿真。

步骤8:比较上一步的仿真结果是否相同,若相同,表示选取的测试用例不适合,返回步骤3,若结果不一致,则生成并存储bug报告结果。

其结果如下所示;

相同资源下工具的运行时间:

Yosys 0.9:200 CPU hours

Vivado 18.2:180 CPU hours

Quartus Prime 19.2:180 CPU hours

探测到bug的数量:

Quartus Prime 19.2:2

结果表明:使用本发明方法,可以有效检出测综合工具存在的bug。

- 一种基于差异测试的FPGA综合工具缺陷检测方法

- 一种基于等价取模测试的高级综合工具缺陷检测方法