用于产生模拟信号的装置

文献发布时间:2023-06-19 11:55:48

技术领域

本发明涉及以高输出频率,特别是大于采样频率的输出频率从数字代码中产生模拟信号,同时保持接近第一奈奎斯特区的性能并限制信号处理链中的组件数量。

背景技术

一般而言,实际的数模转换器具有阶梯输出或提供有限宽度的脉冲。转换器的频谱响应以正弦基函数反映。因此,转换器的功率响应允许在第一和第二奈奎斯特区中产生具有宽动态范围的信号,换句话说,在0至fs/2之间以及在fs/2至fs之间,其中fs是数字信号的采样频率。一旦人们希望合成超过采样频率fs(例如2fs或更高)的信号,该信号就会严重衰减。

为了对此进行补救,可以使用放置在转换器的输出处的乘法器,该乘法器将借助于具有频率fm的卷积来转换所生成的信号的频率。然后,来自转换器的模拟系统将围绕频率fm转换,这将允许来自转换器的信号的频率升高(iffm>fs/2),其动态范围与第一奈奎斯特区中的转换器的动态范围相同。然而,该解决方案需要附加的有源元件,特别是射频源,以便产生信号频率fm。这增加了转换器的噪声、失真和功耗。此外,在转换器和乘法器之间使用两个独立的模拟源意味着可重构性很差。

为了避免这种情况,可以选择fm,使得fm=fs;这允许用于采样数字数据的信号用于增加转换器输出处的频率(US 7796971)。因此,转换器输出的模拟信号将围绕采样频率fs转换,其动态范围始终等于第一奈奎斯特区的动态范围。但是,我们不能总是产生频率大于2fs的信号,因为该信号将始终被转换器的正弦基响应强烈衰减,从而降低了系统性能。而且,该解决方案仅适用于电流转换器。

同样可以增加采样频率fs。这允许增加第一和第二奈奎斯特区中的动态范围,但是要获得具有宽奈奎斯特区和强动态范围的转换器很复杂,因为为了实现高采样频率fs,数模转换器内核必须交织在一起,这样会产生额外的寄生信号,从而降低性能。

还有一个可能性是对来自转换器的模拟输出信号执行多次归零(US 8659458)。如果执行N次归零,其中N是整数,则信号将围绕N×fs产生,且衰减很小。这要求在量化时钟上使用频率为fs的快速时钟信号设置,并施加归零,归零随着N的增加而越来越短。这仅适用于电流转换器。

发明内容

本发明的目的是克服现有技术的上述缺点和局限性。更具体地,本发明的目的是提出一种能够优化数模转换器输出功率以及该转换器输入处的数字位率的用于产生模拟信号的装置。

因此,本发明的目的是一种用于产生模拟信号的装置,所述装置包括:数模转换器,其包括至少一个数字输入和一个模拟输出;用于产生频率为fs的第一时钟信号的电路;以及数字寄存器,其被配置为使得在输入处接收并存储代表来自所述数模转换器的模拟输出信号的N个位,N是大于或等于1的整数,以及接收所述第一时钟信号,所述寄存器针对每个位包括两个互补的数字输出,所述装置的特征在于它还包括:用于产生频率为m×fs的第二时钟信号的电路,其中m是大于1的整数;以及N个多路复用器电路,所述N个多路复用器电路放置在所述数字寄存器的所述输出和所述数模转换器的所述输入之间,并且被配置为使得它们分别在控制输入处接收所述第二时钟信号,并且使得它们分别在数据输入处接收来自与所述寄存器的同一输入位对应的所述寄存器的两个数字输出的信号,这样使得离开所述多路复用器电路的信号的频率为2×m×fs。

根据本发明的特定实施例:

-将用于产生所述第一时钟信号的所述电路和用于产生所述第二时钟信号的所述电路进行组合;

-所述用于产生所述第一时钟信号和所述第二时钟信号的电路包括时钟,其被配置为产生频率为m×fs的时钟信号;以及分频器电路,其被配置为使得所述分频器电路的输出处的信号是频率为fs的时钟信号;

-所述转换器是数模电流转换器或数模电压转换器。

-所述多路复用器电路包括至少一个双极型多路复用器。

本发明的另一目的是用于产生模拟信号的方法,所述包括以下步骤:

a)在数字寄存器的输入处提供代表模拟信号的N个位,N是大于或等于1的整数,并且向该数字寄存器施加频率为fs的第一时钟信号,所述寄存器针对每个输入位包括两个互补的数字输出;

b)将频率为2×m×fs的第二时钟信号施加到N个多路复用器电路,m是大于或等于1的整数,并在所述N个多路复用器电路的输入处提供来自所述寄存器的两个互补数字输出的信号,所述多路复用器电路n接收源自所述同一输入位n的两个输出,n是1至N之间的整数;

c)在数模转换器的所述输入处提供来自所述N个多路复用器电路的输出信号;

d)恢复所述转换器的所述输出处的信号,所述信号源自电流或电压值,其频谱响应以频率m×fs为中心。

附图说明

通过阅读参考附图给出的描述,本发明的其他特征、细节和优点将变得明显,这些附图以示例的方式提供并分别为:

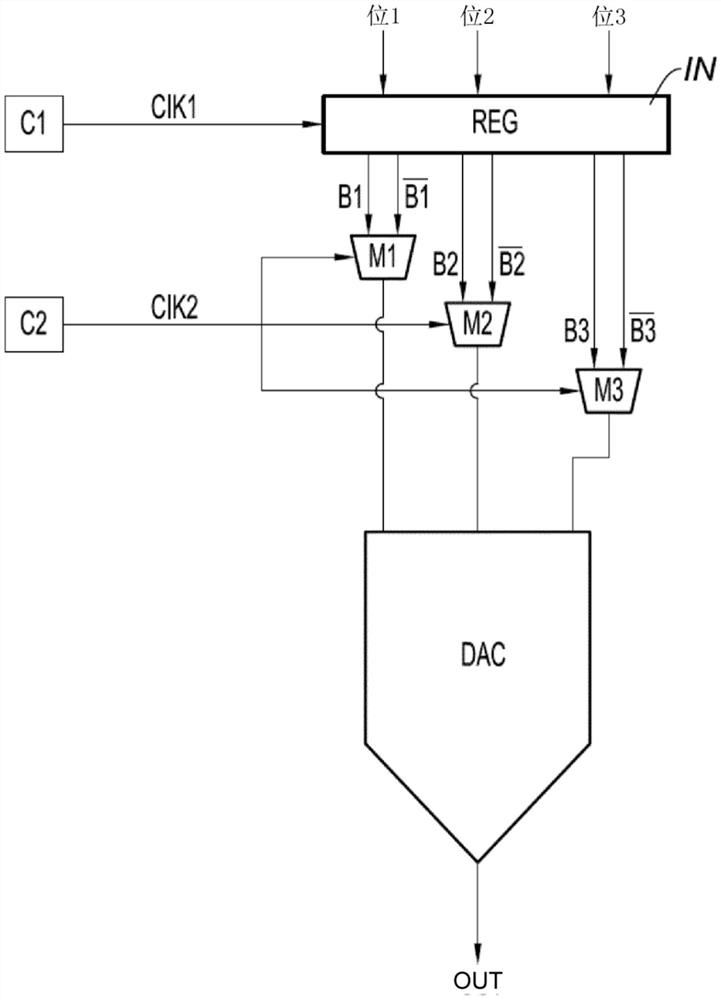

图1是根据本发明的第一实施例的装置;

图2是根据本发明的第二实施例的装置。

图3是根据本发明的第三实施例的装置;以及

图4是根据本发明的用于产生模拟信号的方法。

具体实施方式

图1示出了根据本发明的第一实施例的用于产生模拟信号的装置。该装置包括数字寄存器REG,数字寄存器REG在输入IN处接收要转换的数字数据。该数字数据例如是包括三个位B1、B2和B3的二进制字。寄存器REG针对每个位包括两个互补的输出,分别为用于提供该位的第一输出和用于提供其补码的第二输出。在图1所示的实施例中,仅示出了针对三个位(B1、B2、B3)的三个输入,以及六个输出(B1、

用于产生时钟信号的第一电路C1将频率为fs的时钟信号Clk1发送到寄存器REG,以使这些位及其补码(B1、

存在用于产生时钟信号Clk2的第二电路C2。该电路将频率为m×fs的时钟信号Clk2发送到多路复用器电路M1、M2和M3的控制输入,其中m是大于1的整数。多路复用器电路M1、M2和M3放置在寄存器REG的输出处。每个多路复用器电路(M1、M2、M3)在输入处接收来自寄存器REG的两个输出信号,更具体地说,接收一个位及其补码,因此这两个输出信号对应于寄存器REG中的同一输入位。因此,多路复用器电路M1接收(B1、

然后,将多路复用器电路(M1、M2、M3)的输出发送到数模转换器DAC,数模转换器DAC包括三个数字输入IN_DAC和一个数字输出OUT。图中仅示出了三个输入IN_DAC,因为在寄存器REG的输入处有3个位:位1、位2和位3,但是更一般地说,输入的数量与寄存器REG的输入处的位数一样多。

这些位在转换器DAC中被转换为模拟数据,并且在转换器的输出OUT处获得的模拟信号的频谱响应以最大宽度为fs/2的频率m×fs为中心。这样可以通过快速时钟信号以高频率(m×fs)保持足够的功率水平。

图2示出了根据本发明的第二实施例的用于产生模拟信号的装置。在该实施例中,跟图1一样,数字寄存器REG的输入IN处仅示出了三个位:位1、位2和位3,但是在寄存器REG的输入处可以有N个位,其中N是大于或等于1的整数。与第一实施例不同,用于产生两个时钟信号的电路被组合在一起。只有一个电路C产生频率为m×fs的时钟信号Clkat,其中m是大于或等于1的整数。时钟信号Clk被直接发送到多路复用器电路M1、M2和M3,从而跟图1一样,可以在多路复用器电路M1、M2和M3的输出处以频率2×m×fs获得这些位及其补码。然而,在被发送到寄存器REG之前,时钟信号Clkfirst通过分频器电路D,该分频器电路将时钟信号的频率除以m,从而允许在寄存器的输入处具有频率为fs的时钟信号Clk1。

图3示出了本发明的第三实施例。描述了根据本发明的示例性装置和数模转换器结构。寄存器REG在输入处接收两个位:位1和位2,它们以时钟信号Clk1的频率fs作为(B1、

奇数分支的输出电流在加法器电路中相加,该加法器电路在该实施例中是电阻器R1。偶数分支的输出电流同样在加法器电路中相加,在该实施例中,该加法器电路同样是电阻器R2。电阻器端子R1和R2处的电压之间的电压差表示要转换的二进制字的数字值,该数字值通过位1和位2在装置的输入IN处提供。该电压差在转换器DAC的输出OUT处提供。取决于转换器的类型,换句话说,取决于是电流转换器还是电压转换器,输出OUT将是电流值或电压值。

根据本发明的另一实施例,多路复用器电路(M1、M2、M3)包括至少一个双极型多路复用器。

根据另一实施例,DAC转换器包括双极型晶体管。根据另一实施例,DAC转换器包括MOSFET晶体管,换句话说,包括绝缘栅场效应晶体管。

根据另一实施例,DAC转换器是电压转换器。根据多个实施例,DAC转换器更具体地是:

-具有开关功能的数模转换器,其开关根据转换器输入处的位值进行控制;

-带有电阻器网络R/2R的数模转换器;或者

-带有加权电阻器的数模转换器。

这三个转换器通常以比数模电流转换器低的频率工作。

图4示出了根据本发明的用于产生模拟信号的方法。第一步(步骤a)涉及在数字寄存器的输入处提供代表模拟信号的N个位,N是大于或等于1的整数,以及向该数字寄存器施加频率为fs的第一时钟信号,该寄存器针对每个输入位包括两个互补数字输出。接下来的步骤b涉及将频率为2×m×fs的第二时钟信号施加到N个多路复用器电路,m是大于或等于1的整数,并在N个多路复用器电路的输入处提供来自寄存器的两个互补数字输出的信号,多路复用器电路n接收源自同一输入位n的两个输出,n是1至N之间的整数。然后在步骤c中,在数模转换器的输入处提供N个多路复用器电路的输出信号,最后,在最后一步(步骤d)中,恢复来自转换器的对应于电压或电流值的输出信号,该信号的频谱响应以频率m×fs为中心。

这种产生模拟信号的方法可以在根据本发明的装置上实现,例如先前描述的装置。

- 用于产生由PWM信号产生的模拟信号的方法以及产生这种信号的系统

- 用于产生模拟信号的装置