一种扩频信号同步装置

文献发布时间:2023-06-19 12:07:15

技术领域

本发明涉及扩频通信技术领域,特别是指一种扩频信号同步装置,可用于BPSK调制下的扩频通信系统。

背景技术

扩频通信技术是当今信息社会最为先进的无线电通信技术之一,具有很强的抗干扰能力、很低的截获概率、很好的通信保密性和良好的码分多址通信能力,无论在军用还是民用通信系统中,该技术都有着广阔的应用前景。在扩频通信系统的设计实现中,同步技术是扩频通信系统中的重点和难点。尤其是,对于帧结构分段采用不同扩频码,调制方式为2BPSK,I、Q两路信号扩频码不同并且存在固定延时的一类特殊结构的扩频系统,其同步处理更是一大难点。目前,现有技术中尚没有针对这种扩频系统的信号同步方案。

发明内容

为解决上述背景技术部分所提到的问题,本发明提出一种扩频信号同步装置,其可实现帧结构分段采用不同扩频码,调制方式为2BPSK,I、Q两路信号扩频码不同并且存在固定延时的扩频系统的扩频信号同步。

本发明的目的是这样实现的:

一种扩频信号同步装置,包括I路信号捕获单元、Q路信号捕获单元、延时单元、解扩单元、码发生器、码时钟单元、流程控制单元以及跟踪及同步控制单元;

I/Q路信号捕获单元包括I/Q路PN序列生成器、I/Q路PN序列存储器、I/Q路信号移位寄存器、I/Q路信号功率计算器和I/Q路信号功率比较器;其中,I/Q路PN序列生成器用于生成I/Q路捕获的本地码序列,I/Q路PN序列存储器用于对本地码序列进行装载,I/Q路信号移位寄存器用于完成对I/Q路数据的移位存储与读取,I/Q路信号功率计算器用于完成对I/Q路信号的功率统计,I/Q路信号功率比较器用于完成I/Q路信号功率值与门限值的比较运算,并输出使能信号给码发生器和流程控制单元;

码时钟单元用于产生本地码字的时钟并传给码发生器,码发生器用于生成I路信号和Q路信号的解扰码字并传给解扩单元;

解扩单元包括I路信号解扰单元、Q路信号解扰单元、I路信号累加单元以及Q路信号累加单元;其中,I/Q路信号解扰单元采用码发生器生成的解扰码字完成对I/Q路输入信号的解扰,I/Q路信号累加单元用于完成对I/Q路解扩后的信号的积分累加,并将每个符号的累加完成使能信号输出给同步控制单元;

跟踪及同步控制单元用于完成码片的跟踪以及码发生器的启动,并对码时钟单元进行偏差调整;还用于输出同步使能信号给流程控制单元;

流程控制单元用于控制捕获码的启动;当I/Q路信号功率比较器的使能信号和跟踪及同步控制单元的使能信号不同时为高电平时,流程控制单元输出捕获码启动的使能信号;

外部输入的信号分为两路,其中,一路信号同时经过I路捕获单元和Q路捕获单元完成信号的捕获,捕获过程中,通过加载本地码字并与输入信号做相关运算,得到信号帧头的起始位置以及有效数据的位置标志;另一路信号经过延时单元,延时后的信号进入解扩单元,解扩单元通过码发生器产生的解扰码字与I/Q路信号进行解扰、累加,得到超前、当前、滞后三种信号,其中,超前和滞后信号反馈给跟踪及同步控制单元进行码跟踪处理,当前信号为原始信号,直接输出,实现扩频信号的同步。

本发明具有如下有益效果:

(1)本发明针对传输帧结构在不同的位置采取不同扩频码的一类信号完成了信号的捕获。

(2)本发明针对传输帧I、Q两路信号采取不同的扩频码且存在延时的一类信号,完成了信号的同步。

(3)本发明采用了高倍钟存取码字的策略,减小了信号的处理延时。

附图说明

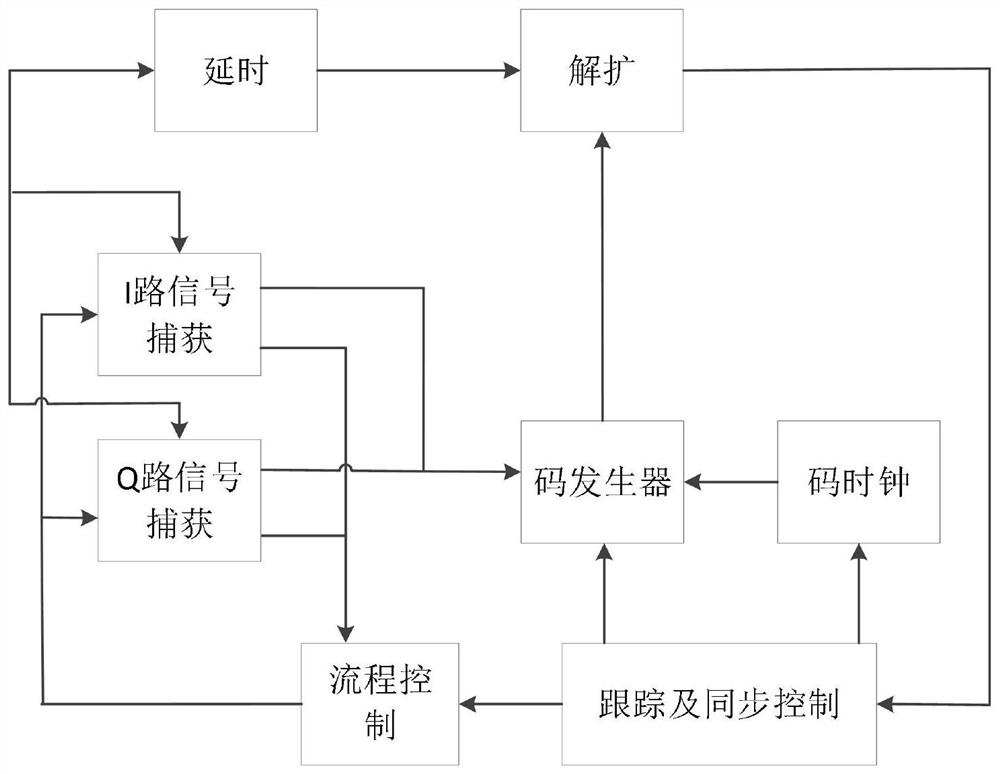

图1是本发明实施例中扩频信号同步的电原理图。

图2是图1中I路信号捕获单元的电原理图。

图3是图1中Q路信号捕获单元的电原理图。

图4是图1中解扩单元的电原理图。

具体实施方式

下面结合附图和具体实施方式对本发明的技术方案做进一步的详细描述。

如图1所示,一种扩频信号同步装置,其包括I路信号捕获单元、Q路信号捕获单元、延时单元、解扩单元、码发生器单元、码时钟单元、流程控制单元以及跟踪及同步控制单元。其中,I路信号捕获单元采用I路信号同步头的码字完成信号同步头的捕获,Q路信号捕获单元采用Q路信号同步头的码字完成信号同步头的捕获,延时单元用于完成对信号的延时处理,解扩单元用于完成I路信号和Q路信号的解扩处理,码发生器单元用来生成I路信号和Q路信号的解扰码字,码时钟单元用于产生本地码字的时钟,流程控制单元用来控制捕获码的启动,跟踪及同步控制单元用于完成码片的跟踪以及码发生器的启动。

如图2所示,I路信号捕获单元由I路PN序列生成单元、I路PN序列存储单元、I路信号移位寄存单元、I路信号功率计算单元和I路信号功率比较单元组成。其中,I路PN序列生成单元用于生成I路捕获的本地码序列,I路PN序列存储单元采用高倍钟将PN序列生成单元的PN码字存储在RAM中,I路信号移位寄存单元采用移位寄存器的形式,完成I路输入信号的移位读取以便与本地PN序列完成相关运算,I路信号功率计算单元用于将相关后的数据进行积分累加运算,完成功率统计,I路信号功率比较单元用于将计算的功率值与预设的功率门限值做比较运算。

如图3所示,Q路信号捕获单元由Q路PN序列生成单元、Q路PN序列存储单元、Q路信号移位寄存单元、Q路信号功率计算单元和Q路信号功率比较单元组成。其中,Q路PN序列生成单元用于生成Q路捕获的本地码序列,Q路PN序列存储单元采用高倍钟将PN序列生成单元的PN码字存储在RAM中,Q路信号移位寄存单元采用移位寄存器的形式,完成Q路输入信号的移位读取以便与本地PN序列完成相关运算,Q路信号功率计算单元将相关后的数据进行积分累加运算,完成功率统计,Q路信号功率比较单元将计算的功率值与预设的功率门限值做比较运算。

如图4所示,解扩单元由I路信号解扰单元、Q路信号解扰单元、I路超前支路信号累加单元、I路滞后支路信号累加单元、I路当前支路累加单元、Q路超前支路信号累加单元、Q路滞后支路信号累加单元、Q路当前信号累加单元组成。其中,I路信号解扰单元采用码发生器生成的扰码完成对I路输入信号的解扰,Q路信号解扰单元采用码发生器生成的扰码完成对Q路输入信号的解扰,I路超前、滞后、当前信号累加单元分别用于完成对I路信号解扰后产生的超前、滞后和当前支路信号的累加,Q路超前、滞后、当前信号累加单元分别用于完成对Q路信号解扰后产生的超前、滞后和当前支路信号的累加。

本装置的简要工作步骤如下:

(1)输入的信号分两路,其中一路信号同时经过I路捕获单元和Q路捕获单元完成信号的捕获,在捕获电路中,主要通过加载本地同步码与输入信号做相关运算,同时得到信号帧头的起始位置以及有效数据的位置标志;

(2)输入信号分的另一路信号经过信号延时单元,使得延时值与捕获延时相同,延时后的数据经过解扩单元,在码发生器和流程控制单元的作用下完成信号的解扩处理;

(3)经过解扩单元产生的超前支路和滞后支路完成码跟踪处理,由流程控制单元控制各个功能模块的正常启动结束,完成整个扩频信号的同步过程。

总之,本发明针对帧结构分段采用不同扩频码,调制方式为2BPSK,I、Q两路信号扩频码不同并且存在固定延时的扩频系统,可以实现普通调制解调器所不具备的信号同步功能,是对现有技术的一种重要改进。

- 一种扩频信号同步装置

- 扩频弱信号同步的方法及装置