一种基于折叠线圈的紧凑功分器芯片

文献发布时间:2023-06-19 12:07:15

技术领域

本发明涉及微波射频集成电路领域,具体而言,涉及一种基于折叠线圈的紧凑功分器芯片。

背景技术

工作带宽是功分器的一个重要指标,其定义为关注指标全部满足使用条件的工作频率范围。通常以相对带宽系数B衡量功分器的带宽,其定义为:

其中,f

芯片面积则直接关系到芯片成本及上层系统的集成度,是芯片的重要关注对象。

现有一分二功分器产品中对于k<1.5的功分器,为了减小版图面积,通常采用集总参数设计,其芯片面积通常大于1mm

发明内容

本发明旨在提供一种基于折叠线圈的紧凑功分器芯片,以解决芯片面积过大的问题。

本发明提供的一种基于折叠线圈的紧凑功分器芯片,包括:

折叠线圈,所述折叠线圈包括相连接的第一级耦合线圈和第二级耦合线圈;所述第一级耦合线圈由两个上下完全对称的电感相互缠绕形成,并且所述第一级耦合线圈的线圈抽头与功分器芯片的合路端口连接,信号由合路端口到达第一级耦合线圈的线圈抽头后分为两路分别按顺时针和逆时针传输;所述第二级耦合线圈也由两个上下完全对称的电感相互缠绕形成,信号由第一级耦合线圈到达第二级耦合线圈后分也分别按顺时针和逆时针传输至功分器芯片的两路功分端口;并且,所述第二级耦合线圈翻折进第一级耦合线圈内部;

RC串联网络,所述RC串联网络设置在第一级耦合线圈内部,包括第一级RC串联网络和第二级RC串联网络,所述第一级RC串联网络连接第一级耦合线圈的功分两路;所述第二级RC串联网络连接第二级耦合线圈的功分两路;

两个谐振电容,所述两个谐振电容连接在第一级耦合线圈和第二级耦合线圈的连接处并接入到地。

进一步的,所述第一级耦合线圈的内径大于第二级耦合线圈的外径。

进一步的,所述第一级耦合线圈的内圈金属边沿到第二级耦合线圈的外圈金属边沿的距离大于3倍线圈宽度。

进一步的,所述第一级耦合线圈与第二级耦合线圈的中心重合。

进一步的,所述第一级RC串联网络和第二级RC串联网络设置在内,并设置在第二级耦合线圈的左右两侧。

进一步的,所述第一级RC串联网络设置在第二级耦合线圈靠近合路端口侧;所述第二级RC串联网络设置在第二级耦合线圈靠近功分端口侧。

进一步的,所述第一级耦合线圈设计为2N圈;所述第二级耦合线圈设计为2M+1圈;其中M和N均为正整数。

进一步的,所述基于折叠线圈的紧凑功分器芯片,还包括衬底;所述折叠线圈、RC串联网络和两个谐振电容均设置在衬底上。

进一步的,所述衬底采用GaAs。

综上所述,由于采用了上述技术方案,本发明的有益效果是:

本发明能够极大的减小功分器芯片的尺寸,并且表现出优异的性能。

附图说明

为了更清楚地说明本发明实施例的技术方案,下面将对实施例中的附图作简单地介绍,应当理解,以下附图仅示出了本发明的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

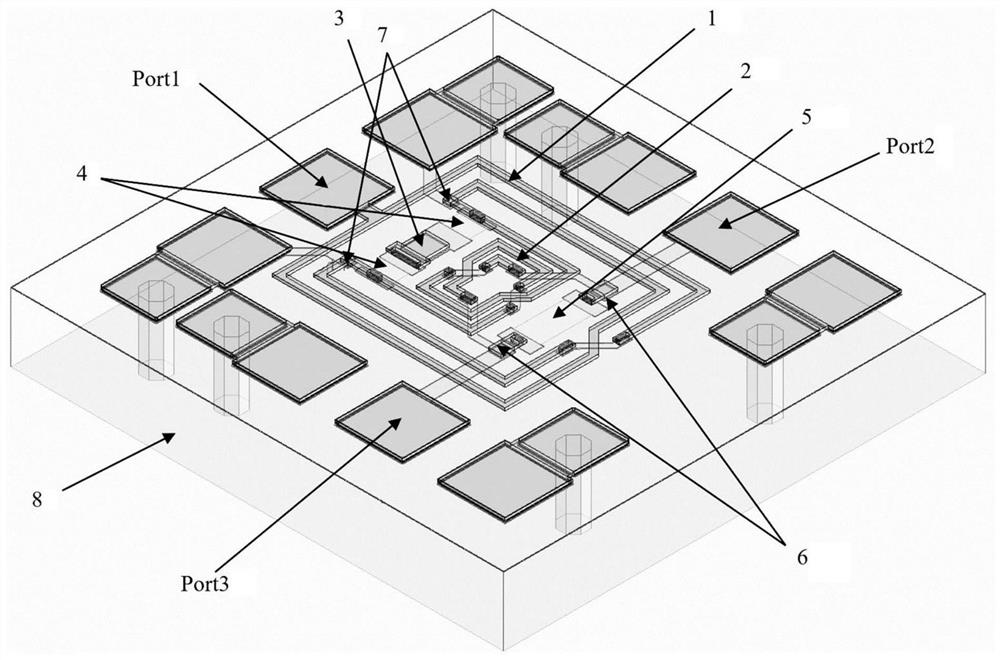

图1为本发明实施例中功分器芯片的立体结构图。

图2为本发明实施例中功分器芯片的折叠线圈折叠过程示意图。

图3为本发明实施例中功分器芯片的版图。

图4为本发明实施例中功分器芯片的S21、S31幅度仿真图。

图5为本发明实施例中功分器芯片的S21、S31相位仿真图。

图6为本发明实施例中功分器芯片的S11、S22、S33仿真图。

图7为本发明实施例中功分器芯片的S32仿真图。

图标:1-第一级耦合线圈,2-第二级耦合线圈,3-第一级RC串联网络中的电容,4-第一级RC串联网络中的电阻,5-第二级RC串联网络中的电阻,6-第二级RC串联网络中的电容,7-两级线圈公共端接入到地的谐振电容,8-100um厚GaAs衬底,Port1为合路端口,Port2及Port3为功分端口。

具体实施方式

为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本发明实施例的组件可以以各种不同的配置来布置和设计。

因此,以下对在附图中提供的本发明的实施例的详细描述并非旨在限制要求保护的本发明的范围,而是仅仅表示本发明的选定实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

实施例

如图1所示,本实施例提出一种基于折叠线圈的紧凑功分器芯片,包括:

折叠线圈,所述折叠线圈包括相连接的第一级耦合线圈和第二级耦合线圈;所述第一级耦合线圈由两个上下完全对称的电感相互缠绕形成,并且所述第一级耦合线圈的线圈抽头与功分器芯片的合路端口连接,信号由合路端口到达第一级耦合线圈的线圈抽头后分为两路分别按顺时针和逆时针传输;所述第二级耦合线圈也由两个上下完全对称的电感相互缠绕形成,信号由第一级耦合线圈到达第二级耦合线圈后分也分别按顺时针和逆时针传输至功分器芯片的两路功分端口;并且,所述第二级耦合线圈翻折进第一级耦合线圈内部;

RC串联网络,所述RC串联网络设置在第一级耦合线圈内部,包括第一级RC串联网络和第二级RC串联网络,所述第一级RC串联网络连接第一级耦合线圈的功分两路;所述第二级RC串联网络连接第二级耦合线圈的功分两路;

两个谐振电容,所述两个谐振电容连接在第一级耦合线圈和第二级耦合线圈的连接处并接入到地。

本发明将第二级耦合线圈设置在第一级耦合线圈内部,从而达到充分利用版图空间,缩小功分器芯片尺寸的目的。为保证将第二级线圈翻折进第一级耦合线圈内部,同时能够将其余元器件全部放入第一级耦合线圈内部,使得整个功分器芯片的电路面积仅为第一级耦合线圈的面积。所述第一级耦合线圈的内径大于第二级耦合线圈的外径。

此外,第一级耦合线圈与第二级耦合线圈之间的壁间寄生电容是我们不需要的,因此所述第一级耦合线圈的内圈金属边沿到第二级耦合线圈的外圈金属边沿的距离大于3倍线圈宽度。线圈宽度是指第一级耦合线圈或第一级耦合线圈中金属边的宽度。

若第一级耦合线圈与第二级耦合线圈之间存在耦合,系统的4个谐振点将相互靠近,从而缩小功分器芯片的工作带宽。为了不让第一级耦合线圈与第二级耦合线圈之间的耦合影响功分器芯片的工作带宽,应使第一级耦合线圈产生的磁力线穿过第二级耦合线圈的磁通量为0。由于信号在第一级耦合线圈中的流向以及线圈对称的特点,只需要将第二级耦合线圈放置在第一级耦合线圈中心位置,即所述第一级耦合线圈与第二级耦合线圈的中心重合,就能使向上穿过第二级耦合线圈的磁力线与向下穿过第二级耦合线圈的磁力线相互抵消,即第一级耦合线圈对第二级耦合线圈不会产生影响。由于互耦关系,第二级耦合线圈对第一级耦合线圈也将没有影响。

第一级耦合线圈输出两路之间通过串联电阻-电容-电阻相连,第二级线圈输出两路之间通过电容-电阻-电容相连。为保证将电阻、电容器件放入第一级线圈内部,同时第二级耦合线圈在第一级耦合线圈内部的中心位置,所述第一级RC串联网络和第二级RC串联网络设置在内,并设置在第二级耦合线圈的左右两侧。进一步的,为了让功分端口远离合路端口,所述第一级RC串联网络设置在第二级耦合线圈靠近合路端口侧;所述第二级RC 串联网络设置在第二级耦合线圈靠近功分端口侧。这样第一级耦合线圈设计为2N圈,第二级耦合线圈设计为2M+1圈,其中N和M为正整数。

示例:

图1所示为采用GaAsum IPD工艺设计的工作于6GHz~26GHz(相对带宽B≈1.6)功分器芯片示意图,包括第一级耦合线圈1,第二级耦合线圈2,第一级RC串联网络3、4,第二级RC串联网络5、6,两个公共端接入到地的谐振电容7。

信号从合路端口Port1进入功分器芯片,合路端口Port1与第一级耦合线圈1的线圈抽头相连,第一级耦合线圈1的功分两路输出分别连接两个公共电容7以及第二级耦合线圈2的两路输入端。信号继续进入第二级耦合线圈2的两个输入端,第二级耦合线圈2的输出端去往功分器芯片的两个功分端口Port2、Port3。第一级RC串联网络3、4和第二级RC串联网络 5、6用来提高功分端口隔离度。

图2为折叠线圈的折叠过程,首先确定第一级耦合线圈1和第二级耦合线圈2所需电感量,合理设计第一级耦合线圈1和第二级耦合线圈2的尺寸,将第二级耦合线圈2以及其余元器件整体翻转180°进入第一级耦合线圈1内部。最后按如图3所示完成版图设计。

按照如上方法设计布版的功分器芯片最终尺寸为0.7mm*0.72mm。除去焊盘,其电路核心区域面积仅为0.32mm*0.3mm,不到0.1mm

由此可见,本发明能够极大的减小功分器芯片的尺寸,并且表现出优异的性能。

以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 一种基于折叠线圈的紧凑功分器芯片

- 一种基于互感耦合的超宽带功分器芯片