一种高导电效率的GaN基HEMT芯片及其制备方法

文献发布时间:2023-06-19 12:13:22

技术领域

本发明涉及半导体器件制造技术领域,具体为一种高导电效率的GaN基HEMT芯片及其制备方法。

背景技术

硅功率MOSFET为电路设计人员提供了许多优势,使其成为许多应用中的明显选择。它提供高开关速度和低导通电阻,与之前的双极晶体管不同,MOSFET不会受到热失控的影响。制造技术的进一步发展使得可以使用垂直配置,并联多个晶体管的设备,进一步降低了导通电阻。

在几十年的时间里,制造商对基本设计进行了改进,设置导通电阻和击穿电压的新标准。然而,这些参数通常需要在MOSFET设计中相互折衷。增加击穿电压的技术往往会推高导通电阻。因此,诸如绝缘栅双极晶体管(IGBT)等竞争器件已经取得了进展,其应用需要比MOSFET更高的击穿电压额定值。

一种选择是更换材料。氮化镓(GaN)和碳化硅是硅的潜在替代品,由于这些材料具有更高的带隙,因此可以在不影响导通电阻的情况下支持击穿电压的大幅增加。SiC和GaN的临界电场强度均高于硅,给予它们导通电阻和击穿电压之间的优越关系。这使得器件可以做得更小,并且电气端子可以在给定的击穿电压要求下更紧密地联系在一起。

AlGaN/GaN HEMT作为GaN基器件的代表,由于材料GaN具有直接带隙、宽带隙(3.4eV)的特点从而具有高效率,同时具有高热导率因此耐高温辐射,可应用于严苛环境中,并且GaN材料具有高电子迁移率因此奇迹适用于高频率、大功率电路中。由于目前主流的AlGaN/GaN HEMT均是沿Ga面生长,因为AlGaN与GaN材料的禁带宽度不同,AlGaN的禁带宽度高于GaN,使二者的导带底存在一个带阶差,这个导带的带阶差加上上面分析的界面处的大量正电荷会使导带底能带弯曲,能带弯曲使异质结结面处形成一个二维势阱。这个二维势阱将会把之前讨论的极化诱生电子限制其中,这些电子在势阱中只能沿着平行于突变结界面的平面内作二维运动,因此被称为二维电子气(2DEG)。所以,在Al(Ga)N/GaN突变异质结结构中,即使不对AlGaN势垒层进行任何掺杂,凭借数量巨大的极化正电荷,所感应得到的2DEG的面密度也能高达2×1013cm-2。

但是,当AlGaN/GaN HEMT器件工作时所受的栅极电压偏置较大时,AlGaN势垒的能带被拉低,处于异质结界面的2DEG将会通过隧穿或者热激发直接越过势垒进入AlGaN势垒层中移动。

发明内容

本发明的目的在于提供了一种在相同芯片面积的前提下,且兼顾了芯片的耐压能力,提高了芯片导电效率同时可降低芯片成本的一种高导电效率的GaN基HEMT芯片及其制备方法。

为实现上述目的,本发明提供如下技术方案:一种高导电效率的GaN基HEMT芯片,包括:

硅基衬底;

外延层,所述外延层包括GaN外延层和AlGaN外延层,所述GaN外延层表面均匀开设有沟槽,所述AlGaN外延层固定连接于GaN外延层表面开设的沟槽中;

其中,所述GaN外延层固定连接于硅基衬底顶端表面。

优选的,所述AlGaN外延层表面通过沉积和光刻等制程形成P-GaN Gate、源极接触和漏极接触。

优选的,所述AlGaN外延层通过第一金属层和第二金属层形成源极接触孔和漏极接触孔。

优选的,所述AlGaN外延层通过注入制程形成隔离氧化层。

优选的,所述P-GaN Gate、源极接触和漏极接触上沉积有第一层绝缘层。

优选的,所述P-GaN Gate表面固定连接有栅极金属,所述栅极金属表面沉积有第二绝缘层。

优选的,所述第一金属层表面沉积有第三绝缘层,所述第二金属层表面设置有钝化层。

优选的,所述沟槽均匀分布于GaN外延层表面。

优选的,所述GaN外延层表面的沟槽深度小于20nm。

一种高导电效率的GaN基HEMT芯片的制备方法,包括以下步骤:

S1、选取原物料硅基衬底作为准备;

S2、在硅基衬底上进行GaN外延层生长,GaN外延层厚度约为1-2um,在GaN外延层表面进行第一道光刻制程形成均匀的沟槽;

S3、在GaN外延层表面进行AlGaN外延层生长,因为沟槽,形成了凹凸不平的GaN外延层和AlGaN外延层设计;

S4、在AlGaN外延层上进行掺杂的P-GaN沉积并进行第二次光刻制程(PG)形成P-GaN Gate,形成E-mode GaN基器件;

S5、在AlGaN外延层上进行Ohmic Contact金属沉积并进行第三次光刻制程(OC)形成源极接触和漏极接触;

S6、在AlGaN外延层上进行第四次光刻制程(IS)并通过注入制程形成隔离氧化层,作为单胞隔离作用,在P-GaN Gate、源极接触和漏极接触上沉积第一层绝缘层;

S7、对第一层绝缘层上进行第五次光刻制程(GS),露出P-GaN Gate以便将栅极引出;

S8、在芯片表面上沉积金属并在P-GaN Gate位置进行第六次光刻制程(GT)形成栅极金属,通过栅极金属将栅极引出;

S9、在栅极金属上沉积第二绝缘层并进行第七次光刻制程(V0),露出源极接触和漏极接触;

S10、在芯片表面上进行第一金属层沉积并进行第八次光刻制程(M1),将源极接触和漏极接触通过第一金属层引出;

S11、在芯片表面上进行第三绝缘层沉积并进行第九次光刻制程(V1),露出源极和漏极上面的第一金属层;

S12、在芯片表面上进行第二金属层沉积并进行第十次光刻制程(M2),将源极金属和漏极金属引出;

S13、在芯片表面进行钝化层沉积并进行第十次光刻制程(TP),做芯片正面保护层,并露出栅极、源极和漏极打线区域,即可得到一种高导电效率的GaN基HEMT芯片。

与现有技术相比,本发明的有益效果是:

1.本发明在相同芯片面积的前提下,提高了芯导通的电流密度,兼顾了芯片的耐压能力下,提高了芯片导电效率同时可降低芯片的成本。

2.本发明通过在GaN外延层表面均匀开设沟槽,在沟槽蚀刻完成后再进行ALGaN外延层生长,形成凹凸不平的AlGaN/GaN外延层设计,增加了AlGaN外延层和GaN外延层界面的二维电子气密度,提高了芯片导通的电流密度,提高了GaN基HEMT芯片的导电效率。

3.本发明通过采用GaN外延层刻蚀沟槽的方法实现了凹凸不平的AlGaN/GaN外延层设计,增加了AlGaN外延层和GaN外延层接触面积,增加了外延层中的二维电子气面积,在兼顾了芯片的耐压能力下,该设计可节省部分芯片面积,降低了GaN基HEMT芯片的成本。

附图说明

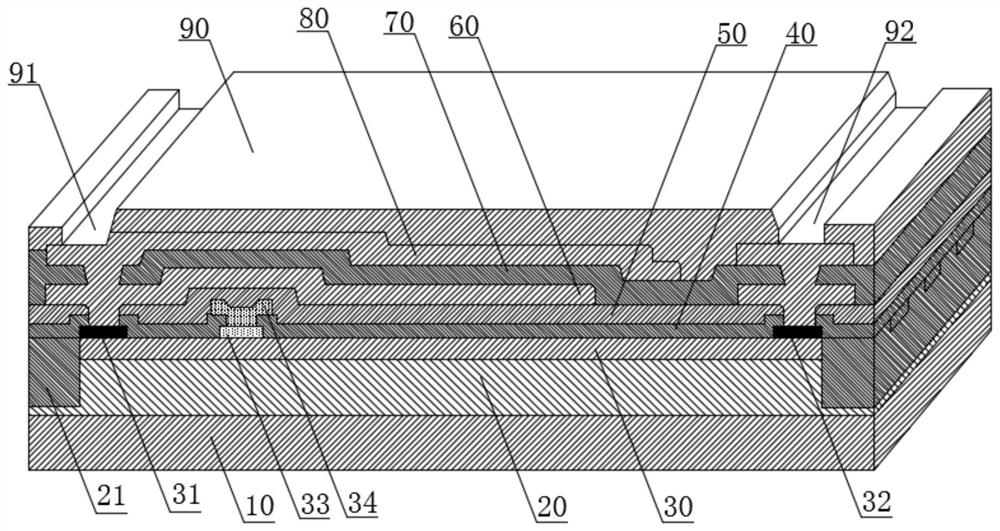

图1为本发明的整体结构示意图;

图2为本发明的局部结构示意图。

图中:10-硅基衬底;20-GaN外延层;21-隔离氧化层;22-沟槽;30-AlGaN外延层;31-源极接触;32-漏极接触;33-P-GaN Gate;34-栅极金属;40-第一绝缘层;50-第二绝缘层;60-第一金属层;70-第三绝缘层;80-第二金属层;90-钝化层;91-源极接触孔;92-漏极接触孔。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

实施例1:

请参阅图1-2,本发明提供一种技术方案:一种高导电效率的GaN基HEMT芯片,包括:硅基衬底10和外延层。

其中,所述外延层包括GaN外延层20和AlGaN外延层30,所述GaN外延层20表面均匀开设有沟槽22,所述AlGaN外延层30固定连接于GaN外延层20表面开设的沟槽22中。

本实施例中,具体的,沟槽22均匀分布于GaN外延层20表面。

本实施例中,具体的,GaN外延层20表面的沟槽22深度小于20nm。

进一步地,GaN外延层20采用沟槽22设计来增加AlGaN/GaN界面的二维电子气密度,提高了芯片导通的电流密度,提高了GaN基HEMT芯片的导电效率;同时该设计也增加了AlGaN外延层和GaN外延层接触面积,增加了外延层中的二维电子气面积,在兼顾了芯片的耐压能力下,该设计可节省部分芯片面积,可降低GaN基HEMT芯片的成本。

其中,所述GaN外延层20固定连接于硅基衬底10顶端表面。

其中,所述AlGaN外延层30表面通过沉积和光刻等制程形成P-GaNGate33、源极接触31和漏极接触32。

进一步地,GaN外延层20的整个表面均匀开设沟槽22的设计,可以看出图中GaN外延层20、AlGaN外延层30、P-GaN Gate33、源极接触31和漏极接触32均为均匀沟槽22设计,在保证栅极控制速度、源极和漏极导通速度的同时,增加了GaN外延层20和AlGaN外延层30之间的二维电子气密度,提高了导通电流密度,提高了E-mode GaN基HEMT芯片的导电效率。

其中,所述AlGaN外延层30通过第一金属层60和第二金属层80形成源极接触孔91和漏极接触孔92。

其中,所述AlGaN外延层30通过注入制程形成隔离氧化层21。

其中,所述P-GaN Gate33、源极接触31和漏极接触32上沉积有第一层绝缘层40。

其中,所述P-GaN Gate33表面固定连接有栅极金属34,所述栅极金属34表面沉积有第二绝缘层50。

其中,所述第一金属层60表面沉积有第三绝缘层70,所述第二金属层80表面设置有钝化层90。

综合以上实施例所述,通过在GaN外延层表面均匀开设沟槽,在沟槽蚀刻完成后再进行ALGaN外延层生长,形成凹凸不平的AlGaN/GaN外延层设计,增加了AlGaN外延层和GaN外延层界面的二维电子气密度,提高了芯片导通的电流密度,提高了GaN基HEMT芯片的导电效率;同时也增加了AlGaN外延层和GaN外延层接触面积,增加了外延层中的二维电子气面积,在兼顾了芯片的耐压能力下,该设计可节省部分芯片面积,可降低GaN基HEMT芯片的成本。

实施例流片制程步骤:

请参阅图1-2,本发明提供一种技术方案:一种高导电效率的GaN基HEMT芯片的制备方法,包括以下步骤:

S1、选取原物料硅基衬底10作为准备;

S2、在硅基衬底10上进行GaN外延层20生长,GaN外延层20厚度约为1-2um,在GaN外延层20表面进行第一道光刻制程形成均匀的沟槽22;

S3、在GaN外延层20表面进行AlGaN外延层30生长,因为沟槽22,形成了凹凸不平的GaN外延层20和AlGaN外延层30设计;

S4、在AlGaN外延层30上进行掺杂的P-GaN沉积并进行第二次光刻制程(PG)形成P-GaN Gate33,形成E-mode GaN基器件;

S5、在AlGaN外延层30上进行Ohmic Contact金属沉积并进行第三次光刻制程(OC)形成源极接触31和漏极接触32;

S6、在AlGaN外延层30上进行第四次光刻制程(IS)并通过注入制程形成隔离氧化层21,作为单胞隔离作用,在P-GaN Gate33、源极接触31和漏极接触32上沉积第一层绝缘层40;

S7、对第一层绝缘层40上进行第五次光刻制程(GS),露出P-GaN Gate33以便将栅极引出;

S8、在芯片表面上沉积金属并在P-GaN Gate33位置进行第六次光刻制程(GT)形成栅极金属34,通过栅极金属34将栅极引出;

S9、在栅极金属34上沉积第二绝缘层50并进行第七次光刻制程(V0),露出源极接触31和漏极接触32;

S10、在芯片表面上进行第一金属层60沉积并进行第八次光刻制程(M1),将源极接触31和漏极接触32通过第一金属层60引出;

S11、在芯片表面上进行第三绝缘层70沉积并进行第九次光刻制程(V1),露出源极和漏极上面的第一金属层60;

S12、在芯片表面上进行第二金属层80沉积并进行第十次光刻制程(M2),将源极金属和漏极金属引出;

S13、在芯片表面进行钝化层90沉积并进行第十次光刻制程(TP),做芯片正面保护层,并露出栅极、源极和漏极打线区域,即可得到一种高导电效率的GaN基HEMT芯片。

本发明以P-GaN Gate的E-mode GaN基HEMT器件结构为图例说明本发明的设计,但其他设计的E-mode GaN基HEMT器件结构也适用,例如沟槽栅设计的E-mode GaN基HEMT器件也适用,并且其他的D-mode GaN基HEMT器件结构也同样适用。

需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。

以上所述仅为本发明的实施方式,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

- 一种高导电效率的GaN基HEMT芯片及其制备方法

- 一种高导电效率的GaN基HEMT芯片