CIS芯片深阱设计方法与制作工艺方法

文献发布时间:2023-06-19 12:14:58

技术领域

本发明涉及CIS芯片深阱设计与制作工艺技术领域,尤其涉及一种CIS芯片深阱设计方法与制作工艺方法。

背景技术

CMOS图像传感器(CMOS image sensor,CIS)目前在市场上应用较为广泛的是像素pitch size(图形周期大小)在1.1um左右,随着对CIS应用的要求越来越高与之对应的像素尺寸要求越来越小,从而可以相同面积内得到更多的像素点,从像素设计上来说对应的pitch也随之缩小。

小像素的优点是在同样的面积上可以得到更多的像素点,要得到更高像素和更清晰的图像;也就意味着在更小的感光面积上得到与大像素一样的满阱能力(Full WellCapability,FWC),而要在更小面积的得到同样的FWC,只能往PD(Photodiode,光电二极管)的纵深方向发展,从工艺上来说也就是将形成PD的N型离子和隔离每个PD的P型离子注入的更深。

在CIS芯片中P型深阱(Deep P+Well,DPW)是隔离每个像素中Photodiode的一道工艺,但是对于这些需要高剂量离子注入的layer(层)来说需要相对较厚的光阻(>2um),在同样光阻的高深宽比的条件下pitch缩小意味着工艺难度的成倍提升。

发明内容

本发明的目的是提供一种CIS芯片深阱设计方法与制作工艺方法,可以降低工艺难度,得到较好形貌的目标图案。

本发明的目的是通过以下技术方案实现的:

一种CIS芯片深阱设计方法,包括:

将原来图形周期大小为A的P型深阱DPW设为光罩DPW1,将光罩DPW1的图案依次沿X方向和Y方向各移动A/2得到图案设为光罩DPW2,将光罩DPW1与光罩DPW2的图案重叠得到图形周期大小为A/2的图案作为CIS芯片P型深阱DPW。

一种CIS芯片深阱的制作工艺方法,包括:

按照前述的设计方法设计CIS芯片P型深阱DPW;

在一次光刻过程中,先用光罩DPW1曝光,再用光罩DPW2进行曝光,然后进行烘烤与显影处理,得到图形周期大小为A/2的图案。

由上述本发明提供的技术方案可以看出,在原有光罩基础上设计新的光罩图案,并通过对准重叠的方式得到缩小一半图形周期大小的光罩图案,此外,上述方案不仅降低了高像素DPW layer的工艺难度,还能够得到形貌的目标图案。

附图说明

为了更清楚地说明本发明实施例的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域的普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他附图。

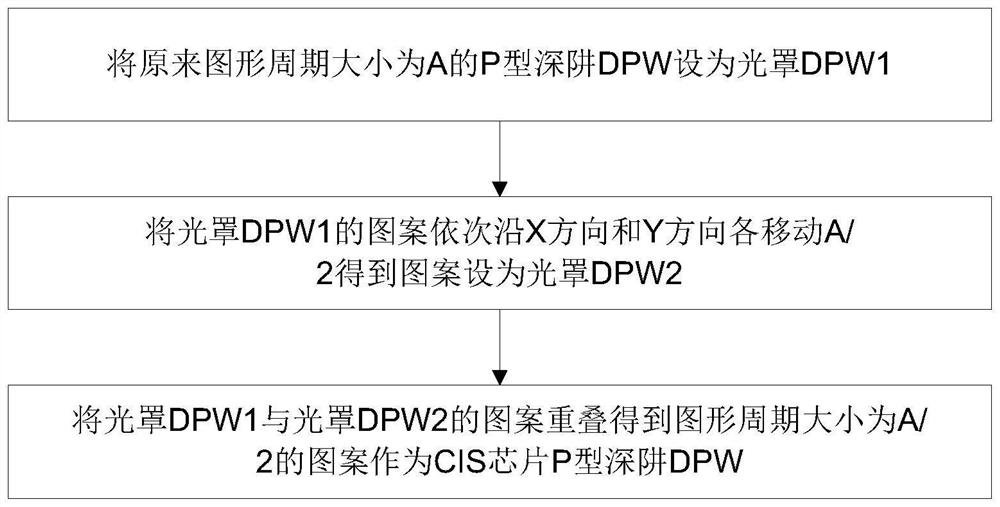

图1为本发明实施例提供的一种CIS芯片深阱设计方法的流程图;

图2为本发明实施例提供的一种CIS芯片深阱的制作工艺方法的流程图;

图3为本发明实施例提供的pitch为A的DPW的GDS与JDV图案示意图;

图4为本发明实施例提供的pitch为A/2的DPW的GDS与JDV图案示意图;

图5为本发明实施例提供的光罩DPW1对AA,光罩DPW2对AA,光罩DPW2对光罩DPW1的套刻标识示意图。

具体实施方式

下面结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明的保护范围。

本发明实施例提供一种CIS芯片深阱设计方法,如图1所示,其主要包括:

将原来图形周期大小为A的P型深阱(DPW)设为光罩DPW1,将光罩DPW1的图案依次沿X方向和Y方向各移动A/2得到图案设为光罩DPW2,将光罩DPW1与光罩DPW2的图案重叠得到图形周期大小为A/2的图案作为CIS芯片P型深阱DPW。

本发明实施例中,为了保证了DPW1图形和DPW2相互间的对准以及它们对于前层的对准,采用了如下方案来将光罩DPW1与光罩DPW2的图案重叠:在光罩DPW1与光罩DPW2上分别设计对准有源区(AA)的套刻标记,以及在光罩DPW1与光罩DPW2之间设计相应的套刻标记,通过设计的三组套刻标记实现光罩DPW1与光罩DPW2的对准,从而实现光罩DPW1与光罩DPW2的图案重叠操作。

本发明实施例中,光罩设计时,主要是结合一次光刻用两块的光罩工艺特点,分别对两块光罩的交叠部分和对准标记上的特殊设计,不仅可以得到缩小一半图形周期大小的光罩图案,还可以使得得到的光罩图案具有良好的形貌而且相对位置对准精确。

本发明另一实施例还提供一种CIS芯片深阱的制作工艺方法,如图2所示,包括:

首先,按照权利要求1或2或3所述的设计方法设计CIS芯片P型深阱DPW;具体的:将原来图形周期大小为A的P型深阱(DPW)设为光罩DPW1,将光罩DPW1的图案依次沿X方向和Y方向各移动A/2得到图案设为光罩DPW2;在光罩DPW1与光罩DPW2上分别设计对准AA的套刻标记,以及在光罩DPW1与光罩DPW2之间设计相应的套刻标记,通过设计的三组套刻标记实现光罩DPW1与光罩DPW2的对准;

之后,在一次光刻过程中,先用光罩DPW1曝光,再用光罩DPW2进行曝光,然后进行烘烤和显影处理,得到图形周期大小为A/2的图案。

此外,为了能得到较好的图形形貌,对于光罩DPW1和光罩DPW2各自本身的十字位置使用OPC(Optical Proximity Correction,光学临近效应修正),而光罩DPW1和光罩DPW2之间交叠的十字位置,考虑到此处在曝光过程中没有不同方向光的干涉和衍射影响,只需考虑两次曝光过程中会形成更多光酸导致图形变形的影响稍加修正交叠的十字位置即可,后续工艺过程中再根据实际的形貌来调整烘烤温度。

通过上述工艺方案可以降低高像素DPW layer的工艺难度。

在实际应用中,可以先在晶圆涂布目标厚度光刻胶,在一次曝光过程中先用光罩DPW1进行曝光,然后再用光罩DPW2进行曝光,最后通过烘烤和显影处理,最终得到pitch为A/2的图案。由于光罩中的特殊设计不但能得到较好的图形形貌,而且还保证了光罩DPW1与光罩DPW2相互间的对准以及它们对于前层的对准。

下面结合现有的方案对本发明上述方案的效果进行说明。

如图3所示,为pitch为A的DPW的GDS(Graphic Design System,图形设计系统)与JDV(Job deck view,在线光掩膜数据检视)图案,其中,左侧为GDS,右侧为JDV图案;从一次曝光工艺cross位置(交叉位置)来看,交叉位置存在来自X与Y两个方向的光场感光,其中还会存在相互衍射和干涉干扰,通常状况下JDV图案(pattern)会做出类似如图3所示的OPC修正(光学邻近效应修正)以保证得到接近GDS设计的图形。如图4所示,为基于本发明上述方案得到的pitch为A/2的深阱GDS与JDV图案,其中,左侧为GDS,右侧为JDV图案,左右图中外围区域为光罩DPW1,中间十字区域为DPW2;第一次曝光和第二次曝光交叠的位置,在每一次曝光中只有来自X或者Y方向其中一种方向光场感光,只是在第二次曝光过程中交叠位置下的光阻已经经过一次曝光,但是还没有经过高温烘烤使光酸扩散和显影工艺,所以对重叠位置影响不大,只是在直角接触位置可能在高温烘烤过程形成更多的光酸影响到它的形貌,可以对该位置做出OPC修正和调节烘烤温度来调节形貌。

本发明实施例上述方案,可以得到缩小一半图形周期大小的光罩图案,但是在一次光刻工艺中用两块光罩进行两次曝光过程中,不但需要解决光罩DPW1,光罩DPW2对AA的对准问题,还要解决光罩DPW1与光罩DPW2之间的对准问题。为了如图5所示,提前分别设计出光罩DPW1对AA,光罩DPW2对AA,以及光罩DPW2与光罩DPW1之间的OVL mark(套刻标记),其中:左侧部分为光罩DPW1对AA的套刻标记,外围线条表示AA,内部线条表示光罩DPW1;中间部分为光罩DPW2对AA的套刻标记,外围线条表示AA,内部线条表示光罩DPW2;右侧部分为光罩DPW2与光罩DPW1之间的套刻标记,外围线条表示光罩DPW1,内部线条表示光罩DPW2。在实际工艺过程中根据光罩DPW1和光罩DPW2对AA的OVL结果,来调节对准工艺参数,最终通过量测DPW2对DPW1的OVL结果来判断是否对准。

以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明披露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应该以权利要求书的保护范围为准。

- CIS芯片深阱设计方法与制作工艺方法

- CMOS图像传感器深P型阱层的光刻工艺方法