一种新型栅极驱动电路

文献发布时间:2023-06-19 12:16:29

技术领域

本发明涉及集成电路技术领域,特别涉及一种新型栅极驱动电路。

背景技术

在基于开关操作的各种应用中,效率与开关器件的损耗密切相关。开关元件的功率损耗主要由“开关损耗”和“导通损耗”两部分组成。“开关损耗”与开关速度有关,即指开关元件“从开态到关态”或“从关态到开态”发生的损耗;“导通损耗”是指由于“开关在通电状态时的阻抗”和“流过开关的电流”而造成的损耗。

如图1所示的半桥开关驱动感性负载电路,其开关在开态/关态切换时的功率损失如图2(a)和图2(b)所示,一般来说,降低开关损耗的方法是提高开关速度。即通过减小Tr和Tf来降低功率损耗。然而,开关操作会改变电流流动路径,由于布线中存在寄生参数,它经常引起高频共振(振铃)。通过增加驱动能力来降低Tr和Tf可以增加电流的变化率(di/dt),从而增加振铃的幅度。这不仅“增加了开关元件的应力”,而且“导致电磁波发射,影响外围电路的运行,高频发射造成能量损失”。

因此,有必要通过优化电流流动路径来降低寄生参数的影响。然而,在减少寄生参数方面往往有一定的限制,因此提高驱动能力也有一定的限制。这种有限的驱动能力也会影响导通损耗。这是因为开关完全开启或关闭所需的时间也取决于驱动能力。一般来说,开关具有从关态进入开态的阈值电压。即当控制开关相关节点的电压(控制电压)幅值大于阈值电压时,开关中可能流过电流,随着电压幅值的增大,开关的导通阻抗减小。因此,直到开关控制电压足够高时,开关的导通阻抗的值都高于预期值,以致于导通损耗也很高。

发明内容

本发明的目的在于提供一种新型栅极驱动电路,以解决背景技术中的问题。

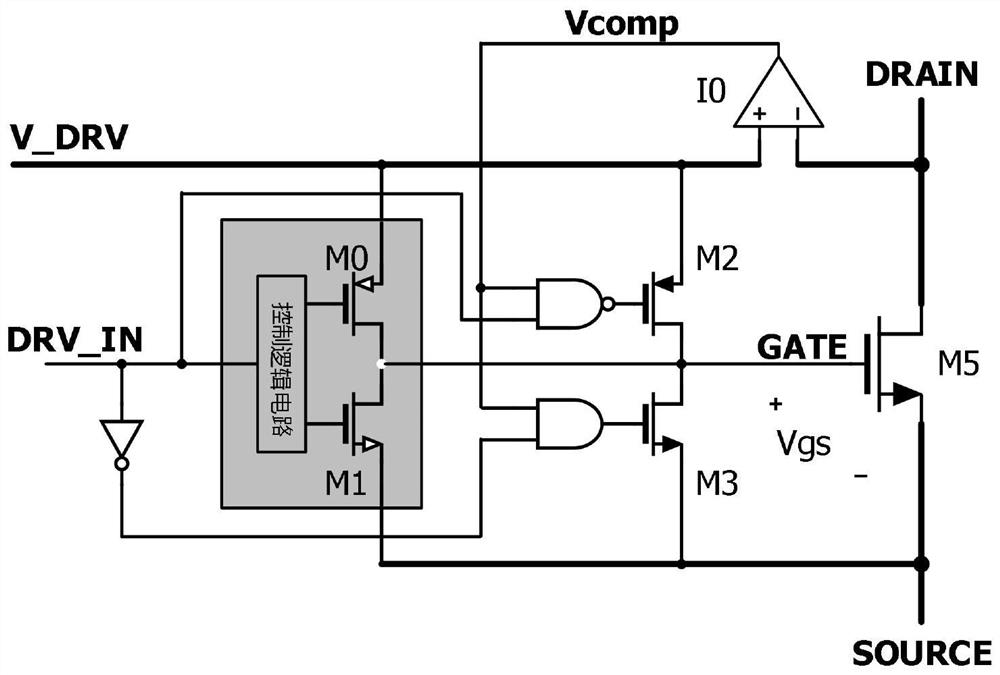

为解决上述技术问题,本发明提供了一种新型栅极驱动电路,包括比较器I0、PMOS管M0、PMOS管M2、NMOS管M1、NMOS管M3、NMOS管M5、非门与非门、与门和控制逻辑电路;

与门的第一输入端连接非门的输出端,第二输入端连接比较器I0的输出端,与门的输出端连接NMOS管M3的栅极;

与非门的第一输入端连接非门的输入端,第二输入端连接比较器I0的输出端,与非门的输出端连接PMOS管M2的栅极;

PMOS管M2的源极连接比较器I0的正输入端,漏极接NMOS管M5的栅极;

NMOS管M3的漏极接NMOS管M5的栅极,源极接源端SOURCE;

NMOS管M5的漏极接比较器I0的负输入端,源端接源端SOURCE。

可选的,所述PMOS管M0的栅极和所述NMOS管M1的栅极均连接控制逻辑电路。

可选的,所述PMOS管M0的源极连接比较器I0的正输入端。

可选的,所述PMOS管M0的漏极接所述NMOS管M5的栅极,所述NMOS管M1的漏极接所述NMOS管M5的栅极。

可选的,所述比较器I0包括NMOS管M6、电阻R0和触发器I1;

所述NMOS管M6的源端接电阻R0,漏端接所述NMOS管M5的漏极,栅极连接PMOS管M2的源极;

触发器I1的输入端连接NMOS管M6的源极,输出端作为比较器I0的输出端。

在本发明提供的新型栅极驱动电路中,包括比较器I0、PMOS管M0、PMOS管M2、NMOS管M1、NMOS管M3、NMOS管M5、非门与非门、与门和控制逻辑电路;与门的第一输入端连接非门的输出端,第二输入端连接比较器I0的输出端,与门的输出端连接NMOS管M3的栅极;与非门的第一输入端连接非门的输入端,第二输入端连接比较器I0的输出端,与非门的输出端连接PMOS管M2的栅极;PMOS管M2的源极连接比较器I0的正输入端,漏极接NMOS管M5的栅极。本发明能够有选择地调整驱动能力,可以降低导通损耗。

附图说明

图1是半桥开关驱动感性负载电路结构示意图;

图2(a)和图2(b)是开关在开态/关态切换时的功率损失示意图;

图3是本发明提供的新型栅极驱动电路结构示意图;

图4是本发明提供的新型栅极驱动电路结构示意图;

图5(a)和图5(b)是在不改变Tr/Tf的情况下降低导通损耗示意图。

具体实施方式

以下结合附图和具体实施例对本发明提出的一种新型栅极驱动电路作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

实施例一

本发明提供了一种新型栅极驱动电路,其结构如图3所示,包括比较器I0、PMOS管M0、PMOS管M2、NMOS管M1、NMOS管M3、NMOS管M5、非门与非门、与门和控制逻辑电路;与门的第一输入端连接非门的输出端,第二输入端连接比较器I0的输出端,与门的输出端连接NMOS管M3的栅极;与非门的第一输入端连接非门的输入端,第二输入端连接比较器I0的输出端,与非门的输出端连接PMOS管M2的栅极;PMOS管M2的源极连接比较器I0的正输入端,漏极接NMOS管M5的栅极;NMOS管M3的漏极接NMOS管M5的栅极,源极接源端SOURCE;NMOS管M5的漏极接比较器I0的负输入端,源端接源端SOURCE;所述PMOS管M0的栅极和所述NMOS管M1的栅极均连接控制逻辑电路;所述PMOS管M0的源极连接比较器I0的正输入端;所述PMOS管M0的漏极接所述NMOS管M5的栅极,所述NMOS管M1的漏极接所述NMOS管M5的栅极。

进一步的,如图4所示,比较器I0包括NMOS管M6、电阻R0和触发器I1;所述NMOS管M6的源端接电阻R0,漏端接所述NMOS管M5的漏极,栅极连接PMOS管M2的源极;触发器I1的输入端连接NMOS管M6的源极,输出端作为比较器I0的输出端。

NMOS管M6的源极电压跟随NMOS管M5漏极电压,而且被钳位(在触发器I1允许输入电压范围内)。也就是说,通过NMOS管M6,NMOS管M5漏极的电压被感应到NMOS管M6的源极。NMOS管M6源极的电压与触发器I1的触发电压进行比较,(触发电压介于“M5源极电压”和“V_DRV”之间)。虽然触发器I1的触发电压与“V_DRV的电压”不同,但这并不重要,由于触发电压与“V_DRV电压”有关,开关过渡通常非常快而且触发器I1的响应时间相当短,所以Vcomp电压反映了图3中比较器I0比较“V_DRV电压”和“M5漏极电压”的结果。根据图3的新型栅极驱动电路有选择地调整驱动能力,可以降低导通损耗,如图5(a)和图5(b)所示。

上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

- 一种栅极驱动电路以及一种正反扫描栅极驱动电路

- 一种栅极驱动电路单元及栅极驱动电路