有机发光二极管显示器的电源和数据路由结构

文献发布时间:2023-06-19 12:19:35

本申请是申请号为201780003465.4、申请日为2017年1月19日、名称为“有机发光二极管显示器的电源和数据路由结构”的发明专利申请的分案申请。

技术领域

本发明整体涉及电子设备,并且更具体地涉及具有有机发光二极管显示器的电子设备。

背景技术

电子设备通常包括显示器。例如,电子设备可具有基于有机发光二极管像素的有机发光二极管显示器。每个像素可具有包括相应发光二极管的像素电路。该像素电路中的薄膜晶体管电路可用于控制向该像素中的发光二极管施加电流。该薄膜晶体管电路可包括驱动晶体管。该像素电路中的驱动晶体管和发光二极管可串联耦接在正电源和接地电源之间。

有机发光二极管显示器中的信号诸如电源信号可能由于用于分配这些信号的导电路径中的电阻损耗而遭受到不期望的电压降。如果不小心,这些电压降可妨碍有机发光二极管显示器的良好运转。在具有信号路由空间受限的布局的显示器中分配电源和数据信号时也会出现挑战。

因此,希望能够提供在显示器诸如有机发光二极管显示器上分配信号诸如电源和数据信号的改进方法。

发明内容

有机发光二极管显示器可具有形成于基板上的薄膜晶体管电路。显示器和基板可具有圆角。像素定义层可形成于薄膜晶体管电路上。该像素定义层中的开口可设置有与有机发光二极管的相应阳极重叠的发射材料。

阴极层可覆盖像素阵列。接地电源路径可用于将接地电压分配到阴极层。接地电源路径可由金属层形成,该金属层使用形成二极管的阳极的金属层的部分而被短接到阴极层,可由网格状金属图案形成,可具有L形路径段,可包括位于阴极层上的激光沉积金属,并可具有便于接地电源的分配的其他结构。网格状金属图案(例如,金属电源网格路径)、具有L形路径段的金属图案、以及其他结构也可用于促进正电源电压的分配。这些电源路径结构可容纳具有圆角的显示器和基板。

附图说明

图1为根据实施方案的具有显示器的示例性电子设备的图示。

图2为根据实施方案的示例性有机发光二极管像素电路的图示。

图3为根据实施方案的示例性有机发光二极管显示器的图示。

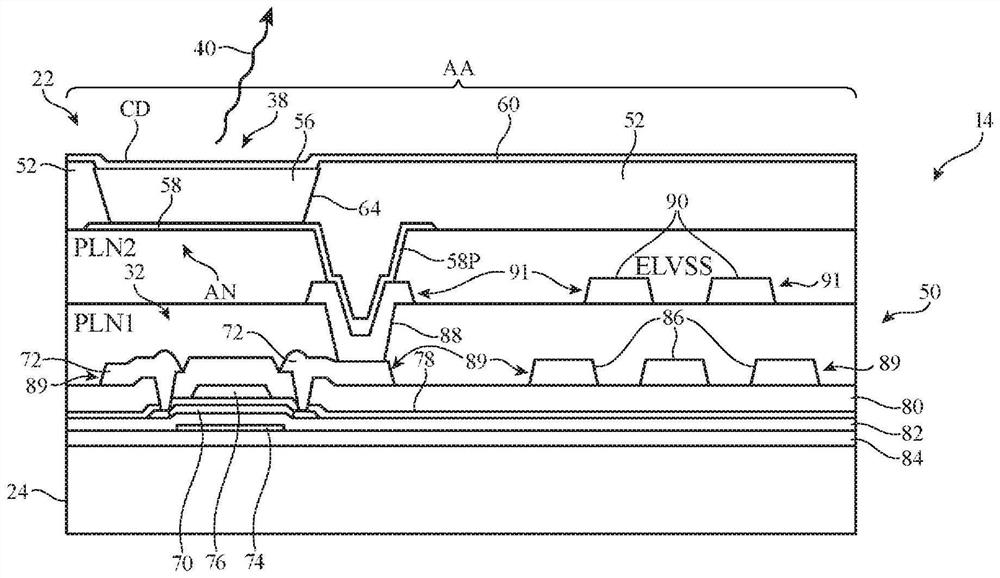

图4为根据实施方案的示例性有机发光二极管显示器的有效区域的一部分的横截面侧视图。

图5为根据实施方案的示例性有机发光二极管显示器的无效边界区域一部分的横截面侧视图。

图6为示出了根据实施方案的可用于显示器中的接地电源路径的示例性网格状图案的图示。

图7为示出了根据实施方案的图6的接地电源路径如何用于具有圆角的显示器的图示。

图8、图9和图10示出了根据实施方案的用于具有柔性尾部部分的显示器的示例性电源路径布局。

图11为根据实施方案的具有正电源路径结构和接地电源路径结构的显示器的拐角部分的顶视图。

图12和图13为根据实施方案的图11的显示器的一部分的横截面侧视图。

图14为根据另一个实施方案的具有正信号路由结构和接地信号路由结构的显示器的拐角部分的顶视图。

图15、图16和图17为根据实施方案的图14的显示器的一部分的横截面侧视图。

图18为根据实施方案的具有由金属线、网格状结构(例如,金属电源网格路径)和条形路径形成的电源路径的示例性显示器的图示。

图19为示出了根据实施方案的可具有带有阶梯状部分的数据线的显示器如何容纳圆形显示信号路由结构拐角的图示。

图20为根据实施方案的示例性有机发光二极管显示器中的层的横截面侧视图。

图21为根据实施方案的用于减小电源电压下降的具有激光沉积信号线的网格的示例性显示器的顶视图。

图22为根据实施方案的图21的显示器的一部分的横截面侧视图。

图23和图24为根据实施方案的制造期间的图21的显示器的一部分的横截面侧视图。

图25、图26、图27和图28为根据实施方案的可用于显示器诸如图21的显示器中的路径诸如激光沉积信号线的示例性图案的顶视图。

图29为根据实施方案的由显示器基板上的薄膜晶体管电路形成的示例性栅极驱动器电路的图示。

图30为示出了根据实施方案的可横向偏移和旋转的栅极驱动器行块如何容纳具有曲边的显示器基板的示例性显示器的图示。

图31为示出了根据实施方案的与显示器的有效区域重叠的数据线延伸部如何用于将来自对角线数据线段的信号路由至数据线的垂直部分的示例性显示器的图示。

图32为示出了根据实施方案的可在不同行中具有不同形状的显示驱动器电路诸如栅极驱动器行块如何容纳弯曲显示器基板边缘的图示。

图33为根据实施方案的可由显示器基板上的薄膜晶体管电路的一部分形成的类型的示例性显示器测试多路复用器电路的图示。

图34为示出了根据实施方案的如何测试可在显示器的下边缘处的测试点至沿显示器的上边缘的测试多路复用器电路之间路由的信号的示例性显示器的图示。

图35为示出了根据实施方案的测试多路复用器电路和测试点如何沿显示器的下边缘上的显示器基板尾部的一部分被定位的示例性显示器的图示。

图36和图37为示出了其中根据实施方案的被布置成容纳弯曲显示器基板边缘的测试电路的示例性显示器的图示。

具体实施方式

图1示出了可具有有机发光二极管显示器的类型的示例性电子设备。电子设备10可为计算设备诸如膝上型计算机、包含嵌入式计算机的计算机监视器、平板电脑、蜂窝电话、媒体播放器、或其他手持式或便携式电子设备、较小的设备(诸如腕表设备、挂式设备、耳机或听筒设备、被嵌入在眼镜中的设备或者佩戴在用户的头部上的其他设备,或其他可佩戴式或微型设备)、显示器、包含嵌入式计算机的计算机显示器、不包含嵌入式计算机的计算机显示器、游戏设备、导航设备、嵌入式系统(诸如其中具有显示器的电子设备被安装在信息亭或汽车中的系统)、或其他电子设备

如图1所示,电子设备10可具有控制电路16。控制电路16可包括用于支持设备10的操作的存储和处理电路。该存储和处理电路可包括存储装置,诸如硬盘驱动器存储装置、非易失性存储器(例如,被配置为形成固态驱动器的闪存存储器或其他电可编程只读存储器)、易失性存储器(例如,静态或动态随机存取存储器),等等。控制电路16中的处理电路可用于控制设备10的操作。该处理电路可基于一个或多个微处理器、微控制器、数字信号处理器、基带处理器、电源管理单元、音频芯片、专用集成电路等。

设备10诸如输入-输出设备12中的输入-输出电路可用于允许将数据提供至设备10,并且允许将数据从设备10提供至外部设备。输入-输出设备12可包括按钮、操纵杆、滚轮、触摸板、小键盘、键盘、麦克风、扬声器、音频发生器、振动器、相机、传感器、发光二极管和其他状态指示器、数据端口等。用户可通过经由输入-输出设备12提供命令来控制设备10的操作并且可使用输入-输出设备12的输出资源来从设备10接收状态信息和其他输出。

输入-输出设备12可包括一个或多个显示器,诸如显示器14。显示器14可为包括用于采集来自用户的触摸输入的触摸传感器的触摸屏显示器,或者显示器14可对触摸不敏感。显示器14的触摸传感器可基于电容性触摸传感器电极阵列、声学触摸传感器结构、电阻性触摸部件、基于力的触摸传感器结构、基于光的触摸传感器、或其他合适的触摸传感器布置。用于显示器14的触摸传感器可由形成在具有显示器14的像素的公共显示器基板上的电极形成,或可由与显示器14的像素重叠的独立触摸传感器面板形成。如果需要,显示器14可对触摸不敏感(即,触摸传感器可被省略)。

可使用控制电路16来在设备10上运行软件,诸如操作系统代码和应用程序。在设备10的操作期间,运行于控制电路16上的软件可在显示器14上显示图像。

显示器14可为有机发光二极管显示器。在有机发光二极管显示器中,每个显示器像素包含相应有机发光二极管。图2中示出了示例性有机发光二极管像素的示意图。如图2所示,显示器像素22可包括发光二极管38。可将正电源电压ELVDD提供至正电源端子34,并且可将接地电源电压ELVSS提供至接地电源端子36。二极管38具有阳极(端子AN)和阴极(端子CD)。驱动晶体管32的状态控制流经二极管38的电流量,并且因此控制来自显示器像素22的发射光40的量。由于二极管38的阴极CD耦接至接地端子36,因此二极管38的阴极端子CD有时可被称为二极管38的接地端子。

为确保晶体管32保持在数据的连续帧之间的期望状态中,显示器像素22可包括存储电容器,诸如存储电容器Cst。存储电容器Cst的第一端子可在节点A处耦接至晶体管32的栅极并且存储电容器Cst的第二端子可在节点B处耦接至二极管38的阳极AN。将存储电容器Cst上的电压在节点A处施加到晶体管32的栅极,以控制晶体管32。可使用一个或多个开关晶体管诸如开关晶体管30来将数据加载到存储电容器Cst中。当开关晶体管30关断时,数据线D从存储电容器Cst隔离,并且节点A上的栅极电压等于被存储在存储电容器Cst中的数据值(即,来自被显示在显示器14上的显示器数据的先前帧的数据值)。当断定与显示器像素22相关联的行中的栅极线G(有时被称为扫描线)时,开关晶体管30将被导通并且数据线D上的新数据信号将被加载到存储电容器Cst中。电容器Cst上的新信号在节点A处被施加到晶体管32的栅极,从而调节晶体管32的状态并且调节由发光二极管38发射的光40的对应量。

如果需要,可使用除图2的构型之外的构型(例如,包括用于补偿驱动晶体管32中的阈值电压变化的电路的构型、发射使能晶体管与驱动晶体管32串联耦接的构型、具有由多个相应扫描线控制的多个开关晶体管的构型、具有多个电容器的构型等)来形成用于控制显示器14中的像素22的发光二极管的操作的电路(例如,显示器像素电路(诸如图2的显示器像素电路)中的晶体管、电容器等)。图2的像素22的电路仅为示例性的。

如图3所示,显示器14可包括层,诸如基板层24。基板24和显示器14中的其他层(如果需要)可由材料层诸如玻璃层、聚合物层(例如,柔性聚酰亚胺片材或其他柔性聚合物)等形成。基板24可为平面的和/或可具有一个或多个弯曲部分。基板24可具有带有左右垂直边缘和上下水平边缘的矩形形状,或者可具有非矩形形状。在基板24具有带有四个拐角的矩形形状的构型中,如果需要,这些拐角可为圆形。如果需要,显示器基板24可具有尾部部分,诸如尾部24T。

显示器14可具有像素22的阵列。像素22形成向用户显示图像的显示器14的有效区域AA。该显示器14的无效边界部分诸如沿基板24的一个或多个边缘的无效区域IA不包含像素22并且不向用户显示图像(即,无效区域IA没有像素22)。

每个像素22可具有发光二极管诸如图2的有机发光二极管38和相关联的薄膜晶体管电路(例如,图2的像素电路或其他合适的像素电路)。像素22的阵列可由像素结构(例如,由显示层上的结构诸如基板24形成的像素)的行和列形成。在像素22的阵列中可具有任何合适数量的行和列(例如,十个或更多个、一百个或更多个,或者一千个或更多个)。显示器14可包括不同颜色的像素22。例如,显示器14可包括发出红光的红色像素,发出绿光的绿色像素、和发出蓝光的蓝色像素。如果需要,可使用显示器14包括其他颜色的像素的构型。使用具有红色像素、绿色像素和蓝色像素的像素布置仅为示例性的。

如图3的示例中所示的,显示器基板24可具有尾部诸如尾部24T,该尾部具有比基板24的包含有效区域AA的一部分窄的宽度。该布置有助于使尾部24T被容纳在设备10的外壳内。如果需要,当显示器14被安装在电子设备外壳内时,尾部24T在显示器14的剩余部分下方可为弯曲的。

显示器14的显示驱动器电路20可被安装在耦接至尾部24T的印刷电路板上或者可被安装在尾部24T上。信号路径诸如信号路径26可耦接显示驱动器电路20,以控制电路16。电路20可包括一个或多个显示驱动器集成电路和/或薄膜晶体管电路。在操作期间,设备10的控制电路(例如,图1的控制电路16)可为电路诸如显示驱动器电路20提供要在显示器14上显示的有关图像的信息。为了在显示器像素22上显示图像,显示驱动器电路20可将对应图像数据提供至数据线D,并同时向支持显示驱动器电路诸如栅极驱动器电路18时发出时钟信号和其他控制信号。栅极驱动器电路18可产生用于像素22的栅极线信号(有时被称为扫描信号、发射使能信号等)或其他控制信号。可使用线诸如栅极线G来将栅极线信号传送至像素22。对于每行像素22可存在一个或多个栅极线。栅极驱动器电路18可包括集成电路和/或薄膜晶体管电路并且可沿显示器14的边缘(例如,沿如图3所示的显示器14的左边缘和/或右边缘)或显示器14中的其他位置(例如,作为尾部24T上的电路20的一部分,沿显示器14的下边缘等)定位。图3的构型仅为示例性的。

显示驱动器电路20将数据信号提供至多个对应数据线D上。利用图3的示例性布置,数据线D垂直延伸通过显示器14。数据线D与像素22的相应列相关联。

利用图3的示例性构型,栅极线G(有时被称为扫描线、发射线等)水平延伸通过显示器14。每个栅极线G与显示器像素22的相应行相关联。如果需要,可存在与像素22的每行相关联的多个水平控制线(栅极线G)。栅极驱动器电路18可断定显示器14中的栅极线G上的栅极信号。例如,栅极驱动器电路18可从显示驱动器电路20接收时钟信号和其他控制信号,并可响应于所接收的信号来从第一行显示器像素22中的栅极线信号G开始依次断定栅极线G上的栅极信号。在断定每个栅极线时,将来自数据线D的数据加载到显示器像素的对应行中。通过这种方式,设备10中的控制电路诸如显示驱动器电路20可为像素22提供用于指导像素22产生光以用于在显示器14上显示目标图像的信号。

可使用薄膜晶体管电路来形成像素22的电路和显示驱动器电路(如果需要)诸如电路18和/或20。通常可使用任何合适类型的薄膜晶体管技术(例如,硅晶体管诸如多晶硅薄膜晶体管、半导体氧化物晶体管诸如铟镓锌氧化物晶体管等等)来形成显示器14中的薄膜晶体管。

导电路径(例如,一个或多个信号线、覆盖导电膜和其他图案化导电结构)可被提供在显示器14中,以将数据信号D和功率信号诸如正电源信号ELVDD和接地电源信号ELVSS路由至像素22。如图3所示,使用从显示器14的尾部部分24T接收信号D、ELVDD和ELVSS的信号路由路径可将这些信号提供给有效区域AA中的像素22。

图4中示出了显示器14的有效区域AA的一部分的横截面侧视图,其示出了可用于形成像素22的示例性构型。如图4所示,显示器14可具有基板,诸如基板24。薄膜晶体管、电容器和其他薄膜晶体管电路50(例如,像素电路,诸如图2的示例性像素电路)可被形成在基板24上。像素22可包括有机发光二极管38。该二极管38的阳极AN可由金属层58(有时被称为阳极金属层)形成。每个二极管38可具有由导电阴极结构诸如阴极层60形成的阴极CD。层60可例如为薄金属层,诸如具有10nm-18nm、大于8nm、小于25nm等厚度的镁银层。层60可覆盖显示器14的有效区域AA中的所有像素22并且可具有延伸到显示器14的无效区域IA的部分(例如,使得层60耦接至向层60提供接地电源电压ELVSS的接地电源路径)。

每个二极管38具有有机发光发射层(有时被称为发射材料或发射层结构),诸如发射层56。发射层56为响应于穿过二极管38的所施加的电流而发光40的电致发光有机层。在彩色显示器中,显示器中的像素阵列中的发射层56包括用于以红色像素发红光的红光发射层,用于以绿色像素发绿光的绿光发射层、和用于以蓝色像素发蓝光的蓝光发射层。除每个二极管38中的发射有机层之外,每个二极管38还可包括用于提高二极管性能的附加层,诸如电子注入层、电子传输层、空穴传输层和空穴注入层。层诸如这些层可由有机材料(例如,层56中的电致发光材料的上表面和下表面上的材料)形成。

层52(有时被称为像素定义层)具有包含层56的发射材料的相应部分的开口阵列。阳极AN在这些开口中的每个开口的底部处形成并且与发射层56重叠。因此,像素定义层52中的二极管开口的形状限定二极管38的发光区域的形状。

像素定义层52可由以光刻方式图案化的感光材料(例如可经处理以形成以光刻方式定义的开口的介电材料,诸如感光聚酰亚胺、感光聚丙烯酸酯等)形成,可由通过荫罩沉积的材料形成,或者可由以其他方式图案化到基板24上的材料形成。如果需要,像素定义层中的二极管开口的壁可为倾斜的,如图4中的倾斜侧壁64所示的。

薄膜电路50可包含晶体管,诸如示例性晶体管32。薄膜晶体管电路诸如图4的示例性薄膜晶体管32可具有由图案化半导体层诸如层70形成的有效区域(沟道区域)。层70可由半导体层诸如多晶硅层或半导体氧化物材料(例如,铟镓锌氧化物)层形成。源极-漏极端子72可接触半导体层70的相对端。栅极76可由图案化栅极金属层或其他导电层形成并且可与半导体70重叠。栅极绝缘体78可被插置在栅极76和半导体层70之间。缓冲层诸如电介质层84可被形成在屏蔽件74下方的基板24上。电介质层诸如电介质层82可覆盖屏蔽件74。电介质层80可被形成在栅极76和源极-漏极端子72之间。层诸如层84、82、78和80可由电介质形成,诸如氧化硅、氮化硅、其他无机介电材料、或其他电介质。附加电介质层诸如有机平面化层PLN1和PLN2可被包括在薄膜晶体管结构诸如晶体管32的结构中并且可有助于使显示器14平面化。

显示器14可具有被嵌入显示器14的电介质层中的多个导电材料层,诸如用于穿过像素22来路由信号的金属层。屏蔽层74可由第一金属层(例如)形成。栅极层76可由第二金属层形成。源极-漏极端子诸如端子72和其他结构诸如信号线86可由第三金属层诸如金属层89的部分形成。金属层89可被形成在电介质层80上并且可覆盖有平面化电介质层PLN1。第四金属层诸如金属层91可用于经由部分88和信号线90来形成二极管。在有效区域AA中,第五金属层诸如阳极金属层58可形成二极管38的阳极AN。每个像素中的第五金属层可具有一部分,诸如耦接至通孔部分88的通孔部分58P,从而使晶体管32的一个源极-漏极端子耦接至二极管38的阳极AN。第六金属层(例如,覆盖膜)诸如阴极金属层60可用于形成发光二极管38的阴极CD。阳极层58可插入金属层91和阴极层60之间。层诸如层58、91、89、76和74可嵌入显示器14的被支撑在基板24上的电介质层内。如果需要,可在显示器14内提供更少的金属层或者显示器14可具有更多的金属层。图4的构型仅为示例性的。

在将功率信号分配给像素22以确保显示器14有效地操作并在显示器14上方生成具有均匀亮度的图像时,使欧姆损耗最小化(有时被称为IR损耗)是期望的。可通过将低电阻信号通路结合到显示器14中来使欧姆损耗最小化。

显示器14的一些层诸如阴极层60可能很薄。阴极层60可由金属诸如镁银形成。为了确保阴极CD足够薄以透明,层60的厚度可为约10nm-18nm(或其他合适的厚度)。在此类型的构型中,层60的薄层电阻可能相对较大(例如,约10欧姆/平方)。为了减小阴极的薄层电阻并由此允许接地电源电压ELVSS以最小IR损耗而被分配到像素22中的二极管38的阴极端子,显示器14可设置有补充导电路径。此类路径可有助于图4的显示器14(或具有其他类型的薄膜堆叠的显示器)容纳具有约束信号分配的几何形状的显示器几何形状(例如,具有圆角的显示器)。

利用一个示例性构型,金属层91的部分可用于形成用作补充ELVSS路径(即,可与由阴极层60形成的ELVSS路径并行操作的信号路径)的信号路径诸如信号路径90,并且由此有助于使操作显示器14时的电压下降和IR损耗最小化。金属层91可沿显示器14的边缘中的一个或多个边缘(例如,沿左边缘、右边缘、下边缘、沿两个或多个边缘、三个或多个边缘等)而被短接到阴极层60,并且可提供尾部24T上的信号ELVSS的源与阴极层60的相应边缘之间的低电阻路径(即,当通过层91中的信号线将信号分配到层60的边缘时可能具有比通过层60本身的薄金属将信号分配到层60的该部分时更小的电阻)。当向层60供电时降低IR损耗有助于减小在有效区域AA中驱动二极管38时的功率损耗。使用层91的一部分来形成用于在显示器14中分配ELVSS的接地电源路径的一部分也可使得减小无效区域IA的宽度。

图5为示出了补充ELVSS电源分配路径(路径90)如何通过用于在有效区域AA中形成阳极AN的相同金属层(金属层58)的一部分而被短接到阴极层60的显示器14的无效区域IA的一部分的横截面侧视图。如图5所示,阴极层60可通过像素定义层52中的开口而被耦接到阳极金属层58。阳极金属层58继而可通过平面化层PLN2中的开口而被短接到形成补充路径90的金属层91的一部分。无效区域IA中的外围信号线诸如信号线86(例如,与栅极线信号相关联的信号线、栅极驱动器电路18的信号和/或显示器14的其他信号)可由路径90下的金属层89的一部分形成。如果需要,电介质层92可覆盖信号线86的部分。信号线86可形成于电介质层80或其他电介质上,该电介质层继而可在薄膜电路和基板结构94上形成(参见,基板24以及图4的电路50的电介质层和金属层)。利用图5的布置,可将ELVSS路径90堆叠在其他信号线诸如信号线86的顶部,这允许将无效区域IA的宽度最小化。

图6为示出了可具有带有开口的网格状的ELVSS路径90如何容纳阳极AN的显示器14的顶视图。可使用如图5所示类型的短接路径来将ELVSS路径90沿显示器14的边缘96短接到阴极60,并且如果需要可使用有效区域AA中的通孔来将其短接到阴极60。当在显示器14中包括补充接地电源路径诸如图6的网格状路径(金属电源网格路径)90时,可减小接地电源信号ELVSS的接地路径的薄层电阻(例如,小于0.1欧姆/平方或其他合适的值)。如果需要,信号ELVSS的补充接地路径90可具有非网格状(例如,路径90可包括垂直线、水平线、L形段、水平和垂直线的组合、稀疏网格、密集网格、网格结构和非网格结构的组合或其他合适的形状)。图6的路径90的网格状仅为示例性的。

如图7所示,显示器14可具有限定用于信号路径的空间量的特征诸如圆角。在这种情况下,路径90的金属条可沿边缘96延伸并且可短接到阴极层60。在拐角98处,可能没有足够的空间形成金属层91的外围条。然而,由于金属层91的网格状部分的存在(即,路径90的网格状部分),对于ELVSS将存在低电阻电路(例如,将与显示器14的下边缘96上的路径90相关联的金属条短接到与显示器14的左边缘和右边缘上的路径90相关联的金属条的路径)。如果需要,显示器14中的ELVDD路径可具有网格状金属迹线(例如,用于形成栅极金属层76、源极-漏极层86、源极-漏极层90、阳极金属层58,和/或可用于形成ELVDD的低电阻网格状正电源分配路径诸如具有由图6的ELVSS迹线所示类型的形状的路径的阴极金属层60)。例如,网格诸如路径90的网格状部分(金属电源网格路径)可用作ELVDD路径。

图8、图9和图10示出了从尾部部分24T到显示器14的下边缘96形成ELVSS和ELVDD分配线的示例性图案。使用此类布置诸如在其中沿尾部24T的中心进行电力线ELVDD和ELVSS布线,可远离显示器14的尺寸约束部分例如拐角98来执行电力布线。

图11、图12、图13、图14、图15、图16和图17示出了显示器14的拐角98处的用于分配正电源电压ELVDD和接地电源电压ELVSS的示例性布置。如图11所示,显示器14的下边缘96可具有水平ELVSS分配路径100H(例如,沿显示器14的下边缘延伸的金属条),并且显示器14的垂直边缘96可具有垂直ELVSS分配路径(例如,沿显示器14的左边缘和右边缘延伸的金属条)诸如路径100V。

路径100H和100V可由金属层89形成。显示器14的拐角98的路径100H和100V之间可能存在间隙(例如,显示器14和基板24可具有限制可用于拐角98的电源分配的空间的圆角)。使用由拐角98的金属层91的部分形成的L形路径和其他导电路径可将路径100H短接到每个路径100V。例如,金属层91可具有被短接到路径100H的部分诸如部分90-1,将路径100V中的金属层91短接到金属层89的连接90-3,以及将部分90-1短接到相应连接点90-3的L形段90-2。可将正电源(ELVDD)路径102H(例如,由平行于沿显示器14的边缘形成ELVSS路径的金属条中的一个金属条延伸的金属条形成的正电源条状路径)直接短接到一些垂直ELVDD分配路径例如垂直线104-1(在层89中形成)。由于拐角98的显示器14的圆形形状,因此断开其他垂直ELVDD分配路径例如垂直线104-2与拐角98的路径102H的连接,但是可使用在路径102H(参见,例如触点90-4)上的触点和将L形路径90-5的金属层91短接到垂直线104的金属层89的触点90-6之间耦接的L形路径部分例如路径90-5进行重新连接。L形路径可用于分配ELVSS,并且L形路径也可用于分配ELVDD(例如,在显示器14中使用网格状ELVDD路径的构型中,在此类构型中金属条诸如路径100H和100V用作ELVDD路径的一部分,和/或在其他构型中)。

图12和图13为分别沿线A’-A和线B’-B截取的图11的显示器14的横截面侧视图。如图12和图13所示,平面化层材料(例如,平面化层PLN1)可将段90-2和段90-5的金属层91与层89中的金属线分开。

在图14的示例性布置中,路径100H和路径102H已由两个金属层(89和91)形成。图15、图16和图17的横截面侧视图(分别对应于沿图14的线A-A’、线B-B’和线C-C’截取的横截面)示出了如何使用平面化层PLN1区分段90-2和段90-5中的上金属层91与下层金属线。如果需要,由段90-2和/或段90-5形成的路径可使用网格状路径实现,如图18所示。

拐角98附近的数据线分配路径由于拐角98的形状可能受到空间限制。拐角98的数据线D可通过使用拐角98的数据线D的阶梯状(阶梯形状)容纳,如图19中的数据线D的阶梯状数据线部分D’所示。在基板24的主要部分和基板24的尾部部分24T之间的过渡,数据线部分D”可沿对角线延伸。

图20为具有多种颜色的像素22的显示器14的一部分(参见,例如红色像素22、绿色像素22G和蓝色像素22B)。在显示器14的此示例性构型中,每个像素具有由层58形成的阳极AN、由覆盖膜形成的空穴注入层(HIL)、第一空穴传输层HTL1(部分公共层)、第二空穴传输层HTL2(所有像素共用覆盖膜)、发射材料EML、公共电子传输层(ETL)、包括覆盖阴极层60的阴极CD和覆盖层CPL(例如,厚度约70nm的调谐层或其他合适厚度)。

图21为显示器14具有诸如图20的像素22R、22G和22B的像素的示例性构型中的显示器14的顶视图。如图21所示,覆盖阴极金属层60可与显示器14的有效区域中的所有像素重叠。层60可由金属诸如镁银或其他合适的金属形成并且可足够薄(例如,10nm-18nm、大于8nm、小于25nm等),以对于由像素中的二极管38发射的光40是透明的。层60可用于向二极管38的阴极CD分配接地电源电压ELVSS。由于层60的厚度相对较小,因此层60可能具有相对较高的薄层电阻(例如,约10欧姆/平方)。为了降低图21的布置中的阴极层的薄层电阻,可将补充阴极路径诸如金属线128(例如,垂直和/或水平线)合并到阴极。线128可使用任何合适的金属沉积技术而被沉积。例如,线128可使用线128的金属从目标消融并且重新沉积到真空室中的阴极层60的暴露表面上的激光沉积系统而被沉积。

图22为沿线120截取并沿方向122观察到的显示器14的横截面侧视图。如图22所示,发光二极管38可具有阳极AN和阴极CD。阴极CD可由覆盖阴极金属层60的一部分形成。补充线128(例如,由网格状图案或其他合适图案形成的水平和/或垂直补充线)可形成于层60上并且被短接到层60,并且因此可减小用于向发光二极管28分配接地电源电压ELVSS的阴极路径的薄层电阻。在一个示例性布置中,层60的厚度D1为约10nm-18nm(例如,大于8nm、小于25nm等),并且线128的厚度D2比厚度D1大10倍(例如,D2可为D1的5倍或更大,可为D1的20倍或更小等)。

图23和图24示出了如何使用激光沉积系统来将金属线128沉积到金属层60。如图23所示,目标诸如目标130可在阴极金属层60已被沉积在显示器14的表面上之后相邻于显示器14的表面而被放置。目标130可包括透明基板(例如玻璃)诸如透明基板134、热吸收材料层诸如层136、以及高导电材料层诸如层138。热吸收层136可由低反射率金属(例如,钼、钨等)或在激光132发射激光束140时吸收激光束140的其他合适的材料形成。激光束140可包括紫外光、可见光和/或红外光,并且可具有1微米-1.2微米、超过1微米、小于5微米、或其他合适尺寸的直径。激光束140可为脉冲激光束(例如,具有1fs至100ps或大于100ps的脉冲宽度的光束),以促进对热吸收层136的照亮部分的加热。层138可由高导电金属诸如铝、锌、镁、银等形成。也可在基板134上由超过两层金属或仅单层金属形成的构型中使用。

如图24所示,当激光132将激光140施加到目标130时,层138和层136的部分138’和部分136’被加热,并且部分138’和部分136’被消融或以其他方式从目标130中去除并且重新被沉积在显示器14中的层60的相邻部分上。部分138’和部分136’的沉积金属形成导电线128,以帮助减小用于将接地电压ELVSS分配到二极管38的导电结构(即阴极层)的薄层电阻。

图25、图26、图27和图28为示出了可用于补充阴极线128(例如,激光沉积金属线)的示例性图案的显示器14的顶视图。线128可具有均匀的竖直或水平布局(参见,例如图25的示例性竖直线128),可具有不均匀的竖直或水平布局(参见,例如图25的示例性竖直线128),或可具有均匀(图27)或不均匀(图28)的网格形状。如果需要,其他图案或这些图案的组合可用于形成线128,并且可与由金属层91(例如,图6的路径90)形成的阴极结构组合使用。图25、图26、图27和图28的构型仅为示例性的。

图29为示出了可具有电路的区域的栅极驱动器电路18如何将水平控制信号(栅极信号)驱动到显示器14的水平栅极线G的图示。如图29所示,例如栅极驱动器电路18可具有使用路径158互连的栅极驱动器电路诸如栅极驱动器行块150的块。每个栅极驱动器行块150可包括电路诸如输出缓冲器和其他输出驱动器电路152、寄存器电路154(例如,可通过路径158链接在一起以形成移位寄存器)和路径156(例如,信号线、电力线和其他线互连)。每个栅极驱动器行块150可向显示器14的有效区域中的像素阵列的像素的相应行中的一个或多个相应栅极线提供一个或多个栅极信号。

图30示出了栅极驱动器行块150可如何横向偏移(例如,通过提供具有沿与栅极线G沿其延伸的水平轴平行的维度的变化的水平偏移DX的块150)和/或可如何旋转到不同角取向(例如,通过旋转块150使得它们具有变化角度偏移DA的角取向)以容纳显示器基板24的曲边98。具有横向变化栅极驱动器行块位置和/或角变化栅极驱动器行块取向的栅极驱动器电路可包括针对每个块150的唯一横向位置和/或角取向,或者可使用一组两个或多个不同的横向位置和/或角取向来増强栅极驱动器电路18容纳弯曲显示器基板边缘的能力。控制信号(例如,时钟信号和其他定时信号)可使用栅极驱动器电路控制线诸如沿基板24的尾部部分24T延伸的线18L而被提供给栅极驱动器电路。

如图31所示,数据线D可具有用于帮助将数据信号分配到位于显示器基板24的弯曲拐角98处的竖直数据线D而无需消耗过多的无效边界区域的L形数据线延伸部诸如延伸部170。延伸部170可形成于显示器14的有效区域中。如图31所示,例如,尾部24L上的数据线D可包括对角线数据线段诸如段164和段166。段164和段166可由金属的同一层形成或可由两个或多个不同的金属层图案化。例如,交替对角线段诸如段164和段166可由相应的第一栅极金属层和第二栅极金属层形成,以増强封装密度。数据线部分164和166可使用通孔162而被耦接到垂直数据线部分诸如在金属层诸如第二源极-漏极金属层91中形成的线D。像素22可包括通孔诸如示例性通孔160,以将由金属层91(即,图31的D(金属层91))形成的数据线连接到由金属层89形成的像素22中的内部路径(即,像素22中的晶体管的源极和漏极)。由金属层89形成的电力线可与数据线D(金属层91)交织。L形延伸部170可由金属层91形成并且可与显示器14的有效区域的拐角重叠,以便不会沿显示器14的基板的边缘而侵入无效区域。

图32为示出了可在不同行中具有不同形状的显示驱动器电路诸如栅极驱动器行块150如何容纳弯曲显示器基板边缘诸如拐角98的基板24的弯曲部分的图示。如图32所示,例如,块150为具有不同纵横比(即,垂直维度除以每个块150的水平维度可能会有所不同)的各种形状的矩形块。例如,块150中的一些块可具有相对较小的纵横比(参见,例如块具有小的高度A1和大的宽度B1),而其他块150可具有相对较大的纵横比(参见,例如块具有中等高度A2和中等宽度B2)。块150中的电路152,154和158可被布置成容纳每个块150或每组块150的定制器件封装(从上方观察时的轮廓)。通常,框150的任何合适类型的定制可围绕弯曲显示边缘诸如拐角98实现(例如,形状定制、横向偏移定制、角取向定制、尺寸定制、电路组件定制等)。块150可各自被定制或块集可被定制,以容纳弯曲显示器基板边缘。

测试电路可在显示器14上实现。例如,测试多路复用器电路诸如图33的测试多路复用器电路176可沿显示器14的上边缘或下边缘而被提供。电路176可用于将相对较少的测试信号路由到相对较多的数据线,以便于在制造期间进行像素测试。在测试期间,可选择性地操作开关SW,以向显示器14中的数据线D提供测试数据。例如,可打开和关闭电路176的开关SW,以将红色数据线D(R)诸如TESTDATARED的测试数据路由到红色数据线D(R),将绿色数据线D(G)诸如TESTDATAGREEN的测试数据路由到绿色数据线D(G),以及将蓝色数据线D(B)诸如TESTDATABLUE的测试数据路由到蓝色数据线D(B)。线D(R)可用于将数据路由到红色像素,线D(G)可与绿色像素相关联,并且线D(B)可被耦接到显示器14的蓝色像素。

测试数据可从被耦接到基板24上的测试点的测试仪和/或从附接到基板24的电路提供给显示器14。当需要在将显示驱动器集成电路附接到基板24之前执行测试时可使用外部测试仪方案。测试线可在测试点和测试电路诸如电路176之间路由信号(例如,TESTDATARED、TESTDATAGREEN、TESTDATABLUE和开关SW中的红色开关、绿色开关和蓝色开关的三个相应多路复用器控制信号)。电路176可由外部测试电路或其他控制器控制,使得不同颜色的数据线能以期望的模式来接收测试数据。这允许独立测试显示器14中的不同颜色的像素22。在测试完成时,开关SW可永久打开,使得显示器14中的数据线D不会一起被短接,并且通常可用于将数据信号路由到像素22。

图34为具有测试电路的示例性显示器的图示。如图34所示,测试多路复用器电路176和测试点174可位于显示器14的相对边缘上。例如,测试点174可位于显示器14的下边缘处的基板24的尾部部分24L上,并且测试多路复用器电路176可沿显示器14的上边缘而被定位。测试信号线172可用于将显示器14的下边缘上的测试点174之间的测试信号路由到沿显示器14的上边缘的测试多路复用器电路176。

如图35的示例性构型所示,测试多路复用器电路176可沿与测试点174相邻的基板24的尾部部分24T的下边缘而被定位。在测试之后,可从尾部24T去除测试多路复用电路176和测试点174(例如,通过使用沿图35的切割线180在尾部24T中形成的切割来切断电路176和测试点174)。

图36和图37示出了如何沿显示器14的弯曲部分来容纳多路复用器测试电路176。在图36的示例性布置中,电路176形成于沿栅极驱动器电路18的块150与数据线D之间的显示器14的有效区域的曲边的弯曲锥形区域内。图37示出了其中测试多路复用器电路176诸如测试多路复用器电路块176B的区域与栅极驱动器电路18诸如栅极驱动器行块150的区域交织的示例性构型。通过将块176B放置在块150的相应对之间,栅极驱动器电路18和测试多路复用器电路176可沿有效区域的边缘而被有效封装。这有助于使沿在其中形成显示驱动器电路18和测试多路复用器电路176的基板24的边缘的无效区域的宽度最小化。如结合图30的栅极驱动器电路18所述,测试多路复用器电路块176B可具有不同的与位置有关的形状(例如,不同尺寸,纵横比等)、角取向、和/或沿与栅极线G平行的尺寸的横向位置,帮助増强显示器14的无效区域中的电路的布局。如果需要,可使用测试多路复用器电路176的区域位于栅极驱动器电路18的区域之间的其他布置或以其他方式布置,以帮助容纳弯曲显示器基板边缘。图37的构型为示例性的。

根据实施方案,提供了一种具有带有像素阵列的有效区域的有机发光二极管显示器,该有机发光二极管显示器包括:基板;位于基板上的包括电介质层的薄膜晶体管电路;位于薄膜晶体管电路上的像素定义层,该像素定义层具有开口,该开口中的每个开口包含有机发光二极管的有机发射层并且该开口中的每个开口与像素中的相应一个像素相关联;覆盖像素阵列的阴极层;和嵌入有效区域中的电介质层内的金属接地电源路径,该金属接地电源路径将接地电源电压承载到阴极层。

根据另一个实施方案,该金属接地电源路径由金属层的第一部分形成,并且金属层的第二部分形成接触薄膜晶体管电路中的晶体管的源极-漏极端子的通孔结构。

根据另一个实施方案,该金属接地电源路径或正电源路径具有网格形状。

根据另一个实施方案,该有效区域具有圆角,并且该金属接地电源路径或正电源路径形成具有圆角的网格。

根据另一个实施方案,该金属接地电源路径或正电源路径包括L形部分。

根据另一个实施方案,该有机发光二极管显示器包括嵌入电介质层中的第一图案化金属层和第二图案化金属层,该金属接地电源路径包括由包括由第二图案化金属层形成的金属段,并且第一图案化金属层包括承载接地电源电压的金属条。

根据另一个实施方案,该显示器具有边缘并且金属条沿边缘中的至少一些边缘延伸。

根据另一个实施方案,第一图案化金属层包括平行于承载接地电源电压的金属条中的一个金属条延伸的正电源金属条。

根据另一个实施方案,该金属段包括L形部分,并且L形部分中的至少一些L形部分跨过正电源金属条。

根据另一个实施方案,该有机发光二极管显示器包括从正电源金属条延伸到跨越有效区域的像素的正电源分配路径。

根据另一个实施方案,该有效区域具有圆角,并且L形部分位于该圆角处。

根据另一个实施方案,薄膜晶体管电路中的晶体管的源极-漏极端子由嵌入电介质层中的第一金属层形成,并且金属接地电源路径由嵌入电介质层中的第二金属层形成。

根据另一个实施方案,有机发光二极管的阳极由嵌入电介质层中并且被插置在第二金属层和阴极层之间的第三金属层形成。

根据另一个实施方案,第三金属层的一部分将由第二金属层形成的金属接地电源路径短接到阴极层。

根据另一个实施方案,该金属接地电源路径包括激光沉积金属线。

根据另一个实施方案,该有机发光二极管层包括向像素提供数据的数据线,该数据线包括阶梯状部分。

根据实施方案,提供了一种具有像素阵列的有机发光二极管显示器,该有机发光二极管显示器包括:基板;位于基板上的薄膜晶体管电路层;位于薄膜晶体管电路层上的像素定义层,该像素定义层具有开口,该开口中的每个开口包含有机发光二极管的有机发射层并且该开口中的每个开口与像素中的相应一个像素相关联;覆盖像素阵列并将接地电源电压分配到开口中的每个开口中的有机发光二极管的阴极层;以及短接到阴极层并且有助于分配接地电源电压的图案化金属网格。

根据另一个实施方案,该图案化金属网格包括位于阴极层上的激光沉积金属线。

根据另一个实施方案,该阴极层由金属的第一层形成,图案化金属网格由金属的第二层形成,并且有机发光二极管的阳极由插置在第一金属层和第二金属层之间的第三金属层形成。

根据另一个实施方案,该有机发光二极管显示器包括位于阴极层上的激光沉积金属线。

根据另一个实施方案,该基板具有圆角。

根据另一个实施方案,该有机发光二极管显示器包括向像素分配数据信号的数据线,该数据线包括具有阶梯形状的部分。

根据实施方案,提供了一种具有像素阵列的有机发光二极管显示器,该有机发光二极管显示器包括:基板;具有位于基板上的电介质层的薄膜晶体管电路层;位于薄膜晶体管电路层上的像素定义层,该像素定义层具有开口,该开口中的每个开口包含有机发光二极管的有机发射层并且该开口中的每个开口与像素中的相应一个像素相关联;和覆盖像素阵列的阴极层,该阴极层接收接地电源电压并且将接地电源电压分配开口中的有机发射层;嵌入电介质层中的形成薄膜晶体管电路层中的薄膜晶体管的源极-漏极端子的第一金属层;嵌入电介质层中的被图案化以将接地电源电压承载到阴极层的第二金属层;以及具有被图案化以形成有机发光二极管的阳极的第一部分和将第二金属层短接到阴极层的第二部分的第三金属层。

根据另一个实施方案,该基板具有曲边。

根据另一个实施方案,该有机发光二极管显示器包括:将数据传送到像素阵列的数据线;垂直于数据线延伸的栅极线;以及由薄膜晶体管电路形成的栅极驱动器电路,该栅极驱动器电路具有各自被耦接到栅极线中的至少相应一个栅极线的栅极驱动器行块。

根据另一个实施方案,该栅极驱动器行块包括不同纵横比的栅极驱动器行块。

根据另一个实施方案,有机发光二极管显示器包括测试多路复用器电路,该测试多路复用器电路包括介于栅极驱动器行块的相应对之间的测试复用器电路块。

根据实施方案,提供了一种有机发光二极管显示器,该有机发光二极管显示器包括:薄膜晶体管电路;具有带有由薄膜晶体管电路的一部分形成的像素阵列的有效区域并且具有没有像素并沿有效区域的与基板的边缘相邻的边缘延伸的无效区域的基板;向像素阵列提供数据的数据线;垂直于数据线延伸并向像素阵列提供控制信号的棚极线;以及无效区域中的由薄膜晶体管电路的一部分形成的棚极驱动器电路,该栅极驱动器电路沿基板的边缘的弯曲部分延伸。

根据另一个实施方案,该栅极驱动器电路具有多个栅极驱动器行块,该多个栅极驱动器行块中的每个栅极驱动器行块被耦接到像素阵列的相应像素行中的栅极线中的至少一个栅极线。

根据另一个实施方案,该栅极驱动器行块包括在像素的相应第一行和第二行中的具有不同形状的第一栅极驱动器行块和第二栅极驱动器行块。

根据另一个实施方案,该栅极驱动器行块包括在像素的相应第一行和第二行中具有不同角取向的第一栅极驱动器行块和第二栅极驱动器行块。

根据另一个实施方案,该栅极驱动器行块包括像素的不同行中的沿平行于栅极线延伸的维度偏移不同量的栅极驱动器行块,使得栅极驱动器行块容纳基板的边缘的弯曲部分。

根据另一个实施方案,该有机发光二极管显示器包括被耦接到数据线的测试多路复用器电路。

根据另一个实施方案,该测试多路复用器电路沿基板的边缘的弯曲部分的至少部分延伸。

根据另一个实施方案,该测试多路复用器电路包介于括栅极驱动器行块之间的测试电路的区域。

根据另一个实施方案,该数据线包括L形数据线部分。

根据另一个实施方案,该数据线具有垂直于栅极线延伸的数据线部分,并且其中数据线中的一些数据线各自具有对角线部分和将对角线部分耦接到垂直于栅极线延伸的数据线部分的相应一个数据线部分的L形延伸部。

根据实施方案,提供了一种有机发光二极管显示器,该有机发光二极管显示器包括薄膜晶体管电路;具有带有由薄膜晶体管电路的一部分形成的像素阵列的有效区域并且具有没有像素并沿有效区域的与基板的边缘相邻的边缘延伸的无效区域的基板;由无效区域中的薄膜晶体管电路的一部分形成的栅极驱动器电路;从栅极驱动器电路向像素阵列提供控制信号;向像素阵列提供数据的数据线,该数据线具有垂直于栅极线延伸的数据线部分,并且其中数据线中的一些数据线各自具有对角线部分和将对角线部分耦接到垂直于栅极线延伸的数据线部分的相应一个数据线部分的L形延伸部。

根据另一个实施方案,基板的边缘具有弯曲部分,该有机发光二极管显示器包括具有与有效区域重叠的L形段的电源线路。

根据另一个实施方案,该栅极驱动器电路包括多个栅极驱动器行块,该多个栅极驱动器行块中的每个栅极驱动器行块向栅极线的相应一个栅极线提供控制信号中的至少一个控制信号,该栅极驱动器行块包括沿弯曲部分具有不同形状的栅极驱动器行块。

根据另一个实施方案,该栅极驱动器电路包括多个栅极驱动器行块,该多个栅极驱动器行块中的每个栅极驱动器行块向栅极线的相应一个栅极线提供控制信号中的至少一个控制信号,该栅极驱动器行块包括沿弯曲部分具有不同角取向的栅极驱动器行块。

前述内容仅为示例性的并且可对所述实施方案作出各种修改。前述实施方案可单独实施或可以任意组合实施。

- 有机发光二极管显示器的电源和数据路由结构

- 有机发光二极管显示器的电源和数据路由结构