存储器装置的制造方法

文献发布时间:2023-06-19 13:46:35

技术领域

本发明实施例涉及半导体装置,特别是涉及存储器装置的形成方法。

背景技术

半导体集成电路(integrated circuit,IC)工业经历了指数型成长。IC材料与设计的技术进步已产出数代的IC,其中每一代都比上一代具有更小且更复杂的电路。在IC的发展过程,功能密度(即每单位芯片区域互连装置的数量)已大量增加,而几何大小(即可以使用制程产出的最小组件(或线))已缩小。这种微缩化制程一般通过提高生产效率与降低相关成本以提供效益。这种微缩化也增加了IC制程与制造的复杂性。

一些IC设计和制造的进展之一是非易失性存储器(non-volatile memory,NVM)的开发,特别是磁性随机存取存储器(magnetic random-access memory,MRAM)。磁性随机存取存储器(MRAM)具有与易失性静态随机存取存储器(static random-access memory,SRAM)相当的性能,且具有与易失性动态随机存取存储器(dynamic random accessmemory,DRAM)相当的密度但较低的功耗。与非易失性(NVM)快闪存储器想比,磁性随机存取存储器(MRAM)可以提供更快的存取时间且承受较少的经时劣化。一个磁性随机存取存储器(MRAM)单元由一个包括两个铁磁层的磁性穿隧接面(magnetic tunneling junction,MTJ)形成,这两个铁磁层被薄的绝缘障壁分开,且借由电子穿隧过在两个铁磁层间的绝缘障壁运行。在操作中,磁性随机存取存储器(MRAM)单元的可变状态(例如逻辑的“0”或“1”态)通常借由测量磁性穿隧接面(MTJ)的电阻来读取。由于磁性穿隧效应,测量磁性穿隧接面(MTJ)的电阻随着磁极性而变化。当施加偏压在顶金属线(例如位元线)、顶电极导孔、顶电极、测量磁性穿隧接面(MTJ)、底电极、底电极导孔以及底金属线(例如字元线)的组合结构时,我们可以得到组合结构的串联电阻,当测量到流经其中的电流。串联电阻包括测量磁性穿隧接面(MTJ)的电阻与附加的电阻。为了提高磁性随机存取存储器(MRAM)单元的灵敏度与速度,附加的电阻应该被减少或维持在尽可能低的理想值。尽管现有形成磁性随机存取存储器(MRAM)单元的方法已经大致能满足其预期目的,但并非在所有方面都令人满意。举例而言,高电阻的底电极导孔(bottom electrode via,BEVA),通常是磁性随机存取存储器(MRAM)单元中附加电阻的主要贡献,而降低了存储器电路的性能。因此,需要对本领域进行改进。

发明内容

本发明实施例提供一种制造存储器装置的方法,包括:形成导孔沟槽在基板中;形成导孔在导孔沟槽中,其中导孔的下部包括第一金属,且导孔的上部包括不同于第一金属的第二金属;形成磁性穿隧接面在导孔上方;以及形成上电极在磁性穿隧接面上方。

本发明实施例提供一种制造存储器装置的方法,包括:提供基板;形成导孔沟槽基板中;沉积第一金属于导孔沟槽的下部中;沉积第二金属于导孔沟槽的上部中,从而于导孔沟槽中形成导孔,其中第二金属具有比第一金属更高的电阻率;形成下电极层于导孔上方;形成磁性穿隧接面堆叠于下电极层上方,其中磁性穿隧接面包括:下铁磁层;穿隧阻障层,于下铁磁层上方;以及上铁磁层,于穿隧阻障层上方;以及形成上电极层于磁性穿隧接面堆叠层上方。

本发明实施例提供一种存储器装置,包括:下电极导孔,其包括下部和上部,其中下部包括第一金属,上部包括不同于第一金属的第二金属;下电极,设置于下电极导孔上方;磁性穿隧接面,设置于下电极上方;以及上部电极,设置于磁性穿隧接面上方。

附图说明

以下将配合所附图式详述本发明实施例。应注意的是,依据在业界的标准做法,各种特征并未按照比例绘制且仅用以说明例示。事实上,可任意地放大或缩小单元的尺寸,以清楚地表现出本发明实施例的特征。

图1A及图1B绘示出磁性随机存取存储器单元内的磁性穿隧接面的透视图。

图1C是根据本发明的一些实施例,绘示出磁性随机存取存储器阵列。

图2A及图2B是根据本发明的一些实施例,绘示出磁性随机存取存储器单元阵列形成方法的流程图。

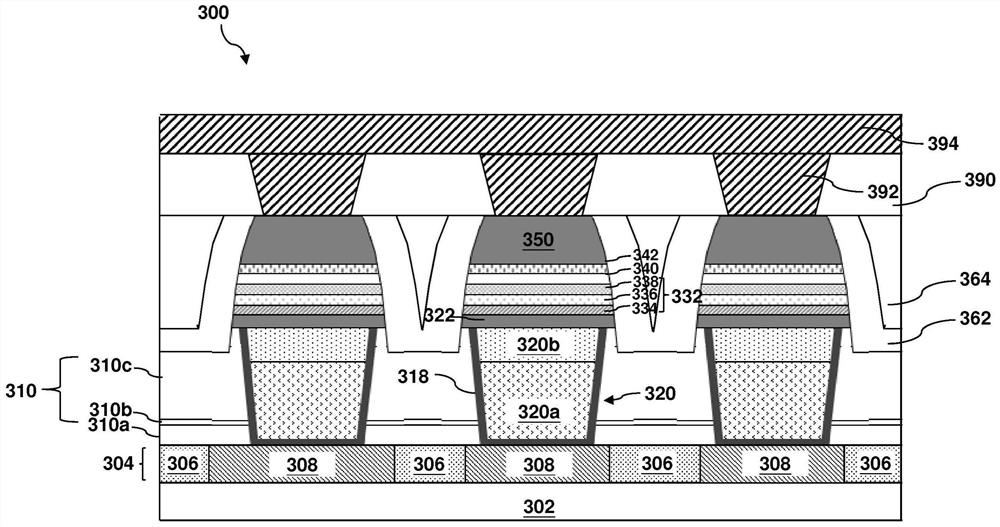

图3至图18是根据本发明的一些实施例,依据图2A及图2B的方法绘示出制造过程中半导体结构的截面图。

其中,附图标记说明如下:

100:磁性穿隧接面

102:上铁磁板

104:下铁磁板

106:绝缘层

112A,112B,114A,114B:磁场方向

120:磁性随机存取存储器单元阵列

200:方法

202,204,206,208,210,212,214,216,218,220,222,224,226:操作

300:装置结构

302:基板

304:互连结构

306,390:金属间介电质层

308,394:金属线

310,364:介电层

310a:碳氮化硅层

310b:氧化铝层

310c:未掺杂氧化硅玻璃层

310d:覆盖层

312:遮罩

314:蚀刻制程

316:导孔沟槽

318:扩散阻障层

320,320a,320b:底电极导孔材料

321:虚线

322:底电极层

330:磁性穿隧接面堆叠

332:下铁磁电极层

334:底钉扎铁磁层

336:金属层

338:顶钉扎铁磁层

340:穿隧阻障层

342:上铁磁电极层

350:顶电极层

354:顶表面

356:虚线圆

360:硬遮罩层

362:侧壁间隔物

370:阻抗层

372:底部抗反射涂层

374:光敏层

392:顶电极导孔

H1:高度

H2:厚度

H3,H4:距离

BL

WL

具体实施方式

以下公开提供了许多的实施例或范例,用于实施所提供的标的物的不同元件。各元件和其配置的具体范例描述如下,以简化本发明实施例的说明。当然,这些仅仅是范例,并非用以限定本发明实施例。举例而言,叙述中若提及第一元件形成在第二元件之上,可能包含第一和第二元件直接接触的实施例,也可能包含额外的元件形成在第一和第二元件之间,使得它们不直接接触的实施例。此外,本发明实施例可能在各种范例中重复参考数值以及/或字母。如此重复是为了简明和清楚的目的,而非用以表示所讨论的不同实施例及/或配置之间的关系。

再者,其中可能用到与空间相对用词,例如“在……之下”、“下方”、“较低的”、“上方”、“较高的”等类似用词,是为了便于描述图式中一个(些)部件或特征与另一个(些)部件或特征之间的关系。空间相对用词用以包括使用中或操作中的装置的不同方位,以及图式中所描述的方位。当装置被转向不同方位时(旋转90度或其他方位),其中所使用的空间相对形容词也将依转向后的方位来解释。

本公开大致上涉及半导体装置和制造方法。本公开的一些面向涉及磁性随机存取存储器(MRAM)单元。更具体地,本公开涉及提供一种具有底电极导孔(BEVA)的磁性随机存取存储器(MRAM)单元,这底电极导孔包括至少两种不同的金属(例如铜和钨),减少了通过磁性随机存取存储器(MRAM)单元的电流路径中的附加电阻。借由具有低电阻的电流路径,磁性随机存取存储器(MRAM)单元的灵敏度和速度得以提升。

图1A及图1B绘示出磁性随机存取存储器(MRAM)单元内的磁性穿隧接面(MTJ)100的透视图。测量磁性穿隧接面(MTJ)100包括由薄的绝缘层106(也称为隧道阻障层)隔开的上铁磁板102和下铁磁板104。两个铁磁板中的一个(例如下铁磁板104)是钉扎在反铁磁层上的磁性层,而另一个铁磁板(例如上铁磁板102)是“自由”磁层,可以将其磁场改变为两个或多个值之一以存储两个或多个相应数据态之一。

测量磁性穿隧接面(MTJ)100使用穿隧式磁阻(tunnel magnetoresistance,TMR)以存储上铁磁板102与下铁磁板104的磁场。对于足够薄的绝缘层106厚度(例如约

测量磁性穿隧接面(MTJ)100的电阻根据存储在上和下铁磁板102和104中的磁场变化,由于磁穿隧效应。举例而言,在图1A中,上和下铁磁板102和104的磁场是对准的(例如箭头112A及114A),造成低电阻态(即逻辑“0”态)。在图1B中,电流经过测量磁性穿隧接面(MTJ)100以感应磁性自由层(例如上铁磁板102)的磁场的变化。因此,在这数据写入操作之后,上下铁磁板102和104中的磁场彼此相反(例如箭头112B和114B),这造成高电阻态(即逻辑“1”态)。因此,通过测量上下铁磁板102和104之间的电阻,耦合到测量磁性穿隧接面(MTJ)100的读取电路可以识别“0”和“1”的数据状态。

图1C绘示出磁性随机存取存储器(MRAM)单元阵列120,其包括磁性随机存取存储器(MRAM)单元的M行(row)(字元)和N列(column)(位元)。每个磁性随机存取存储器(MRAM)单元包括一个测量磁性穿隧接面(MTJ)100。字元线WL

图2A及图2B根据一个实施例,绘示出用于形成磁性随机存取存储器单元阵列的方法200的流程图。方法200为示例,且不意图将本公开作出除了权利要求中明确记载范围之外的限制。在方法200之前、期间以及/或之后,可提供额外的步骤。一些所述操作在另外的实施例中可被替换、删去或移动。半导体装置结构可增加额外部件。一些所述部件在不同实施例中可被替换或删去。尽管所讨论的一些实施例以特定顺序的步骤执行,这些步骤仍可以另一合乎逻辑的顺序执行。下面结合图3至图18描述方法200,根据方法200,这些图绘示出在制造步骤期间,一部分磁性随机存取存储器(MRAM)单元阵列的各种截面图。

在操作202,方法200(图2A)提供或配备有具有基板302的装置结构300,例如图3所示。在此实施例中,基板302是硅基板。或者,基板302可以包括另一种元素半导体,例如锗,一种化合物半导体,包括碳化硅、氮化镓、砷化镓、磷化镓、磷化铟、砷化铟和锑化铟,一种合金半导体,包括硅锗、磷砷化镓、磷化铝铟、砷化铝镓、砷化镓铟、磷化镓铟和砷磷化镓铟;或其组合。在另一个实施例中,基板302包括铟锡氧化物(indium tin oxide,ITO)玻璃。在各种实施例中,基板302是晶圆,例如硅晶圆,且可以在其上部中包括一个或多个外延生长的半导体层。

在基板302表面上设置有互连结构304。互连结构304包括金属间介电质(inter-metal dielectric,IMD)层306和在金属间介电质(IMD)层306中水平延伸的金属线308。金属间介电质(IMD)层306可以是氧化物,例如二氧化硅,低k介电材料,例如碳掺杂的氧化物,或极低k介电材料,例如多孔碳掺杂的二氧化硅。金属线308可以由金属制成,例如铝(Al)、铜(Cu)或其组合。

在操作204,方法200(图2A)在互连结构304上方沉积介电层310,如图4所示。在示例性的实施例中,介电层310的形式为堆叠子层,举例而言,碳氮化硅(SiCN)层310a、氧化铝(AlO

在形成介电层310之后,然后在介电层310上形成遮罩312,例如光阻遮罩。然后在备妥遮罩312的情况下执行蚀刻制程314以图案化介电层310。蚀刻制程314可以使用适合的干蚀刻操作。在一些实施例中,干蚀刻包括采用含氟气体的反应式离子蚀刻(reactive ionetch,RIE)。在一些实施例中,干蚀刻操作可以是任何合适的介电质蚀刻,以在常规互补金属氧化物半导体(CMOS)技术的金属化结构中形成导孔沟槽316。导孔沟槽316暴露金属线308的一部分。遮罩312可以在蚀刻之后移除。

在操作206,方法200(图2A)形成扩散阻障层318,此扩散阻挡层318覆盖在导孔沟槽316的侧壁和底部上方以及介电层310上方。扩散阻挡层318可以包括导电材料,例如钛(Ti)、氮化钛(TiN)、钽(Ta)、氮化钽(TaN)、钴(Co)或一种或多种的前述组合。扩散阻障层318可以通过制程例如原子层沉积(atomic layer deposition,ALD)、化学气相沉积(CVD)、物理气相沉积(PVD)或其他合适的方法来沉积。举例而言,扩散阻障层318可以包括三个子层,且通过物理气相沉积(PVD)依次沉积钽层(例如大约

在操作208,方法200(图2A)在导孔沟槽316中与在扩散阻挡层318上方进行底电极导孔材料320b的第二沉积如图6所示。底电极导孔材料320b包括与底电极材料320a不同的金属。第二沉积的底电极导孔材料320b可以通过多种技术形成,例如高密度离子化金属等离子体(IMP)沉积、高密度感应耦合等离子体(ICP)沉积、溅射、化学气相沉积(CVD)、物理气相沉积(PVD)、低压化学气相沉积(LP-CVD)、等离子体化学气相沉积(PE-CVD)等。在此示例性的实施例中,底电极导孔材料320b为钨(W),且在镶嵌操作后接着平坦化制程例如化学机械研磨(chemical mechanical polishing,CMP)、蚀刻操作或其组合,以移除过多的导电材料。平坦化制程也从导孔沟槽316外部的位置移除了扩散阻障层318,而暴露出介电层310的顶表面。介电层310顶部中的覆盖层310d也可以平坦化制程移除。平坦化制程之后所得的结构在图7中示出。如果导孔沟槽316的开口宽于预定值,则由于平坦化制程,在第二道沉积的底电极导孔材料320b中可能出现凹陷效应。如果发生凹陷效应,第7图中的虚线321代表第二沉积的底电极导孔材料320b的替代顶表面。第二沉积的底电极导孔材料320b的厚度H2,在其最薄的位置(例如虚线321的最底点)测量。

第一沉积的底电极导孔材料320a和第二沉积的底电极导孔材料320b共同定义了底电极导孔320。换句话说,底电极导孔320包括填充有第一导电材料320a的下部和填充有不同于第一导电材料320a的第二导电材料320b的上部。如上所述,在此示例性的实施例中,第一导电材料320a为铜(Cu),第二导电材料320b为钨(W)。值得注意的是,第二导电材料320b作为覆盖层,以阻止铜(Cu)扩散到随后将形成的磁性穿隧接面(MTJ)堆叠的上层。铜(Cu)扩散到测量磁性穿隧接面(MTJ)堆叠对磁性随机存取存储器(MRAM)单元的操作有害。因此,在各种实施例中,导电材料320b的厚度H2具有约

在一些实施例中,通过使铜(Cu)作为底电极导孔的主要部分而不会引起铜(Cu)扩散到测量磁性穿隧接面(MTJ)堆叠中,可以将底电极导孔的电阻降低约60%至约90%。因此,通过磁性随机存取存储器(MRAM)单元的电流路径中的总串联电阻也减少了。此外,降低串联电阻的方法很容易与后段制程(back-end-of-line,BEOL)流程兼容,而在受控的制造成本提供更好的磁性随机存取存储器(MRAM)操作。

在操作210,方法200(图2A)在介电层310上方形成底电极层322,且与底电极导孔320接触,如图8所示。底电极层322可以是导电材料,例如TiN、TaN、Ti、Ta或前述中的一种或多种的组合。底电极层320可以通过例如原子层沉积(ALD)、化学气相沉积(CVD)、物理气相沉积(PVD)或其他合适方法的制程来沉积。举例来说,底电极层320可以通过物理气相沉积(PVD)制程中沉积TiN,在高于摄氏300度的温度下形成。底电极层322的顶表面在沉积之后可以具有非平面的顶表面,且此后可以在一个或多个化学机械研磨(CMP)制程中被平坦化。在一些实施例中,底电极层322具有约

在操作212,方法200(图2A)在底电极层322的上表面上方形成磁性穿隧接面(MTJ)堆叠330,例如图9所示。在此示例性的实施例中,测量磁性穿隧接面(MTJ)堆叠330包括下铁磁电极层332(可以具有固定的磁场方向)和上铁磁电极层342(可以具有自由的磁场方向)。穿隧阻障层340设置在下铁磁电极层332和上铁磁电极层342之间。下铁磁电极层332可以是合成反铁磁(synthetic anti-ferromagnetic,SAF)结构,其包括底钉扎铁磁层334,顶钉扎铁磁层338以及夹在底钉扎铁磁层334和顶钉扎铁磁层338之间的金属层336。磁性穿隧接面(MTJ)堆叠330的每一层通过适当的层成长技术设置。一些层成长技术包括溅镀沉积、分子束外延(molecular beam epitaxy,MBE)、脉冲雷射溅镀(pulsed laser deposition,PLD)、原子层沉积(ALD)、电子束(electron beam,e-beam)外延、化学气相沉积(CVD)或类似的化学气相沉积(CVD)制程还包括低压化学气相沉积(LP-CVD)、原子层化学气相沉积(atomiclayer CVD,AL-CVD)、超高真空化学气相沉积(ultrahigh vacuum CVD,UHV-CVD)、减压化学气相沉积(reduced pressure CVD,RP-CVD)或其任意组合。

在一些实施例中,上铁磁电极层342包括Fe、Co、Ni、FeCo、CoNi、CoFeB、FeB、FePt、FePd等,且具有在约

在操作214,方法200(图2B)在磁性穿隧接面(MTJ)堆叠330的上表面上形成顶电极层350,如图10所示。顶电极层350可以是导电材料,例如TiN、TaN、Ti、Ta或前述中一种或多种的组合。顶电极层350可以通过例如原子层沉积(ALD)、化学气相沉积(CVD)、物理气相沉积(PVD)或其他合适方法的制程来沉积。举例而言,顶部电极层350可以通过物理气相沉积(PVD)制程沉积TiN在高于摄氏300度的温度下形成。顶电极层350的顶表面在沉积之后可以具有非平面的顶表面,且此后可以在一个或多个化学机械研磨(CMP)制程中被平坦化。在一些实施例中,底电极层322和顶电极层350在底电极层322中包括不同的导电材料,例如Ta、TaN或Ta和TaN的组合,而在顶电极层350中包括TiN。在一些实施例中,顶电极层350具有约

在操作216,方法200(图2B)在顶电极层350上方形成硬遮罩层360,例如图11所示。硬遮罩层360可以包括一个或多个图案化层。在一些实施例中,硬遮罩层360包括介电材料,例如氧化硅、氮化硅、氮氧化硅、非晶碳(amorphous carbon,APF)或其合适的组合。硬遮罩层360可以通过例如化学气相沉积(CVD)或其他合适方法的制程沉积。操作216进一步包括通过微影和蚀刻制程来图案化硬遮罩层360,例如在图12和图13中所示。微影和蚀刻制程可以首先在硬遮罩层360上方形成并图案化阻抗层370,然后使用图案化的阻抗层370作为蚀刻遮罩来对硬遮罩层360进行图案化。在此示例性的实施例中,阻抗层370可以包括两层或更多层,例如底部抗反射涂层(BARC)层372和光敏层374。示例性的微影制程可以包括对光敏层374所选区域暴露于辐射,执行微影曝光。曝光导致在光阻的曝光区域中发生化学反应。曝光后,将显影剂加在光阻上。在正光阻显影制程的情况下,显影剂溶解或以其他方式移除曝光区域,在负光阻显影制程的情况下,显影剂溶解或以其他方式移除未曝光区域。合适的正显影剂包括四甲基氢氧化铵(TMAH)、氢氧化钾(KOH)和氢氧化钠(NaOH),合适的负性显影剂包括溶剂,例如乙酸丁酯、乙醇、己烷、苯和甲苯。在显影光阻之后,通过选择性地蚀穿显影的光敏层374中的开口,将在光敏层374中形成的图案转移到底部抗反射(BARC)层372,而形成图案化的阻抗层370。随后,如图13所示,硬遮罩层360的暴露部分可以通过例如湿蚀刻、干蚀刻、反应式离子蚀刻(RIE)、等离子体清洗及/或其他蚀刻方法的蚀刻制程376移除,以形成图案化的硬遮罩层360。从俯视图看,图案化的硬遮罩层360可以具有圆形的柱状形式。图案化的硬遮罩层360的形状将通过本文后续实施例中公开的图案化方法转移到顶电极层350和下面的磁性穿隧接面(MTJ)堆叠330。在图案化硬掩模层360之后,可以移除阻抗层370。

在操作218,方法200(图2B)使用图案化的硬遮罩层360作为蚀刻遮罩来蚀刻顶电极层350,如图13所示。操作218可以使用干蚀刻、湿蚀刻或其他合适的蚀刻制程。举例来说,干蚀刻制程可以实施含氧气体、含氟气体(例如CF4、SF6、CH

在操作220,方法200(图2B)以图案化的顶电极层350作为蚀刻遮罩来蚀刻磁性穿隧接面(MTJ)堆叠330和底电极层322,如图14所示。操作220包括蚀刻制程以蚀穿磁性穿隧接面(MTJ)堆叠330和底电极层322。在一实施例中,蚀刻制程是等向性干蚀刻制程。在一些实施例中,蚀刻制程首先将在顶电极层350中定义的图案例如柱阵列(例如圆柱形图案)转移到磁性穿隧接面(MTJ)堆叠330中,然后使用图案化顶电极层350和图案化的磁性穿隧接面(MTJ)堆叠330一起作为蚀刻遮罩移除部分的底电极层322。在一些实施例中,蚀刻制程蚀刻磁性穿隧接面(MTJ)堆叠330和下电极层322没有中间蚀刻步骤。在一些实施例中,操作218中的蚀刻制程和操作220中的蚀刻制程是一个蚀刻步骤,无需中间蚀刻步骤就蚀刻顶电极层350、磁性穿隧接面(MTJ)堆叠330和底电极层322。在图案化顶电极层350、磁性穿隧接面(MTJ)堆叠330和底电极层320之后,为了简单描述,将图案化的顶电极层350表示为顶电极350,图案化的磁性穿隧接面(MTJ)堆叠330表示为磁性穿隧接面(MTJ)330,图案化的下电极层322表示为下电极322。

在一些实施例中,蚀刻制程包括在预定时间中使用湿蚀刻剂或等离子体蚀刻剂。在一些实施例中,操作220使用端点控制方法来精确地控制蚀刻时间。端点控制可在蚀刻过程中即时分析发射的残留物,例如通过使用光放射光谱仪(optical emissionspectroscopy,OES)检查等离子体蚀刻制程中等离子体所发射的光谱。当来自底电极322的材料成分减少时,蚀刻制程轻微地过度蚀刻到介电层310的顶部,使得未掺杂氧化硅玻璃(USG)层310c的顶表面354在底电极322的底表面下方一距离H3。在一示例中,距离H3约为

在操作222,方法200(图2B)形成如图15所示的侧壁间隔物362,此侧壁间隔物362覆盖顶电极350、磁性穿隧接面(MTJ)330和底电极320的侧壁,并覆盖顶电极350与介电层310的顶表面。侧壁间隔物362可包括介电材料,例如氧化硅、氮化硅、氮氧化硅、碳化硅、其他介电材料或其组合,且可包括一层或多层材料。侧壁间隔物362可以通过在装置结构300上方沉积作为覆盖层的间隔物材料来形成。随后,在侧壁间隔物362上方沉积介电层364,例如原硅酸四乙酯(tetraethyl orthosilicate,TEOS)层。介电层364可以通过等离子体化学气相沉积(PE-CVD)、流动式化学气相沉积(flowable chemical vapor deposition,F-CVD)或其他合适的方法形成。然后在介电层364和侧壁间隔物362上执行平坦化操作,使得在平坦化操作之后暴露出顶电极350的顶表面。平坦化操作之后所得结构如图16中示出。由于介电层310凹入的顶表面,侧壁间隔物362的一部分在底电极322的底表面下方。

在操作224,方法200(图2B)形成金属间介电质(inter-metal dielectric,IMD)层390,此金属间介电质(IMD)层390覆盖侧壁间隔物层362和介电层364,如图17所示。金属间介电质(IMD)层390可以包括正硅酸四乙酯(TEOS)氧化物、未掺杂硅酸盐玻璃或掺杂硅氧化物,例如硼磷硅酸盐玻璃(borophosphosilicate glass,BPSG)、熔融石英玻璃(fusedsilica glass,FSG)、磷硅酸盐玻璃(phosphosilicate glass,PSG)、硼掺杂硅玻璃(borondoped silicon glass,BSG)及/或其他合适的介电材料。可以通过等离子体化学气相沉积(PE-CVD)、流动式化学气相沉积(F-CVD)或其他合适的方法来形成金属间介电质(IMD)层390。在一些实施例中,金属间介电质(IMD)层396由低k介电层或极低k介电层形成,厚度约为

在操作226,方法200(图2B)执行进一步的步骤以完成装置结构300的制造。举例而言,方法200可以在金属间介电质(IMD)层396中形成导孔沟槽和开口(未示出),且在其中沉积导电材料以提供互连,例如金属线394和坐落在其上的顶电极导孔(top electrode via,TEVA)392,如图17所示。金属线394是金属互连层的一部分,例如磁性随机存取存储器(MRAM)单元阵列中的位线(例如,图1C中的位线BL

如图18绘示出图1C中磁性随机存取存储器(MRAM)单元阵列沿A-A线的截面图。参照图18,沿着位线(例如图1C中的位线BL

本公开的一个或多个实施例为半导体装置及其形成提供了许多益处。且不意图将本公开作出范围之外的限制。举例来说,本公开的实施例提供了具有低电阻的含铜底电极导孔的磁性随机存取存储器(MRAM)单元阵列,以实现磁性随机存取存储器(MRAM)单元阵列的高灵敏度和高速,而没有铜扩散到测量磁性穿隧接面(MTJ)中的风险。此外,磁性随机存取存储器(MRAM)单元阵列的形成可以容易地整合到现有的半导体制造制程中。

在一个示例性的面向,本公开针对一种用于制造存储器装置的方法。此方法包括用于制造存储器装置的方法。此方法包括:形成导孔沟槽在基板中;形成导孔在导孔沟槽中,其中导孔的下部包括第一金属,且导孔的上部包括不同于第一金属的第二金属;形成磁性穿隧接面在导孔上方;以及形成上电极在磁性穿隧接面上方。在一些实施例中,第一金属的电阻率低于第二金属的电阻率。在一些实施例中,第一金属具有第一厚度,第二金属具有小于第一厚度的第二厚度。在一些实施例中,第一厚度与第二厚度的比例为约2∶1至约5∶1。在一些实施例中,第二厚度不小于约

在另一个示例性的面向,本公开针对一种用于制造存储器装置的方法。此方法包括:提供基板;形成导孔沟槽基板中;沉积第一金属于导孔沟槽的下部中;沉积第二金属于导孔沟槽的上部中,从而于导孔沟槽中形成导孔,其中第二金属具有比第一金属更高的电阻率;形成下电极层于导孔上方;形成磁性穿隧接面堆叠于下电极层上方,其中磁性穿隧接面包括:下铁磁层;穿隧阻障层,于下铁磁层上方;以及上铁磁层,于穿隧阻障层上方;以及形成上电极层于磁性穿隧接面堆叠层上方。在一些实施例中,其中第一金属为铜,第二金属为钨。在一些实施例中,第二金属的厚度小于该第一金属的厚度。在一些实施例中,第二金属的厚度至少为

在又另一个示例性的面向,本公开针对一种用于存储器装置。此存储器装置包括:下电极导孔,其包括下部和上部,其中下部包括第一金属,上部包括不同于第一金属的第二金属;下电极,设置于下电极导孔上方;磁性穿隧接面,设置于下电极上方;以及上部电极,设置于磁性穿隧接面上方。在一些实施例中,第一金属的电阻率低于第二金属的电阻率。在一些实施例中,第一金属为铜,第二金属为钨。在一些实施例中,存储器装置,更包括:介电层,环绕于下电极导孔,其中介电层的部分于下电极的正下方,且与下电极接触。

以上概述数个实施例的部件,以便在本发明所属技术领域中具有通常知识者可更易理解本发明实施例的观点。在本发明所属技术领域中具有通常知识者应理解,他们能以本发明实施例为基础,设计或修改其他制程和结构,以达到与在此介绍的实施例相同的目的及/或优势。在本发明所属技术领域中具有通常知识者也应理解到,此类等效的制程和结构并无悖离本发明的精神与范围,且他们能在不违背本发明的精神和范围之下,做各式各样的改变、取代和替换。