字线驱动器电路及存储器

文献发布时间:2023-06-19 18:32:25

技术领域

本申请实施例涉及半导体领域,特别涉及一种字线驱动器电路及存储器。

背景技术

存储器中的各种电路需要使用各种信号,用于将信号施加于信号线的信号驱动器被普遍应用。字线驱动器用于向存储单元阵列中的字线施加电压,字线可以从子字线驱动器(SWD,Sub Wordline Driver)开始延伸并穿过存储单元整列。子字线驱动器可以响应于存储设备接收到的对应于字线的行地址而选择性地激活对应的字线,与被激活字线连接的每个存储单元可以将数据输出或输入。

发明内容

本申请实施例提供一种新的字线驱动器电路及存储器。

根据本申请一些实施例,本申请实施例提供一种字线驱动器电路,包括:多个字线驱动器,每一所述字线驱动器包含PMOS管和NMOS管,多个所述字线驱动器包含多个PMOS管和多个NMOS管,所述多个PMOS管并排设置,在所述多个PMOS管的排列方向上,部分所述多个NMOS管位于所述PMOS管的一侧,另一部分所述NMOS管位于所述多个PMOS管的相对的另一侧。

根据本申请一些实施例,本申请实施例还提供一种存储器,包含上述字线驱动器电路。

本申请实施例提供的技术方案至少具有以下优点:

本申请实施例中,多个PMOS管并排设置,且在多个PMOS管的排列方向上,多个NMOS管位于多个PMOS管的相对两侧,如此,有利于避免在垂直上述排列方向的方向上PMOS管和NMOS管并排设置,使得在垂直方向上PMOS管和NMOS管具有更大的空间,从而有利于延长PMOS管和NMOS管的沟道长度或栅极宽度,提升字线驱动器电路的电学性能;同时,控制NMOS管位于PMOS管的相对两侧,有利于使得不同字线驱动器对应的PMOS管与NMOS管之间的间距较短,从而缩短布线长度、降低导线电阻以及降低信号延迟;此外,将NMOS管设置于PMOS管的相对两侧,有利于提升字线驱动器电路的对称性,从而字线驱动器电路的电学性能。

附图说明

一个或多个实施例通过与之对应的附图中的图片进行示例性说明,这些示例性说明并不构成对实施例的限定,除非有特别申明,附图中的图不构成比例限制。

图1为本申请实施例提供的存储器的结构示意图;

图2为本申请实施例提供的字线驱动器电路的电路结构示意图;

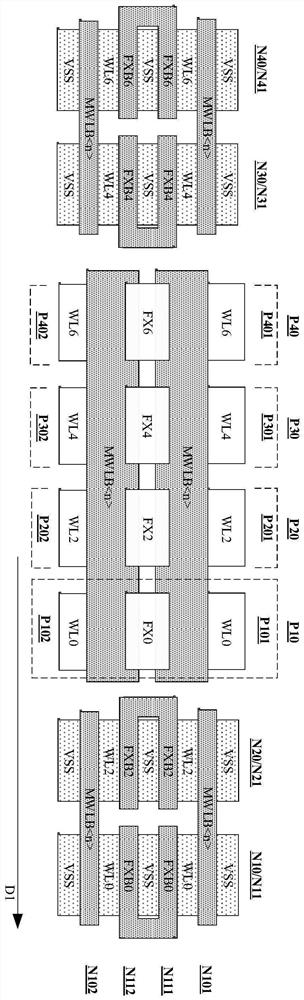

图3至图9为本申请实施例提供的字线驱动器电路的版图结构示意图。

具体实施方式

下面将结合附图对本申请的各实施例进行详细的阐述。然而,本领域的普通技术人员可以理解,在本申请各实施例中,为了使读者更好地理解本申请而提出了许多技术细节。但是,即使没有这些技术细节和基于以下各实施例的种种变化和修改,也可以实现本申请所要求保护的技术方案。

图1为本申请实施例提供的存储器的结构示意图;图2为本申请实施例提供的字线驱动器电路的电路结构示意图;图3至图9为本申请实施例提供的字线驱动器电路的版图结构示意图。

字线驱动器电路包括:多个字线驱动器,每一字线驱动器包含PMOS管和NMOS管,多个字线驱动器包括多个PMOS管和多个NMOS管,多个PMOS管并排设置,在多个PMOS管的排列方向上,部分NMOS管位于多个PMOS管的一侧,另一部分NMOS管位于多个PMOS管的另一侧。

以下将结合附图对本申请实施例进行更为详细的说明。

参考图1,根据连接的字线不同,字线驱动器可分为奇数字线驱动器SWD_ODD和偶数字线驱动器SWD_EVEN,奇数字线驱动器SWD_ODD用于连接奇数位字线(例如WL1、WL3、WL5以及WL7),偶数字线驱动器SWD_EVEN用于连接偶数位字线(例如WL0、WL2、WL4以及WL6)。在存储设备中,奇数字线驱动器SWD_ODD和偶数字线驱动器SWD_EVEN通常间隔设置,奇数位字线与偶数位字线通常间隔排列。

参考图1和图2,以每一字线驱动器电路包含四个字线驱动器作为示例进行说明,根据图示可知,同一字线驱动器电路中的不同字线驱动器的类型相同,即均为奇数字线驱动器或偶数字线驱动器;每一字线驱动器可包含一个PMOS管和两个NMOS管,记为第零PMOS管、第零NMOS管和第一NMOS管,第零PMOS管的栅极和第零NMOS管的栅极用于接收第一控制信号MWLB(例如MWLB

其中,第二控制信号FX向高电平跳变的时刻与第二控制互补信号FXB向低电平跳变的时刻、第一控制信号MWLB向低电平跳变的时刻相同,第二控制互补信号FXB向高电平跳变的时刻晚于第二控制信号FX向低电平跳变的时刻,第一控制信号MWLB向高电平跳变的时刻晚于第二控制互补信号FXB向高电平跳变的时刻。

示例性地,字线驱动器电路包括第一字线驱动器SWD1、第二字线驱动器SWD2、第三字线驱动器SWD3以及第四字线驱动器SWD4,第一字线驱动器SWD1包括PMOS管P10与NMOS管N10和N11,第二字线驱动器SWD2包括PMOS管P20与NMOS管N20和N21,第三字线驱动器SWD3包括PMOS管P30与NMOS管N30和N31,第四字线驱动器SWD4包括PMOS管P40与NMOS管N40和N41,其中,P10、P20、P30以及P40属于第零PMOS管,N10、N20、N30以及N40属于第零NMOS管,N11、N21、N31以及N41属于第一NMOS管。

在一些实施例中,每一PMOS管由至少两个子PMOS管构成;在另一些实施例中,每一NMOS管由至少两个子NMOS管构成;在又一实施例中,每一PMOS管由至少两个子PMOS管构成,且每一NMOS管由至少两个子NMOS管构成。示例性地,第零PMOS管由第零一PMOS管和第零二PMOS管构成,第零NMOS管由第零一NMOS管和第零二NMOS管构成,第一NMOS管由第一一NMOS管和第一二NMOS管构成。需要说明的是,本申请实施例中,第零一PMOS管和第零二PMOS管为物理特性完全相同的NMOS管,区别仅在于自身的位置不同以及与其他部件的连接关系不同,同理地,第一一NMOS管和第一二NMOS管以及第零一NMOS管和第零二NMOS管为物理特性完全相同的NMOS管,区别仅在于自身的位置不同以及与其他部件的连接关系不同。设置由两个子MOS管共同构成PMOS管或NMOS管,有利于调节版图的布局。

为了图示的简洁,图3至图9中并未标示每一晶体管或子晶体管,本领域技术人员可以根据图2中不同晶体管的栅源漏所接收的信号,确定图3至图9中不同位置的晶体管表征的是哪一晶体管或哪一子晶体管。

在一些实施例中,参考图3,第一字线驱动器中的P10、第二字线驱动器中的P20、第三字线驱动器中的P30以及第四字线驱动器中的P40沿第一方向D1并排设置,在第一方向D1上,第一字线驱动器中的N10和N11与第二字线驱动器中的N20和N21位于上述多个PMOS管的一侧,第三字线驱动器中的N30和N31与第四字线驱动器中的N40和N41位于上述多个PMOS管的相对的另一侧。

在一些实施例中,记字线驱动器中PMOS管与NMOS管之间的间距为预设间距,不同字线驱动器之间的预设间距相同。其中,参考图3,在第一方向D1上,字线驱动器中第零PMOS管与第零NMOS管和第一NMOS管之间的间距相等,具体地,P10与N10和N11之间的间距相等,P20与N20和N21之间的间距相等,P30与N30和N31之间的间距相等,P40与N40和N41之间的间距相等;进一步地,P10与N10之间的第一间距与P20与N20之间的第二间距、P30与N30之间的第三间距以及P40与N40之间的第四间距相等。设置不同的预设间距相等,有利于使得不同字线驱动器具有相同或相近的性能,从而使得不同字线驱动器向对应的字线施加电压的时刻相近,保证存储器内部时序的稳定性。

在一些实施例中,两个子PMOS管共用同一源极。以第一字线驱动器为例,第一字线驱动器中的PMOS管P10由P101和P102两个子PMOS管构成,P101和P102共用同一有源区,用于接收第一控制信号FX,具体为FX0。

在一些实施例中,多个PMOS管的排列方向(即第一方向D1)垂直于PMOS管的沟道长度方向,其中,两个子PMOS管的排列方向平行于PMOS管的沟道长度方向且垂直于第一方向D1。继续以第一实施例作为示例,P101和P102的排列方向平行于沟道长度方向且垂直于第一方向D1。

在一些实施例中,每一PMOS管包括第一子PMOS管和第二子PMOS管,不同PMOS管对应的第一子PMOS管共用同一栅极,不同PMOS管对应的第二子PMOS管共用同一栅极。如图3所示,PMOS管P20包括P201和P202,PMOS管P30包括P301和P302,PMOS管P40包括P401和P402,P101、P201、P301以及P401沿第一方向D1并排设置且共用同一栅极,P102、P202、P302以及P402沿第一方向D1并排设置且共用另一栅极。

在一些实施例中,第一一NMOS管和第一二NMOS管位于第零一NMOS管和第零二NMOS管之间。参考图3,不同字线驱动器的NMOS管的内部排列方式相同,以第一字线驱动器为例,第一字线驱动器中的第零NMOS管N10包括第零一NMOS管N101和第零二NMOS管N102,第一NMOS管N11包括第一一NMOS管N111和第一二NMOS管N112,N111和N112位于N101和N102之间。

在一些实施例中,第一一NMOS管和第一二NMOS管的排列方向平行于第零一NMOS管和第零二NMOS管的排列方向。同样地,以第一字线驱动器为例,N111与N112的排列方向平行于N101与N102的排列方向。

在一些实施例中,不同晶体管及其子晶体管的沟道长度方向相同,如此,有利于实现同一字线驱动器中PMOS管与NMOS管之间具有唯一的预设间距,如此,有利于使得字线驱动器具有更为稳定和均衡的性能。具体地,以第一字线驱动器为例,在第一方向D1上,P101与N101之间的距离等于P102和N102之间的距离;其中,在第一方向D1上,P101的栅极的水平位置与N101的栅极的水平位置至少部分重合,P101与N101之间的距离为P101的栅极与N101的栅极之间的距离,P102与N102之间同理,在此不再进行赘述。

相应地,在第一方向D1上,P101与N111之间的距离等于P102与N112之间的距离;其中,在第一方向D1上,P101的栅极的水平位置与N111的栅极的水平位置至少部分重合,P101与N111之间的距离为P101的栅极与N111的栅极之间的距离,P102与N112之间同理,在此不再进行赘述。

在一些实施例中,第零一NMOS管与第一一NMOS管共用同一漏极,第一一NMOS管与第一二NMOS管共用同一源极,第一二NMOS管与第零二NMOS管共用同一漏极,不同晶体管共用同一源极或漏极,有利于减小字线驱动器的整体尺寸,进而实现字线驱动器电路以及存储器的小型化和微型化。以第一字线驱动器为例,N101和N111共用同一有源区,该有源区通过接触孔与第零字线WL0连接,N111和N112共用同一有源区,该有源区接地或连接低电平信号,N112和N102共用同一有源区,该有源区同样通过接触孔与第零字线WL0连接。

其中,第一一NMOS管和第一二NMOS管共用同一栅极,不同晶体管共用同一栅极有利于降低栅极的制作难度和保证栅极的导电性能,具体来说,有利于降低掩膜的图案化开口的复杂度,避免因图案较为复杂而出现刻蚀缺陷,保证栅极能够有效形成。以第一字线实施例为例,N111和N112共用同一栅极,或者说,N111的栅极和N112的栅极为同一导电层的不同部分,用于连通N111的栅极和N112的栅极的另一部分导电层位于隔离结构上。隔离结构用于隔离相邻有源区,字线可以采用掺杂多晶硅或金属材料制成,例如钨和钼。

在一些实施例中,第零一NMOS管和第零二NMOS管位于第一一NMOS管和第一二NMOS管之间;其中,第零一NMOS管和第零二NMOS管可共用同一栅极。参考图4,不同字线驱动器的NMOS管的内部排列方式相同,以第一字线驱动器为例,N101和N102位于N111和N112之间,N101和N102共用同一栅极。

与上一实施例类似的是,位于中间位置的第零一NMOS管和第零二NMOS管的排列方向平行于位于两侧的第一一NMOS管和第一二NMOS管的排列方向,对应图4,N101与N102的排列方向平行于N111与N112的排列方向。

相应地,第一一NMOS管与第零一NMOS管共用同一漏极,第零一NMOS管与第零二NMOS管共用同一源极,第零二NMOS管与第一二NMOS管共用同一漏极。对应图4,N111和N101和共用同一有源区,该有源区通过接触孔与第零字线WL0连接,N101和N102共用同一有源区,该有源区接地或连接低电平信号,N102和N112共用同一有源区,该有源区同样通过接触孔与第零字线WL0连接。

在一些实施例中,参考图4,字线驱动器包括第一字线驱动器和第二字线驱动器,第一字线驱动器中的NMOS管N10与第二字线驱动器中的NMOS管N20共用同一源极和同一栅极。其中,N20由N201和N202构成,N10由N101和N102构成,N201、N202、N101以及N102共用同一连续的有源区和同一连续的导电层。可以理解的是,不同晶体管的栅极为同一导电层的不同部分,连接不同晶体管的栅极的其他部分导电层位于隔离结构上,隔离结构用于隔离相邻有源区;此外,共用的连续导电层可以根据晶体管的排布呈现出各种形状,在一些实施例中,共用的连续导电层呈现环状。

相应地,第一字线驱动器包含的第一NMOS管与第二字线驱动器包括的第一NMOS管共用源极。其中,第一字线驱动器中的第一NMOS管由N111和N112构成,第二字线驱动器中的第一NMOS管由N111和N112构成,N111和N211共用同一源极,N112和N212共用同一源极。

可以理解的是,不同字线驱动器之间存在多种组合,本申请实施例以第一字线驱动器和第二字线驱动器的NMOS管设置在PMOS管的同一侧作为示例,并基于该示例说明字线驱动器电路中位于PMOS管同一侧的相邻字线驱动器的NMOS管的连接关系。可以理解的是,在图4所示实施例中,第三字线驱动器的NMOS管和第四字线驱动器的NMOS管可同样适用上述连接关系;同理,在其他实施例中,若第一字线驱动的NMOS管和第三字线驱动器的NMOS管位于PMOS管的一侧,则上述连接关系的表述还适用于第一字线驱动器的NMOS管和第三字线驱动器的NMOS管。后续仍以第一字线驱动器和第二字线驱动器作为示例进行说明,关于其适用情况不再进行赘述。

在一些实施例中,第一一NMOS管和第一二NMOS管的排列方向平行于第零一NMOS管和第零二NMOS管的排列方向;其中,第零一NMOS管和第零二NMOS管共用同一栅极,和/或第一一NMOS管和第一二NMOS管共用同一栅极。

其中,在一些实施例中,参考图5,字线驱动器包括第一字线驱动器和第二字线驱动器,第一字线驱动器包含的第一NMOS管和第二字线驱动器包含的第一NMOS管位于第一字线驱动器包含的第零NMOS管和第二字线驱动器包含的第零NMOS管之间,即N11和N21位于N10和N20之间。

在另一些实施例中,参考图6,字线驱动器包括第一字线驱动器和第二字线驱动器,第一字线驱动器包含的第零NMOS管和第二字线驱动器包含的第零NMOS管位于第一字线驱动器包含的第一NMOS管和第二字线驱动器包含的第一NMOS管之间,即N10和N20位于N11和N21之间;此外,N10和N20共用同一栅极。

在一些实施例中,参考图3至图6,字线驱动器中NMOS管的沟道长度方向平行于PMOS管的沟道长度方向,或者说,PMOS管的沟道长度方向与NMOS管的沟道长度方向相同;在另一些实施例中,参考图7至图9,字线驱动器中NMOS管的沟道长度方向垂直于PMOS管的沟道长度方向。其中,图7所示实施例与图3所示实施例的区别在于整体调整字线驱动器电路中NMOS管的沟道长度方向,相应地,图8所示实施例与图6所示实施例以及图9和图5所示实施例的主要区别特征也在于此。

由于与字线驱动器连接的字线的延伸方向一般平行于字线驱动器中PMOS管的栅极的延伸方向,设置NMOS管的沟道长度方向垂直于PMOS管的沟道长度方向,有利于避免在垂直于第一方向D1的第二方向D2上并排较多的NMOS管,为NMOS管的漏极的延伸预留更大的空间,使得NMOS管的漏极具有较大的宽度,进而有利于使得从PMOS管的漏极延伸出来的字线无需弯折即可直接与对应的NMOS管的漏极连接,即使得字线呈现直线,降低字线的电阻和电阻导致的RC延迟,保证字线驱动器电路具有良好的电学性能。

本实施例中,多个PMOS管并排设置,且在多个PMOS管的排列方向上,多个NMOS管位于多个PMOS管的相对两侧,如此,有利于避免在垂直上述排列方向的方向上PMOS管和NMOS管并排设置,使得在垂直方向上PMOS管和NMOS管具有更大的空间,从而有利于延长PMOS管和NMOS管的沟道长度或栅极宽度,提升字线驱动器电路的电学性能;同时,控制NMOS管位于PMOS管的相对两侧,有利于使得不同字线驱动器对应的PMOS管与NMOS管之间的间距较短,从而缩短布线长度、降低导线电阻以及降低信号延迟;此外,将NMOS管设置于PMOS管的相对两侧,有利于提升字线驱动器电路的对称性,从而字线驱动器电路的电学性能。

本申请实施例还提供一种存储器,包括上述任一项所述的字线驱动器电路。在集成电路的尺寸日益微缩的情况下,采用上述结构的字线驱动器电路,由于其晶体管和字线可具有良好的电学性能,因此字线驱动器电路可具有良好的特性,从而提升存储器的整体性能。

本领域的普通技术人员可以理解,上述各实施方式是实现本申请的具体实施例,而在实际应用中,可以在形式上和细节上对其作各种改变,而不偏离本申请的精神和范围。任何本领域技术人员,在不脱离本申请的精神和范围内,均可作各自更动与修改,因此本申请的保护范围应当以权利要求限定的范围为准。

- 一种减少电压差的存储器字线选择电路及芯片和存储器

- 驱动器以及具有该驱动器的存储器控制器

- 存储器保护电路及包括该存储器保护电路的液晶显示器

- 在非易失性存储器中确定快速编程字线

- 用于降低三维NOR存储器阵列中的干扰的交错的字线架构

- 包括存储器阵列的存储器单元下方的感测放大器电路系统和字线驱动器电路系统的集成组合件

- 用于避免由于分段字线驱动器电路中的浮动字线而导致的失灵的本地字线驱动器电路