运用于多次编程非易失性存储器的差动存储器胞阵列结构

文献发布时间:2023-06-19 18:32:25

技术领域

本发明涉及一种阵列结构(memory cell array),且特别涉及一种运用于多次编程非易失性存储器的差动存储器胞阵列结构。

背景技术

众所周知,非易失性存储器在断电之后仍旧可以保存其数据内容。以多次编程非易失性存储器(multi-time programming non-volatile memory,简称MTP非易失性存储器)为例,使用者可进行编程操作(program operation)并将数据存储在非易失性存储器中。再者,使用者可进行读取操作(read operation)并获得非易失性存储器中的存储数据。当然,使用者也可以进行擦除操作(erase operation)用以清除非易失性存储器中的存储数据。

一般来说,非易失性存储器是由多个存储器胞组成一阵列结构,而阵列结构连接至多条信号线,例如字线(word line)、位线(bit line)、擦除线(erase line)。再者,提供适当的偏压至这些信号线时,使用者可对阵列结构中的存储器胞进行编程操作、读取操作或者擦除操作。

然而,由于已知非易失性存储器的阵列结构设计,对阵列结构进行擦除操作时,阵列结构内一个区域(area)中所有存储器胞的数据会同时被擦除,例如芯片擦除(chiperase)或者区段擦除(segment erase)。举例来说,在擦除操作时,阵列结构一个区段(segment)中的256个存储器胞的数据会同时被擦除。换句话说,已知非易失性存储器无法对阵列结构中单一个存储器胞进行擦除操作。

发明内容

本发明涉及一种差动存储器胞阵列结构。该差动存储器胞阵列结构包括:一第一差动存储器胞。该第一差动存储器胞包括:一第一选择晶体管,该第一选择晶体管的一第一漏/源端连接至一第一源极线,该第一选择晶体管的一栅极端连接至一第一字线,该第一选择晶体管的一体极端接收一第一井区电压;一第一浮动栅晶体管,该第一浮动栅晶体管的一第一漏/源端连接至该第一选择晶体管的一第二漏/源端,该第一浮动栅晶体管的一第二漏/源端耦合至一第一位线,该第一选择晶体管的一体极端接收该第一井区电压;一第一电容器,该第一电容器的一第一端连接至该第一浮动栅晶体管的一浮动栅极,该第一电容器的一第二端连接至一第一擦除线;一第二选择晶体管,该第二选择晶体管的一第一漏/源端连接至该第一源极线,该第二选择晶体管的一栅极端连接至该第一字线,该第二选择晶体管的一体极端接收该第一井区电压;一第二浮动栅晶体管,该第二浮动栅晶体管的一第一漏/源端连接至该第二选择晶体管的一第二漏/源端,该第二浮动栅晶体管的一第二漏/源端耦合至一第一反相位线,该第二浮动栅晶体管的一体极端接收该第一井区电压;以及,一第二电容器,该第二电容器的一第一端连接至该第二浮动栅晶体管的一浮动栅极,该第二电容器的一第二端连接至该第一擦除线。

为了对本发明的上述及其他方面有更佳的了解,下文特举优选实施例,并配合附图,作详细说明如下:

附图说明

图1A至图1C为本发明第一实施例差动存储器胞的制作流程图;

图1D为本发明第一实施例差动存储器胞的等效电路;

图2A为本发明第一实施例差动存储器胞进行编程操作、读取操作与擦除操作的偏压表;

图2B至图2D为差动存储器胞进行编程操作、读取操作与擦除操作的偏压示意图;

图3A与图3B为本发明MTP非易失性存储器的阵列结构俯视图以及阵列结构的等效电路。

图4A为本发明阵列结构进行编程操作、读取操作与擦除操作的偏压表;

图4B至图4D为阵列结构进行编程操作、读取操作与擦除操作的偏压示意图;

图5A为本发明第二实施例差动存储器胞的等效电路;

图5B为第二实施例差动存储器胞所组成的阵列结构;

图6A至图6C为本发明第三实施例差动存储器胞的制作流程图;

图6D为本发明第三实施例差动存储器胞的等效电路;

图7A与图7B为本发明MTP非易失性存储器的阵列结构俯视图以及阵列结构的等效电路;

图8A为本发明阵列结构进行各种操作的偏压表;以及

图8B为阵列结构进行擦除操作的偏压示意图。

【符号说明】

102,110,120,202,204,210,220,230,240,250,260,270,280,602,610,620,702,704,710,720,730,740,750,760,770,780:栅极结构

112,114,116,122,124,126,212,214,216,222,224,226,232,234,236,242,244,246,252,254,256,262,264,266,272,274,276,282,284,286,612,614,616,622,624,626,712,714,716,722,724,726,732,734,736,742,744,746,754,756,764,766,774,776,784,786:p掺杂区

192,292,294,691,692,791,792,793,794,795,796:n掺杂区

具体实施方式

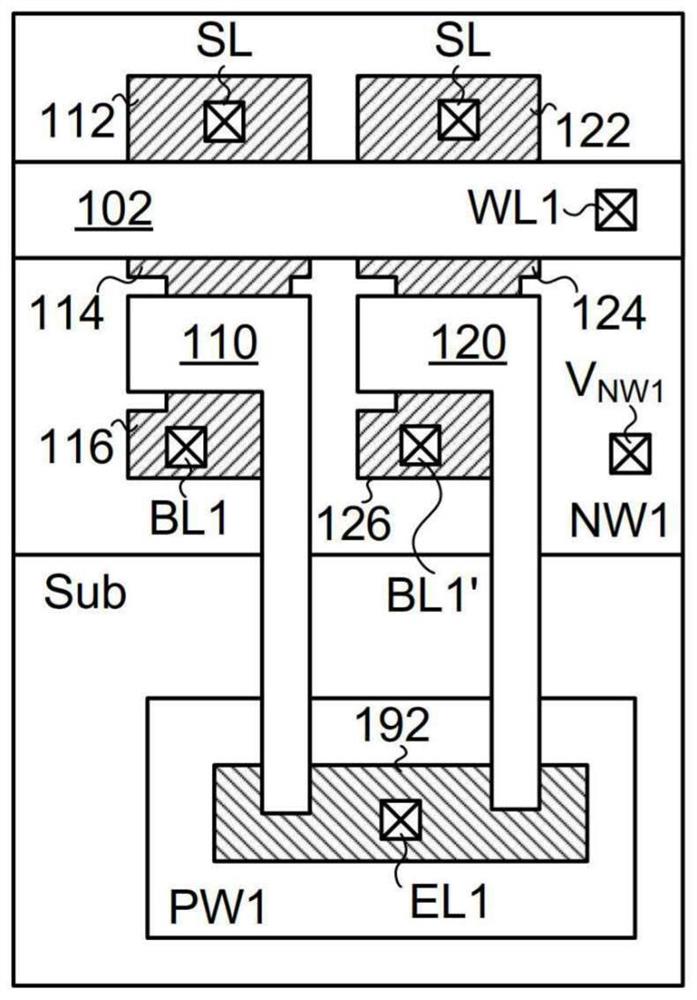

请参照图1A至图1C,其所绘示为本发明第一实施例差动存储器胞的制作流程图。图1D为本发明第一实施例差动存储器胞的等效电路。

如图1A所示,在半导体基板(substrate)Sub的表面下方形成N型井区(N-well)NW1,以及P型井区(P-well)PW1。

如图1B所示,形成多个栅极结构102、110、120。其中,栅极结构102覆盖于N型井区NW1。另外,栅极结构110、120覆盖于N型井区NW1,且栅极结构110、120经由半导体基板Sub上方延伸至P型井区PW1。亦即,栅极结构110、120覆盖于N型井区NW1与P型井区PW1。其中,栅极结构102、110、120皆包括一栅极端氧化层(gate oxide layer)与一多晶硅栅极层(polysilicon gate layer),栅极端氧化层覆盖于半导体基板Sub的表面,且多晶硅栅极层覆盖于栅极端氧化层上。

进行第一次掺杂工艺,在N型井区NW1中形成p掺杂区112、114、116、122、124、126。其中,p掺杂区112位于栅极结构102第一侧,p掺杂区114位于栅极结构102第二侧以及栅极结构110第一侧之间,p掺杂区116位于栅极结构110第二侧。p掺杂区122位于栅极结构102第一侧,p掺杂区124位于栅极结构102第二侧以及栅极结构120第一侧之间,p掺杂区126位于栅极结构120第二侧。

接着,进行第二次掺杂工艺,在P型井区PW1中形成n掺杂区192。如图1B所示,n掺杂区192相邻于延伸至P型井区PW1的栅极结构110、120。

当然,上述二次掺杂工艺的顺序可以互换。也就是说,第一次掺杂工艺可在P型井区PW1中形成n掺杂区192,第二次掺杂工艺可在N型井区NW1中形成p掺杂区112、114、116、122、124、126。

如图1C所示,进行连线工艺,形成多条金属线(metal line)。其中,连接至p掺杂区112、122的金属线作为源极线SL。连接至p掺杂区116的金属线作为位线BL1。连接至p掺杂区126的金属线作为反相位线BL1'。连接至栅极结构102的金属线作为字线WL1。连接至n掺杂区192的金属线作为擦除线EL1。再者,金属线连接至N型井区NW1,使得N型井区NW1可接收井区电压V

如图1D所示,差动存储器胞c11包括二个子存储器胞(sub cell)c1、c1',且二个子存储器胞c1、c1'的结构相同。

子存储器胞c1包括二个晶体管M

相同地,子存储器胞c1'包括二个晶体管M

请参照图2A,其所绘示为本发明第一实施例差动存储器胞进行编程操作、读取操作与擦除操作的偏压表。再者,图2B至图2D为差动存储器胞进行编程操作、读取操作与擦除操作的偏压示意图。

请参考图2A与图2B,在编程操作(PGM)时,差动存储器胞c11的源极线SL接收编程电压(program voltage)Vpp,字线WL1接收一半的编程电压(Vpp/2),擦除线EL1接收一半的编程电压(Vpp/2),位线BL1接收接地电压(0V),反相位线BL1'为浮接(floating,简称FLT)。另外,井区电压V

在子存储器胞c1中,由于字线WL1动作(activated),选择晶体管M

在子存储器胞c1'中,虽然字线WL1动作(activated),但由于反相位线BL1'为浮接(FLT),所以无法产生编程电流。因此,热载子,例如电子,无法注入浮动栅晶体管M

也就是说,在编程操作(PGM)时,控制浮动栅晶体管M

当然,在编程操作(PGM)时,也可以控制反相位线BL1'接收接地电压(0V),而位线BL1为浮接(FLT)。此时,浮动栅晶体管M

由以上的说明可知,在编程操作(PGM)时,控制位线BL1以及反相位线BL1'所接收的电压,可将差动存储器胞c11编程为第一存储状态或者为第二存储状态。

请参考图2A与图2C,在读取操作(READ)时,差动存储器胞c11的源极线SL接收读取电压Vr,字线WL1接收开启电压(turn on voltage)Von,擦除线EL1接收接地电压(0V),位线BL1接收接地电压(0V),反相位线BL1'接收接地电压(0V)。另外,井区电压V

如图2C所示,在读取操作(READ)时,字线WL1动作,选择晶体管M

也就是说,在读取操作(READ)时,判断位线BL1与反相位线BL1'上的读取电流Ir、Ir'大小即可确认差动存储器胞c11的存储状态。在图2C中,读取电流Ir大于读取电流Ir',所以确认差动存储器胞c11为第一存储状态。反之,当读取电流Ir'大于读取电流Ir时,则确认差动存储器胞c11为第二存储状态。

请参考图2A与图2D,在擦除操作(ERS)时,差动存储器胞c11的源极线SL接收接地电压(0V),字线WL1接收接地电压(0V),位线BL1接收接地电压(0V),反相位线BL1'接收接地电压(0V),擦除线EL1接收擦除电压(erase voltage)Vee。另外,井区电压V

如图2D所示,在擦除操作(ERS)时,字线WL1动作。由于擦除线EL1与浮动栅晶体管M

当然,在擦除操作(ERS)时,如果热载子存储于浮动栅晶体管M

再者,结合多个第一实施例差动存储器胞可组成MTP非易失性存储器。也就是说,本发明的MTP非易失性存储器,其包括多个差动存储器胞,并组成差动存储器胞阵列结构。根据本发明的实施例,在MTP非易失性存储器中,可针对阵列结构中任一个存储器胞来单独进行擦除操作。

请参照图3A与图3B,其所绘示为本发明MTP非易失性存储器的阵列结构俯视图以及阵列结构的等效电路。其中,MTP非易失性存储器包括4个差动存储器胞c11~c22,组成2x2的阵列结构。当然,本发明的MTP非易失性存储器并不限定于2x2的阵列结构,也可以组成mxn的阵列结构,其中m、n为正整数。

如图3A所示,在半导体基板(substrate)Sub的表面下方形成二个N型井区(N-well)NW1、NW2,以及二个P型井区(P-well)PW1、PW2。其中,分离的二个N型井区(N-well)NW1、NW2形成在半导体基板Sub的上方区域与下方区域形成,而分离的二个P型井区(P-well)PW1、PW2则形成在半导体基板Sub的中间区域。再者,半导体基板Sub可为P型半导体基板。

接着,形成多个栅极结构202、204、210、220、230、240、250、260、270、280。栅极结构202覆盖于N型井区NW1,栅极结构204覆盖于N型井区NW2。栅极结构210、220覆盖于N型井区NW1与P型井区PW1。栅极结构230、240覆盖于N型井区NW1与P型井区PW2。栅极结构250、260覆盖于N型井区NW2与P型井区PW1。栅极结构270、280覆盖于N型井区NW2与P型井区PW2。

接着,进行第一次掺杂工艺,在N型井区NW1、NW2中形成p掺杂区212、214、216、222、224、226、232、234、236、242、244、246、252、254、256、262、264、266、272、274、276、282、284、286。以p掺杂区212、214、216为例来说明,p掺杂区212位于栅极结构202第一侧,p掺杂区214位于栅极结构202第二侧以及栅极结构210第一侧之间,p掺杂区216位于栅极结构210第二侧。

再者,进行第二次掺杂工艺,在P型井区PW1、PW2中形成n掺杂区292、294。n掺杂区292相邻于延伸至P型井区PW1的栅极结构210、220、250、260。n掺杂区294相邻于延伸至P型井区PW2的栅极结构230、240、270、280。

再者,进行连线工艺,形成多个金属线(metal line)SL、WL1、WL2、BL1、BL1'、BL2、BL2'、EL1、EL2。其中,源极线SL连接至p掺杂区212、222、232、242、252、262、272、282。位线BL1连接至p掺杂区216、256。反相位线BL1'连接至p掺杂区226、266。位线BL2连接至p掺杂区236、276。反相位线BL2'连接至p掺杂区246、286。字线WL1连接至栅极结构202。字线WL2连接至栅极结构204。擦除线EL1连接至n掺杂区292。擦除线EL2连接至n掺杂区294。井区电压V

如图3B所示,4个差动存储器胞c11~c22组成2x2的阵列结构。其中,每个差动存储器胞c11~c22的等效电路皆相同于图1D,此处不再赘述差动存储器胞c11~c22内部的连接关系。再者,差动存储器胞c11包括二个子存储器胞c1、c1',差动存储器胞c12包括二个子存储器胞c2、c2',差动存储器胞c21包括二个子存储器胞c3、c3',差动存储器胞c22包括二个子存储器胞c4、c4'。

根据本发明的实施例,在图3B的阵列结构中,同一行差动存储器胞的晶体管皆设计在相同的井区。举例来说,在第一行的二个差动存储器胞c11、c12中,选择晶体管M

再者,源极线SL连接至所有差动存储器胞c11~c22。亦即,源极线SL连接至选择晶体管M

字线WL1连接至相同行(row)的二个差动存储器胞c11、c12。亦即,字线WL1连接至选择晶体管M

位线BL1与反相位线BL1'连接至相同列(column)的二个差动存储器胞c11、c21。亦即,位线BL1连接至浮动栅晶体管M

根据本发明的实施例,在图3B的阵列结构中,同一行的多个差动存储器胞分别连接至相异的擦除线。也就是说,相同行的n个差动存储器胞会连接至相异的n条擦除线。在图3B中,第一行的二个差动存储器胞c11、c12分别连接至擦除线EL1、EL2。亦即,擦除线EL1连接至电容器C

请参照图4A,其所绘示为本发明阵列结构进行编程操作、读取操作与擦除操作的偏压表。再者,图4B至图4D为阵列结构进行编程操作、读取操作与擦除操作的偏压示意图。根据本发明的实施例,在MTP非易失性存储器中,可对差动存储器胞中的单一个差动存储器胞进行编程操作、擦除操作、读取操作。以下说明以差动存储器胞c11为选定存储器胞(selected memory cell),并对选定存储器胞来进行编程操作、擦除操作、读取操作。

请参考图4A与图4B,在编程操作(PGM)时,源极线SL接收编程电压Vpp,字线WL1接收一半的编程电压(Vpp/2)、字线WL2接收编程电压(Vpp)、位线BL1接收接地电压(0V),反相位线BL1'为浮接(FLT)、位线BL2为浮接(FLT),反相位线BL2'为浮接(FLT)、擦除线EL1接收一半的编程电压(Vpp/2)、擦除线EL2接收接地电压(0V)、井区电压V

在阵列结构中,由于字线WL1接收一半的编程电压(Vpp/2),所以字线WL1动作(activated),且连接至字线WL1的第一行为选定行(selected row)。再者,字线WL2接收编程电压(Vpp),所以字线WL2未动作(inactivated),且连接至字线WL2的第二行为非选定行(unselected row)。

由于第二行为非选定行,所以差动存储器胞c21、c22中的选择晶体管M

另外,由于第一行为选定行,且位线BL1接收接地电压(0V),反相位线BL1'为浮接(FLT)、位线BL2为浮接(FLT),反相位线BL2'为浮接(FLT)。所以第一行中的差动存储器胞c11为选定存储器胞(selected memory cell),差动存储器胞c12为非选定存储器胞(unselected memory cell)。因此,选定存储器胞(亦即差动存储器胞c11)被编程为第一存储状态;非选定存储器胞c12被编程抑制(program inhibition)。

当然,在上述的编程操作(PGM)时,如果位线BL1为浮接(FLT),反相位线BL1'接收接地电压(0V),则差动存储器胞c11为选定存储器胞,且选定存储器胞会被编程为第二存储状态。

请参考图4A与图4C,在读取操作(READ)时,源极线SL接收读取电压Vr,字线WL1接收开启电压(Von)、字线WL2接收关闭电压(Voff)、位线BL1接收接地电压(0V),反相位线BL1'接收接地电压(0V)、位线BL2为浮接(FLT),反相位线BL2'为浮接(FLT)、擦除线EL1接收接地电压(0V)、擦除线EL2接收接地电压(0V)、井区电压V

在阵列结构中,由于字线WL1接收开启电压(Von),所以字线WL1动作(activated),且连接至字线WL1的第一行为选定行(selected row)。再者,字线WL2接收关闭电压(Voff),所以字线WL2未动作(inactivated),且连接至字线WL2的第二行为非选定行。

由于第二行为非选定行,所以差动存储器胞c21、c22中的选择晶体管M

另外,由于第一行为选定行,且位线BL1接收接地电压(0V),反相位线BL1'接收接地电压(0V)、位线BL2为浮接(FLT),反相位线BL2'为浮接(FLT)。所以,第一行中的差动存储器胞c11为选定存储器胞,差动存储器胞c12为非选定存储器胞,且非选定存储器胞被读取抑制(read inhibition)。也就是说,在读取操作(READ)时,选定存储器胞的位线BL1以及反相位线BL1'会产生读取电流,而根据二读取电流大小可以判断选定存储器胞(差动存储器胞c11)的存储状态。

请参考图4A与图4D,在擦除操作(ERS)时,源极线SL接收接地电压(0V),字线WL1接收接地电压(0V)、字线WL2接收编程电压(Vpp)、位线BL1接收接地电压(0V),反相位线BL1'接收接地电压(0V)、位线BL2为浮接(FLT),反相位线BL2'为浮接(FLT)、擦除线EL1接收擦除电压(Vee)、擦除线EL2接收接地电压(0V)、井区电压V

在阵列结构中,由于字线WL1接收接地电压(0V),所以字线WL1动作(activated),且连接至字线WL1的第一行为选定行。再者,字线WL2接收编程电压(Vpp),所以字线WL2未动作(inactivated),且连接至字线WL2的第二行为非选定行。

在非选定行的差动存储器胞c21中,擦除线EL1与浮动栅晶体管M

在选定行的差动存储器胞c12中,擦除线EL2与浮动栅晶体管M

另外,在选定行的差动存储器胞c11中,擦除线EL1与浮动栅晶体管M

根据本发明的实施例,在擦除操作(ERS)时,MTP非易失性存储器不会将选定行上所有差动存储器胞中的数据擦除。MTP非易失性存储器仅将选定行中单一个选定存储器胞中的数据擦除。

由于半导体工艺的变异,在擦除操作(ERS)时,某些非选定存储器胞可能会发生软擦除(soft erase)的情况。举例来说,图4D中,与选定存储器胞(差动存储器胞c11)相同列(column)的差动存储器胞c21是被擦除抑制(erase inhibition)。然而,在差动存储器胞c21中,擦除线EL1与浮动栅晶体管M

为了解决上述问题,可修改第一实施例的差动存储器胞。请参照图5A,其所绘示为本发明第二实施例差动存储器胞的等效电路。图5B为第二实施例差动存储器胞所组成的阵列结构。

如图5A所示,差动存储器胞c11包括二个子存储器胞c1、c1',且二个子存储器胞c1、c1'的结构相同。相较于第一实施例差动存储器胞,第二实施例差动存储器胞c11中增加了二个耦合元件(coupling device)512、514。以下仅介绍耦合元件512、514的连接关系以及操作原理。

耦合元件512的第一端连接至浮动栅晶体管M

根据本发明的第二实施例,在进行编程操作(PGM)以及读取操作(READ)时,耦合元件512的第一端与第二端连接,耦合元件514的第一端与第二端连接。也就是说,耦合元件512将浮动栅晶体管M

另外,在进行擦除操作(ERS)时,根据字线WL1是否动作(activated)来切换差动存储器胞c11的耦合元件512、514。举例来说,在擦除操作(ERS)且字线WL1未动作时,耦合元件512的第一端与第二端连接,耦合元件514的第一端与第二端连接。也就是说,耦合元件512将浮动栅晶体管M

另外,在擦除操作(ERS)且字线WL1动作时,耦合元件512的第一端与第三端连接,耦合元件514的第一端与第三端连接。也就是说,耦合元件512将浮动栅晶体管M

请参照图5B,其所绘示为第二实施例差动存储器胞所组成的阵列结构以及擦除操作的偏压示意图。其中,2个差动存储器胞c11~c21组成2×1的阵列结构。当然,类似于图3B的连接关系,也可以将图5B的阵列结构扩大成为2×2或者m×n的阵列结构。再者,每个差动存储器胞c11~c21的等效电路皆相同于图5A,此处不再赘述差动存储器胞c11~c21内部的连接关系。

差动存储器胞c11包括二个子存储器胞c1、c1',差动存储器胞c21包括二个子存储器胞c2、c2'。其中,源极线SL连接至选择晶体管M

在编程操作(PGM)与读取操作(READ)时,图5B的阵列结构的偏压与操作原理类似于图4B与图4C,此处不再赘述。

请参考图5B,在擦除操作(ERS)时,源极线SL接收接地电压(0V),字线WL1接收接地电压(0V),字线WL2接收编程电压(Vpp),擦除线EL1接收擦除电压(Vee)、井区电压V

在阵列结构中,由于字线WL1接收接地电压(0V),所以字线WL1动作(activated),且连接至字线WL1的第一行为选定行(selected row),耦合元件512第一端与第三端连接,耦合元件514第一端与第三端连接。再者,字线WL2接收编程电压(Vpp),所以字线WL2未动作(inactivated),且连接至字线WL2的第二行为非选定行,耦合元件516第一端与第二端连接,耦合元件518第一端与第二端连接。

在选定行的差动存储器胞c11中,擦除线EL1与浮动栅晶体管M

在非选定行的差动存储器胞c21中,擦除线EL1与浮动栅晶体管M

另外,在非选定存储器胞(差动存储器胞c21)中,擦除线EL1与浮动栅晶体管M

请参照图6A至图6C,其所绘示为本发明第三实施例差动存储器胞的制作流程图。图6D为本发明第三实施例差动存储器胞的等效电路。

如图6A所示,在半导体基板(substrate)Sub的表面下方形成N型井区(N-well)NW1,以及P型井区(P-well)PW1、PW2。

如图6B所示,形成多个栅极结构602、610、620。其中,栅极结构602覆盖于基板Sub以及N型井区NW1。另外,栅极结构610、620覆盖于N型井区NW1,栅极结构610经由半导体基板Sub上方延伸至P型井区PW1,栅极结构620经由半导体基板Sub上方延伸至P型井区PW2。亦即,栅极结构610覆盖于N型井区NW1与P型井区PW1,栅极结构620覆盖于N型井区NW1与P型井区PW2。其中,栅极结构602、610、620皆包括一栅极端氧化层(gate oxide layer)与一多晶硅栅极层(polysilicon gate layer),栅极端氧化层覆盖于半导体基板Sub的表面,且多晶硅栅极层覆盖于栅极端氧化层上。

接着,进行第一次掺杂工艺,在N型井区NW1中形成p掺杂区612、614、616、622、624、626。其中,p掺杂区612位于栅极结构602第一侧,p掺杂区614位于栅极结构602第二侧以及栅极结构610第一侧之间,p掺杂区616位于栅极结构610第二侧。p掺杂区622位于栅极结构602第一侧,p掺杂区624位于栅极结构602第二侧以及栅极结构620第一侧之间,p掺杂区626位于栅极结构620第二侧。

接着,进行第二次掺杂工艺,在P型井区PW1、PW2中形成n掺杂区691、692。其中,n掺杂区691相邻于延伸至P型井区PW1的栅极结构610,n掺杂区692相邻于延伸至P型井区PW2的栅极结构620。

当然,上述二次掺杂工艺的顺序可以互换。也就是说,第一次掺杂工艺可在P型井区PW1、PW2中形成n掺杂区691、692,第二次掺杂工艺可在N型井区NW1中形成p掺杂区612、614、616、622、624、626。

如图6C所示,进行连线工艺,形成多个金属线。其中,连接至p掺杂区612、622的金属线作为源极线SL1。连接至p掺杂区616的金属线作为位线BL1。连接至p掺杂区626的金属线作为反相位线BL1'。连接至栅极结构602的金属线作为字线WL1。连接至n掺杂区691的金属线作为擦除线EL1。连接至n掺杂区692的金属线作为擦除线EL1。再者,金属线连接至N型井区NW1,使得N型井区NW1可接收井区电压V

如图6D所示,差动存储器胞c11包括二个子存储器胞(sub cell)c1、c1',且二个子存储器胞c1、c1'的结构相同。

子存储器胞c1包括二个晶体管M

相同地,子存储器胞c1'包括二个晶体管M

基本上,图6D的差动存储器胞c11与图1D的差动存储器胞c11有相同的内部连接关系。因此,对第三实施例差动存储器胞c11进行编程操作(PGM)、读取操作(READ)、擦除操作(RES)的偏压相同于第一实施例,此处不再赘述。

虽然第一实施例差动存储器胞与第三实施例差动存储器胞有相同的内部连接关系,但是第一实施例差动存储器胞所组成的阵列结与第三实施例差动存储器胞所组成的阵列结构则会有不同的连接关系。

请参照图7A与图7B,其所绘示为本发明MTP非易失性存储器的阵列结构俯视图以及阵列结构的等效电路。其中,MTP非易失性存储器包括4个差动存储器胞c11~c22,组成2x2的阵列结构。当然,本发明的MTP非易失性存储器并不限定于2x2的阵列结构,也可以组成mxn的阵列结构,其中m、n为正整数。

如图7A所示,在半导体基板(substrate)Sub的表面下方形成二个N型井区(N-well)NW1、NW2,以及六个P型井区(P-well)PW1~PW6。其中,二个N型井区(N-well)NW1、NW2互相分离。再者,半导体基板Sub可为P型半导体基板。

接着,形成多个栅极结构702、704、710、720、730、740、750、760、770、780。栅极结构702、704覆盖于半导体基板Sub表面以及二个N型井区NW1、NW2。栅极结构710覆盖于N型井区NW1与P型井区PW1。栅极结构720覆盖于N型井区NW1与P型井区PW2。栅极结构730覆盖于N型井区NW2与P型井区PW2。栅极结构740覆盖于N型井区NW2与P型井区PW3。栅极结构750覆盖于N型井区NW1与P型井区PW4。栅极结构760覆盖于N型井区NW1与P型井区PW5。栅极结构770覆盖于N型井区NW2与P型井区PW5。栅极结构780覆盖于N型井区NW2与P型井区PW6。

接着,进行第一次掺杂工艺,在N型井区NW1中形成p掺杂区712、714、716、722、724、726、754、756、764、766;并且,在N型井区NW2中形成p掺杂区732、734、736、742、744、746、774、776、784、786。以p掺杂区712、714、716为例来说明,p掺杂区712位于栅极结构702第一侧以及栅极结构704第一侧之间,p掺杂区714位于栅极结构702第二侧以及栅极结构710第一侧之间,p掺杂区716位于栅极结构710第二侧。

再者,进行第二次掺杂工艺,在P型井区PW1~PW6中形成n掺杂区791~796。n掺杂区791相邻于延伸至P型井区PW1的栅极结构710。n掺杂区792相邻于延伸至P型井区PW2的栅极结构720、730。n掺杂区793相邻于延伸至P型井区PW3的栅极结构740。n掺杂区794相邻于延伸至P型井区PW4的栅极结构750。n掺杂区795相邻于延伸至P型井区PW5的栅极结构760、770。n掺杂区796相邻于延伸至P型井区PW6的栅极结构780。

再者,进行连线工艺,形成多个金属线(metal contact line)SL1、SL2、WL1、WL2、BL1、BL1'、BL2、BL2'、EL1、EL2。其中,源极线SL1连接至p掺杂区712、722,源极线SL2连接至p掺杂区732、742。位线BL1连接至p掺杂区716、756。反相位线BL1'连接至p掺杂区726、766。位线BL2连接至p掺杂区736、776。反相位线BL2'连接至p掺杂区746、786。字线WL1连接至栅极结构702。字线WL2连接至栅极结构704。擦除线EL1连接至n掺杂区791~793。擦除线EL2连接至n掺杂区294~796。井区电压V

如图7B所示,4个差动存储器胞c11~c22组成2x2的阵列结构。其中,每个差动存储器胞c11~c12的等效电路皆相同于图6D,此处不再赘述内部的连接关系。再者,差动存储器胞c11包括二个子存储器胞c1、c1',差动存储器胞c12包括二个子存储器胞c2、c2',差动存储器胞c21包括二个子存储器胞c3、c3',差动存储器胞c22包括二个子存储器胞c4、c4'。

根据本发明的实施例,在阵列结构中,同一行差动存储器胞的晶体管设计在不相同的井区。在第一行的二个差动存储器胞c11、c12中,差动存储器胞c11的选择晶体管M

同理,在第二行的二个差动存储器胞c21、c22中,差动存储器胞c21的选择晶体管M

再者,源极线SL1连接至差动存储器胞c11、c21,源极线SL2连接至差动存储器胞c12、c22。亦即,源极线SL1连接至选择晶体管M

字线WL1连接至相同行(row)的二个差动存储器胞c11、c12。亦即,字线WL1连接至选择晶体管M

位线BL1与反相位线BL1'连接至相同列(column)的二个差动存储器胞c11、c21。亦即,位线BL1连接至浮动栅晶体管M

擦除线EL1连接至相同行的二个差动存储器胞c11、c12。亦即,擦除线EL1连接电容器C

请参照图8A,其所绘示为本发明阵列结构进行各种操作的偏压表。基本上,在编程操作(PGM)与读取操作(READ)时,图8B的阵列结构的偏压与操作原理类似于图4B与图4C,此处不再赘述。

请参照图8B,其所绘示为阵列结构进行擦除操作的偏压示意图。在擦除操作(ERS)时,源极线SL1接收接地电压(0V),源极线SL2接收编程电压Vpp,字线WL1接收接地电压(0V)或编程电压Vpp、字线WL2接收编程电压(Vpp)、位线BL1接收接地电压(0V),反相位线BL1'接收接地电压(0V)、位线BL2接收编程电压Vpp,反相位线BL2'接收编程电压Vpp、擦除线EL1接收擦除电压(Vee)、擦除线EL2接收接地电压(0V)、井区电压V

在阵列结构中,由于擦除线EL1接收擦除电压Vee,所以连接至擦除线EL1的第一行为选定行(selected row)。再者,擦除线EL2接收接地电压(0V),所以连接至擦除线EL2的第二行为非选定行。

在非选定行的差动存储器胞c21中,擦除线EL2与浮动栅晶体管M

在选定行的差动存储器胞c12中,擦除线EL1与浮动栅晶体管M

另外,在选定行的差动存储器胞c11中,擦除线EL1与浮动栅晶体管M

根据本发明的实施例,在擦除操作(ERS)时,MTP非易失性存储器不会将选定行上所有差动存储器胞中的数据擦除。MTP非易失性存储器仅将选定行中单一个选定存储器胞中的数据擦除。

综上所述,虽然本发明已以优选实施例公开如上,然其并非用以限定本发明。本发明所属领域技术人员,在不脱离本发明的精神和范围内,当可作各种的更动与润饰。因此,本发明的保护范围当视所附权利要求书界定范围为准。

- 非易失性存储器装置和包括其的存储器系统及其编程方法

- 非易失性存储器件以及操作非易失性存储器件的方法

- 交叉点存储器结构阵列和形成交叉点存储器结构阵列的方法

- 降低非易失性存储器单元中的编程干扰的方法

- 多次编程非易失性存储器的存储器胞阵列

- 具多阶型存储器胞阵列的非易失性存储器及编程控制方法