用于测试半导体衬底的应力鲁棒性的方法

文献发布时间:2024-04-18 19:48:15

技术领域

本发明涉及一种用于测试半导体衬底的应力鲁棒性(或稳健性)的方法。

现有技术/问题

先进的器件处理可能对半导体衬底施加较高程度的应力。诸如鳍式场效应晶体管的3D结构以及极端热处理可能导致局部应力场,并引起诸如衬底中的塑性变形的机械损伤。塑性变形又会对器件图案叠加以及电气器件性能产生不利影响。因此,重要的是,要知道衬底在器件制造过程中分别在机械鲁棒性和叠加性能方面将会如何表现。以降低的复杂性来模拟器件制造过程的可靠测试允许研发耐用(稳健)的半导体衬底。诸如压头(压痕)测试的现有测试会产生穿入衬底几(若干)微米的明显机械损伤。

EP 2 959 500 B1涉及一种应力测试,其包括利用压痕工具对衬底晶片(或晶圆)造成机械损伤,然后进行热处理。该测试的缺点是引入了深度晶格损伤和塑性变形(其对于半导体器件工艺而言是非典型的)。此外,压痕仅提供关于衬底特性的非常局部的信息,而并不提供遍及整个半导体晶片的信息。

所要求保护的发明的目的是提供一种替代方法,该方法无需对衬底晶片进行机械压痕。所要求保护的发明的优点是与依赖于纯膜诱发的机械近表面应力的器件工艺非常类似,并且可以揭示整个晶片表面上的鲁棒性信息。

发明内容

该目的通过一种用于测试半导体衬底的应力鲁棒性的方法来实现,该方法包括

在所述半导体衬底的表面上形成氮化物层;

通过光刻将所述氮化物层图案化为图案化的氮化物,所述光刻包括利用由包括氢或氢化合物或者两者的气体产生的离子进行反应离子蚀刻的步骤;

在不低于800℃且不高于1300℃的温度下处理所述图案化的氮化物和所述半导体衬底,以在所述图案化的氮化物与所述半导体衬底之间的界面处诱发位错的形成;以及

评估与所形成的位错相关的至少一种特性。

本发明提供了一种在不造成作为应力源的机械损伤的情况下专注于定位器件处的近表面区域的测试。该测试允许对器件制造工艺进行简单模拟,并专注于半导体衬底在位错形成方面的机械鲁棒性。在测试结构内具有降低的位错形成速率或位错传播的半导体衬底将在器件制造工艺中以更高的产率(产出)予以制造。该测试允许研发和生产具有改进的机械鲁棒性的半导体衬底,因为其更接近于真实的器件制造工艺且不会造成作为应力源的严重机械损伤。

由于该方法不具有机械压痕,并且专注于将形成电子器件处的近表面区域,因此可以获得半导体衬底的应力鲁棒性的更为真实的图像。该测试专注于定位电子器件处的近表面区域,并允许识别具有改进的应力鲁棒性的半导体衬底。器件处理中的位错缺陷通常仅可被在线(或线上)检测或者甚至在就电气性能方面对器件进行测试时的后端被检测。该测试允许在晶片上大批量地处理器件之前,在半导体衬底研发过程中已经模拟最关键的器件处理。

该方法在近表面区域中诱发位错的形成,并使用与位错相关的至少一种特性,以量化半导体衬底的应力鲁棒性。

位错在衬底的表面与形成于该表面上的图案化的氮化物之间的界面处借助于热处理被诱发。在半导体衬底和图案化的氮化物的热处理之后,可以去除图案化的氮化物,并且检查与所形成的位错相关的至少一种特性。

在形成图案化的氮化物之前,氮化物层(例如氮化硅层)被直接沉积在半导体衬底的表面上,而无需插置诸如氧化物层之类的另一层。然而,作为例外,在氮化物层与半导体衬底之间可能存在天然氧化物层。优选地,该氮化物层具有均匀的厚度。氮化物层的直接沉积在该层与衬底材料之间提供了显著的机械应力,其由在层沉积之后的冷却期间衬底与氮化物层之间的不同热膨胀系数所引起。氮化物层可以例如借助于LPCVD(低压化学气相沉积)在700℃与800℃之间的高温(升高的温度)下沉积而成。氮化物层可以具有不小于150nm且不大于400nm的厚度。在沉积氮化物层之前,半导体衬底可以经受例如在专用于电子器件制造工艺的条件下的热预处理。

接着氮化物层的沉积,通过光刻(法)将氮化物层转变为图案化的氮化物,该光刻包括在氮化物层上形成图案化的光致抗蚀剂(光刻胶)并且通过RIE(反应离子蚀刻)在没有光致抗蚀剂的位置处去除氮化物的步骤。图案化的氮化物可以包括具有诸如线条、圆、正方形和矩形之类的形式的氮化物结构。线条、正方形和矩形可以侧向(横向)延伸100μm至几(若干)毫米的距离。圆可以具有100μm至5000μm的外径。优选地,氮化物结构的线宽可以为5μm至1000μm。相邻的氮化物结构可以彼此间隔开10μm至几毫米的距离。为了产生具有用于RIE的离子的等离子体,使用包括氢或氢化合物或者两者的气体,例如CHF

在已经形成图案化的氮化物之后,光致抗蚀剂被去除,并且半导体衬底和图案化的氮化物经受随后的热处理,该热处理在RTP(快速热处理)工具中或在分批(间歇式)炉中进行。该热处理可以在氮(气)气氛中实施,并导致位错的形成,所述位错始于半导体衬底与图案化的氮化物之间的界面的边缘位置。热处理的温度可以在800℃至1300℃的范围内,并影响位错传播(扩展)的动力学。在使用RTP的情况下,斜率可以为10℃/s至100℃/s,并且半导体衬底和图案化的氮化物可以在目标温度下退火1分钟至10分钟或更长的时间。在分批炉中进行的热处理可以持续15分钟至3小时或更长的时间。

接下来,可以从半导体衬底上去除图案化的氮化物,并且评估与所形成的位错相关的至少一种特性。所述至少一种特性可以是例如半导体衬底的表面上在热处理期间被埋在氮化物下方(下面)的位置处的位错密度。半导体材料的机械鲁棒性越高,位错密度将越低。在热处理期间,位错密度在已作为边缘位置的位置处最高,并且随着与氮化物边缘相距的距离的增大而降低。由于先前边缘位置处的高位错密度,可以在从先前边缘位置偏移至少1μm地定位的位置处评估位错密度。与所形成的位错相关的所述至少一个特性可以是例如位错传播长度。它标记与最近的先前边缘位置相距的距离,在所述最近的先前边缘位置处,位错密度已降低到接近或等于零的低阈值。半导体材料的机械鲁棒性越高,位错传播长度将越小。

与所形成的位错相关的所述至少一种特性可以在预先去除图案化的氮化物或不需要预先去除图案化的氮化物的情况下被评估。图案化的氮化物可以被去除,并且半导体衬底可以被蚀刻,以对位错进行划线(划界、勾划轮廓或标示边界)。该缺陷蚀刻可以例如利用赖特蚀刻剂实施,并且可以随后使用光学或扫描电子显微镜进行评估。例如,可以从半导体衬底的蚀刻的前表面获取显微(微观)图像,并且可以通过使用评估软件自动计数缺陷,由此可以计算相应的位错相关特性。可替代地,去除图案化的氮化物和随后的蚀刻可以被省略,并且可以使用XRT(x射线形貌术)或PL(光致发光分析)来评估与所形成的位错相关的所述至少一种特性。PL映射器同样能够评估位错进入半导体衬底的块体(体积)中的穿入深度。

半导体衬底可以是例如由单晶制造的抛光硅晶片,包括这种硅晶片和沉积在其上的硅外延层的外延晶片或者SOI(绝缘体上硅)晶片。在(100)取向的硅单晶晶格的情况下,所诱发的位错也传播到晶体块体中,即沿着(111)取向的平面传播,所述平面以约55°的角度与(100)取向的表面相交。

参照附图进一步公开本发明。

附图说明

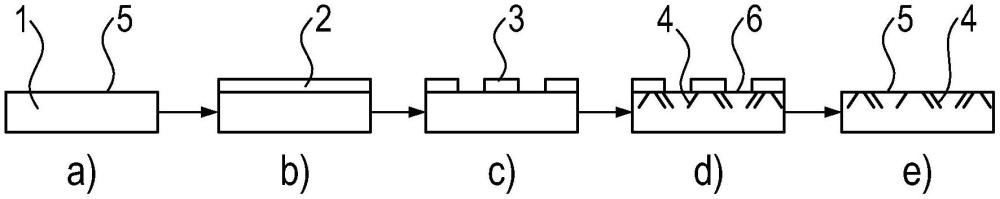

图1示意性地描绘了所要求保护的方法的各个步骤的可能流程。

图2显示了氮化物图案的一些可能的构成形式。

图3示出了在图1的步骤e)期间的位错相关特性的评估的示例。

采用的附图标记列表

1半导体衬底

2氮化物层

3图案化的氮化物

4位错

5表面

6边缘位置

具体实施方式

根据图1,所要求保护的方法可以从可选的步骤a)开始,在步骤a)处,半导体衬底经受热预处理。例如,半导体衬底可以在由器件制造工艺条件所规定的条件下被加热。

所要求保护的方法的第一必要步骤b)包括在半导体衬底的表面5上沉积氮化物层2。表面2是衬底晶片的其中预定内置电子器件的区域的顶端。通常,表面5是半导体衬底1的前表面。

在步骤c)期间,借助于光刻工艺形成图案化的氮化物3,其中通过RIE部分地去除氮化物层2,从而留下图案化的氮化物3。包括氢或氢化合物或者两者的气体被用作产生等离子体的源。

随后的步骤d)包括在处于800℃至1300℃的范围中的温度下,在炉(例如分批炉)中或在RTP工具中对半导体衬底1和图案化的氮化物3进行热处理。与衬底1的材料和图案化的氮化物3的材料之间的机械应力相关的该热处理在图案化的氮化物3的下方诱发位错4的形成。从边缘位置6(即图案化的氮化物3的侧向边界)开始,延伸到半导体衬底1的一定深度处的位错4在图案化的氮化物3的下方侧向传播。

接下来,在步骤e)期间,可以从半导体衬底1的表面5去除图案化的氮化物3,并且在热处理期间,在由氮化物结构3覆盖的区域中对与所形成的位错4相关的至少一种特性进行评估。

如图2所示,图案化的氮化物3可以呈诸如具有一定线宽d的正方形、圆、直线或斜线之类的形式。在热处理期间,位错形成于边缘位置6中,并在图案化的氮化物3的下方侧向传播。

示例

图3的中心部分示出了在从被用作半导体衬底的硅单晶晶片上去除图案化的氮化物之后以及在利用赖特蚀刻剂处理硅晶片之后,方格(正方)形氮化物结构周围的区域的光学显微镜图像。最高的位错密度位于边缘位置6处及其附近。图3的左侧部分表示中心部分中利用虚线矩形标记出的区域的放大视图。针对位错相关特性(即,位错密度和位错传播长度),该区域被评估。

图3的右侧部分为一图表,其中计算出的位错密度作为与边缘位置相距的距离的函数(并带有偏移量,以排除边缘位置处及其附近的相对高的位错密度)被绘制。在距离为约1μm的位置处发现最大密度,并且位错传播长度为约75μm。

根据图1的步骤b)至e),对不同的半导体衬底进行测试,测试结果被总结在下表中。在步骤c)期间形成的图案化的氮化物呈方格形的形式并具有250nm的厚度。步骤d)期间的热处理以RTP在1000℃的温度下实施,并且在步骤e)期间对位错密度(dd)和位错传播长度(dpl)进行评估。使用直径为300mm的抛光硅单晶晶片作为半导体衬底,其或者以20Ohmcm或更大的高电阻率进行p掺杂(p

表格

较高的体积氧水平(或含氧水平)揭示较高的机械鲁棒性,这可以在减小的位错传播长度中看出。类似地,p型掺杂剂的浓度也可以被用于控制该机械鲁棒性。此外,所发现的是,如果热处理期间的温度从900℃增大到1000℃,则位错密度和位错传播长度增大。类似地,如果氮化物结构的厚度从250nm增大到320nm,则位错密度和位错传播长度也增大。最后,可以确认就位错密度和位错传播长度两方面进行的测试的再现性。

- 一种功率半导体芯片的鲁棒性测试方法、系统及装置

- 提供至少一个信号的方法和系统以及用于信号接收器的鲁棒性测试的测试和测量系统