具有占空比校正电路的高速数字相位插值器

文献发布时间:2023-06-19 09:47:53

优先权声明

本申请要求享有于2018年12月14日提交的题为“HIGH SPEED DIGITAL PHASEINTERPOLATOR WITH DUTY CYCLE CORRECTION CIRCUITRY”的美国专利申请No.16/221,392的优先权,该申请通过引用的方式全部并入本文。

背景技术

在高速串行链路中,时钟数据恢复(CDR)是从串行数据流中提取采样时钟的机制。朝向数据流的眼图中心精细地相移所提取的时钟,以实现最佳位数据误差(BER)。这种相移通常通过两个时钟的加权之和来完成,这两个时钟在频率上相同,但是由已知相位差(例如,45°、90°等)来分离。对于千兆赫(GHz)高速链路,提取的采样时钟必须满足线性、粒度、功率和延迟方面的严格要求。另外,提取的采样时钟的占空比必须接近50%以实现双边沿采样。在这点上,可以实施占空比校正(DCC)机制以调整采样时钟的转换边沿。DCC范围、粒度和延迟是DCC电路的关键性能度量。开发满足上述规范并提供低功耗的CDR和DCC电路架构是一个挑战。

本文提供的背景技术描述是为了总体上呈现本公开的背景。除非本文中另有说明,否则本部分中描述的材料不是本申请中权利要求的现有技术,并且不因为包含在本部分中而承认是现有技术。

附图说明

根据下面给出的具体实施方式和本公开的各种实施例的附图,将更全面地理解本公开的实施例,然而其不是用于将本公开限于特定实施例,而仅用于解释和理解。

图1示出了根据本公开的一些实施例的通信链路的高级架构,所述通信链路采用具有带占空比校正(DCC)的低功率数字相位插值器(PI)的时钟数据恢复(CDR)。

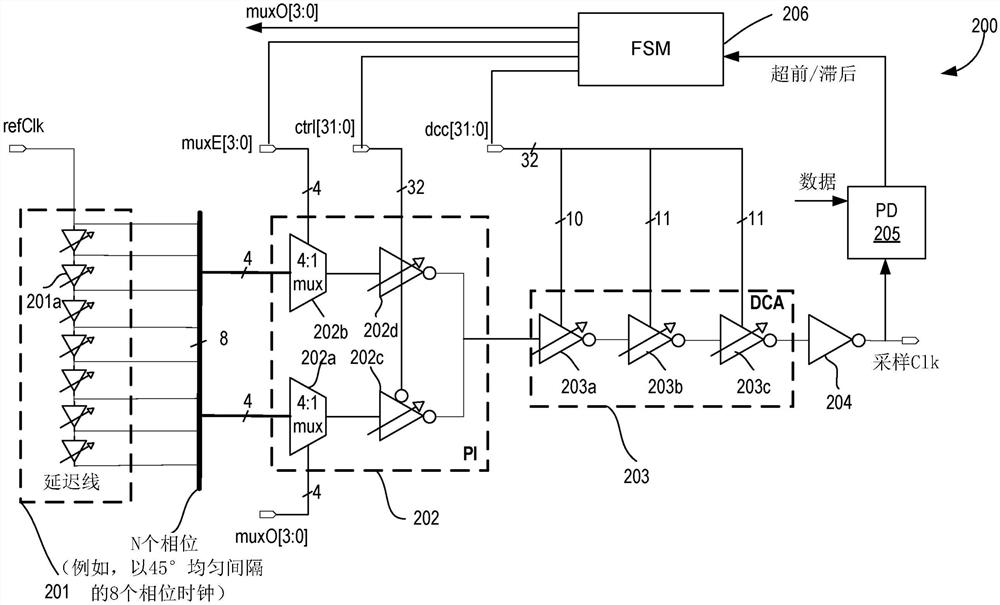

图2示出了根据一些实施例的具有与DCC分开的PI的CDR的示意图。

图3示出了根据一些实施例的图2中使用的PI和DCC的示意图。

图4示出了根据一些实施例的生成用于图2的CDR的PI、DCC和一个(或多个)多路复用器的控制代码的有限状态机(FSM)的一部分。

图5示出了根据一些实施例的图2的CDR的操作的时序图。

图6示出了根据一些实施例的具有完全集成的PI和DCC功能的低功率CDR的示意图。

图7示出了根据一些实施例的完全集成的PI和DCC功能的功能示意图。

图8A-B分别示出了根据一些实施例的具有DCC功能的偶数和奇数PI电路和用于DCC的可中断保持器。

图9示出了根据一些其他实施例的具有DCC功能的偶数和奇数PI电路。

图10示出了根据一些实施例的生成用于图6的CDR的PI/DCC和一个(或多个)多路复用器的控制代码的FSM的一部分。

图11示出了根据一些实施例的用于操作图6的CDR的时序图。

图12示出了根据一些实施例的用于操作图6的CDR的时序图,其中PI以最小码操作并且DCC代码是低码。

图13示出了根据本公开的一些实施例的具有带DCC的高速低功率PI的智能设备或计算机系统或SoC(片上系统)。

具体实施方式

一些实施例描述了将相位插值(PI)混频器与占空比校正(DCC)相组合的电路和架构。组合的PI混频器和DCC防止了三态反相器对之间的交叉竞争。在一些实施例中,将用于PI混频器中的p型和n型网络的控制代码解耦,并且将DCC机制融合在PI混频器代码解码方案中以实现低延迟相位插值和占空比校正。

各种实施例存在许多技术效果。例如,与分离且不同的过渡PI和DDC电路相比,各种实施例的架构减少了平均功耗(例如,高达44%)。PI和DCC功能的组合或集成减少了时钟数据恢复(CDR)环路延迟。例如,CDR环路延迟减少了大约0.5UI(单位间隔)。与分离且不同的过渡PI和DDC电路相比,PI和DCC功能的组合或集成还减少了微分非线性(DNL)和积分非线性(INL)。例如,DNL从2.48x减少到0.45x,而INL从7ps(皮秒)减少到2.8ps。与分离且不同的过渡PI和DDC电路相比,PI和DCC功能的组合或集成增加了DCC的范围。例如,DCC范围从55ps增加到60ps。而且,具有PI和DCC功能的组合或集成的电路还通过限制短路电流和消除慢占空比调整(DCA)电路来降低老化风险。根据各个附图和实施例,其他技术效果将是明显的。

在以下描述中,讨论了许多细节以提供对本公开的实施例的更透彻的解释。然而,对于本领域技术人员而言显而易见的是,可以在没有这些具体细节的情况下实施本公开的实施例。在其他实例中,以框图形式而不是详细地示出了公知的结构和设备,以免使本公开的实施例难以理解。

注意,在实施例的相应附图中,以线来表示信号。一些线可以较粗,用以表示更多的组成信号路径,和/或在一端或多端具有箭头,用以表示主要信息流动方向。这样的表示并非旨在是限制性的。相反,结合一个或多个示例性实施例来使用这些线,以有助于更容易地理解电路或逻辑单元。任何表示的信号(如按照设计需要或偏好所规定的)实际上都可以包括一个或多个信号,其可以在任一方向上传播,并且可以以任何适当类型的信号方案来实施。

术语“器件”通常可以指根据该术语的使用的上下文而定的装置。例如,器件可以指层或结构的堆叠、单个结构或层、具有有源和/或无源元件的各种结构的连接等。通常,器件是三维结构,其具有沿着x-y-z笛卡尔坐标系的x-y方向的平面和沿着z方向的高度。该器件的平面也可以是包括该器件的装置的平面。

在整个说明书和权利要求书中,术语“连接”表示在相连的事物之间的直接电连接(例如,电、机械或磁连接),没有任何中间器件。

术语“耦合”表示直接或间接连接,例如相连的事物之间的直接电、机械或磁连接,或者通过一个或多个无源或有源中间器件的间接连接。

术语“相邻”在此一般指事物的位置与另一事物相邻(例如,紧挨着或靠近,其间具有一个或多个事物)或毗连另一事物(例如,邻接它)。

术语“电路”或“模块”可以指被布置为彼此协作以提供期望功能的一个或多个无源和/或有源部件。

术语“信号”可以指至少一个电流信号、电压信号、磁信号或数据/时钟信号。“一”、“一个”和“该”的含义包括复数引用。“在……中”的含义包括“在……中”和“在……上”。

术语“缩放”通常指将设计(示意图和布图)从一个工艺技术转换为另一个工艺技术,并且随后减小布图面积。术语“缩放”通常还指在相同技术节点内减小布局和器件尺寸。术语“缩放”通常还可以指相对于另一个参数(例如,电源电平)调整(例如,减慢或加快—即,分别按比例减小或按比例加大)信号频率。

术语“基本上”、“接近”、“近似地”、“附近”和“约”通常指在目标值的+/-10%内。例如,除非在它们使用的明确上下文中另外指明,否则术语“基本上相等”、“大约相等”和“近似相等”意味着在如此描述的事物之间仅存在偶然变化。在本领域中,这种变化通常不超过预定目标值的+/-10%。

除非另有指明,否则用于描述共同对象的序数词“第一”、“第二”和“第三”等的使用仅仅表示涉及相似对象的不同实例,并非旨在暗示如此描述的对象必须在时间、空间、排序上或者以任何其他方式处于给定的顺序中。

对于本公开,短语“A和/或B”和“A或B”表示(A)、(B)或(A和B)。对于本公开,短语“A、B和/或C”表示(A)、(B)、(C)、(A和B)、(A和C)、(B和C)或(A、B和C)。

说明书和权利要求书中的术语“左”、“右”、“前”、“后”、“顶部”、“底部”、“上方”、“下方”等(如果有的话)用于描述性目的,而不一定用于描述永久的相对位置。例如,如本文中所使用的术语“上方”、“下方”、“前侧”、“后侧”、“顶部”、“底部”、“上方”、“下方”和“上”是指一个部件、结构或材料相对于器件内的其他所涉及的部件、结构或材料的相对位置,其中这种物理关系是明显的。

术语“之间”可以在器件的z轴、x轴或y轴的上下文中使用。在两个其他器件之间的器件可以直接连接到那些器件中的一个或两个,或者其可以通过一个或多个中间器件与其他两个器件这二者分离。

要指出的是,附图中具有与任何其他附图的元件相同的附图标记(或名称)的那些元件可以以与所描述的方式类似的任何方式操作或起作用,但不限于此。

图1示出了根据本公开的一些实施例的通信链路的高级架构100,所述通信链路采用具有带占空比校正(DCC)的低功率数字相位插值器(PI)的时钟数据恢复(CDR)。架构100包括域101和域102,其中域101用于通过信道103向域102发送数据流。在此,术语域可以指与另一域物理分离的任何电路区域,使得两个域之间的通信可能需要接收域中的时钟数据恢复(CDR)装置。例如,域101可以是第一管芯,并且域102可以是第二管芯。在另一示例中,域101可以是第一管芯的一个区域,并且域102可以是同一管芯的另一区域。

域101可以包括传送(Tx)时钟控制源(例如,Tx锁相环(PLL))101a和发射器(TX)。Tx PLL 101a可以接收参考时钟(RefClk)并生成锁相输出时钟(Tx Clk)以用于对要传送的数据TxData进行采样。然后,由Tx 101b的传送驱动器通过信道103将经采样数据驱动到接收器102c。由于时钟不是从域101传送到域102,因此在域102中使用CDR来产生时钟以对域102的接收器所接收的输入数据进行采样。

在一些实施例中,域102包括接收器PLL或延迟锁相环(DLL)102a、时钟数据恢复(CDR)电路102b和接收器102c。接收器PLL或DLL提供相对于接收器参考时钟(RefClk)的相位的多个时钟相位。N相位(其中“N”是任何数量)的时钟由包括相位插值器和占空比校正装置的CDR 102b接收。在各种实施例中,将PI(或PI混频器)和DCC功能集成在一起以产生高速CDR。组合的PI混频器和DCC防止了三态反相器对之间的交叉竞争。在一些实施例中,将用于PI混频器中的p型和n型网络的控制代码解耦,并且将DCC机制融合在PI混频器代码解码方案中以实现低延迟相位插值和占空比校正。

用于对所接收的数据流进行采样的时钟通常具有基本上等于由域101所发送的数据的输入数据速率的频率。例如,用于域102中的采样的时钟对于10Gb/s数据速率可以是10GHz,或者以100ps间隔的多个时钟。换言之,采样时钟可以与输入数据具有适当的相位关系,以获得足够的定时余量来实现期望的误码率(BER)。

在各种实施例中,从输入数据流中提取时钟频率和最佳相位位置。在一些实施例中,相位检测电路用于将来自PI的采样时钟与参考时钟进行比较。在一些实施例中,该参考时钟是经滤波的数据流本身。例如,由相位检测器使用针对符号间干扰(ISI)而滤波的数据流。期望相位检测器利用输入数据序列中的丢失的转变边沿来操作。这样,CDR 102b的相位检测器比较输入数据和采样该数据的恢复时钟之间的相位,并提供信息(超前或滞后(early or late))以调整采样时钟的相位。

图2示出了根据一些实施例的具有与DCC分开的PI的CDR的示意图100。示意图100包括相位发生器201、相位插值器(PI)202、占空比调节器203、输出缓冲器204、相位检测器205和有限状态机206。相位发生器201可以是任何适当的延迟线。在一些实施例中,延迟线是包括延迟单元的(PLL的)压控振荡器的一部分,其中每个延迟单元的输出提供不同的相位输出。在一些实施例中,延迟线是压控延迟线(VCDL),其是延迟锁相环(DLL)的一部分,并将每个延迟单元的延迟调整到特定的传播延迟。每个延迟单元201a的输出提供不同的相位。在该示例中,示出了七个延迟单元201a,其提供以45度均匀间隔开的八个不同相位时钟。在一些实施例中,将整个延迟线201锁定到一或具有输入时钟周期(在此为0000参考时钟)。

N相时钟(例如,8相时钟)由PI 202接收,PI 202生成相位插值时钟。PI 202实现数字至相位的转换。其产生作为两个输入时钟相位的加权之和的输出时钟。PI 202可以实现为尾电流求和插值电路或电压模式插值。用于插值器代码的映射技术可以是正弦的或线性的。

在一些实施例中,PI 202是数字PI,包括多路复用器202a和202b,用于各自接收一半的相位。例如,多路复用器202a从延迟线201接收后四个相位,而多路复用器202b从延迟线201接收前四个相位。取决于多路复用器的数量,可以利用同相时钟(I时钟)和正交相位时钟(Q时钟)的线性求和来生成任意相移。

在该示例中,多路复用器202a/b是4:1多路复用器(mux)且可由其相应的控制信号控制。多路复用器202a也被称为奇数多路复用器,并且可由4位控制信号(muxO[3:0])控制,而多路复用器202b被称为偶数多路复用器,并且可由另一个4位控制信号(muxE[3:0])控制。

多路复用器202a和202b的输出然后由相应的混频器202c和202d接收,所述混频器对其相应的输入进行插值并提供其输入的平均或插值版本作为输出。具有相邻相位的两个时钟通过多路复用器202a和202b被选择,并被馈送到PI混频器202c和202d,用于电压模式求和和插值。在一些实施例中,混频器202c和202d包括电流不补偿反相器(currentstarved inverter)。混频器202c和202d的驱动强度由互补温度计代码ctrl和ctrlb来调节。通过改变代码,可以混合时钟的特定权重,并且随后产生具有细粒度相移的输出时钟。插值线性通常是相位间隔与输出时间常数比率的函数。

然后,由DCA 203针对占空比失真调整PI 202的输出。在一些实施例中,DCA包括可调延迟反相器,其调整PI 202的输出的上升沿和/或下降沿以生成50%或接近50%的占空比输出。DCA的输出然后由缓冲器204(或反相器204)缓冲。缓冲器204的输出是采样时钟(采样Clk),相位检测器(PD)205将该采样时钟与输入数据流进行比较。在由PD 205接收输入数据流之前可以针对ISI和/或其他噪声对其进行滤波。PD 205的输出是用于调整采样时钟的相位的信息(超前或滞后)。

相位检测器可以是线性的或非线性的。线性相位检测器(例如,Hogge相位检测器)提供关于采样相位误差的符号和幅度信息。非线性相位检测器仅提供关于采样相位误差的符号信息。非线性相位检测器的示例包括Alexander、2x过采样或Band-Bang相位检测器。

PD 205的输出(超前/滞后)由FSM接收,其生成控制信号muxE、ctrl、dcc和muxO以调整samplingClk的相位和转换边沿,直到SamplingClk的采样边沿位于数据眼图的中心。在该示例中,muxE和muxO为4位信号,Ctrl为32位信号,并且dcc为32位信号。

图3示出了根据一些实施例的图2中使用的PI 202和DCA203的示意图300。PI混频器202包括奇数混频器202c和偶数混频器202d。在该示例中,提供了奇数混频器202c和偶数混频器202d的32个副本。奇数混频器202c包括如图所示耦合在一起的p型晶体管MP1和MP2以及n型晶体管MN1和MN2。偶数混频器202c包括如图所示耦合在一起的p型晶体管MP3和MP4以及n型晶体管MN3和MN4。反相器的输出是由DCA203接收的公共节点。DCA203包括三个反相器203a、203b和203c,在转换边沿中的一个上具有可调节延迟。反相器203a包括如图所示耦合在一起的p型晶体管MP5、MP6和MP7以及n型晶体管MN5。晶体管MP7可由dcc_code(例如,dcc_code[31:21])控制。反相器203b包括如图所示耦合在一起的p型晶体管MP8以及n型晶体管MN7、MN8和MN9。晶体管MN9可由dcc_code_b(例如,dcc_code_b[21:11])控制。反相器203c包括如图所示耦合在一起的p型晶体管MP5b、MP6b和MP7b以及n型晶体管MN5b。晶体管MP7b可由dcc_code(例如,dcc_code[10:0])控制。在各种实施例中,控制信号或时钟信号的后缀“b”指示对应控制信号或时钟信号的反相或互补信号。

图4示出了根据一些实施例的生成用于图2的CDR的PI、DCC和一个(或多个)多路复用器的控制代码的有限状态机(FSM)的一部分400。部分400包括控制器401、二进制至温度计解码器402和403、以及用于奇数多路复用器的时钟选择器404和用于偶数多路复用器的时钟选择器405。在一些实施例中,时钟选择器404和405实现独热编码器,其提供来自PI代码(例如,代码[7:0])的最高有效位(MSB)的独热信号muxO和muxE。在一些实施例中,从PI代码的最低有效位(LSB)解码PI混频器代码(例如,温度计代码ctrl)。在一些实施例中,从DCC二进制代码(例如,代码[4:0])的LSB解码DCA代码(例如,dcc)。表404a和405a分别示出了给定代码的MuxO和MuxE的解码模式(或真值表)。本领域的任何技术人员都可以实现用于表404a和405a的硬件。

图5示出了根据一些实施例的图2的CDR的操作的时序图500。在时序图500中示出了PI混频器202c/d的操作。在标记(1)处,偶数PI混频器202c的上拉网络由具有0相位的时钟(时钟0)驱动。偶数PI混频器202c的上拉网络包括晶体管MP1。在标记(2)处,用于奇数PI混频器202d的上拉网络由具有45°相位的时钟(时钟45)驱动。偶数PI混频器202d的上拉网络包括晶体管MP3。在标记(3)处,使上拉网络中的至少一个p型器件导通。这样,将混频器节点NL上拉到1。例如,PI混频器202c的p型器件MP2由ctrl_b导通。

在标记(4)处,偶数PI混频器202d的下拉网络由相同的时钟0驱动。下拉网络包括晶体管MN1。在标记(5)处,奇数PI混频器202c的下拉网络由相同的时钟45驱动。在标记(6)处,使下拉混频器202c/d中的至少一个n型器件(例如,MN2)导通,使得将混频器节点n1下拉到“0”。在标记(7)处,使PI混频器202c/d之一的上拉和下拉网络都导通。因此,短路电流流过上拉和下拉网络。在标记(8)处,基于混频器的权重调整混频器节点n1处的上升和下降转换。

在此,下拉和上拉网络分别被激活5/8周期。因此,短路电流在每一单个周期的至少1/4内流过PI混频器202c/d。参考图5所示的示例,在由标记为(7)的矩形表示的0°-45°和180°-225°相位期间发生竞争。

即使三态反相器202c和202d由互补温度计代码ctrl和ctrlb控制,由于奇数和偶数时钟之间的相位差,奇数和偶数三态反相器之间的交叉竞争仍会发生。这种竞争发生在插值阶段期间,并且可以持续总共2×45°=90°(1/4周期)。当反相器都被半启用时,这个短路电流是令人担心的。在最坏的情况下,平均电流可以高达72%以上。

为了支持合理的DCC范围(例如,1/8周期),使用具有至少三个CMOS级的DCA203。这种额外的单元延迟约为期望的DCC范围的2倍,即1/4周期或0.5UI,并且直接使CDR环延迟承受负担。

期望相移的粒度与温度计代码成线性关系。换言之,混频器202c/d应具有低微分非线性(DNL)和积分非线性(INL)。在此,DNL表示实际相移增量与理想相移增量的偏差,而INL表示实际相移与理想相移之间的偏差。图2的架构具有一个LSB步长高达2.48的DNL,并且在INL中接近10°或7ps。

通过调整转换边沿之一的驱动强度来实现占空比校正。然而,架构200的校正范围对PVT(工艺、电压和温度)变化敏感。在这方面,在慢和快工艺拐点处的支持的DCC范围可以相差高达2.5x。这可能限制在慢拐点处的最小延迟和在快拐点处的DCC范围之间的设计空间。此外,PI混频器202c/d上的短路电流以及DCA级203a/b/c上的慢斜率增加了由于老化应力而导致的电路故障的风险。

图6示出了根据一些实施例的具有完全集成的PI和DCC功能的低功率CDR的示意图600。为了减轻高功率、高延迟、高DNL和INL、窄DCC范围以及来自短路电流的可靠性问题中的一些,将相位插值和占空比调整功能集成在一起。集成的相位插值和占空比调整功能防止三态反相器对之间的交叉竞争。在各种实施例中,将PI混频器中的PMOS和NMOS网络的控制代码去耦,并且将DCC机制融合在PI混频器代码解码方案中以实现低延迟相位插值和占空比校正。

在一些实施例中,用集成的PI和DCA602(下文中称为电路602)代替PI 202和DCA203。电路602包括如图所示耦合在一起的多路复用器602a(用于偶数路径)和602b(或奇数路径)、斜率或延迟可调驱动器602c和602d、以及保持器门602e和602f。在一些实施例中,将斜率或延迟可调驱动器602c和602d实现为一对三态反相器,其具有在接地和电源节点之间的堆叠中的三个晶体管,如参考图8A所述。返回参考图6,在一些实施例中,对于较低功率设计,可以用如参考图9所描述的与传输门组合的二晶体管堆叠代替三晶体管堆叠。返回参考图6,在一些实施例中,保持器门602e和602f的功能可以由图8B的电路实施。

返回参考图6,在一些实施例中,通过使三态缓冲器的上拉和下拉网络去耦并且由不同的时钟和混频器代码集控制上拉和下拉网络来执行电路602(即,DCC特征集成到PI混频器中)。在一些实施例中,提供FSM 606以实施解码方案,以提供适当的混频器代码—Nctrl和PCtrl。Nctrl代码控制PI混频器602c和602d的下拉网络,而PCtrl代码控制PI混频器602c和602d的上拉网络。在该示例中将,32位代码用于Nctrl和PCtrl。FSM 606还提供用于多路复用器602a和602b的选择代码(例如,NnuxE、PmuxE、NmuxO和PmuxO)。后缀“E”和“O”分别指示偶数和奇数,而前缀“N”和“P”指示用于混频器的下拉和上拉器件的选择代码。在该示例中,4位代码用于多路复用器选择代码。在一些实施例中,奇数多路复用器602a的输出是用于控制混频器602c的上拉和下拉网络的时钟相位。在一些实施例中,偶数多路复用器602b的输出是用于控制混频器602d的上拉和下拉网络的时钟相位。

混频器代码将PI和DCC代码组合。下拉网络驱动固定边沿,其仅由PI代码控制,而驱动DCC的可调边沿的上拉网络由PI代码和DCC代码之和控制。在一些实施例中,DCC代码是2的互补形式。也可以使用其他形式的编码。除了通过FSM 606的导致本文讨论的各种优点的解码方案之外,PD 205和FSM 606的功能在其他方面大致相同。

图7示出了根据一些实施例的完全集成的PI和DCC功能的功能示意图700。功能示意图700包括集成的PI和DCC功能的功能电路(如虚线框701所示的)和保持器702。集成PI和DCC电路701的上拉和下拉功能包括偶数上拉网络701a、偶数下拉网络701b、第一偶数电阻性器件701c、第二偶数电阻性器件701d、奇数上拉网络701e和偶数下拉网络702f、第一奇数电阻性器件701g和第二奇数电阻性器件701h。

偶数上拉网络701a由相对于彼此相移90度的偶数时钟(clk_even_P和clk_even_P-90)控制。这些时钟由多路复用器602b提供。奇数上拉网络70le由相对于彼此相移90度的奇数时钟(clk_odd_P和clk_odd_P-90)控制。这些时钟由多路复用器602b提供。例如,如果clk_even_P经135°相移,那么上拉网络701a中的附加串联晶体管将由具有135°-90°=45°相移的时钟控制。

偶数下拉网络701b由相对于彼此相移90度的偶数时钟(clk_even_N和clk_even_N-90)控制。这些时钟由多路复用器602a提供。奇数下拉网络702f由相对于彼此相移90度的奇数时钟(clk_odd_N和clk_odd_N-90)控制。这些时钟由多路复用器602a提供。偶数上拉网络701a还耦合到由FSM606提供的Pctrlb控制的另一组上拉器件701c(第一偶数电阻性器件)。这些组的上拉器件701c具有可由Pctrlb代码控制的可调电阻。奇数上拉网络701c还耦合到由FSM 606提供的Pctrl控制的另一组上拉器件701g(第一奇数电阻性器件),其中Pctrlb是Petrl的反相。这些组的上拉器件701g具有可由Pctrl代码控制的可调电阻。

偶数下拉网络701b还耦合到由FSM 606提供的Nctrl控制的另一组下拉器件701d(第二偶数电阻性器件)。这些组的下拉器件701d具有可由Nctrlb代码控制的可调电阻。奇数下拉网络701f还耦合到由FSM 606提供的Nctrlb控制的另一组下拉器件701h(第二奇数电阻性器件),其中Nctrlb为Nctrl的反相。这些组的下拉器件701h具有可由Nctrlb代码控制的可调电阻。

利用这种配置,将上拉或下拉网络的有效活动阶段从1/2周期减少到1/4周期。这有助于消除经由图2的实施例所观察到的交叉竞争问题。由于有效活动阶段的缩短,内部节点n1可以在总共1/4时钟相位内不受驱动。根据各种实施例,通过引入弱可中断保持器702来防止这种浮置状态。

图8A-B分别示出了根据一些实施例的具有DCC功能的偶数和奇数PI电路800和可中断保持器820。在一些实施例中,PI和DCC功能由6个晶体管的堆叠来执行。在此,对于偶数模式,PI混频器和DCA堆叠包括p型晶体管MP1a、MP2a和MP3a以及n型晶体管MN1a、MN2a和MN3a。晶体管MP1a和MP2a形成上拉网络701a,而晶体管MN1a和MN2a形成下拉网络701b。在这些相应的网络中,晶体管串联连接并且由相应的但具有-90°相移的时钟控制。晶体管MP3a和MN3a由组合PI和DCC功能的代码控制。通过参考图10描述的解码方案生成这些代码(Pctrl和Nctrl以及它们的补码Pctrlb和Nctrlb)。

返回参考图8A-B,对于奇数模式,PI混频器和DCA堆叠包括p型晶体管MP1b、MP2b和MP3b以及n型晶体管MN1b、MN2b和MN3b。晶体管MP1b和MP2b形成上拉网络701c,而晶体管MN1b和MN2b形成下拉网络702d。在这些相应的网络中,晶体管串联连接并且由相应的但具有-90°相移的时钟控制。晶体管MP3b和MN3b由组合PI和DCC功能的代码控制。

在一些实施例中,保持器电路820(其实施门602e和602f的功能)包括与PI混频器和DCC堆叠800类似的堆叠。在一些实施例中,保持器电路820包括p型晶体管MP1c、MP2c和MP3c、n型晶体管MN1c、MN2c和MN3c以及反馈反相器821。反馈反相器821的输入耦合到节点n1(图8A的n1的相同节点)以用于启用或禁用保持器功能。还应注意,将相反极性时钟相位提供给保持器电路820的上拉和下拉器件。例如,将clk_even_N和clk_odd_N分别提供给P型器件MP1c和MP2c,而将clk_even_P和clk_odd_P分别提供给N型器件MN1c和MN2c。

由于PI混频器和DCC堆叠602c和602d的上拉或下拉网络的有效活动阶段从1/2周期减少到1/4周期,因此减轻了PI混频器堆叠202c/d所遇到的交叉竞争问题。然而,由于缩短了上拉或下拉网络的有效活动阶段,而在没有保持器电路820的情况下,内部节点n1在总共1/4时钟相位内不受驱动。通过弱可中断保持器820防止这种浮置状态。

图9示出了根据一些其他实施例的具有DCC功能的偶数和奇数PI电路900。对于较低功率设计,图8A中所示的602c/d的6晶体管堆叠可以用如图9中所示的与传输门组合的4晶体管堆叠(在接地与电源之间)代替。在一些实施例中,偶数上拉网络701a包括P型器件MP11a,其栅极由传输门901控制。传输门901的晶体管由偶数时钟及其互补(clk_even_P和clkb_even_P)控制,并且用于传递clk_even_P-90以控制MP11a的栅极。在此,MP11a具有32个并联耦合在一起的实例。在一些实施例中,甚至下拉网络701b也包括n型器件MN11a,其栅极由传输门902控制。传输门902的晶体管由偶数时钟和其互补(clk_even_N和clkb_even_N)控制,并且用于传递clk_even_N-90以控制MN11a的栅极。在此,MNlla具有32个并联耦合在一起的实例。晶体管MP3a和MN3a由Pctrlb_even和Nctrl_even控制,正如图8A中所示。

返回参考图9,在一些实施例中,奇数上拉网络701c包括p型器件MP11b,其栅极由传输门903控制。传输门903的晶体管由奇数时钟及其互补(clk_odd_P和clkb_odd_P)控制,并且用于传递clk_odd_P-90以控制MP11b的栅极。在此,MP11b具有32个并联耦合在一起的实例。在一些实施例中,奇数下拉网络701d包括n型器件MN11b,其栅极由传输门904控制。传输门904的晶体管由奇数时钟及其互补(clk_odd_N和clkb_odd_N)控制,并且用于传递clk_odd_N-90以控制MN11b的栅极。在此,MN11a具有32个并联耦合在一起的实例。晶体管MP3b和MN3b由Pctrl_odd和Nctrlb_odd控制,正如图8A中所示。

图10示出了根据一些实施例的生成用于图6的CDR的PI/DCC以及(一个或多个)多路复用器的控制代码的FSM的一部分1000。部分1000包括控制器1001、加法器1002、温度计编码器403和404、奇数时钟选择器404a和405b以及偶数时钟选择器404b和405b。图11-12示出了图10的操作。

图11示出了根据一些实施例的用于操作图6的CDR的时序图1100。时序图1100示出了其中不存在DC校正(即,DCC代码=0)的基线场景。在这种情况下,PI混频器的P和N网络都从PI时钟多路复用器接收相同的时钟。通过启用可中断保持器702/820来防止从135°到180°和315°到360°的浮置状态。

在标记1处,偶数上拉网络中的串联p型器件(例如,MP1a、MP2a)分别由时钟0和时钟270驱动。有效时钟是时钟90而不是时钟180。在标记2处,奇数上拉网络中的串联p型器件(例如,MP1b和MP2b)由时钟45和时钟315驱动。有效时钟是90而不是180。在标记3处,使上拉网络中的至少一个p型器件导通,从而允许将混频器节点n1上拉至逻辑1。

在标记4处,偶数下拉网络中的串联n型器件(例如,MN1a、MN2a)分别由时钟0和时钟270驱动。有效时钟是时钟90而不是时钟180。在标记5处,奇数下拉网络中的串联n型器件(例如MN1b和MN2b)由时钟0和时钟270驱动。有效时钟是90而不是180。在标记6处,使下拉网络中的至少一个n型器件导通,从而允许将混频器节点n1下拉至逻辑0。

在一些实施例中,从135°到180°启用保持器的下拉网络以将内部节点n1保持到VSS。同时,从315°到360°启用保持器702/820的上拉网络以将内部节点n1保持到VCC,如标记(7)所示。在标记7处,上拉和下拉网络两者都截止,这使得节点n1浮置并且启用保持器820。在标记8处,可以基于PI控制代码来微调混频器节点n1处的上升转换和下降转换两者的时钟相位。

存在两种极端情况,其中(a)将PI混频器锁定在最小代码,并且DCC为最负代码(-32);(b)将PI混频器锁定在最大代码,并且DCC为最正代码(+31)。注意,与图2的架构相反,混频器的上拉和下拉网络可以连接到不同的时钟源。例如,如果从0°和45°时钟生成固定边沿,则可以从(i)315°和0°、(ii)0°和45°、(iii)45°和90°中的任一个生成可调边沿。

图12示出了根据一些实施例的用于操作图6的CDR的时序图1200,其中PI以最小代码操作并且DCC代码是低代码。

在标记1处,假设PI被锁定在最小代码,而DCC代码=-32(最小),则进入PU网络的PI码被减去32。当PI被锁定时,MuxE_PD和MuxO_PD选择代码保持相同,并且选择时钟0°和45°。在标记1处,MuxE_PU继续选择时钟0°,而MuxO_PU从时钟45°切换到时钟315°。这允许混频器节点n1在相位上较早地上升到45°。

在标记2,假设PI被锁定在最大代码,而DCC代码=31(最大),则进入PU网络的PI代码增加31。当PI被锁定时,MuxE_PD和MuxO_PD选择代码保持相同,并且选择时钟0°和45°。MuxE_PU继续选择时钟0°,而MuxO_PU从时钟45°切换到时钟135°。这允许混频器节点n1在相位上较慢地上升到45°。

在标记3处,PD的PI代码没有被并入DCC代码中。因此,PD网络的所有控制和时钟保持相同(例如,锁定在相应的PI代码)。在标记4处,PU网络控制固定边沿。该边沿保持在PI代码所指示的相移。在标记5处,混频器节点n1在相位上较早上升到45°。这允许DCC达到-45°。在标记6处,混频器节点在相位上较晚地上升到45°。这允许DCC达到+45°。

图13示出了根据本公开的一些实施例的具有包括带DCC的高速低功率PI的时钟数据恢复电路的智能设备或计算机系统或SoC(片上系统)。

图13示出了其中可以使用平面接口连接器的移动设备的实施例的框图。在一些实施例中,计算设备1600表示移动计算设备,例如计算平板电脑、移动电话或智能电话、支持无线功能的电子阅读器或其他无线移动设备。应理解的是,总体上示出了某些部件,并且在计算设备1600中未示出这种设备的所有部件。

在一些实施例中,根据所讨论的一些实施例,计算设备1600包括具有带DCC的高速低功率PI(例如,图6的架构)的第一处理器1610。根据一些实施例,计算设备1600的其他块也可以包括带DCC的高速低功率PI(例如,图6的架构)。

本公开的各种实施例还可以包括1670内的网络接口(例如,无线接口),从而使系统实施例可以包含到无线设备中,例如蜂窝电话或个人数字助理。

在一些实施例中,处理器1610可以包括一个或多个物理设备,例如微处理器、应用处理器、微控制器、可编程逻辑器件或其他处理装置。由处理器1610执行的处理操作包括在其上执行应用程序和/或设备功能的操作平台或操作系统的执行。处理操作包括与和用户或和其他设备的I/O(输入/输出)有关的操作、与电源管理有关的操作、和/或与将计算设备1600连接到另一设备有关的操作。处理操作还可以包括与音频I/O和/或显示I/O有关的操作。

在一些实施例中,计算设备1600包括音频子系统1620,其表示与向计算设备提供音频功能相关联的硬件(例如,音频硬件和音频电路)和软件(例如,驱动器、编码解码器)部件。音频功能可以包括扬声器和/或耳机输出、以及麦克风输入。用于这种功能的设备可以集成到计算设备1600中,或者连接到计算设备1600。在一个实施例中,用户通过提供由处理器1610接收并处理的音频命令来与计算设备1600交互。

在一些实施例中,计算设备1600包括显示子系统1630。显示子系统1630表示为用户提供视觉和/或触觉显示以与计算设备1600交互的硬件(例如,显示设备)和软件(例如,驱动器)部件。显示子系统1630包括显示接口1632,其包括用于向用户提供显示的特定屏幕或硬件设备。在一个实施例中,显示接口1632包括与处理器1610分离的逻辑装置,用以执行与显示有关的至少一些处理。在一个实施例中,显示子系统1630包括触摸屏(或触控板)设备,其向用户提供输出和输入。

在一些实施例中,计算设备1600包括I/O控制器1640。I/O控制器1640表示与和用户的交互有关的硬件设备和软件部件。I/O控制器1640可操作用于管理作为音频子系统1620和/或显示子系统1630的一部分的硬件。另外,I/O控制器1640示出了用于连接到设备1600的额外设备的连接点,用户可以通过其与系统交互。例如,可以附接到计算设备1600的设备可以包括麦克风设备、扬声器或立体声系统、视频系统或其他显示设备、键盘或辅助键盘设备、或者用于与诸如读卡器的特定应用或其他设备一起使用的其他I/O设备。

如上所述,I/O控制器1640可以与音频子系统1620和/或显示子系统1630交互。例如,通过麦克风或其他音频设备的输入可以提供用于计算设备1600的一个或多个应用程序或功能的输入或命令。另外,代替或除了显示输出,可以提供音频输出。在另一个示例中,如果显示子系统1630包括触摸屏,则显示设备还用作输入设备,其可以至少部分由I/O控制器1640管理。计算设备1600上也可以有另外的按钮或开关,以提供由I/O控制器1640管理的I/O功能。

在一些实施例中,I/O控制器1640管理设备,例如加速度计、相机、光传感器或其他环境传感器、或者可以包括在计算设备1600中的其他硬件。输入可以是部分直接用户交互,以及向系统提供环境输入以影响其操作(例如,滤除噪声、针对亮度检测调整显示、为相机应用闪光灯、或其他特征)。

在一些实施例中,计算设备1600包括电源管理1650,其管理电池电力的使用、电池的充电、以及与省电操作有关的特征。存储器子系统1660包括用于在计算设备1600中存储信息的存储器设备。存储器可以包括非易失性(如果中断到存储器设备的电力,状态不改变)和/或易失性(如果中断到存储器设备的电力,状态不确定)存储器设备。存储器子系统1660可以存储应用程序数据、用户数据、音乐、照片、文档、或其他数据、以及与计算设备1600的应用程序和功能的执行有关的系统数据(无论是长期的还是暂时的)。

实施例的元件也可以作为用于存储计算机可执行指令(例如,用以实施本文所讨论的任何其他处理的指令)的机器可读介质(例如,存储器1660)来提供。机器可读介质(例如,存储器1660)可以包括但不限于闪存、光盘、CD-ROM、DVD ROM、RAM、EPROM、EEPROM、磁或光卡、相变存储器(PCM)、或者适合于存储电子或计算机可执行指令的其他类型的机器可读介质。例如,本公开的实施例可以作为计算机程序(例如,BIOS)下载,其可以通过数据信号的方式经由通信链路(例如,调制解调器或网络连接)从远程计算机(例如,服务器)传送到请求计算机(例如,客户机)。

在一些实施例中,计算设备1600包括连接1670。连接1670包括硬件设备(例如,无线和/或有线连接器和通信硬件)和软件部件(例如,驱动器、协议栈),以使得计算设备1600能够与外部设备通信。计算设备1600可以是分离的设备,例如其他计算设备、无线接入点或基站,以及外围设备(例如,耳机、打印机或其他设备)。

连接1670可以包括多个不同类型的连接。概括而言,计算设备1600被示为具有蜂窝连接1672和无线连接1674。蜂窝连接1672通常是指由无线载波提供的蜂窝网络连接,例如借助GSM(全球移动通信系统)或其变型或其派生物、CDMA(码分多址)或其变型或其派生物、TDM(时分复用)或其变型或其派生物、或者其他蜂窝服务标准来提供。无线连接(或无线接口)1674是指不是蜂窝的无线连接,并且可以包括个域网(例如,蓝牙、近场等)、局域网(例如,Wi-Fi)和/或广域网(例如,WiMax)或其他无线通信。

在一些实施例中,计算设备1600包括外设连接1680。外设连接1680包括硬件接口和连接器、以及软件部件(例如,驱动器、协议栈),用以进行外设连接。应理解的是,计算设备1600可以是到其他计算设备的外围设备(“至”1682)、以及具有连接到其的外围设备(“自”1684)。计算设备1600通常具有“对接”连接器以连接到其他计算设备,用于例如管理(例如,下载和/或上载、改变、同步)计算设备1600上的内容的目的。另外,对接连接器可以允许计算设备1600连接到特定外设,其允许计算设备1600控制例如到视听或其他系统的内容输出。

除了专有的对接连接器或其他专有连接硬件之外,计算设备1600还可以经由常用或基于标准的连接器获得外设连接1680。常用类型可以包括通用串行总线(USB)连接器(其可以包括任何数量的不同硬件接口)、包括MiniDisplayPort(MDP)的DisplayPort、高清晰度多媒体接口(HDMI)、火线(Firewire)或其他类型。

说明书中提及“实施例”、“一个实施例”、“一些实施例”或“其他实施例”表示结合实施例说明的特定特征、结构或特性包括在至少一些实施例中,但不一定是所有实施例。“实施例”、“一个实施例”或“一些实施例”的多次出现不一定全都指相同的实施例。如果说明书表述部件、特征、结构或特性“可以”、“或许”或“能够”被包括,那么该特定部件、特征、结构或特性不必需被包括。如果说明书或权利要求提及“一”或“一个”元件,这并不表示仅有一个元件。如果说明书或权利要求书提及“一个额外的”元件,这并不排除一个以上的该额外元件的存在。

此外,特定特征、结构、功能或特性可以在一个或多个实施例中以任何适当的方式组合。例如,第一实施例可以与第二实施例组合,只要与这两个实施例相关联的特定特征、结构、功能或特性不相互排斥。

尽管结合其特定实施例说明了本公开,但根据前述说明,这种实施例的许多替代、修改和变化对于本领域普通技术人员而言是显而易见的。本公开的实施例旨在涵盖如落入所附权利要求书的宽泛范围内的所有这种替代、修改和变化。

另外,为了图示和论述的方便起见,在所呈现的附图内可以显示或可以不显示公知的与集成电路(IC)芯片或其他部件的电源/接地连接,从而不使本公开难以理解。此外,可以以方框图形式显示装置,以避免使本公开难以理解,并且还鉴于以下事实:相对于这种方框图装置的实施方式的细节与要在其内实施本公开的平台极为相关(即,这种细节应完全在本领域技术人员的理解范围内)。在阐述了特定细节(例如,电路)以便说明本公开的示例性实施例的情况下,对于本领域技术人员而言显而易见的是,可以无需这些特定细节或者借助这些特定细节的变化来实施本公开。本说明因而应视为说明性的而非限制性的。

提供了摘要,其允许读者确定本技术公开的本质和要旨。在有如下认识的情况下提交了摘要:其不用于限制权利要求书的范围或含义。所附权利要求书由此包含到具体实施方式中,其中每个权利要求都独立作为单独的实施例。

- 具有占空比校正电路的高速数字相位插值器

- 一种占空比稳定数字控制单级多时钟相位插值器